www.datasheeTOSHIBA

### CMOS 32-bit Micro-controller

# TMP92CD54IF

# 1. Outline and Device Characteristics

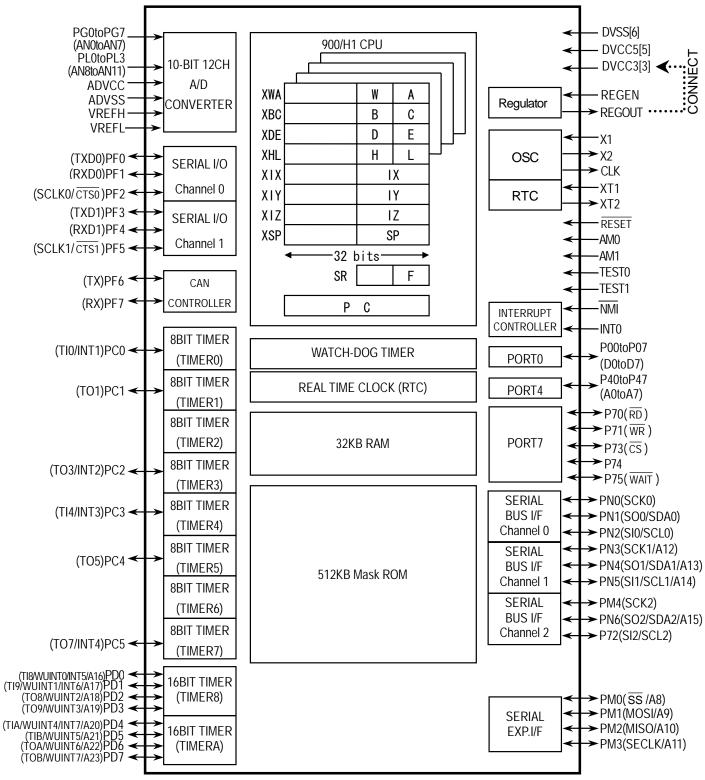

TMP92CD54I is high-speed advanced 32-bit micro-controller developed for controlling equipment which processes mass data.

TMP92CD54I is a micro-controller which has a high-performance CPU (900/H1 CPU) and various built-in I/Os. TMP92CD54I is housed in a 100-pin mini flat package.

Device characteristics are as follows:

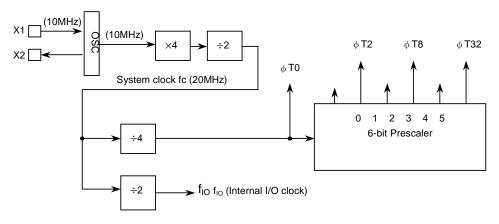

(1) CPU: 32-bit CPU(900/H1 CPU)

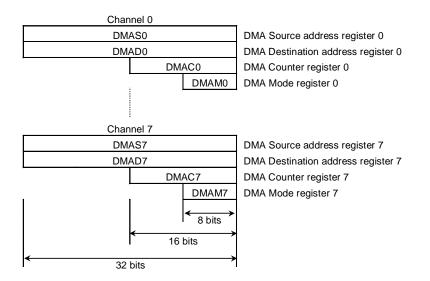

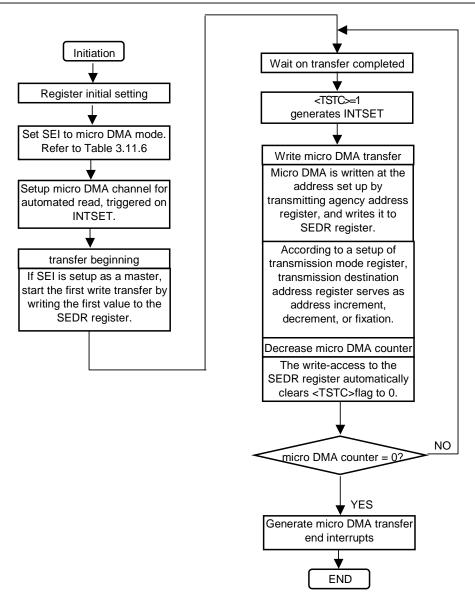

Compatible with TLCS-900,900/L,900/L1,900/H,900/H2's instruction code 16Mbytes of linear address space General-purpose register and register banks Micro DMA : 8channels (250ns / 4bytes at fc = 20MHz, best case) Minimum instruction execution time : 50ns(at 20MHz) Internal data bus : 32-bit

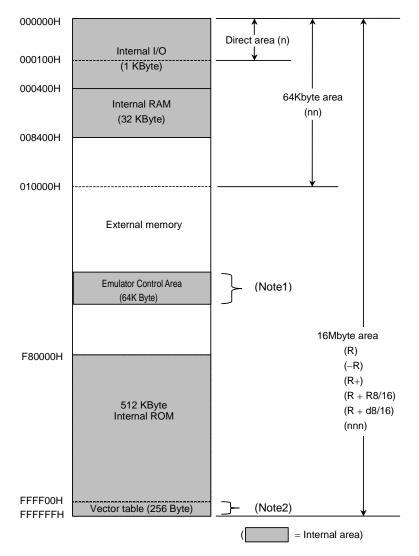

### (2) Internal memory

Internal RAM : 32K-byte Internal ROM : 512K-byte Mask ROM

### **RESTRICTIONS ON PRODUCT USE**

060116EBP

- The information contained herein is subject to change without notice. 021023\_D

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc. 021023\_A

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunctionor failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk. 021023\_B

- The products described in this document shall not be used or embedded to any downstream products of which manufacture, use and/or sale are prohibited under any applicable laws and regulations. 060106\_Q

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of TOSHIBA or others. 021023\_C

- The products described in this document are subject to the foreign exchange and foreign trade laws. 021023\_E

- For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance/Handling Precautions. 030619\_S

| (3)          | External memory expansion                                                                                                         |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------|

|              | 16M-byte linear address space (memory mapped I/O)                                                                                 |

|              | External data bus : 8bit(for external I/O expansion)                                                                              |

|              | * Can't use upper address bus when built in I/Os are selected                                                                     |

| (4)          | Memory controller (MEMC)                                                                                                          |

|              | Chip select output : 1 channel                                                                                                    |

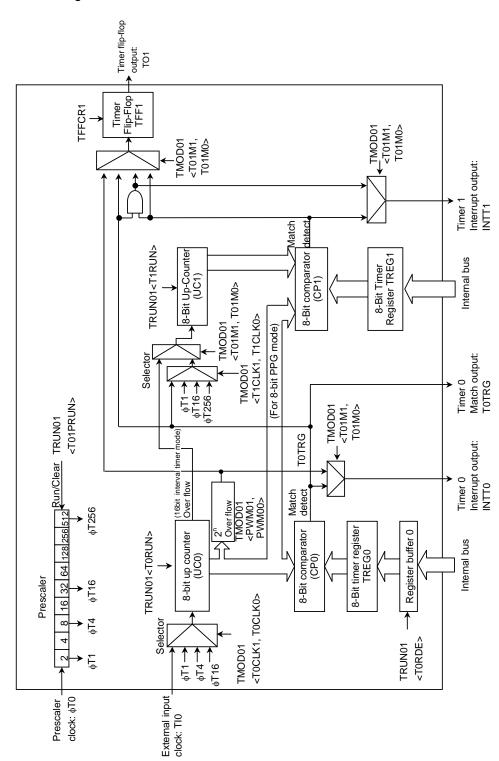

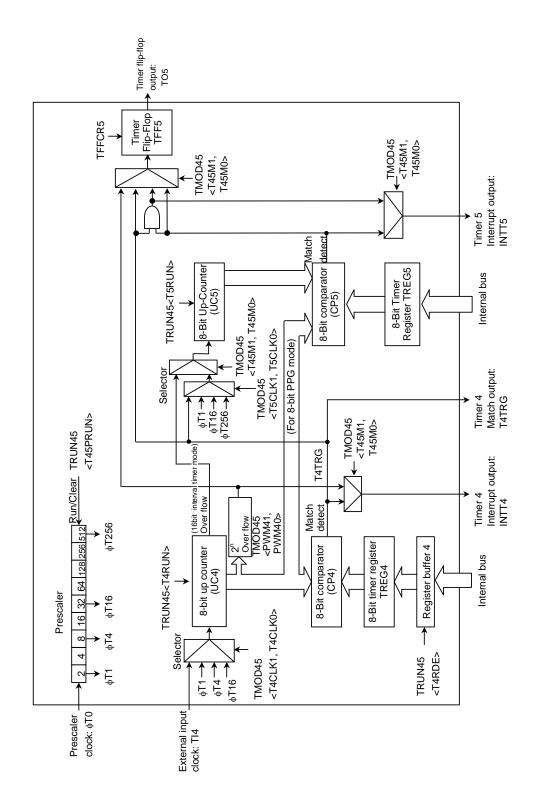

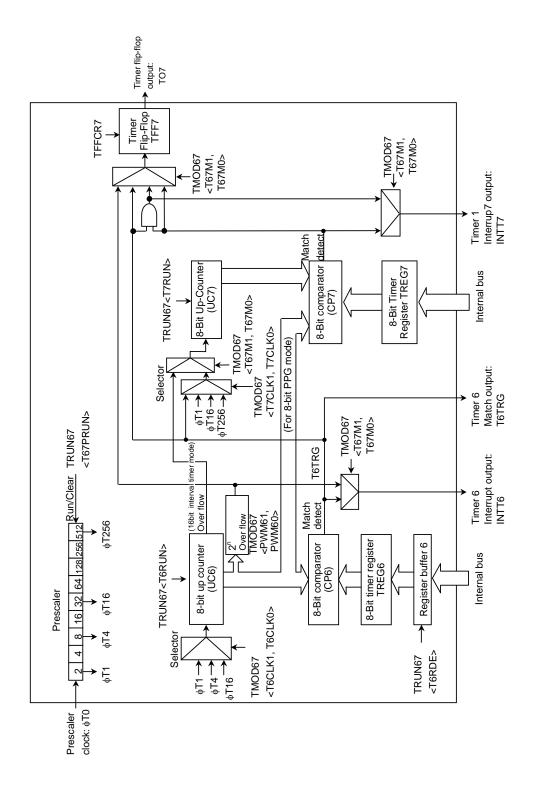

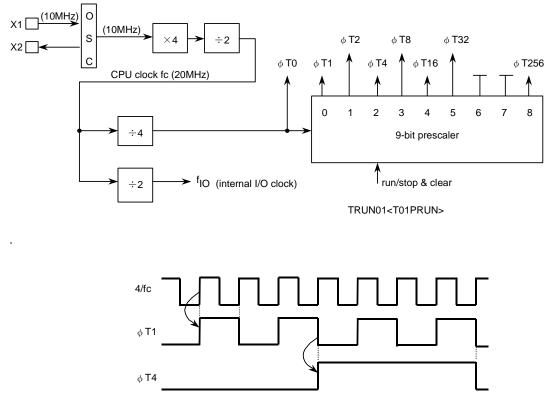

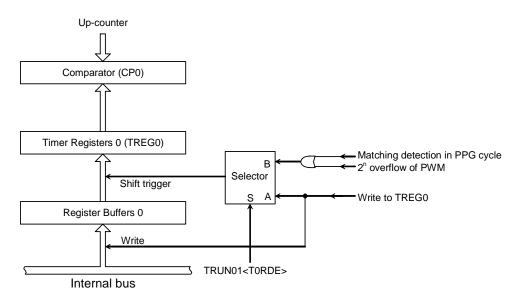

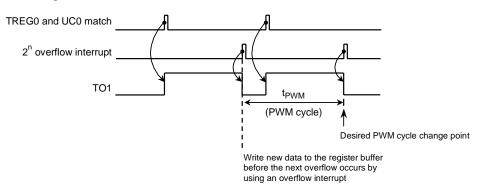

| (5)          | 8-bit timer : 8 channels                                                                                                          |

|              | 8-bit interval timer mode (8 channels)                                                                                            |

|              | 16-bit interval timer mode (4 channels)                                                                                           |

|              | 8-bit programmable pulse generation (PPG) output mode (4 channels)<br>8-bit pulse width modulation (PWM) output mode (4 channels) |

| (6)          | 16-bit timer : 2 channels                                                                                                         |

|              | 16-bit interval timer mode                                                                                                        |

|              | 16-bit event counter mode                                                                                                         |

|              | 16-bit programmable pulse generation (PPG) output mode                                                                            |

|              | Frequency measurement mode                                                                                                        |

|              | Pulse width measurement mode                                                                                                      |

| (-)          | Time differential measurement mode                                                                                                |

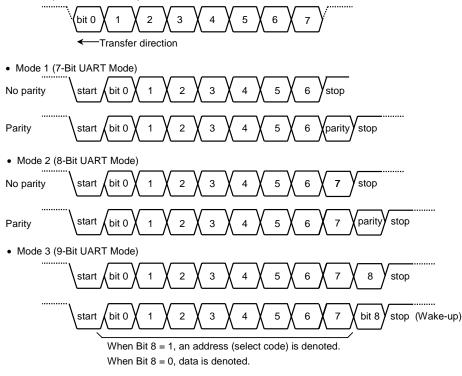

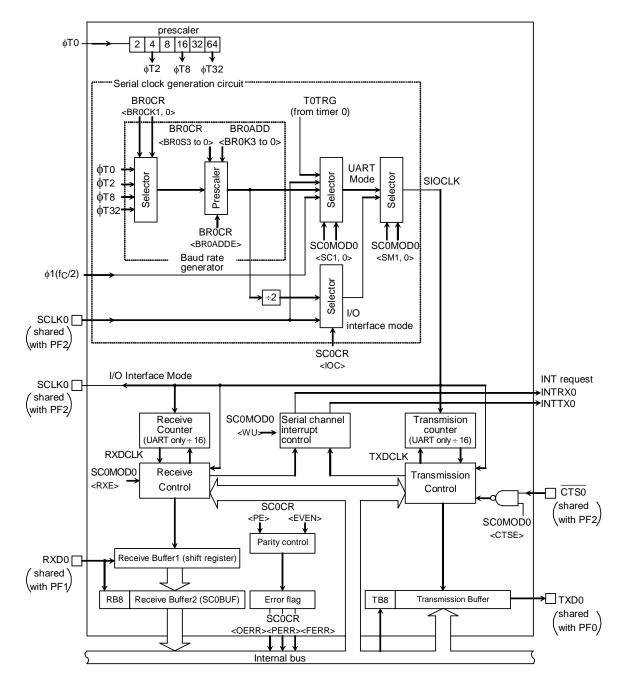

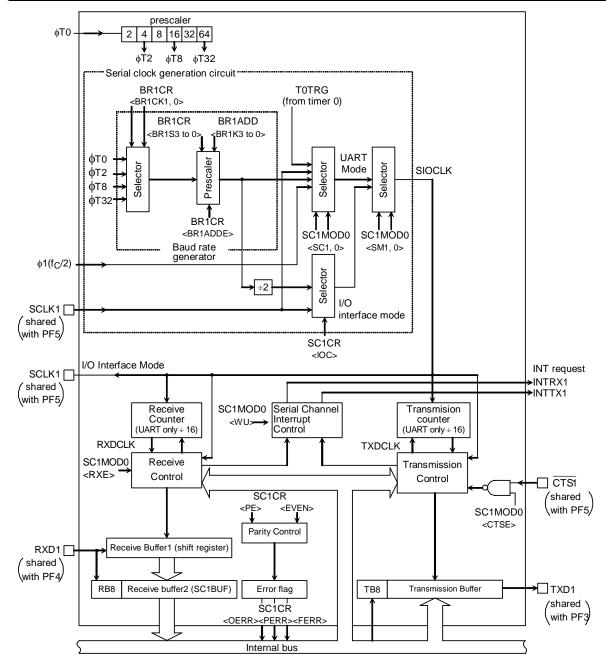

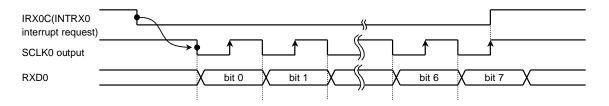

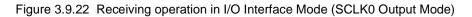

| (7)          | Serial interface (SIO) : 2 channels                                                                                               |

|              | I/O interface mode                                                                                                                |

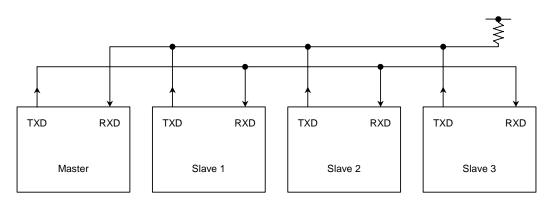

| (8)          | Universal asynchronous receiver transmitter (UART) mode<br>Serial expansion interface (SEI) : 1 channel                           |

| (6)          | -                                                                                                                                 |

| ( <b>0</b> ) | Baud rate $4/2/0.5$ Mbps at fc=20MHz.                                                                                             |

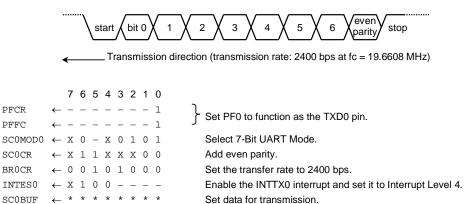

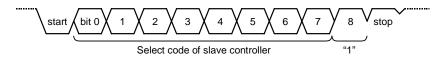

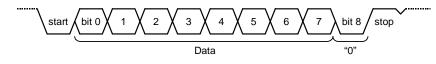

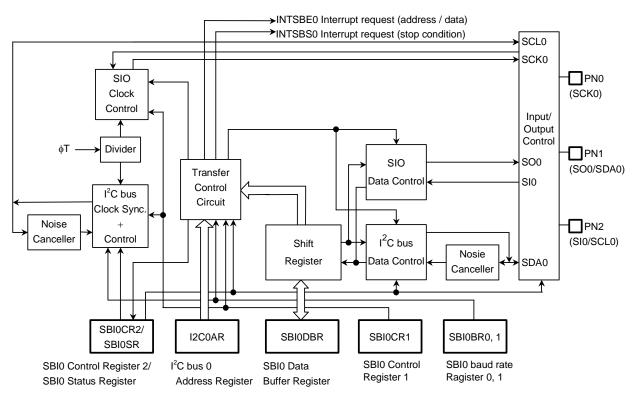

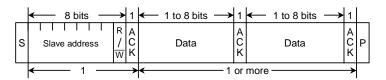

| (9)          | Serial bus interface (SBI) : 3 channels                                                                                           |

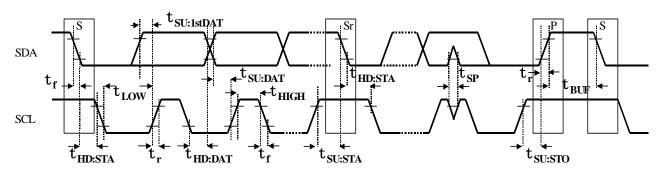

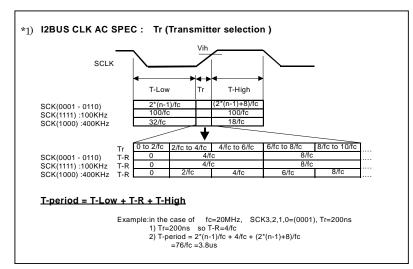

|              | Clocked-synchronous 8-bit serial interface mode<br>I <sup>2</sup> C bus mode                                                      |

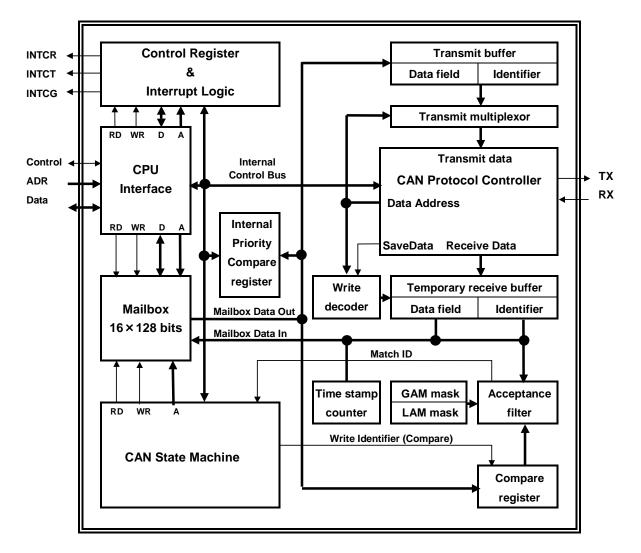

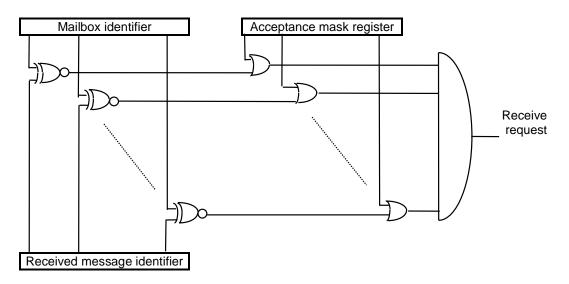

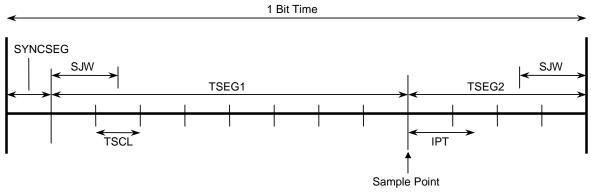

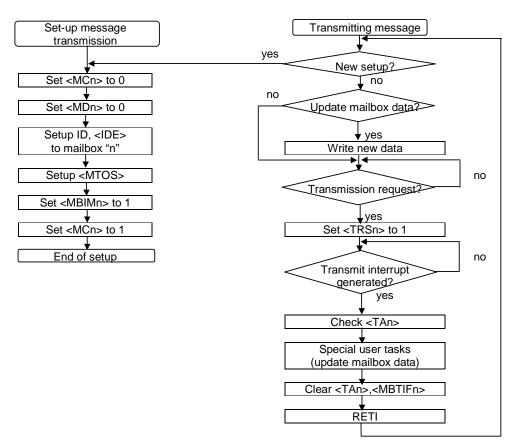

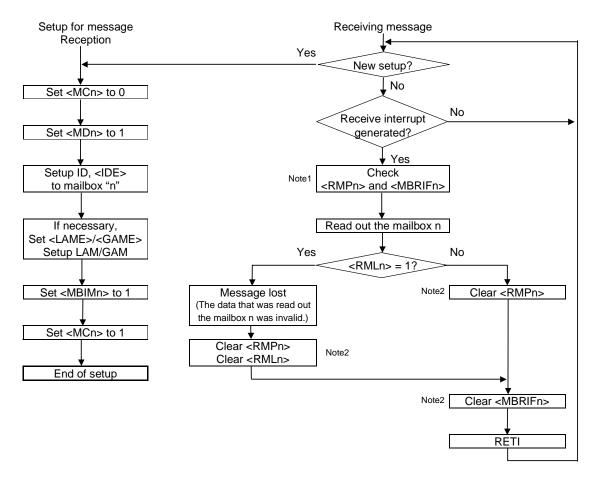

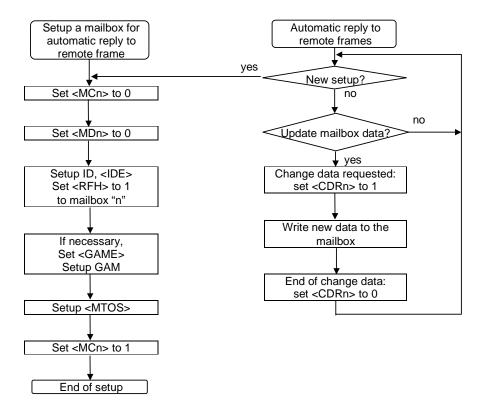

| (10)         | CAN controller : 1channel                                                                                                         |

| (10)         | Supports CAN version 2.0B.                                                                                                        |

|              | 16 mailboxes                                                                                                                      |

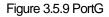

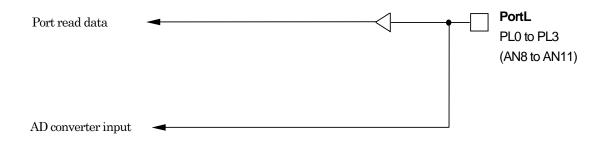

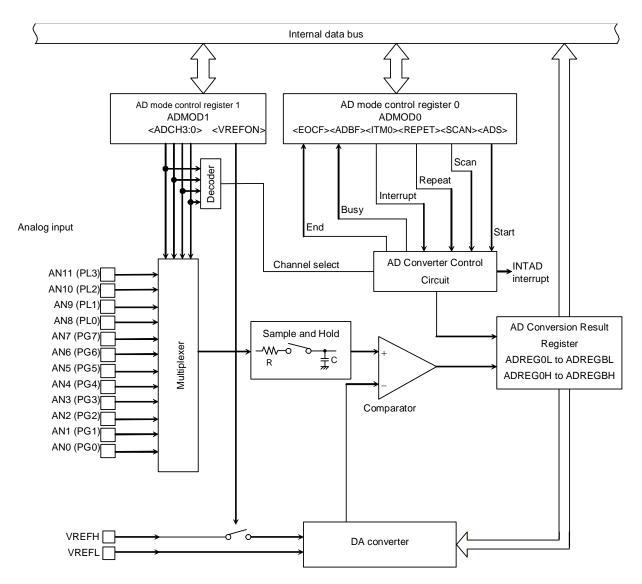

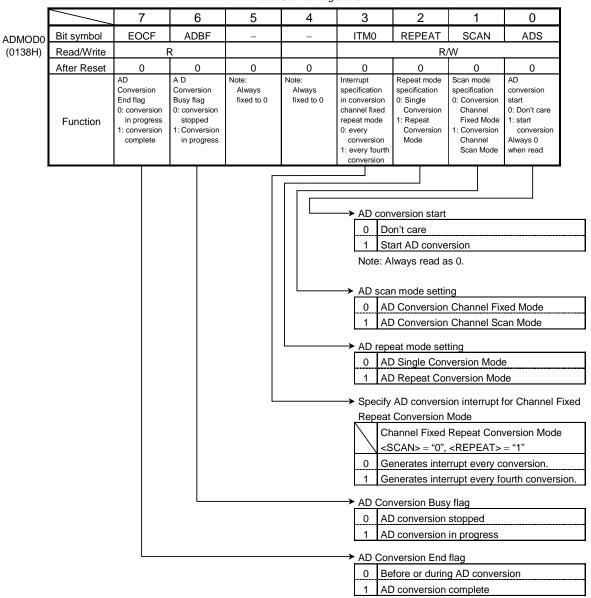

| (11)         | 10-bit A/D converter (ADC) : 12 channels                                                                                          |

|              | A/D conversion time 8µsec @fc=20MHz.                                                                                              |

|              | Total tolerance +/- 3LSB (excluding quantization error)                                                                           |

|              | Scan mode for all 12channels                                                                                                      |

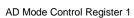

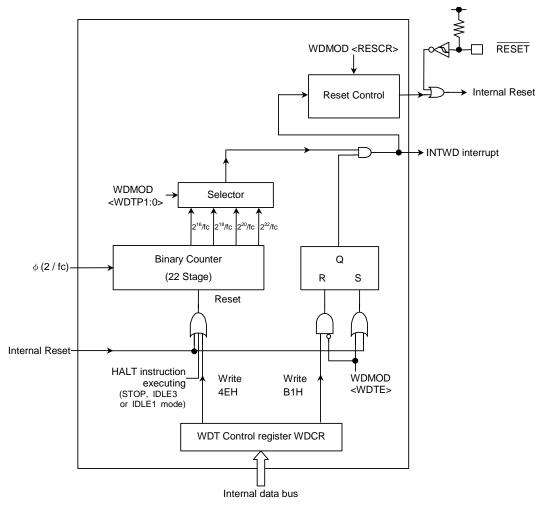

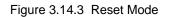

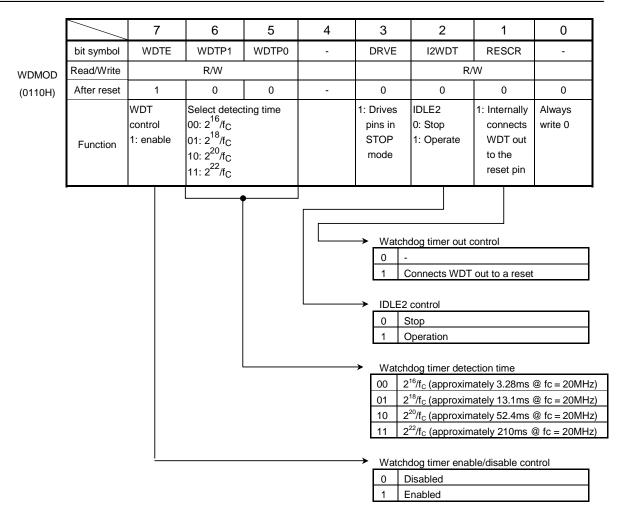

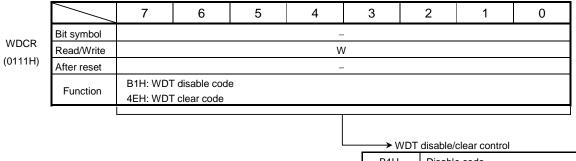

| (12)         | Watch dog timer (WDT)                                                                                                             |

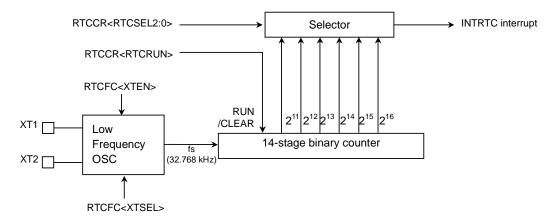

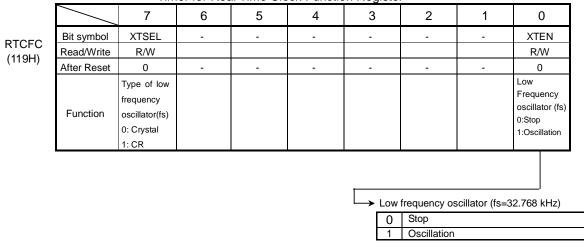

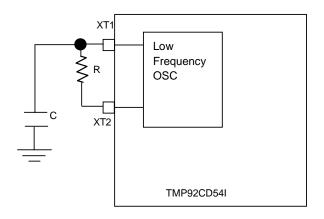

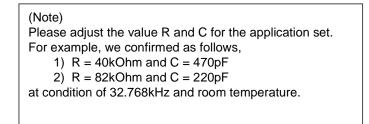

| (13)         | Timer for real-time clock (RTC)                                                                                                   |

|              | Can operate with only low frequency oscillator.                                                                                   |

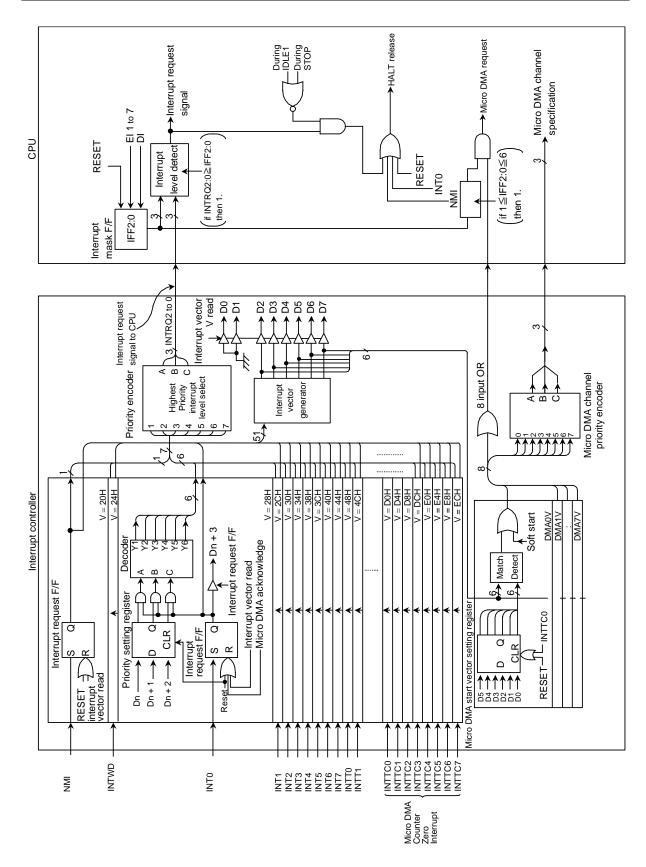

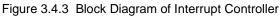

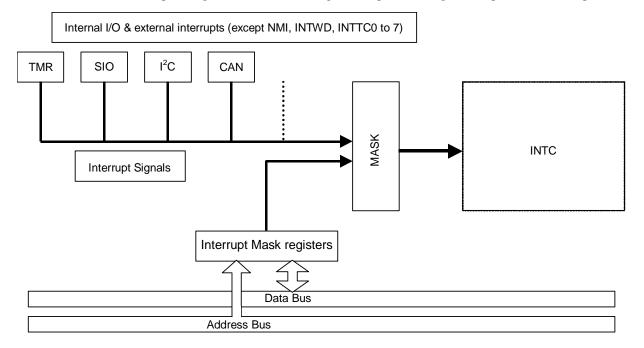

| (14)         | Interrupt controller (INTC) : 60 interrupt sources                                                                                |

|              | 9 interrupts from CPU                                                                                                             |

|              | 42 internal interrupt vectors                                                                                                     |

| <i>,</i> , , | 9 external interrupt vectors                                                                                                      |

|              | I/O Port : 68pins                                                                                                                 |

| (16)         | Standby mode                                                                                                                      |

|              | Four modes : IDLE3, IDLE2, IDLE1 and STOP                                                                                         |

|              | STOP mode can be released by 9 external inputs.                                                                                   |

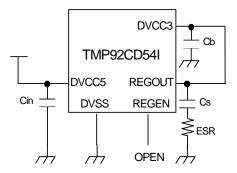

(17) Internal voltage detection flag (RAMSTB)

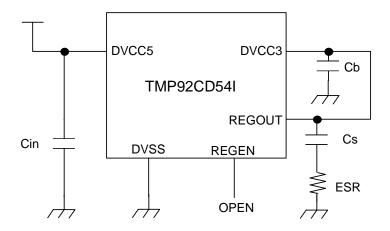

- Power supply voltage

VCC5 = 4.5V to 5.25V

VCC3 = 3.3V (VCC3 Connect to REGOUT; built-in voltage regulator.)

- (19) Operating temperature : -40 to 85 degree C

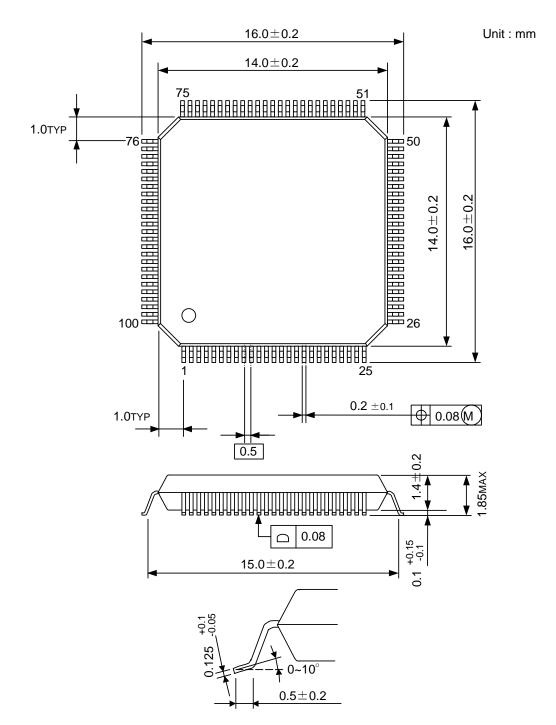

- (20) Package: P-LQFP100-1414-0.50F

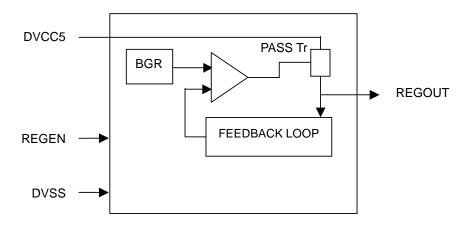

Figure 1 TMP92CD54I block diagram

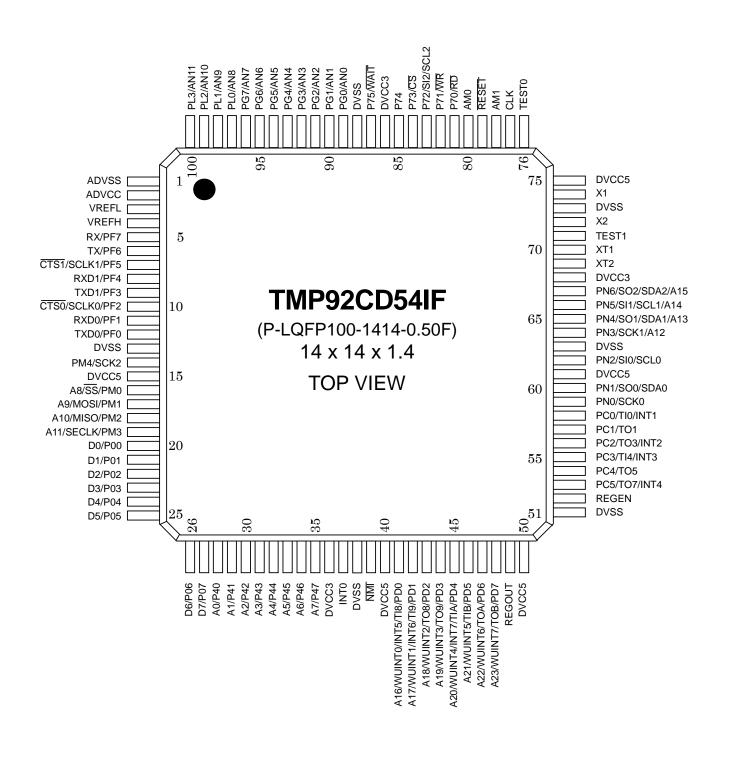

# 2. Pin Assignment and Functions

2.1 Pin Assignment

Figure 2.1 TMP92CD54I Pin Assignment

## 2.2 Pin names and functions

The following table shows the names and functions of the input/output pins.

| Pin name                            | Pin<br>number                     | Number of pins      | In/Out                          | Function                                                                                                                                                                                                                                                                                         |

|-------------------------------------|-----------------------------------|---------------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

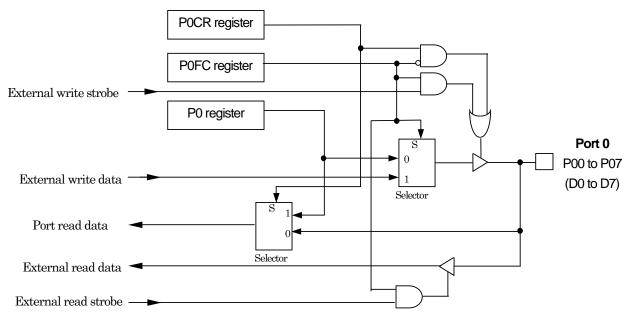

| P00P07<br>D0D7                      | 20 <sup>th</sup> 27 <sup>th</sup> | 8 (CMOS)<br>8 (TTL) | in/out<br>in/out                | Port 0: I/O port. Input or output specifiable in units of bits.<br>Data: Data bus 0 to 7.                                                                                                                                                                                                        |

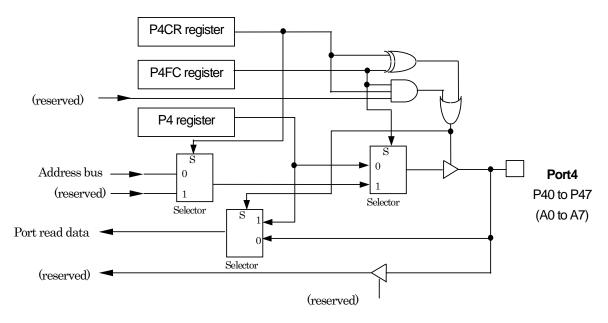

| P40P47<br>A0A7                      | 28 <sup>th</sup> 35 <sup>th</sup> | 8                   | in/out<br>out                   | Port4: I/O port. Input or output specifiable in units of bits.<br>Address: Address bus 0 to 7.                                                                                                                                                                                                   |

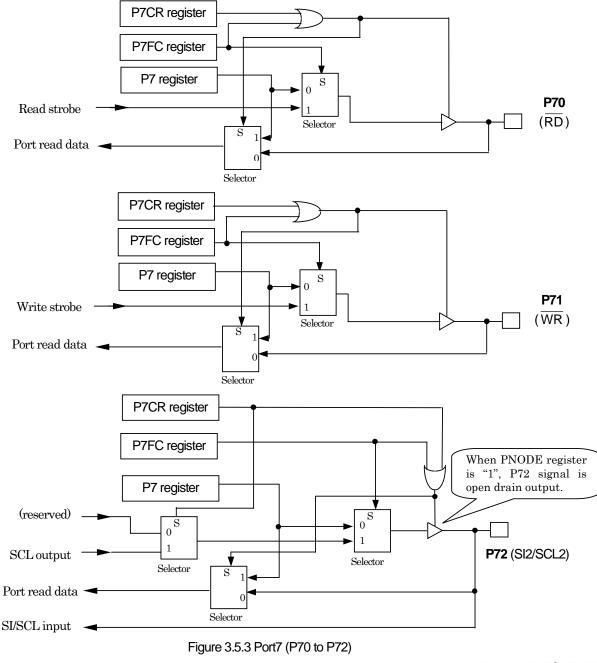

| $\frac{P70}{RD}$                    | 81 <sup>st</sup>                  | 1                   | in/out<br>out                   | Port 70: I/O port.<br>Read: Outputs strobe signal to read external memory.                                                                                                                                                                                                                       |

| $\frac{P71}{WR}$                    | 82 <sup>nd</sup>                  | 1                   | in/out<br>out                   | Port 71: I/O port.<br>Write: Output strobe signal to write external memory.                                                                                                                                                                                                                      |

| P72<br>SI2<br>SCL2                  | 83 <sup>rd</sup>                  | 1                   | in/out                          | Port 72: I/O port.<br>SBI channel 2: Input data at SIO mode<br>SBI channel 2: Clock input/output at I <sup>2</sup> C mode                                                                                                                                                                        |

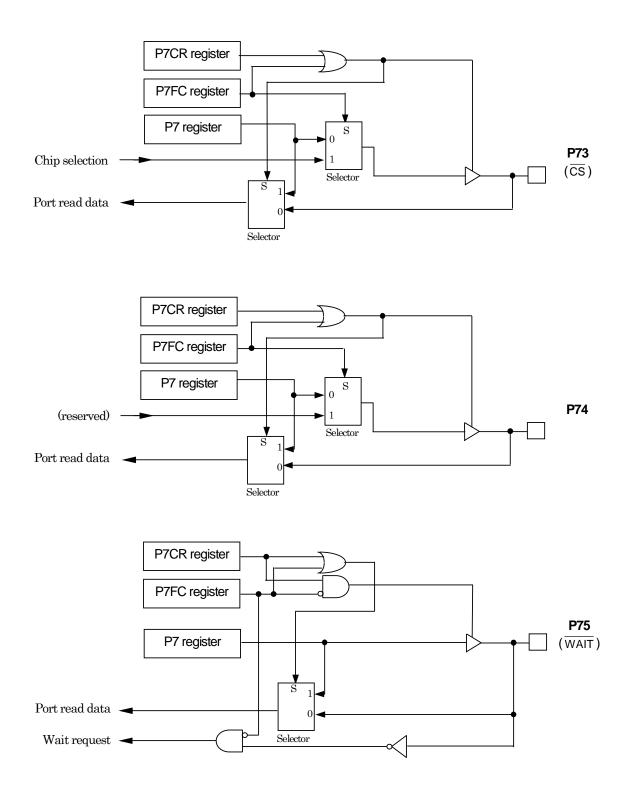

| $\frac{P73}{CS}$                    | 84 <sup>th</sup>                  | 1                   | in/out<br>out                   | Port 73: I/O port.<br>Chip select: Outputs "low" if address is within specified address area.                                                                                                                                                                                                    |

| P74                                 | $85^{\text{th}}$                  | 1                   | in/out                          | Port 74: I/O port.                                                                                                                                                                                                                                                                               |

| $\frac{P75}{WAIT}$                  | 87 <sup>th</sup>                  | 1                   | in/out<br>in                    | Port 75: I/O port.<br>Wait: Signal used to request CPU bus wait.                                                                                                                                                                                                                                 |

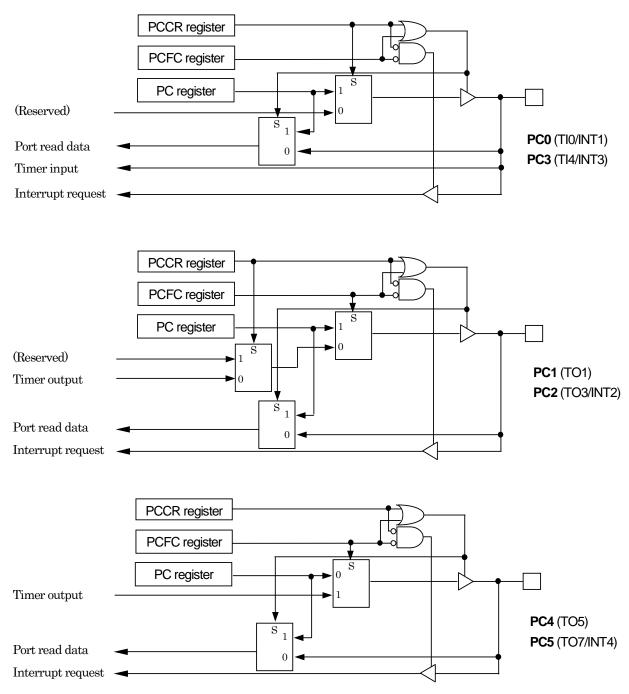

| PC0<br>TI0                          | $58^{\text{th}}$                  | 1                   | in/out<br>in                    | Port C0: I/O port.<br>Timer input 0: Input pin for timer 0.                                                                                                                                                                                                                                      |

| INT1<br>PC1<br>TO1                  | 57 <sup>th</sup>                  | 1                   | in<br>in/out<br>out             | Interrupt request pin 1: Rising-edge interrupt request pin                                                                                                                                                                                                                                       |

| PC2<br>TO3<br>INT2                  | $56^{\mathrm{th}}$                | 1                   | in/out<br>out<br>in             | Port C2: I/O port.<br>Timer output 3: Output pin for timer 3.<br>Interrupt request pin 2: Rising-edge interrupt request pin.                                                                                                                                                                     |

| PC3<br>TI4<br>INT3                  | $55^{\mathrm{th}}$                | 1                   | in/out<br>in<br>in              | Port C3: I/O port.<br>Timer input 4: Input pin for timer 4.<br>Interrupt request pin 3: Rising-edge interrupt request pin.                                                                                                                                                                       |

| PC4<br>TO5                          | $54^{\mathrm{th}}$                | 1                   | in/out<br>out                   | Port C4: I/O port.<br>Timer output 5: Output pin for timer 5.                                                                                                                                                                                                                                    |

| PC5<br>TO7<br>INT4                  | $53^{ m rd}$                      | 1                   | in/out<br>out<br>in             | Port C5: I/O port.<br>Timer output 7: Output pin for timer 7.<br>Interrupt request pin 4: Rising-edge interrupt request pin.                                                                                                                                                                     |

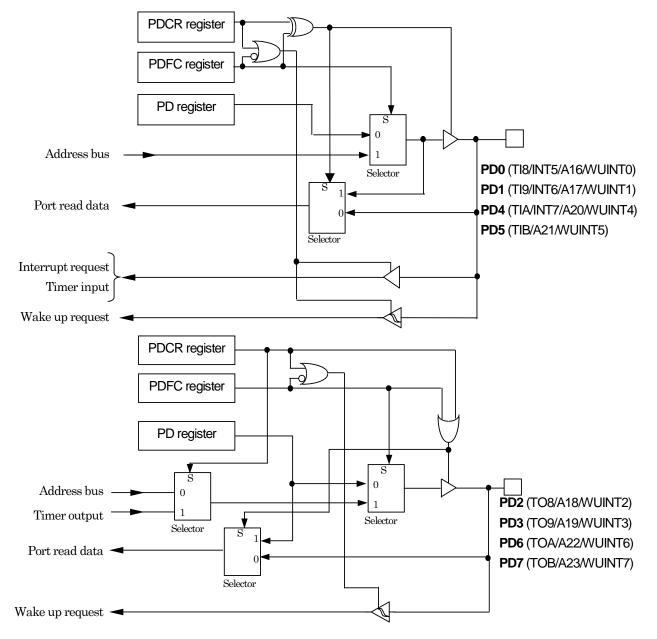

| PD0<br>TI8<br>INT5<br>A16<br>WUINT0 | 41 <sup>st</sup>                  | 1                   | in/out<br>in<br>in<br>out<br>in | Port D0: I/O port.<br>Timer input 8: Input pin for timer 8.<br>Interrupt request pin 5: Interrupt request pin with programmable rising/falling<br>edge.<br>Address: Address bus 16.<br>Wake up input 0: Wake up request pin with programmable rising, falling or both                            |

| PD1<br>TI9<br>INT6<br>A17<br>WUINT1 | 42 <sup>nd</sup>                  | 1                   | in/out<br>in<br>in<br>out<br>in | falling and rising edge.<br>Port D1: I/O port.<br>Timer input 9: Input pin for timer 9.<br>Interrupt request pin 6: Rising-edge interrupt request pin.<br>Address: Address bus 17.<br>Wake up input 1: Wake up request pin with programmable rising, falling or both<br>falling and rising edge. |

| PD2<br>TO8<br>A18<br>WUINT2         | 43 <sup>rd</sup>                  | 1                   | in/out<br>out<br>out<br>in      | Port D2: I/O port.<br>Timer output 8: Output pin for timer 8<br>Address: Address bus 18.<br>Wake up input 2: Wake up request pin with programmable rising, falling or both<br>falling and rising edge.                                                                                           |

| PD3<br>TO9<br>A19<br>WUINT3         | 44 <sup>th</sup>                  | 1                   | in/out<br>out<br>out<br>in      | Port D3: I/O port.<br>Timer output 9: Output pin for timer 9<br>Address: Address bus 19.<br>Wake up input 3: Wake up request pin with programmable rising, falling or both<br>falling and rising edge.                                                                                           |

| PD4<br>TA<br>TA<br>TA<br>NT7       infour<br>part Det D0 port.       Part D4 D0 port.       Part D4<br>Time Timer upper A1 flopt in for timer A       Part D4<br>with programmable rising fulling<br>edge.         A20       infour part D4 D0 port.       www.rr       www.rr       www.rr         A20       infour part D5 D0 port.       www.rr       www.rr       www.rr         A21       46 <sup>th</sup> 1       www.rr       www.rr       www.rr         A21       46 <sup>th</sup> 1       induct part D5 D0 port.       www.rr       www.rr         WUINT3       induct part D5 D0 port.       www.rr       www.rr       www.rr       www.rr         VUINT5       induct part D5 D0 port.       www.rr       www.rr       www.rr       www.rr         PD6       induct part D4 D0 D0 port.       www.rr       www.rr       www.rr       www.rr         VUINT5       induct part D4 D0 D0 port.       www.rr       www.rr       www.rr       www.rr         A22       47 <sup>th</sup> 1       with wrate up input 5 Walke up request pin with programmable rising fulling or both falling and rising edge.       induct part D1 D0 port.         TD50       1       induct part D5 D0 port.       www.rr       www.rr       www.rr         P10       1       induct part D4 D0 port.       WuiN7       www.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Pin name                   | Pin<br>number                     | Number<br>of pins | In/Out | Function                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------------|-------------------|--------|---------------------------------------------------------------------------------|

| TTA       in       Time: input A: Input pin for timer A       water         45 <sup>th</sup> 1       in       Interrupt request pin 7: Interrupt request pin with programmable rising, falling or both falling and rising deg.         200       water       water       water         WUINTS1       inform the part D5 100 port.       m         Address: Address bus 20.       water       water         WUINTS1       inform the part D5 100 port.       m         Address: Address bus 21.       water       water         WUINTS1       inform the part D5 100 port.       m         TDA       m       Wate up input 5: Walke up request pin with programmable rising, falling or both falling and rising edge.         WUINTS1       inform the port D5 100 port.       m       Water         WUINTS1       inform the port D5 100 port.       water       water         WUINTS1       inform the port D5 100 port.       water       water         WUINTS1       inform the port D5 100 port.       water       water         WUINTS1       inform the port D5 100 port.       water       water         WUNTS1       inform the port D5 100 port.       water       water         MUINTS1       inform the port D5 100 port.       water       water       water                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | PD4                        |                                   |                   | in/out | Port D4: I/O port.                                                              |

| $\Delta_{20}$ $45^{th}$ 1out $Address: Address has 20.$ $vare a$ WUINT4inWake up input 4: Wake up request pin with programmable rising, falling or both<br>falling and rising cdge. $vare a$ PD5 $10^{th}$ in $Part D5: 100 part.$ $vare a$ WUINT5in $Part D5: 100 part.$ $vare a$ WUINT5in $Part D5: 100 part.$ $vare a$ PD61out $Address: Address has 21.$ $vare a$ PD7inin $Part D5: 100 part.$ $vare a$ PD8in out $Part D5: 100 part.$ $vare a$ $vare a$ A22 $47^{th}.$ in out $Part D5: 100 part.$ $vare a$ PD7in out $Part D5: 100 part.$ $vare a$ $vare a$ PD7in out $Part D5: 100 part.$ $vare a$ $vare a$ PD7in out $Part D5: 100 part.$ $vare a$ $vare a$ PD8out $Part D5: 100 part.$ $vare a$ $vare a$ PD7in out $Part D5: 100 part.$ $vare a$ $vare a$ PD7in out $Part D5: 100 part.$ $vare a$ $vare a$ PD8 $10^{th}$ $vare a$ $vare a$ $vare a$ PD7in outPart D5: 100 part. $vare a$ PD8 $10^{th}$ $vare a$ $vare a$ PD7in outPart D5: 100 part. $vare a$ PD8 $10^{th}$ $vare a$ $vare a$ PD7in outPart D5: 100 part. $vare a$ PD8 $1^{th}$ $vare$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | TIA                        |                                   |                   | in     |                                                                                 |

| A20Address: Address bus 20.Address: Address bus 20.WUINT4inWeinert 4: Make up request pin with programmable rising, fulling or both<br>fulling and rising edge.PD5involution Pin D5 (O part.<br>Time rinput B: Input pin for timer R.WUR55WUINT5involution Pin D6 (O part.<br>Wullers: Address bus 21.WUR55PD6involution Pin D6 (O part.<br>Fulling and rising edge.WUR55PD6involution Pin D6 (O part.<br>Timer output 5. Wake up request pin with programmable rising, fulling or both<br>failing and rising edge.PD7involution Pin D6 (O part.<br>Timer output 4: O Output pin for timer A.<br>WUR55WUR55PD7out Address: Address bus 22.WUR55PD7involution Port D7 (D part.<br>Timer output 4: O Output pin for timer A.<br>wake up input 7: Wake up request pin with programmable rising, fulling or both<br>failing and rising edge.PD7involution Port D7 (D part.<br>Timer output 4: O Output pin for timer B.<br>wake up input 7: Wake up request pin with programmable rising, fulling or both<br>failing and rising edge.PD7involution Port D10 (D ort.<br>to the Prot D10 (D ort.PD712thinforth Port D10 (D ort.<br>to the Prot D10 (D ort.PD8inforth Port D10 (D ort.<br>to the Prot D10 (D ort.PD8inforth Port D10 (D ort.<br>to the Prot D10 (D ort.PD712thinforth Port P3: I/O port.SCLK010thinforth Port P3: I/O port.SCLK010thinforth Port P3: I/O port.RXD19thinforth Port P3: I/O port.RXD19thinforth Port P3: I/O port.                                                                                                                                                                                                                                                                                                                                                            | INT7                       |                                   |                   | in     | Interrupt request pin 7: Interrupt request pin with programmable rising/falling |

| WUNTY4         in         Wake up input 4: Wake up request pin with programmable rising, falling or both<br>falling and rising adge.           PD5         in         International and rising adge.         MANTS           A21         46 <sup>th</sup> 1         out         Address Address has 21.           WUNT5         in         Times input 8: lippet pin for timer 8.         MANTS           PD6         out         Theorating and rising adge.         MANTS           PD7         in         Totat         Totat         Marke up input 5: Wake up request pin with programmable rising, falling or both falling and rising adge.           PD7         in         Wake up input 5: Wake up request pin with programmable rising, falling or both falling and rising edge.           PD7         in         Wake up input 5: Wake up request pin with programmable rising, falling or both falling and rising edge.           PD7         in         Wake up input 7: Wake up request pin with programmable rising, falling or both falling and rising edge.           WUNT97         in         Wake up input 7: Wake up request pin with programmable rising, falling or both falling and rising edge.           PD7         in         Wake up input 7: Wake up request pin with programmable rising, falling or both falling and rising edge.           PD7         in         Into theore The 70 D port.           TD0         1         indout                                                                                                                                                                                                                                                                                                                                 |                            | $45^{\text{th}}$                  | 1                 |        | U UUUU                                                                          |

| PD5Inling and rising edge.PD5inTIBinA21if $0^{ch}$ A21inMUINT5inPD6inPD7inTOAAddress' Address bus 21.PD7inPD8in/outPO16in/outPO17in/outPO18in/outPO17in/outPO17in/outPO17in/outPO17in/outPO17in/outPO17in/outPO17in/outPO17in/outPO17in/outPO17in/outPO17in/outPO17in/outPO17in/outPO17in/outPO17in/outPO17in/outPO17in/outPO17in/outPO17in/outPO11in/outPO11in/outPO12in/outPO11in/outPO11in/outPO11in/outPO11in/outPO11in/outPO11in/outPO11in/outPO12in/outPO13in/outPO14in/outPO15in/outPO15in/outPO15in/outPO15in/outPO15in/outPO15in/outPO15in/outPO15in/outPO15in/out <td></td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            |                                   |                   |        |                                                                                 |

| P105<br>TIB<br>A21<br>A21infout<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | WUIN'I'4                   |                                   |                   | in     |                                                                                 |

| TIB<br>A21<br>A2146%<br>40%1in<br>number of the time input fb Input pin for timer B.WARTSWUINT5in<br>in<br>to de Address Address bas 21.Wake up input 5: Wake up request pin with programmable rising, falling or both<br>falling and rising edge.PD6<br>TOA<br>A22in/out<br>to attackers: Address bas 22.WARTSWUINT5out<br>to attackers: Address bas 22.WUINT6<br>TOB<br>A23in/out<br>to attackers: Address bas 22.PD7<br>TOB<br>A23in/out<br>to attackers: Address bas 23.PD7<br>TOB<br>A23in/out<br>to attackers: Address bas 23.PD7<br>TD8<br>TD9in/out<br>to attackers: Address bas 23.PD7<br>TD9in/out<br>to attackers: Address ba                                                                                                                                                                                                                                                                                                                                                                                                     |                            |                                   |                   | :      |                                                                                 |

| A21<br>WUNT54G*<br>a1out<br>Address bus 21. $J_{\rm address}$ bus 21.WUNT5<br>TOA<br>A22in Wake up input 5° Wake up request pin with programmable rising, falling or both<br>falling and rising edge.PD6<br>TOA<br>A2247*1out<br>outFore output A Output pin for timer A.<br>Make up input 6° Wake up request pin with programmable rising, falling or both<br>falling and rising edge.PD7<br>TOB<br>A23infout<br>to tD7:10 port.Infout D7:10 port.TOB<br>A23infout<br>to tD7:10 port.Infout Port D7:10 port.TD5<br>TOD<br>TODinfout<br>to tD7:10 port.Infout Port PD:10 port.TD6<br>TXD012*1infout<br>to tD7:10 port.TD70<br>TXD012*1infout<br>to tP:10 port.TXD0<br>TXD012*1infout<br>infout PF:10 port.TXD0<br>TXD010*1infout<br>infout PF:10 port.SCLK0<br>TCT5010*1infout<br>infout Pf:10 port.SCLK0<br>TCT5110*1infout<br>infout Pf:10 port.SCLK0<br>TCT5110*1infout Pf:10 port.SCLK1<br>TCT511infout<br>infout Pf:10 port.Serial interface channel 0: Clock input/output.<br>Serial interface channel 1: Clock input/output.TCT51<br>TCT51infout<br>infout Pf:10 port.Serial interface channel 1: Clock input/output.<br>Serial infort Pf:10 port.                                                                                                                                                                                                                                                                                                                                                                             |                            |                                   |                   |        |                                                                                 |

| WUINT5inWake up input 5: Wake up request pin with programmable rising, falling or both<br>falling and rising edge.PD6in/outPort D6: D0 port.<br>Tork A22Timer output A: Output pin for timer A.<br>WUINT6WUINT6in/outPort D6: D0 port.<br>WUINT7Wue programmable rising, falling or both<br>falling and rising edge.PD7in/outPort D7: D0 port.<br>outWue up request pin with programmable rising, falling or both<br>falling and rising edge.PD7in/outPort D7: D0 port.<br>outWue up request pin with programmable rising, falling or both<br>falling and rising edge.PT012 <sup>th</sup> in/outPort F0: D0 port.<br>outWue up request pin with programmable rising, falling or both<br>falling and rising edge.PT012 <sup>th</sup> in/outPort F0: D0 port.<br>TO port.Wue programmable rising in programmable rising |                            | 1Cth                              | 1                 |        |                                                                                 |

| falling and rising edge.Falling and rising edge.Falling and rising edge.PD6<br>TOA<br>A2247 <sup>th</sup> in/outPort D6 1/O port.A22<br>A2247 <sup>th</sup> 1outMUINT6inValke up input 6 Wake up request pin with programmable rising, falling or both<br>falling and rising edge.PD7<br>TOB<br>A23in/out P or D7 1/O port.TOB<br>A23in/out P or D7 1/O port.A2348 <sup>th</sup> 1VIINT7outAddress: Address bas 23.WUINT6in/out P or D7 1/O port.Address: Address bas 23.VUINT7outAddress: Address bas 23.VUINT7in/out P or D7 1/O port.TXD010 <sup>th</sup> 11 <sup>th</sup> in/out P or D7 1/O port.TXD010 <sup>th</sup> PF2in/out P or D7 1/O port.SCILK010 <sup>th</sup> 11 <sup>th</sup> in/out P or P3 1/O port.TXD1in/out P or F3 1/O port.TXD1in/out P or F6 F0 port.TXD1in/out Serial interface channel 1: Data ready to send. (Clear-to-send)PF5in/out P or F6 F0 port.TXin/out P or F6 F0 port.TXin/out P or F6 F0 port.TXin/out P or H0 iO port. </td <td></td> <td>40</td> <td>1</td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            | 40                                | 1                 |        |                                                                                 |

| PD6         indux         Port D6 100 port.         WUNT6           A22 $47^{h}$ 1         out         Timer output A: Output pin for timer A.         WUNT6           MUINT6         in         Wilk outping edge.         Wilk outping edge.         WUNT6         Image edge.           PD7         in         out         Timer output B: Output pin for timer B.         WUNT7         Image edge.           A23         48 <sup>a</sup> 1         out         Timer output B: Output pin for timer B.         WUNT7           A23         48 <sup>a</sup> 1         out         Address: Address bus 23.         WUNT7         Image edge.         Image edge.           P10         12 <sup>a</sup> 1         indout         Port FD: D0 port.         Twild be up input 7: Wake up request pin with programmable rising, falling or both falling and rising edge.           P10         11 <sup>a</sup> indout         Port FD: D0 port.         Twild be up input 7: Wake up request pin with programmable rising. falling or both falling and rising edge.           P10         1         indout         Port FD: D0 port.         To port.           RD0         1         indout         Port FD: D0 port.         To port.           GTS0         1         indout         Port FD: D0 port.         To port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | WOINTO                     |                                   |                   |        |                                                                                 |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | PD6                        |                                   |                   | in/out |                                                                                 |

| A22<br>WUINT647%1out<br>inAddress' Address bus 22<br>wake up input 6 Wake up request pin with programmable rising, falling or both<br>falling and rising edge.PD7<br>TOB<br>A2348%induitFor D7: IO port.<br>TW ake up input 7 Wake up request pin with programmable rising, falling or both<br>falling and rising edge.PF0<br>TD0<br>12%1infoutPort FF: IO port.<br>Wake up input 7. Wake up request pin with programmable rising, falling or both<br>falling and rising edge.PF0<br>TD012%1infoutPort FF: IO port.<br>TW ake up input 7. Wake up request pin with programmable rising, falling or both<br>falling and rising edge.PF0<br>TD01infoutPort FF: IO port.PT0<br>SCLK0<br>TD01infoutPort FF: IO port.SCLK0<br>TD101infoutPort FF: IO port.SCLK0<br>TXD11infoutPort FF: IO port.SCLK1<br>TTh11infoutPort FF: IO port.SCLK1<br>TTh11infout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                            |                                   |                   |        |                                                                                 |

| PD7<br>TOB<br>TOB<br>A23infout<br>infoutPort D7: I/O port.<br>Timer output B* Output pin for timer B.WANT<br>WANTA23<br>A2348 <sup>th</sup> 1outTimer output B* Output pin for timer B.WANTA23<br>A2348 <sup>th</sup> 1outAddress' Address bus 23.<br>Wake up input F* Wake up request pin with programmable rising, falling or both<br>falling and rising edge.PF0<br>TXD012 <sup>th</sup> 1in/outPort FV: I/O port.PT2<br>TXD011 <sup>th</sup> 1in/outPort FV: I/O port.SCLK0<br>CTS010 <sup>th</sup> 1in/outPort FV: I/O port.PF2<br>CTS010 <sup>th</sup> 1in/outPort FV: I/O port.SCLK0<br>TS010 <sup>th</sup> 1in/outPort FV: I/O port.PF3<br>SCLK1<br>CTS09 <sup>th</sup> 1in/outPort FV: I/O port.TXD15 <sup>th</sup> 1in/outPort FV: I/O port.SCLK1<br>CTS17 <sup>th</sup> 1in/outPort FV: I/O port.SCLK1<br>CTS11in/outPort FV: I/O port.SCLK26 <sup>th</sup> 1outCAN: Transmission data.PF51in/outPort FV: I/O port.SCLK2 <td>A22</td> <td><math>47^{\text{th}}</math></td> <td>1</td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | A22                        | $47^{\text{th}}$                  | 1                 |        |                                                                                 |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | WUINT6                     |                                   |                   | in     | Wake up input 6: Wake up request pin with programmable rising, falling or both  |

| TOB<br>A2348 <sup>th</sup> 1out<br>outTimer output B: Output pin for timer B.WMNTA2348 <sup>th</sup> 1out<br>outAddress: Address bus 23.WUNT7in1induity and rising edge.PF012 <sup>th</sup> 1induity out Fo: Uo port.TXD012 <sup>th</sup> 1induity out Fo: Uo port.PT111 <sup>th</sup> 1induity out Fo: Uo port.PP2induity out Fo: Uo port.Serial interface channel 0: Receive data.PP2induity output Fo: Fo: Uo port.Serial interface channel 0: Clock input/output.CTS5010 <sup>th</sup> 1induity output Fo: Uo port.SCLK010 <sup>th</sup> 1induity output Fo: Uo port.PF39 <sup>th</sup> 1induity output Fo: Uo port.RXD18 <sup>th</sup> 1induity output Fo: Uo port.RXD17 <sup>th</sup> 1induity output Fo: Uo port.RXD11ind                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                            |                                   |                   |        | falling and rising edge.                                                        |

| A23<br>WUINT748h1out<br>hAddress' Address bus 23. $\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | PD7                        |                                   |                   | in/out |                                                                                 |

| WUINT7inWake up input 7: Wake up request pin with programmable rising, falling or both<br>falling and rising edge.PF0 $12^{th}$ 1in/outSerial interface channel 0: Transmission data.PF1 $11^{th}$ 1in/outPort F1: I/O port.RXD0 $10^{th}$ 1in/outPort F2: I/O port.SCLK0 $10^{th}$ 1in/outPort F2: I/O port.CTS0 $10^{th}$ 1in/outPort F3: I/O port.SCLK1 $10^{th}$ 1in/outPort F3: I/O port.TXD1 $9^{th}$ 1in/outPort F3: I/O port.SCLK1 $7^{th}$ 1in/outPort G3: Input only port.RX </td <td></td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            |                                   |                   |        |                                                                                 |

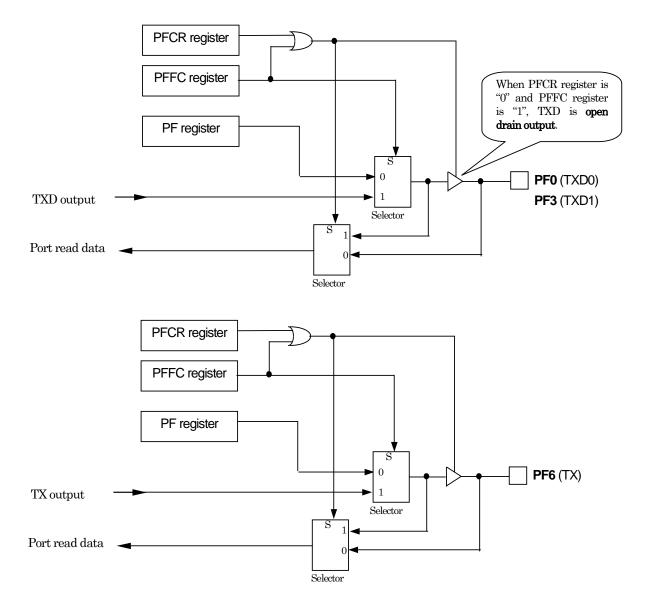

| PF0<br>TXD012 <sup>th</sup> 1in/out<br>in/outPort F0: I/O port.<br>Serial interface channel 0: Transmission data.PF1<br>RXD011 <sup>th</sup> 1in/out<br>inPort F1: I/O port.RXD010 <sup>th</sup> 1in/out<br>in/outPort F2: I/O port.SCLK0<br>CTS010 <sup>th</sup> 1in/out<br>in/outSerial interface channel 0: Clock input/output.CTS010 <sup>th</sup> 1in/out<br>in/outSerial interface channel 0: Data ready to send. (Clear-to-send)PF3<br>SD19 <sup>th</sup> 1in/out<br>serial interface channel 1: Transmission data.PF4<br>SCLK1<br>CTS18 <sup>th</sup> 1in/out<br>serial interface channel 1: Receive data.PF5<br>SCLK1<br>T7 <sup>th</sup> 1in/out<br>in/outPort F5: I/O port.SCLK1<br>T7 <sup>th</sup> 1in/out<br>in/outPort F6: I/O port.SCLK1<br>T7 <sup>th</sup> 1in/out<br>in/outPort F6: I/O port.CTS1<br>PF6<br>G6 <sup>th</sup> 1in/out<br>outPort F6: I/O port.TX<br>S7 <sup>th</sup> 1in/out<br>in/outPort F6: I/O port.TX<br>RX0.AN7<br>S9 <sup>th</sup> 1in/out<br>inPort F1: Do port.TX<br>RX0.AN7<br>S9 <sup>th</sup> 1in/out<br>inPort F1: Do port.TX<br>RX0.AN7<br>S9 <sup>th</sup> 1in/out<br>inPort F1: Do port.RX0.AN7<br>S9 <sup>th</sup> 1 <t< td=""><td></td><td><math>48^{\text{th}}</math></td><td>1</td><td></td><td></td></t<>                                                                                                                                                                                                                                                                                                                                  |                            | $48^{\text{th}}$                  | 1                 |        |                                                                                 |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | WUINT7                     |                                   |                   | in     |                                                                                 |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | DEO                        |                                   |                   | • • •  |                                                                                 |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -                          | $12^{\text{th}}$                  | 1                 |        |                                                                                 |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                            |                                   |                   |        |                                                                                 |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                            | 11 <sup>th</sup>                  | 1                 |        |                                                                                 |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                            |                                   |                   |        |                                                                                 |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                            | 1.0th                             | 1                 |        |                                                                                 |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                            | 1041                              | 1                 |        |                                                                                 |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                            |                                   |                   |        |                                                                                 |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                            | $9^{\text{th}}$                   | 1                 |        |                                                                                 |

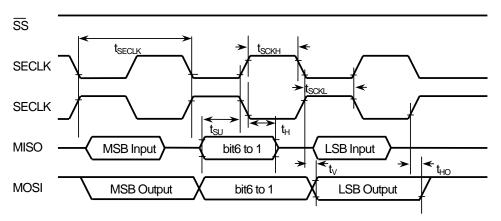

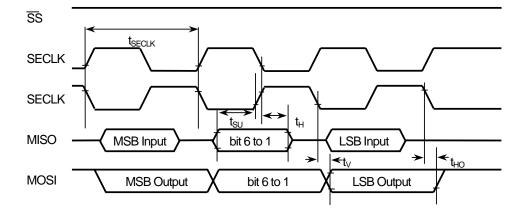

| RXD1 $S^{ab}$ 1inSerial interface channel 1: Receive data.PF5<br>SCLK1<br>CTS17 <sup>th</sup> 1in/outPort F5: I/O port.SCLK1<br>CTS17 <sup>th</sup> 1in/outSerial interface channel 1: Clock input/output.<br>inSerial interface channel 1: Data ready to send. (Clear-to-send)PF6<br>TX6 <sup>th</sup> 1in/outPort F6: I/O port.<br>outCAN: Transmission data.PF7<br>RX5 <sup>th</sup> 1in/outPort F7: I/O port.<br>inRX89 <sup>th</sup> 96 <sup>th</sup> 8inPort G: Inputronly port.<br>Analog input 0 to 7: AD converter input pins.PGO.PG7<br>RANDAN789 <sup>th</sup> 96 <sup>th</sup> 8inPort L0 to L3: Input-only port.<br>Analog input 0 to 7: AD converter input pins.PLO.PL3<br>ANSAN197 <sup>th</sup> 100 <sup>th</sup> 4inPort M0: I/O port.<br>in<br>SEI: Slave select input.<br>outAddress: Address bus 8.1in/outPort M1: I/O port.<br>in<br>outAddress: Address bus 8.1in/outPM1<br>MOSI17 <sup>th</sup> 1in/outNSO<br>MISO18 <sup>th</sup> 1in/outSEI: Master output, slave output.<br>outAddress: Address bus 9.PM2<br>MISO18 <sup>th</sup> 1in/outSECLK19 <sup>th</sup> <td< td=""><td></td><td></td><td></td><td></td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                            |                                   |                   |        |                                                                                 |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                            | 8 <sup>th</sup>                   | 1                 |        | -                                                                               |