# RENESAS

# Description

The 9FGV1005C is a member of the Renesas PhiClock<sup>™</sup> programmable clock generator family. The 9FGV1005C provides two copies of a single non-spread spectrum output frequency and one copy of the crystal reference input. Two select pins allow for hardware selection of the desired configuration, or two I<sup>2</sup>C bits allow easy software selection of the desired configuration. The user may configure any one of the four OTP configurations as the default when operating in I<sup>2</sup>C mode. Four unique I<sup>2</sup>C addresses are available, allowing easy I<sup>2</sup>C access to multiple components.

# **Typical Applications**

- HPC

- Storage

- 10G/25G Ethernet

- Fiber Optic Modules

- SSDs

- NVLink

### **Output Features**

- 1 integer output frequency per configuration

- 2 programmable output pairs plus 1 LVCMOS REF output

- 1MHz–325MHz LVDS or LP-HCSL outputs

- 1MHz–200MHz LVCMOS outputs

### **Features**

- 1.8V–3.3V operation

- Individual 1.8V–3.3V V<sub>DDO</sub> for each programmable output pair

- Supports HCSL, LVDS and LVCMOS I/O standards

- Supports LVPECL and CML logic with easy AC coupling see application note <u>AN-891</u> for alternate terminations

- HCSL utilizes Renesas' LP-HCSL technology for improved performance, lower power and higher integration:

- Programmable output impedance of  $85\Omega$  or  $100\Omega$

- On-board OTP supports up to 4 complete configurations

- Configuration selected via strapping pins or I<sup>2</sup>C

- < 100mW at 1.8V, < 200mW at 3.3V (LP-HCSL outputs running at 100MHz)

- 4 programmable I<sup>2</sup>C addresses: D0/D1, D2/D3, D4/D5, D6/D7 read/write

- Supported by Renesas <u>Timing Commander</u>™ software

- 3 × 3 mm 16-LGA with integrated crystal option (9FGV1005CQ)

## **Key Specifications**

- 259fs rms typical phase jitter outputs at 156.25MHz (12kHz– 20MHz)

- PCIe Gen1–5 compliant

# **PCIe Clocking Architectures**

- Common Clocked (CC)

- Independent Reference without spread spectrum (SRnS)

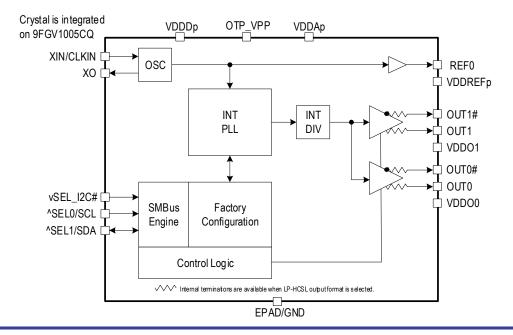

# Block Diagram

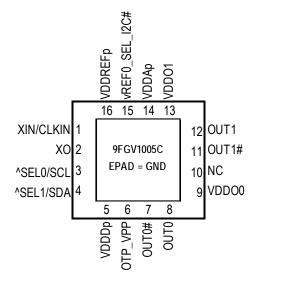

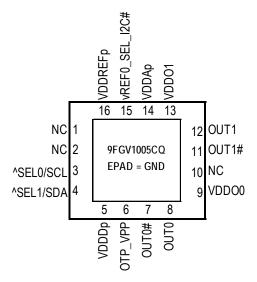

### **Pin Assignments**

Figure 1. Pin Assignments for 3 × 3 mm 16-LGA Package - Top View

16-LGA 3 x 3 mm, 0.5mm pitch ^ prefix indicates internal pull-up resistor v prefix indicates internal pull-down resistor

16-LGA 3 x 3 mm, 0.5mm pitch ^ prefix indicates internal pull-up resistor v prefix indicates internal pull-down resistor

### **Pin Descriptions**

#### Table 1. Pin Descriptions

| Number           | Name              | Туре           | Description                                                                                                                                                                                                                                                    |

|------------------|-------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 <sup>[a]</sup> | XIN/CLKIN         | Input          | Crystal input or reference clock input.                                                                                                                                                                                                                        |

| 2 <sup>[a]</sup> | XO                | Output         | Crystal output.                                                                                                                                                                                                                                                |

| 3                | ^SEL0/SCL         | Input          | Select pin for internal frequency configurations/I <sup>2</sup> C clock pin. Function is determined by state of SEL_I2C# upon power-up. This pin has an internal pull-up.                                                                                      |

| 4                | ^SEL1/SDA         | I/O            | Select pin for internal frequency configurations/I <sup>2</sup> C data pin. Function is determined by state of SEL_I2C# upon power-up. This pin has an internal pull-up.                                                                                       |

| 5                | V <sub>DDDp</sub> | Power          | Digital power. 1.8V to 3.3V. $V_{DDAp}$ and $V_{DDDp}$ should be connected to the same power supply.                                                                                                                                                           |

| 6                | OTP_VPP           | Power          | Voltage for programming OTP. During normal operation, this pin should be connected to the same power rail as $V_{\text{DDD}}$ .                                                                                                                                |

| 7                | OUT0#             | Output         | Complementary output clock 0.                                                                                                                                                                                                                                  |

| 8                | OUT0              | Output         | Output clock 0.                                                                                                                                                                                                                                                |

| 9                | V <sub>DDO0</sub> | Power          | Power supply for output 0.                                                                                                                                                                                                                                     |

| 10               | NC                | —              | No connect.                                                                                                                                                                                                                                                    |

| 11               | OUT1#             | Output         | Complementary output clock 1.                                                                                                                                                                                                                                  |

| 12               | OUT1              | Output         | Output clock 1.                                                                                                                                                                                                                                                |

| 13               | V <sub>DDO1</sub> | Power          | Power supply for output 1.                                                                                                                                                                                                                                     |

| 14               | V <sub>DDAp</sub> | Power          | Power supply for analog circuits. $V_{DDAp}$ and $V_{DDDp}$ should be connected to the same power supply. Programmable for nominal voltages of 1.8V, 2.5V or 3.3V.                                                                                             |

| 15               | vREF0_SEL_I2C#    | Latched<br>I/O | Latched input/LVCMOS output. At power-up, the state of this pin is latched to select the state of the I <sup>2</sup> C pins. After power-up, the pin acts as an LVCMOS reference output. This pin has an internal pull-down.<br>1 = SEL0/SEL1.<br>0 = SCL/SDA. |

| 16               | VDDREFp           | Power          | Power supply for REF outputs and the internal XO. Nominal voltages are 1.8V, 2.5V or 3.3V.                                                                                                                                                                     |

| 17               | EPAD              | GND            | Connect to ground.                                                                                                                                                                                                                                             |

Note: Unused outputs can be programmed off and left floating.  $V_{\text{DDREF}}$  and  $V_{\text{DD00}}$  have to be connected.

<sup>[a]</sup> These pins are 'No Connect' on 9FGV1005Q integrated quartz versions and should have no stubs. See *Pin Assignments* diagram for 9FGV1005Q.

### **Absolute Maximum Ratings**

The absolute maximum ratings are stress ratings only. Stresses greater than those listed below can cause permanent damage to the device. Functional operation of the 9FGV1005C at absolute maximum ratings is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

#### Table 2. Absolute Maximum Ratings

| Parameter                                                              | Rating                           |

|------------------------------------------------------------------------|----------------------------------|

| Supply Voltage, V <sub>DDA</sub> , V <sub>DDD</sub> , V <sub>DDO</sub> | 3.465V                           |

| Storage Temperature, T <sub>STG</sub>                                  | -65°C to 150°C                   |

| ESD Human Body Model                                                   | 2000V                            |

| Junction Temperature                                                   | 125°C                            |

| Inputs                                                                 |                                  |

| XIN/CLKIN                                                              | 0V to 1.2V voltage swing         |

| Other Inputs                                                           | -0.5V to V <sub>DDD</sub>        |

| Outputs                                                                |                                  |

| Outputs, V <sub>DDO</sub> (LVCMOS)                                     | -0.5V to V <sub>DDO</sub> + 0.5V |

| Outputs, IO (SDA)                                                      | 10mA                             |

# **Thermal Characteristics**

#### Table 3. Thermal Characteristics <sup>1</sup>

| Parameter                                             | Symbol               | Conditions                       | Package | Typical Values | Units | Notes |

|-------------------------------------------------------|----------------------|----------------------------------|---------|----------------|-------|-------|

|                                                       | $\theta_{\text{JC}}$ | Junction to case.                |         | 66             | °C/W  | 1     |

| Thermal Resistance<br>(devices with external crystal) | $\theta_{Jb}$        | Junction to base.                |         | 5.1            | °C/W  | 1     |

|                                                       | $\theta_{JA0}$       | Junction to air, still air.      | LTG16   | 63             | °C/W  | 1     |

|                                                       | $\theta_{JA1}$       | Junction to air, 1 m/s air flow. | LIGIO   | 56             | °C/W  | 1     |

|                                                       | $\theta_{JA3}$       | Junction to air, 3 m/s air flow. |         | 51             | °C/W  | 1     |

|                                                       | $\theta_{JA5}$       | Junction to air, 5 m/s air flow. |         | 49             | °C/W  | 1     |

|                                                       | $\theta_{\text{JC}}$ | Junction to case.                |         | 82.1           | °C/W  | 1     |

| Thermal Resistance                                    | $\theta_{Jb}$        | Junction to base.                |         | 42.3           | °C/W  | 1     |

| Q-series (devices with internal                       | $\theta_{JA0}$       | Junction to air, still air.      | LTG16   | 93.6           | °C/W  | 1     |

| crystal)                                              | $\theta_{JA1}$       | Junction to air, 1 m/s air flow. |         | 87.1           | °C/W  | 1     |

|                                                       | $\theta_{JA3}$       | Junction to air, 3 m/s air flow. |         | 83.3           | °C/W  | 1     |

<sup>1</sup> EPAD soldered to board.

# **Recommended Operating Conditions**

#### Table 4. Recommended Operating Conditions

| Symbol            | Parameter                                                                                                         | Minimum | Typical | Maximum | Units |

|-------------------|-------------------------------------------------------------------------------------------------------------------|---------|---------|---------|-------|

|                   | Power supply voltage for supporting 1.8V outputs.                                                                 | 1.71    | 1.8     | 1.89    | V     |

| V <sub>DDOx</sub> | Power supply voltage for supporting 2.5V outputs.                                                                 | 2.375   | 2.5     | 2.625   | V     |

|                   | Power supply voltage for supporting 3.3V outputs.                                                                 | 3.135   | 3.3     | 3.465   | V     |

| V <sub>DDD</sub>  | Power supply voltage for core logic functions.                                                                    | 1.71    |         | 3.465   | V     |

| V <sub>DDA</sub>  | Analog power supply voltage. Use filtered analog power supply if available.                                       | 1.71    |         | 3.465   | V     |

| Τ <sub>Α</sub>    | Operating temperature, ambient.                                                                                   | -40     |         | 85      | °C    |

| CL                | Maximum load capacitance (3.3V LVCMOS only).                                                                      |         |         | 15      | pF    |

| t <sub>PU</sub>   | Power-up time for all $V_{\text{DD}}\text{s}$ to reach minimum specified voltage (power ramps must be monotonic). | 0.05    |         | 5       | ms    |

### **Electrical Characteristics**

$V_{DDx}$  = 3.3V ±5%, 2.5V ±5%, 1.8V ±5%,  $T_A$  = -40°C to +85°C unless stated otherwise.

#### Table 5. Common Electrical Characteristics

| Parameter                                                              | Symbol                         | Conditions                     | Minimum                   | Typical | Maximum                  | Units | Notes |

|------------------------------------------------------------------------|--------------------------------|--------------------------------|---------------------------|---------|--------------------------|-------|-------|

| Innut Fragueney                                                        | £                              | Crystal input frequency.       | 8                         |         | 50                       | MHz   | 1     |

| Input Frequency                                                        | f <sub>IN</sub>                | CLKIN input frequency.         | 1                         |         | 240                      | MHz   | 5     |

|                                                                        | £                              | Differential clock output.     | 1                         |         | 325                      | MHz   |       |

| Output Frequency                                                       | f <sub>OUT</sub>               | Single-ended clock output.     | 1                         |         | 200                      | MHz   |       |

| VCO Frequency                                                          | f <sub>VCO</sub>               | VCO operating frequency range. | 2400                      | 2500    | 2600                     | MHz   |       |

| Loop Bandwidth                                                         | f <sub>BW</sub>                | Input frequency = 25MHz.       | 0.06                      |         | 0.9                      | MHz   |       |

| Input High Voltage                                                     | V <sub>IH</sub>                | SEL[1:0].                      | 0.7 x V <sub>DDD</sub>    |         | V <sub>DDD</sub> + 0.3   | V     |       |

| Input Low Voltage                                                      | V <sub>IL</sub>                | SEL[1:0].                      | GND - 0.3                 |         | 0.8                      | V     |       |

| Input High Voltage                                                     | V <sub>IH</sub>                | REF/SEL_I2C#.                  | 0.65 x V <sub>DDREF</sub> |         | V <sub>DDREF</sub> + 0.3 | V     |       |

| Input Low Voltage                                                      | V <sub>IL</sub>                | REF/SEL_I2C#.                  | -0.3                      |         | 0.4                      | V     |       |

| Input High Voltage                                                     | V <sub>IH</sub>                | XIN/CLKIN.                     | 0.8                       |         | 1.2                      | V     |       |

| Input Low Voltage                                                      | V <sub>IL</sub>                | XIN/CLKIN.                     | -0.3                      |         | 0.4                      | V     |       |

| Input Rise/Fall Time                                                   | T <sub>R</sub> /T <sub>F</sub> | SEL1/SDA, SEL0/SCL.            |                           |         | 300                      | ns    |       |

| Input Capacitance                                                      | C <sub>IN</sub>                | SEL[1:0].                      |                           | 3       | 7                        | pF    |       |

| Internal Pull-up Resistor                                              | R <sub>UP</sub>                | SEL[1:0] at 25°C.              | 200                       | 237     | 300                      | kΩ    |       |

| Internal Pull-down Resistor                                            | R <sub>DOWN</sub>              | REF/SEL_I2C#.                  | 200                       | 237     | 300                      | kΩ    |       |

| Programmable Capacitance<br>at XIN and XO (XIN in<br>parallel with XO) | CL                             | XIN/CLKIN, XO.                 | 0                         |         | 8                        | pF    |       |

#### Table 5. Common Electrical Characteristics (Cont.)

| Parameter         | Symbol                                                                                                                      | Conditions                                                                                                                                                                                       | Minimum | Typical | Maximum | Units  | Notes |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|---------|--------|-------|

| Input Duty Cycle  | t2                                                                                                                          | CLKIN, measured at V <sub>DDREF</sub> /2.                                                                                                                                                        | 40      | 50      | 60      | %      |       |

|                   |                                                                                                                             | LVCMOS, f <sub>OUT</sub> > 156.25MHz.                                                                                                                                                            | 40      | 50      | 60      | %      |       |

| Output Duty Cycle | t3                                                                                                                          | LVCMOS, f <sub>OUT</sub> ≤ 156.25MHz.                                                                                                                                                            | 45      | 50      | 55      | %      |       |

|                   |                                                                                                                             | LVDS, LP-HCSL outputs.                                                                                                                                                                           | 45      | 50.2    | 55      | %      |       |

|                   |                                                                                                                             | Cycle-to-cycle jitter (peak-to-peak), See<br>"Test Frequencies for Jitter Measurements<br>in Common Electrical Characteristics" for<br>configurations.                                           |         | 30      | 50      | ps     | 4     |

| Clock Jitter      | t6<br>5MHz integra<br>Frequencies<br>Common Ele<br>configuration<br>OUTx RMS<br>integration ra<br>"Test Freque<br>in Common | Reference clock RMS phase jitter (12kHz to<br>5MHz integration range). See "Test<br>Frequencies for Jitter Measurements in<br>Common Electrical Characteristics" for<br>configurations.          |         | 284     |         | fs rms | 4     |

|                   |                                                                                                                             | OUTx RMS phase jitter(12kHz to 20MHz<br>integration range) differential output. See<br>"Test Frequencies for Jitter Measurements<br>in Common Electrical Characteristics" for<br>configurations. |         | 259     |         | fs rms | 4     |

| Output Skew       | t7                                                                                                                          | Skew between the same frequencies, with outputs using the same driver format.                                                                                                                    |         | 37      | 50      | ps     |       |

| Look Timo         | t8a                                                                                                                         | PLL outputs valid from VDDs reaching 1.5V                                                                                                                                                        |         | 5       | 10      | ms     | 2,3   |

| Lock Time         | t8b                                                                                                                         | REF outputs valid from VDDs reaching 1.5V                                                                                                                                                        |         | 5       | 11      | ms     | 2,3   |

<sup>1</sup> Practical lower frequency is determined by loop filter settings.

<sup>2</sup> Includes loading the configuration bits from OTP to registers.

<sup>3</sup> Actual PLL lock time depends on the loop configuration.

<sup>4</sup> Actual jitter is configuration dependent. These values are representative of what the device can achieve.

<sup>5</sup> Input doubler off. Maximum input frequency with input doubler on is 160MHz.

#### Table 6. Test Frequencies for Jitter Measurements in Common Electrical Characteristics Table

$V_{DDx}$  = 3.3V ±5%, 2.5V ±5%, 1.8V ±5%, T<sub>A</sub> = -40°C to +85°C unless stated otherwise.

| Device      | XIN/CLKIN | OUT0   | OUT1 | Unit | Notes |

|-------------|-----------|--------|------|------|-------|

| 9FGV1005C   | 50        | 156.25 |      | MHz  | 1,3   |

| 9FGV1005CQ5 | 50        | 10     | 00   | MHz  | 2,3   |

<sup>1</sup> This configuration used for 12kHz–20MHz phase jitter measurement.

<sup>2</sup> This configuration used for PCIe filtered phase jitter measurements.

<sup>3</sup> Outputs configured as LP-HCSL or LVDS with REF output off, unless noted.

#### Table 7. LVCMOS Output Electrical Characteristics

| Parameter                            | Symbol            | Conditions                                                             | Minimum                | Typical | Maximum          | Units |

|--------------------------------------|-------------------|------------------------------------------------------------------------|------------------------|---------|------------------|-------|

|                                      |                   | $3.3V \pm 5\%$ , 20% to 80% of V <sub>DDO</sub> (output load = 4.7pF). | 2.5                    | 3.7     | 4.6              |       |

| Slew Rate                            | S <sub>R</sub>    | $2.5V \pm 5\%$ , 20% to 80% of V <sub>DDO</sub> (output load = 4.7pF). | 1.5                    | 2.4     | 4.6              | V/ns  |

|                                      |                   | $1.8V \pm 5\%$ , 20% to 80% of V <sub>DDO</sub> (output load = 4.7pF). | 0.8                    | 1.7     | 3.5              |       |

|                                      |                   | I <sub>OH</sub> = -15mA at 3.3V.                                       |                        |         |                  |       |

| Output High Voltage                  | V <sub>OH</sub>   | I <sub>OH</sub> = -12mA at 2.5V.                                       | 0.8 x V <sub>DDO</sub> | l .     | V <sub>DDO</sub> | V     |

|                                      |                   | I <sub>OH</sub> = -8mA at 1.8V.                                        |                        |         |                  |       |

|                                      |                   | I <sub>OL</sub> = 15mA at 3.3V.                                        |                        |         |                  |       |

| Output Low Voltage                   | V <sub>OL</sub>   | I <sub>OL</sub> = 12mA at 2.5V.                                        |                        | 0.22    | 0.4              | V     |

|                                      |                   | I <sub>OL</sub> = 8mA at 1.8V.                                         | -                      |         |                  |       |

| Output Leakage Current<br>(OUT[0:1]) | I <sub>OZDD</sub> | Programmable outputs, tri-state,<br>V <sub>DDO</sub> = 3.465V.         |                        | 0       | 5                | μA    |

| Output Leakage Current (REF)         | I <sub>OZDD</sub> | REF outputs, tri-state, V <sub>DDO</sub> = 3.465V.                     |                        | 0       | 5                | μA    |

| CMOS Output Driver Impedance         | R <sub>OUT</sub>  | T <sub>A</sub> = 25°C.                                                 |                        | 17      |                  | Ω     |

#### Table 8. LVDS Output Electrical Characteristics

| Parameter                                                                                       | Symbol              | Minimum | Typical | Maximum | Units |

|-------------------------------------------------------------------------------------------------|---------------------|---------|---------|---------|-------|

| Differential Output Voltage for the TRUE Binary State                                           | V <sub>OT</sub> (+) | 247     | 328     | 454     | mV    |

| Differential Output Voltage for the FALSE Binary State                                          | V <sub>OT</sub> (-) | -454    | -332    | -247    | mV    |

| Change in V <sub>OT</sub> between Complementary Output States                                   | $\Delta V_{OT}$     |         |         | 50      | mV    |

| Output Common Mode Voltage (Offset Voltage) at 3.3V +5% and 2.5V +5%                            | V <sub>OS</sub>     | 1.125   | 1.19    | 1.55    | V     |

| Output Common Mode Voltage (Offset Voltage) at 1.8V +5%                                         | V <sub>OS</sub>     | 0.8     | 0.86    | 0.95    | V     |

| Change in V <sub>OS</sub> between Complementary Output States                                   | $\Delta V_{OS}$     |         | 0       | 50      | mV    |

| Outputs Short Circuit Current, V <sub>OUT</sub> + or V <sub>OUT</sub> - = 0V or V <sub>DD</sub> | I <sub>OS</sub>     |         | 6       | 12      | mA    |

| Differential Outputs Short Circuit Current, V <sub>OUT</sub> + = V <sub>OUT</sub> -             | I <sub>OSD</sub>    |         | 3       | 12      | mA    |

| Rise Times Tested at 20% – 80%                                                                  | T <sub>R</sub>      |         | 257     | 400     | ps    |

| Fall Times Tested at 80% – 20%                                                                  | Τ <sub>F</sub>      |         | 287     | 400     | ps    |

#### Table 9. Low-Power (LP) Push-Pull HCSL Differential Outputs

| Parameter                     | Symbol                  | Conditions                                   | Minimum | Typical | Maximum | Units | Notes          |

|-------------------------------|-------------------------|----------------------------------------------|---------|---------|---------|-------|----------------|

| Slew Rate                     | T <sub>R/F</sub>        | Scope averaging on.                          | 1       | 2.5     | 4       | V/ns  | 2,3,16         |

| Slew Rate Matching            | $\Delta T_{R/F}$        |                                              |         | 9       | 20      | %     | 1,14,16        |

| Crossing Voltage (abs)        | V <sub>CROSS</sub>      | Scope averaging off.                         | 250     | 424     | 550     | mV    | 1,4,5,16       |

| Crossing Voltage (var)        | $\Delta V_{CROSS}$      | Scope averaging off.                         |         | 16      | 140     | mV    | 1,4,9,16       |

| Average Clock Period Accuracy | T <sub>PERIOD_AVG</sub> | Outputs set to 100MHz for PCIe applications. | -100    | 0       | +2600   | ppm   | 2,10,12,<br>13 |

| Absolute Period               | T <sub>PERIOD_ABS</sub> | Includes jitter and spread modulation.       | 9.949   | 10      | 10.101  | ns    | 2,6            |

| Absolute Maximum Voltage      | V <sub>MAX</sub>        | Includes 300mV of overshoot (Vovs).          | 660     | 808     | 1150    | mV    | 1,7,15         |

| Absolute Minimum Voltage      | V <sub>MIN</sub>        | Includes -300mV of undershoot (Vuds).        | -300    | -54     | 150     | mV    | 1,8,15         |

$V_{DDO}$  = 3.3V ±5%, 2.5V ±5%, 1.8V ±5%, T<sub>A</sub> = -40°C to +85°C unless stated otherwise.

<sup>1</sup> Measured from single-ended waveform.

<sup>2</sup> Measured from differential waveform.

<sup>3</sup> Measured from -150mV to +150mV on the differential waveform (derived from REFCLK+ minus REFCLK-). The signal must be monotonic through the measurement region for rise and fall time. The 300mV measurement window is centered on the differential zero crossing.

<sup>4</sup> Measured at crossing point where the instantaneous voltage value of the rising edge of REFCLK+ equals the falling edge of REFCLK-.

<sup>5</sup> Refers to the total variation from the lowest crossing point to the highest, regardless of which edge is crossing. Refers to all crossing points for this measurement.

<sup>6</sup> Defined as the absolute minimum or maximum instantaneous period. This includes cycle to cycle jitter, relative ppm tolerance, and spread spectrum modulation.

<sup>7</sup> Defined as the maximum instantaneous voltage including overshoot.

<sup>8</sup> Defined as the minimum instantaneous voltage including undershoot.

<sup>9</sup> Defined as the total variation of all crossing voltages of rising REFCLK+ and falling REFCLK-. This is the maximum allowed variance in V<sub>CROSS</sub> for any particular system.

<sup>10</sup> Refer to Section 8.6 of the PCI Express Base Specification, Revision 4.0 for information regarding PPM considerations.

<sup>11</sup> System board compliance measurements must use the test load. REFCLK+ and REFCLK- are to be measured at the load capacitors CL. Single ended probes must be used for measurements requiring single ended measurements. Either single ended probes with math or differential probe can be used for differential measurements. Test load C<sub>L</sub> = 2pF.

<sup>12</sup> PCIe Gen1 through Gen4 specify ±300ppm frequency tolerances. The PhiClock devices already meet the tighter ±100ppm frequency tolerances proposed for PCIe Gen5 and required by most servers.

<sup>13</sup> "ppm" refers to parts per million and is a DC absolute period accuracy specification. 1 ppm is 1/1,000,000th of 100.000000MHz exactly or 100Hz. For 100ppm, then we have an error budget of 100Hz/ppm × 100 ppm =10kHz. The period is to be measured with a frequency counter with measurement window set to 100ms or greater. The ±100 ppm applies to systems that do not employ spread spectrum clocking, or that use common clock source. For systems employing spread spectrum clocking, there is an additional 2,500 ppm nominal shift in maximum period resulting from the 0.5% down spread resulting in a maximum average period specification of +2,600 ppm for Common Clock architectures. Separate Reference Clock architectures may have a lower allowed spread percentage.

<sup>14</sup> Matching applies to rising edge rate for REFCLK+ and falling edge rate for REFCLK-. It is measured using a ±75mV window centered on the median cross point where REFCLK+ rising meets REFCLK- falling. The median cross point is used to calculate the voltage thresholds the oscilloscope is to use for the edge rate calculations. The rise edge rate of REFCLK+ should be compared to the fall edge rate of REFCLK-; the maximum allowed difference should not exceed 20% of the slowest edge rate.

<sup>15</sup> At default amplitude settings.

<sup>16</sup> Guaranteed by design and characterization.

#### Table 10. Filtered Phase Jitter Parameters - PCIe Common Clocked (CC) Architectures

T<sub>AMB</sub> = over the specified operating range. Supply Voltages per normal operation conditions; see Test Loads for loading conditions.

| Parameter            | Symbol                     | Conditions                                                                                          | Minimum | Typical | Maximum | Industry<br>Limits | Units       | Notes |

|----------------------|----------------------------|-----------------------------------------------------------------------------------------------------|---------|---------|---------|--------------------|-------------|-------|

| PCIe Phase<br>Jitter | t <sub>jphPCleG1-CC</sub>  | PCle Gen1.                                                                                          |         | 11      | 18      | 86                 | ps<br>(p-p) | 1,2,3 |

|                      | t <sub>jphPCleG2-CC</sub>  | PCIe Gen2 Low Band<br>10kHz < f < 1.5MHz<br>(PLL BW of 5–16MHz, 8–16MHz,<br>CDR = 5MHz).            |         | 0.1     | 0.14    | 3                  | ps<br>(rms) | 1,2   |

|                      |                            | PCIe Gen2 High Band<br>1.5MHz < f < Nyquist (50MHz)<br>(PLL BW of 5–16MHz, 8–16MHz,<br>CDR = 5MHz). |         | 1.1     | 1.6     | 3.1                | ps<br>(rms) | 1,2   |

|                      | t <sub>jphPCle</sub> G3-CC | PCIe Gen3<br>(PLL BW of 2–4MHz, 2–5MHz,<br>CDR = 10MHz).                                            |         | 0.27    | 0.37    | 1                  | ps<br>(rms) | 1,2   |

|                      | t <sub>jphPCle</sub> G4-CC | PCIe Gen4<br>(PLL BW of 2–4MHz, 2–5MHz,<br>CDR = 10MHz).                                            |         | 0.27    | 0.37    | 0.5                | ps<br>(rms) | 1,2   |

#### Table 11. Filtered Phase Jitter Parameters - PCIe Independent Reference (IR) Architectures

T<sub>AMB</sub> = over the specified operating range. Supply Voltages per normal operation conditions; see Test Loads for loading conditions.

| Parameter  | Symbol                      | Conditions                                    | Minimum | Typical | Maximum | Industry<br>Limits | Units       | Notes |

|------------|-----------------------------|-----------------------------------------------|---------|---------|---------|--------------------|-------------|-------|

| PCle Phase | tjphPCleG2-SRIS             | PCIe Gen2<br>(PLL BW of 16MHz, CDR = 5MHz).   |         | 1.1     | 1.34    | 2                  | ps<br>(rms) | 1,4,5 |

|            | t <sub>jphPCleG3-SRIS</sub> | PCIe Gen3<br>(PLL BW of 2–4MHz, CDR = 10MHz). |         | 0.28    | 0.39    | 0.7                | ps<br>(rms) | 1,4,5 |

Notes for Filtered Phase Jitter Parameters tables:

<sup>1</sup> Applies to all differential outputs at 100MHz, guaranteed by design and characterization.

<sup>2</sup> Based on PCIe Base Specification Rev4.0 version 0.7draft. See http://www.pcisig.com for latest specifications.

<sup>3</sup> Sample size of at least 100K cycles. This figure extrapolates to 108ps pk-pk at 1M cycles for a BER of 1<sup>-12</sup>.

<sup>4</sup> IR is the new name for Separate Reference Independent Spread (SRIS) and Separate Reference no Spread (SRNS) PCIe clock architectures.

<sup>5</sup> According to the PCIe Base Specification Rev4.0 version 0.7 draft, the jitter transfer functions and corresponding jitter limits are not defined for the IR clock architecture. Widely accepted industry limits using widely accepted industry filters are used to populate this table. There are no accepted filters or limits for IR clock architectures at PCIe Gen1 or Gen4 data rates.

#### Table 12. Current Consumption

| Parameter                                           | Symbol               | Conditions                                          | Minimum | Typical | Maximum | Units | Notes |

|-----------------------------------------------------|----------------------|-----------------------------------------------------|---------|---------|---------|-------|-------|

| V <sub>DDREF</sub> Supply Current                   | IDDREF               | 50MHz REFCLK.                                       |         | 5       | 8       | mA    |       |

| Core Supply Current                                 | IDDCORE              | 2500MHz VCO, 50MHz REFCLK.                          |         | 24      | 31      | mA    | 3     |

|                                                     |                      | LVDS, 325MHz.                                       |         | 22      | 28      | mA    | 2     |

| Output Buffer Supply                                |                      | LP-HCSL, 100MHz.                                    |         | 17      | 24      | mA    | 2     |

| Current (V <sub>DDO1</sub> )                        | - I <sub>DDO</sub> x | LVCMOS, 50MHz.                                      |         | 15      | 20      | mA    | 1,2   |

|                                                     |                      | LVCMOS, 200MHz.                                     |         | 25      | 40      | mA    | 1,2   |

|                                                     |                      | LVDS, 325MHz.                                       |         | 8       | 12      | mA    | 2     |

| Output Buffer Supply<br>Current (V <sub>DDO0)</sub> |                      | LP-HCSL, 100MHz                                     |         | 6       | 10      | mA    | 2     |

|                                                     |                      | LVCMOS, 50MHz.                                      |         | 4       | 7       | mA    | 1,2   |

|                                                     |                      | LVCMOS, 200MHz.                                     |         | 13      | 26      | mA    | 1,2   |

| Total Power Down Current                            |                      | Programmable outputs in HCSL mode, B37[6,0] = 0.    |         | 7       | 10      | mA    | 2     |

|                                                     | I <sub>DDPD</sub>    | Programmable outputs in LVDS mode, B37[6,0] = 0.    |         | 16      | 21      | mA    | 2     |

|                                                     |                      | Programmable outputs in LVCMOS1 mode, B37[6,0] = 0. |         | 5       | 7       | mA    | 2     |

$V_{DDO}$  = 3.3V ±5%, 2.5V ±5%, 1.8V ±5%,  $T_A$  = -40°C to +85°C unless stated otherwise.

<sup>1</sup> Single CMOS driver active for each output pair.

<sup>2</sup> See Test Loads for details.

$^{3}$  I<sub>DDCORE</sub> = I<sub>DDA</sub>+ I<sub>DDD</sub>.

# I<sup>2</sup>C Bus Characteristics

### Table 13. I<sup>2</sup>C Bus DC Characteristics

| Parameter             | Symbol           | Conditions             | Minimum                 | Typical | Maximum                | Units |

|-----------------------|------------------|------------------------|-------------------------|---------|------------------------|-------|

| Input High Level      | V <sub>IH</sub>  |                        | 0.7 x V <sub>DDD</sub>  |         |                        | V     |

| Input Low Level       | V <sub>IL</sub>  |                        |                         |         | 0.3 x V <sub>DDD</sub> | V     |

| Hysteresis of Inputs  | V <sub>HYS</sub> |                        | 0.05 x V <sub>DDD</sub> |         |                        | V     |

| Input Leakage Current | I <sub>IN</sub>  |                        | -1                      |         | 30                     | μA    |

| Output Low Voltage    | V <sub>OL</sub>  | I <sub>OL</sub> = 3mA. |                         |         | 0.4                    | V     |

### Table 14. I<sup>2</sup>C Bus AC Characteristics

| Parameter                            | Symbol                | Conditions | Minimum                   | Typical | Maximum | Units |

|--------------------------------------|-----------------------|------------|---------------------------|---------|---------|-------|

| Serial Clock Frequency (SCL)         | F <sub>SCLK</sub>     |            | 10                        |         | 400     | kHz   |

| Bus free time between STOP and START | t <sub>BUF</sub>      |            | 1.3                       |         |         | μs    |

| Setup Time, START                    | t <sub>SU:START</sub> |            | 0.6                       |         |         | μs    |

| Hold Time, START                     | t <sub>HD:START</sub> |            | 0.6                       |         |         | μs    |

| Setup Time, Data Input (SDA)         | t <sub>SU:DATA</sub>  |            | 0.1                       |         |         | μs    |

| Hold Time, Data Input (SDA) 1        | t <sub>HD:DATA</sub>  |            | 0                         |         |         | μs    |

| Output Data Valid from Clock         | t <sub>OVD</sub>      |            |                           |         | 0.9     | μs    |

| Capacitive Load for Each Bus Line    | CB                    |            |                           |         | 400     | pF    |

| Rise Time, Data and Clock (SDA, SCL) | t <sub>R</sub>        |            | 20 + 0.1 x C <sub>B</sub> |         | 300     | ns    |

| Fall Time, Data and Clock (SDA, SCL) | t <sub>F</sub>        |            | 20 + 0.1 x C <sub>B</sub> |         | 300     | ns    |

| High Time, Clock (SCL)               | t <sub>HIGH</sub>     |            | 0.6                       |         |         | μs    |

| Low Time, Clock (SCL)                | t <sub>LOW</sub>      |            | 1.3                       |         |         | μs    |

| Setup Time, STOP                     | t <sub>SU:STOP</sub>  |            | 0.6                       |         |         | μs    |

Note: A device must internally provide a hold time of at least 300ns for the SDA signal (referred to the V<sub>IH(MIN)</sub> of the SCL signal) to bridge the undefined region of the falling edge of SCL.

### **Crystal Characteristics**

| Parameter                                                         | Value       | Units       |

|-------------------------------------------------------------------|-------------|-------------|

| Frequency                                                         | 8–50        | MHz         |

| Resonance Mode                                                    | Fundamental | —           |

| Frequency Tolerance at 25°C                                       | ±20         | ppm maximum |

| Frequency Stability, REF at 25°C Over Operating Temperature Range | ±20         | ppm maximum |

| Temperature Range (commercial)                                    | 0–70        | ٥°          |

| Temperature Range (industrial)                                    | -40–85      | 0°          |

| Equivalent Series Resistance (ESR)                                | 50          | Ω maximum   |

| Shunt Capacitance (C <sub>O</sub> )                               | 7           | pF maximum  |

| Load Capacitance (C <sub>L</sub> )                                | 8           | pF maximum  |

| Drive Level                                                       | 0.1         | mW maximum  |

| Aging per year                                                    | ±5          | ppm maximum |

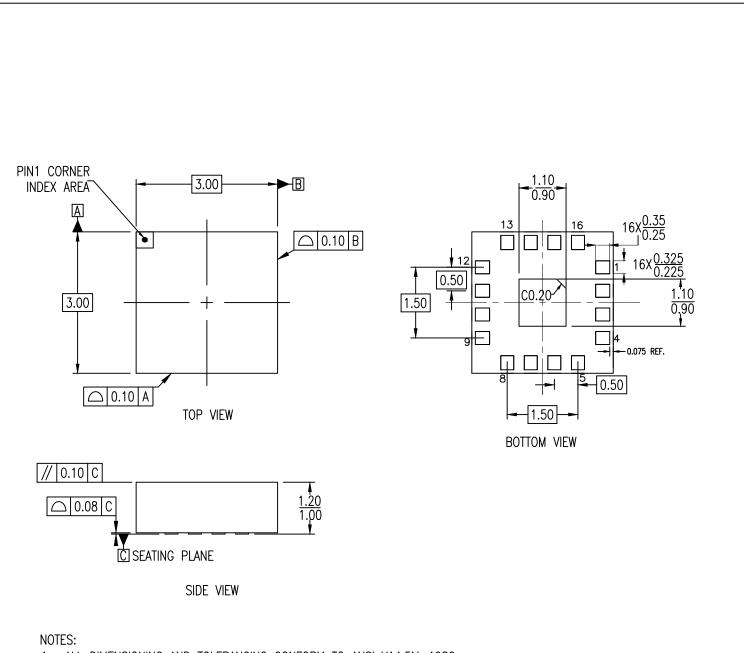

# Package Outline Drawings

The package outline drawings are appended at the end of this document and are accessible from the link below. The package information is the most current data available.

www.idt.com/us/en/document/psc/16-Iga-package-outline-drawing-30-x-30-x-110-mm-body-05mm-pitch-Itg16p1

### **Marking Diagrams**

|       | 5Cxxx<br>YWW\$<br>XXX |

|-------|-----------------------|

| ullet |                       |

- Line 1: truncated part number

- "YWW" denotes the last digits of the year and week the part was assembled.

- "\$" denotes mark code.

- "XXX" denotes lot number.

# **Ordering Information**

| Orderable Part Number | Package                      | Carrier Type | Temperature  | Description            |

|-----------------------|------------------------------|--------------|--------------|------------------------|

| 9FGV1005CnnnLTGI      | 3 × 3 mm, 0.5mm pitch 16-LGA | Tray         | -40 to +85°C | External Crystal       |

| 9FGV1005CnnnLTGI8     | 3 × 3 mm, 0.5mm pitch 16-LGA | Reel         | -40 to +85°C | External Crystal       |

| 9FGV1005CQ5aaLTGI     | 3 × 3 mm, 0.5mm pitch 16-LGA | Tray         | -40 to +85°C | Internal 50MHz Crystal |

| 9FGV1005CQ5aaLTGI8    | 3 × 3 mm, 0.5mm pitch 16-LGA | Reel         | -40 to +85°C | Internal 50MHz Crystal |

"G" indicates RoHS 6.6 compliance.

"nnn" are decimal digits indicating a specific configuration.

"aa" are alphanumeric digits indicating a specific configuration.

"Q5" indicates 50MHz internal crystal.

### **Revision History**

| Revision Date     | Description of Change                                                                      |  |  |

|-------------------|--------------------------------------------------------------------------------------------|--|--|

| February 14, 2020 | pdated Lock Time in Common Electri9cal Characteristics table.<br>loved datasheet to Final. |  |  |

| January 22, 2020  | <ul><li>Updated marking diagram.</li><li>Updated datasheet to latest template.</li></ul>   |  |  |

| December 20, 2019 | Initial release.                                                                           |  |  |

# RENESAS

## 16-LGA Package Outline Drawing

3.0 x 3.0 x 1.10 mm Body, 0.5mm Pitch LTG16P1, PSC-4651-01, Rev 02, Page 1

- 1. ALL DIMENSIONING AND TOLERANCING CONFORM TO ANSI Y14.5M-1982.

- 2. ALL DIMENSIONS ARE IN MILLIMETERS.

# RENESAS

# 16-LGA Package Outline Drawing

3.0 x 3.0 x 1.10 mm Body, 0.5mm Pitch LTG16P1, PSC-4651-01, Rev 02, Page 2

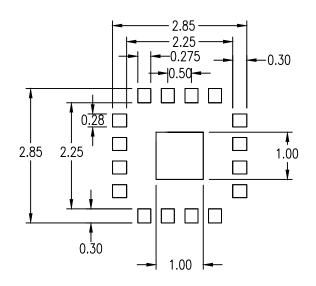

#### RECOMMENDED LAND PATTERN DIMENSION

NOTES:

- 1. ALL DIMENSION ARE IN mm. ANGLES IN DEGREES.

- 2. TOP DOWN VIEW. AS VIEWED ON PCB.

- 3. LAND PATTERN RECOMMENDATION PER IPC-7351B GENERIC REQUIREMENT FOR SURFACE MOUNT DESIGN AND LAND PATTERN.

|               | Package Revision History         |                                   |  |  |  |

|---------------|----------------------------------|-----------------------------------|--|--|--|

| Date Created  | Date Created Rev No. Description |                                   |  |  |  |

| Nov 6, 2017   | Rev 02                           | Modify Solder Mask & Epad Chamfer |  |  |  |

| Sept 29, 2017 | Rev 01                           | Modify Land Pattern               |  |  |  |

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Rev.1.0 Mar 2020)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: www.renesas.com/contact/