# onsemi

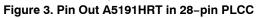

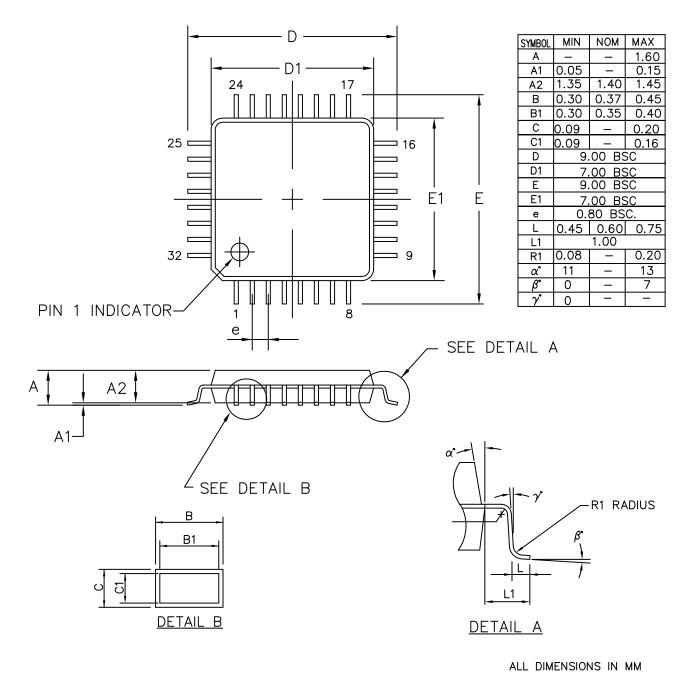

LQFP-32

L SUFFIX

## HART Modem A5191HRT

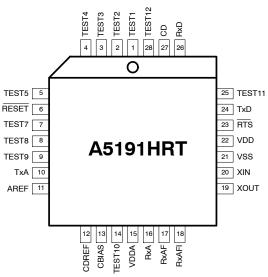

PLCC-28

**P SUFFIX**

Description

The A5191HRT is a single-chip, CMOS modem for use in highway addressable remote transducer (HART) field instruments and masters. The modem and a few external passive components provide all of the functions needed to satisfy HART physical layer requirements including modulation, demodulation, receive filtering, carrier detect, and transmit-signal shaping.

The A5191HRT uses phase continuous frequency shift keying (FSK) at 1200 bits per second. To conserve power the receive circuits are disabled during transmit operations and vice versa. This provides the half-duplex operation used in HART communications.

#### Features

- Single-chip, Half-duplex 1200 Bits per Second FSK Modem

- Bell 202 Shift Frequencies of 1200 Hz and 2200 Hz

- 3.0 V 5.5 V Power Supply

- Transmit-signal Wave Shaping

- Receive Band-pass Filter

- Low Power: Optimal for Intrinsically Safe Applications

- Compatible with 3.3 V or 5 V Microcontroller

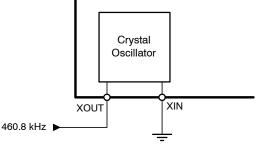

- Internal Oscillator Requires 460.8 kHz Crystal or Ceramic Resonator

- Meets HART Physical Layer Requirements

- Industrial Temperature Range of -40°C to +85°C

- Available in 28-pin PLCC, 32-pin QFN and 32-pin LQFP Packages

- These are Pb-Free Devices

#### Applications

- HART Multiplexers

- HART Modem Interfaces

- 4 20 mA Loop Powered Transmitters

CASE 776AA CASE 488AM CASE 561AB MARKING DIAGRAMS (Top Views)

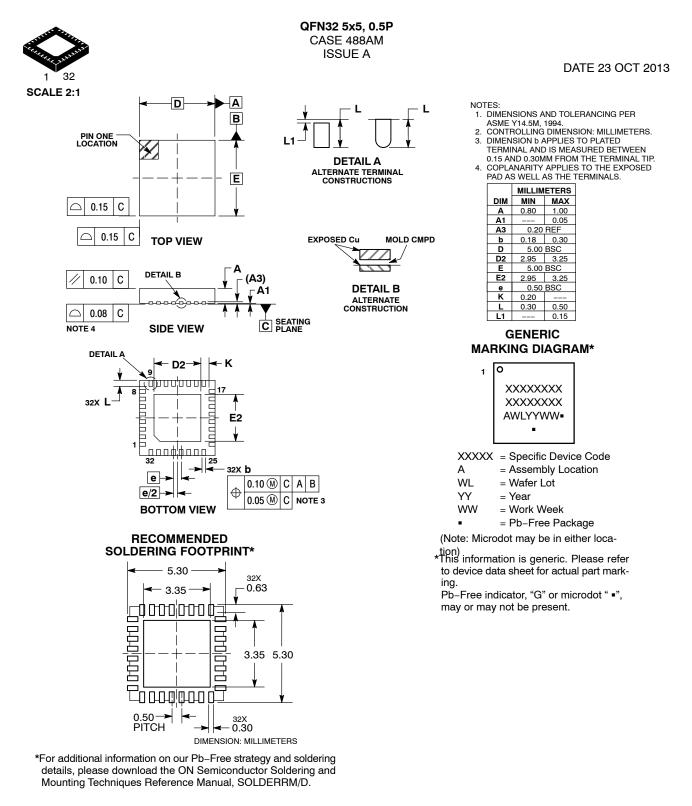

QFN-32 N SUFFIX

A5191HRTxx = Specific Device Code

- = P (PLCC), L (LQFP) or N (QFN)

- = Assembly Location

- WL = Wafer Lot

- YY = Year

XX

А

- WW = Work Week

- G or = Pb-Free Package

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 11 of this data sheet.

NOTE: Some of the devices on this data sheet have been **DISCONTINUED**. Please refer to the table on page 11.

1

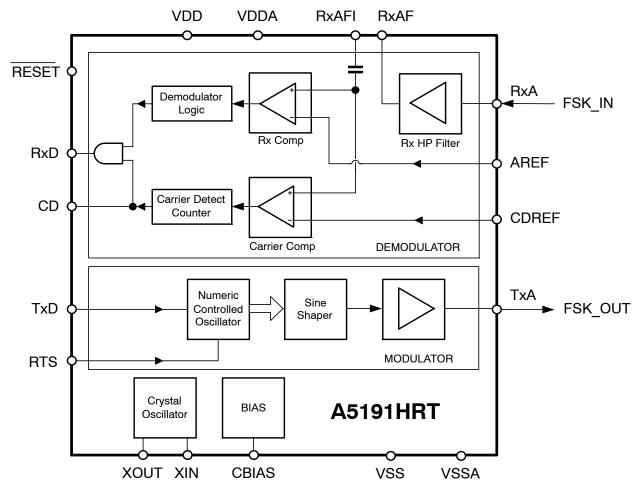

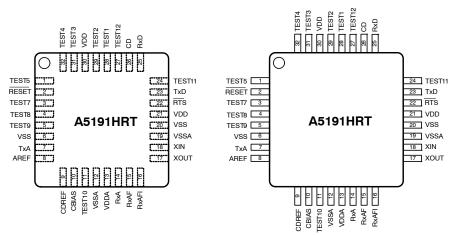

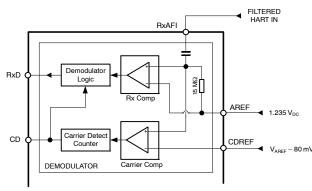

#### **BLOCK DIAGRAM**

Figure 1. Block Diagram A5191HRT

#### **ELECTRICAL SPECIFICATIONS**

#### Table 1. ABSOLUTE MAXIMUM RATINGS (Notes 1 and 2)

| Symbol                             | Parameter            | Min  | Max       | Units |

|------------------------------------|----------------------|------|-----------|-------|

| T <sub>A</sub>                     | Ambient              | -40  | +85       | °C    |

| Τ <sub>S</sub>                     | Storage Temperature  | -55  | +150      | °C    |

| TJ                                 | Junction Temperature | -40  | +85       | °C    |

| V <sub>DD</sub>                    | Supply Voltage       | -0.3 | 6.0       | V     |

| V <sub>IN</sub> , V <sub>OUT</sub> | DC Input, Output     | -0.3 | VDD + 0.3 | V     |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. CMOS devices are damaged by high-energy electrostatic discharge. Devices must be stored in conductive foam or with all pins shunted. Precautions should be taken to avoid application of voltages higher than the maximum rating. Stresses above absolute maximum ratings may result in damage to the device.

2. Remove power before insertion or removal of this device.

| Symbol                        | Parameter                                                      | V <sub>DD</sub> | Min                   | Тур              | Max                   | Units          |

|-------------------------------|----------------------------------------------------------------|-----------------|-----------------------|------------------|-----------------------|----------------|

| V <sub>IL</sub>               | Input Voltage, Low                                             | 3.0 – 5.5 V     |                       |                  | 0.3 * V <sub>DD</sub> | V              |

| VIH                           | Input Voltage, High                                            | 3.0 – 5.5 V     | 0.7 * V <sub>DD</sub> |                  |                       | V              |

| V <sub>OL</sub>               | Output Voltage, Low (I <sub>OL</sub> = 0.67 mA)                | 3.0 – 5.5 V     |                       |                  | 0.4                   | V              |

| V <sub>OH</sub>               | Output Voltage, High (I <sub>OH</sub> = -0.67 mA)              | 3.0 – 5.5 V     | 2.4                   |                  |                       | V              |

| C <sub>IN</sub>               | Input Capacitance of:<br>Analog Input<br>RXA<br>Digital Input  |                 |                       | 2.9<br>25<br>3.5 |                       | pF<br>pF<br>pF |

| $I_{IL}/I_{IH}$               | Input Leakage Current                                          |                 |                       |                  | ±500                  | nA             |

| I <sub>OLL</sub>              | Output Leakage Current                                         |                 |                       |                  | ±10                   | μΑ             |

| I <sub>DDA</sub>              | Power Supply Current (RBIAS = 500 k $\Omega$ , AREF = 1.235 V) | 3.3 V<br>5.0 V  | 150<br>150            | 330<br>300       | 450<br>600            | μΑ<br>μΑ       |

| I <sub>DDD</sub>              | Dynamic Digital Current                                        | 5.0 V           | 25                    |                  | 200                   | μΑ             |

| A <sub>REF</sub>              | Analog Reference                                               | 3.3 V<br>5.0 V  | 1.2                   | 1.235<br>2.5     | 2.6                   | V<br>V         |

| CD <sub>REF</sub><br>(Note 3) | Carrier Detect Reference (AREF - 0.08 V)                       | 3.3 V<br>5.0 V  |                       | 1.15<br>2.42     |                       | V              |

| C <sub>BIAS</sub>             | Comparator Bias Current<br>(RBIAS = 500 kΩ, AREF = 1.235 V)    |                 |                       | 2.5              |                       | μΑ             |

#### Table 2. DC CHARACTERISTICS (V<sub>DD</sub> = 3.0 V to 5.5 V, V<sub>SS</sub> = 0 V, T<sub>A</sub> = $-40^{\circ}$ C to $+85^{\circ}$ C)

3. The HART specification requires carrier detect (CD) to be active between 80 and 120 mVp-p. Setting CDREF at AREF – 0.08 VDC will set the carrier detect to a nominal 100 mVp-p.

| Pin Name | Description                                                                                                                                                                                        | Min          | Тур                                     | Max                    | Units                              |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------------------------------|------------------------|------------------------------------|

| RxA      | Receive analog input<br>Leakage current<br>Frequency – mark (logic 1)<br>Frequency – space (logic 0)                                                                                               | 1190<br>2180 | 1200<br>2200                            | ±150<br>1210<br>2220   | nA<br>Hz<br>Hz                     |

| RxAF     | Output of the high-pass filter<br>Slew rate<br>Gain bandwidth (GBW)<br>Voltage range                                                                                                               | 150<br>0.15  | 0.025                                   | V <sub>DD</sub> – 0.15 | V/μs<br>kHz<br>V                   |

| RxAFI    | Carrier detect and receive filter input<br>Leakage current                                                                                                                                         |              |                                         | ±500                   | nA                                 |

| TxA      | Modulator output<br>Frequency – mark (logic 1)<br>Frequency – space (logic 0)<br>Amplitude (AREF 1.235 V)<br>Slew Rate – mark (logic 1)<br>Slew Rate – space (logic 0)<br>Loading (AREF = 1.235 V) | 30           | 1196.9<br>2194.3<br>500<br>1860<br>3300 |                        | Hz<br>Hz<br>WV<br>V/s<br>V/s<br>kΩ |

| RxD      | Receive digital output<br>Rise/fall time                                                                                                                                                           | 20           |                                         |                        | ns                                 |

| CD       | Carrier detect output<br>Rise/fall time                                                                                                                                                            | 20           |                                         |                        | ns                                 |

#### Table 3. AC CHARACTERISTICS (V<sub>DD</sub> = 3.0 V to 5.5 V, V<sub>SS</sub> = 0 V, T<sub>A</sub> = $-40^{\circ}$ C to $+85^{\circ}$ C) (Note 4)

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

4. The modular output frequencies are proportional to the input clock frequency (460.8 kHz).

#### Table 4. MODEM CHARACTERISTICS (V<sub>DD</sub> = 3.0 V to 5.5 V, V<sub>SS</sub> = 0 V, T<sub>A</sub> = $-40^{\circ}$ C to $+85^{\circ}$ C)

| Parameter                                                                                                                                                             | Min | Тур | Max | Units      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------------|

| Demodulator jitter<br>Conditions<br>1. Input frequencies at 1200 Hz ± 10 Hz, 2200 Hz ± 20 Hz<br>2. Clock frequency of 460.8 kHz ± 0.1%<br>3. Input (RxA) asymmetry, 0 |     |     | 12  | % of 1 bit |

#### Table 5. CERAMIC RESONATOR – External Clock Specifications ( $V_{DD}$ = 3.0 V to 5.5 V, $V_{SS}$ = 0 V, $T_A$ = -40°C to +85°C)

| Parameter                                              | Min         | Тур                                              | Max         | Units         |

|--------------------------------------------------------|-------------|--------------------------------------------------|-------------|---------------|

| Resonator<br>Tolerance<br>Frequency                    |             | 460.8                                            | 1.0         | %<br>kHz      |

| External<br>Clock frequency<br>Duty cycle<br>Amplitude | 456.2<br>40 | 460.8<br>50<br>V <sub>OH</sub> – V <sub>OL</sub> | 465.4<br>60 | kHz<br>%<br>V |

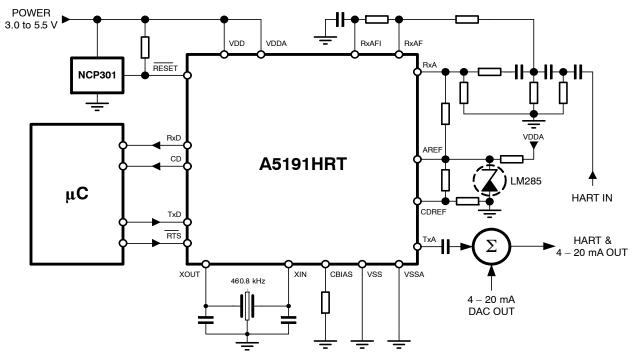

Figure 2. Application Diagram A5191HRT

#### Table 6. PIN OUT SUMMARY 28-PIN PLCC

| Pin No. | Signal Name | Туре   | Pin Description                                                        |

|---------|-------------|--------|------------------------------------------------------------------------|

| 1       | TEST1       | Input  | Connect to VSS                                                         |

| 2, 3, 4 | TEST2, 3, 4 | -      | Do Not Connect                                                         |

| 5       | TEST5       | Input  | Connect to VSS                                                         |

| 6       | RESETB      | Input  | Reset all digital logic when low                                       |

| 7, 8, 9 | TEST7, 8, 9 | Input  | Connect to VSS                                                         |

| 10      | TxA         | Output | Transmit Data Modulator output                                         |

| 11      | AREF        | Input  | Analog reference voltage                                               |

| 12      | CDREF       | Input  | Carrier detect reference voltage                                       |

| 13      | CBIAS       | Output | Comparator bias current                                                |

| 14      | TEST10      | Input  | Connect to VSS                                                         |

| 15      | VDDA        | Power  | Analog supply voltage                                                  |

| 16      | RxA         | Input  | Receive Data Modulator input                                           |

| 17      | RxAF        | Output | Analog receive filter output                                           |

| 18      | RxAFI       | Input  | Analog receive comparator input                                        |

| 19      | XOUT        | Output | Crystal oscillator output                                              |

| 20      | XIN         | Input  | Crystal oscillator input                                               |

| 21      | VSS         | Ground | Ground                                                                 |

| 22      | VDD         | Power  | Digital supply voltage                                                 |

| 23      | RTSB        | Input  | Request to send                                                        |

| 24      | TxD         | Input  | Input transmit date, transmitted HART data stream from microcontroller |

| 25      | TEST11      | -      | Do Not Connect                                                         |

| 26      | RxD         | Output | Received demodulated HART data to microcontroller                      |

| 27      | CD          | Output | Carrier detect output                                                  |

| 28      | TEST12      | -      | Do Not Connect                                                         |

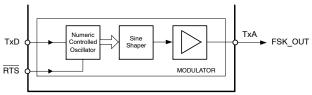

Figure 4. Pin Out A5191HRT in 32-pin QFN and LQFP (top view)

Table 7. PIN OUT SUMMARY 32-PIN QFN AND LQFP

| Pin No. | Signal Name | Туре   | Pin Description                                                     |

|---------|-------------|--------|---------------------------------------------------------------------|

| 1       | TEST5       | Input  | Connect to VSS                                                      |

| 2       | RESETB      | Input  | Reset all logic when low, connect to VDD for normal operation       |

| 3, 4, 5 | TEST7, 8, 9 | Input  | Connect to VSS                                                      |

| 6       | VSS         | Ground | Digital ground                                                      |

| 7       | TxA         | Output | Transmit Data Modulator output                                      |

| 8       | AREF        | Input  | Analog reference voltage                                            |

| 9       | CDREF       | Input  | Carrier detect reference voltage                                    |

| 10      | CBIAS       | Output | Comparator bias current                                             |

| 11      | TEST10      | Input  | Connect to VSS                                                      |

| 12      | VSSA        | Ground | Analog ground                                                       |

| 13      | VDDA        | Power  | Analog supply voltage                                               |

| 14      | RxA         | Input  | Receive Data Modulator input                                        |

| 15      | RxAF        | Output | Analog receive filter output                                        |

| 16      | RxAFI       | Input  | Analog receive comparator input                                     |

| 17      | XOUT        | Output | Crystal oscillator output                                           |

| 18      | XIN         | Input  | Crystal oscillator input                                            |

| 19      | VSSA        | Ground | Analog ground                                                       |

| 20      | VSS         | Ground | Digital ground                                                      |

| 21      | VDD         | Power  | Digital supply voltage                                              |

| 22      | RTSB        | Input  | Request to send                                                     |

| 23      | TxD         | Input  | Input transmit data, transmit HART data stream from microcontroller |

| 24      | TEST11      | -      | Do Not Connect                                                      |

| 25      | RxD         | Output | Received demodulated HART data to microcontroller                   |

| 26      | CD          | Output | Carrier detect output                                               |

| 27      | TEST12      | -      | Do Not Connect                                                      |

| 28      | TEST1       | Input  | Connect to VSS                                                      |

| 29      | TEST2       | -      | Do Not Connect                                                      |

| 30      | VDD         | Power  | Digital supply voltage                                              |

| 31, 32  | TEST3, 4    | -      | Do Not Connect                                                      |

| EP      | Exposed Pad | Power  | Connect to VSS (QFN only)                                           |

#### **Pin Descriptions**

#### Table 8. PIN DESCRIPTIONS

| Symbol     | Pin Name                         | Description                                                                                                                                                                                                                                               |

|------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AREF       | Analog reference voltage         | Receiver Reference Voltage. Normally 1.23 V is selected (in combination with VD-DA = 3.3 V). See Table 2.                                                                                                                                                 |

| CDREF      | Carrier detect reference voltage | Carrier Detect Reference voltage. The value should be 85 mV below AREF to set the carrier detection to a nominal of 100 mV $_{\rm p-p}.$                                                                                                                  |

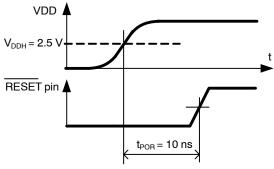

| RESETB     | Reset digital logic              | When at logic low (V <sub>SS</sub> ) this input holds all the digital logic in reset. During normal operation RESETB should be at V <sub>DD</sub> . RESETB should be held low for a minimum of 10 nS after V <sub>DD</sub> = 2.5 V as shown in Figure 14. |

| RTSB       | Request to send                  | Active-low input selects the operation of the modulator. TxA is enabled when this signal is low. This signal must be held high during power-up.                                                                                                           |

| RxA        | Analog receive input             | Receive Data Demodulator Input. Accepts a HART 1200 / 2200 Hz FSK modulated waveform input.                                                                                                                                                               |

| RxAFI      | Analog receive comparator input  | Positive input of the carrier detect comparator and the receiver filter comparator.                                                                                                                                                                       |

| TxD        | Digital transmit input           | Input to the modulator accepts digital data in NRZ form. When TxD is low, the modulator output frequency is 2200 Hz. When TxD is high, the modulator output frequency is 1200 Hz.                                                                         |

| XIN        | Oscillator input                 | Input to the internal oscillator must be connected to a parallel mode 460.8 kHz ce-<br>ramic resonator when using the internal oscillator or grounded when using an exter-<br>nal 460.8 kHz clock signal.                                                 |

| CBIAS      | Comparator bias current          | Connection to the external bias resistor. $R_{BIAS}$ should be selected such that AREF / $R_{BIAS}$ = 2.5 $\mu A$ ± 5 %                                                                                                                                   |

| CD         | Carrier detect output            | Output goes high when a valid input is recognized on RxA. If the received signal is greater than the threshold specified on CDREF for four cycles of the RxA signal, the valid input is recognized.                                                       |

| RxAF       | Analog receive filter output     | The output of the three pole high pass receive data filter                                                                                                                                                                                                |

| RxD        | Digital receive output           | Signal outputs the digital receive data. When the received signal (RxA) is 1200 Hz, RxD outputs logic high. When the received signal (RxA) is 2200 Hz, RxD outputs logic low. The HART receive data stream is only active if Carrier Detect (CD) is high. |

| TxA        | Analog transmit output           | Transmit Data Modulator Output. A trapezoidal shaped waveform with a frequency of 1200 Hz or 2200 Hz corresponding to a data value of 1 or 0 respectively applied to TxD. TxA is active when RTSB is low. TxA equals 0.5 V when RTSB is high.             |

| XOUT       | Oscillator output                | Output from the internal oscillator must be connected to an external 460.8 kHz clock signal or to a parallel mode 460.8 kHz ceramic resonator when using the internal oscillator.                                                                         |

| TEST(12:1) | Factory test                     | Factory test pins; for normal operation, tie these signals as per Tables 6 and 7                                                                                                                                                                          |

| VDD        | Digital power                    | Power for the digital modem circuitry                                                                                                                                                                                                                     |

| VDDA       | Analog supply voltage            | Power for the analog modem circuitry                                                                                                                                                                                                                      |

| VSS        | Ground                           | Digital ground (and Analog ground in the case of PLCC package)                                                                                                                                                                                            |

| VSSA       | Analog ground                    | Analog ground                                                                                                                                                                                                                                             |

#### FUNCTIONAL DESCRIPTION

The A5191HRT is a single-chip modem for use in Highway Addressable Remote Transducer (HART) field instruments and masters. The modem IC contains a transmit data modulator with signal shaper, carrier detect circuitry, an analog receiver, demodulator circuitry and a crystal oscillator, as shown in the block diagram in Figure 1.

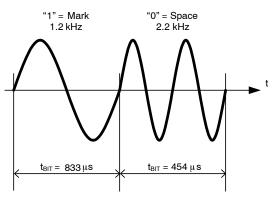

The modulator accepts digital data at its digital input TxD and generates a sine shaped FSK modulated signal at the analog output TxA. A digital "1" or mark is represented with a frequency of 1200 Hz. A digital "0" or space is represented with a frequency of 2200 Hz. The used bit rate is 1200 baud.

The demodulator receives the FSK signal at its analog input, filters it with a band-pass filter and generates 2 digital signals: RxD: Received Data and CD: Carrier Detect. At the digital output RxD the original modulated signal is received. CD outputs the Carrier Detect signal. It goes logic high if the received signal is above 100 mVpp during 4 consecutive carrier periods.

The oscillator provides the modem with a stable time base using either a simple external resonator or an external clock source.

#### DETAILED DESCRIPTION

#### Modulator

The modulator accepts digital data in NRZ form at the TxD input and generates the FSK modulated signal at the TxA output.

A logic "1" or mark is represented by a frequency fm = 1200 Hz. A logic "0" or space is represented by a frequency fs = 2200 Hz.

Figure 6. Modulation Timing

The Numeric Controlled Oscillator NCO works in a phase continuous mode preventing abrupt phase shifts when switching between mark and space frequency. The control signal Request To Send RTSB enables the NCO. When RTSB is logic low the modulator is active and A5191HRT is in transmit mode. When RTSB is logic high the modulator is disabled and A5191HRT is in receive mode.

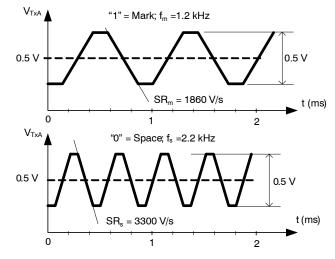

The digital outputs of the NCO are shaped in the Wave Shaper block to a trapezoidal signal. This circuit controls the rising and falling edge to be inside the standard HART waveshape limits. Figure 7 shows the transmit–signal forms captured at TxA for mark and space frequency. The slew rates are  $SR_m = 1860$  V/s at the mark frequency and  $SR_s = 3300$  V/s at the space frequency. For AREF = 1.235 V, TxA will have a voltage swing from approximately 0.25 to 0.75 V<sub>DC</sub>.

Figure 7. Modulator shaped output signal for Mark and Space frequency at TxA pin.

#### Demodulator

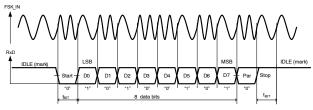

The demodulator accepts a FSK signal at the RxA input and reconstructs the original modulated signal at the RxD output. Figure 8 illustrates the demodulation process.

Figure 8. Modulation Timing

This HART bit stream follows a standard 11-bit UART frame with 1 startbit, 8 databits, 1 paritybit (odd) and 1 stopbit. The communication speed is 1200 baud.

#### **Receive Filter and Comparator**

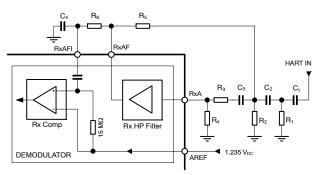

The received FSK signal first is filtered using a band-pass filter build around the low noise receiver operational amplifier "Rx HP filter". This filter blocks interferences outside the HART signal band.

#### Figure 9. Demodulator Receive Filter and Signal Comparator

The filter output is fed into the Rx comparator. The threshold value equals the analog ground making the comparator to toggle on every zero crossing of the filtered FSK signal. The maximum demodulator jitter is 12% of one bit given the input frequencies are within the HART specifications, a clock frequency of 460.8 kHz (±1.0%) and zero input (RxA) asymmetry.

#### **Carrier Detect Circuitry**

Low HART input signal levels increases the risk for the generation of bit errors. Therefore the minimum signal amplitude is set to 80 - 120 mVpp. If the received signal is below this level the demodulator is disabled.

This level detection is done in the Carrier Detector. The output of the demodulator is qualified with the carrier detect signal (CD), therefore, only RxA signals large enough to be detected (100 mVp-p typically) by the carrier detect circuit produce received serial data at RxD.

## Figure 10. Demodulator Carrier and Signal Comparator

The carrier detect comparator shown in Figure 10 generates logic low output if the RxAFI voltage is below CDREF. The comparator output is fed into a carrier detect block. The carrier detect block drives the carrier detect

output pin CD high if RTSB is high and four consecutive pulses out of the comparator have arrived. CD stays high as long as RTSB is high and the next comparator pulse is received in less than 2.5 ms. Once CD goes inactive, it takes four consecutive pulses out of the comparator to assert CD again. Four consecutive pulses amount to 3.33 ms when the received signal is 1200 Hz and to 1.82 ms when the received signal is 2200 HZ.

#### MISCELLANEOUS ANALOG CIRCUITRY

#### Voltage References

The A5191HRT requires two voltage references, AREF and CDREF. AREF sets the DC operating point of the internal operational amplifiers and is the reference for the Rx comparator. If A5191HRT operates at  $V_{DD} = 3.3$  V the **onsemi** LM285D 1.235 V reference is recommended.

The level at which CD (Carrier Detect) becomes active is determined by the DC voltage difference (CDREF – AREF). Selecting a voltage difference of 80 mV will set the carrier detect to a nominal 100 mV<sub>p-p</sub>.

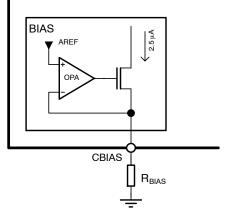

#### **Bias Current Resistor**

The A5191HRT requires a bias current resistor  $R_{BIAS}$  to be connected between CBIAS and  $V_{SS}$ . The bias current controls the operating parameters of the internal operational amplifiers and comparators and should be set to 2.5  $\mu$ A.

The value of the bias current resistor is determined by the reference voltage AREF and the following formula:

$$\mathsf{R}_{\mathsf{BIAS}} = \frac{\mathsf{AREF}}{2.5 \ \mu \mathsf{A}}$$

The recommended bias current resistor is 500 K $\Omega$  when AREF is equal to 1.235 V.

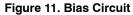

#### Oscillator

The A5191HRT requires a 460.8 kHz clock signal. This can be provided by an external clock or a resonator connected to the A5191HRT internal oscillator.

#### Internal Oscillator Option

The oscillator cell will function with either a 460.8 kHz crystal or ceramic resonator. A parallel resonant ceramic resonator can be connected between XIN and XOUT. Figure 12 illustrates the crystal option for clock generation using a 460.8 kHz ( $\pm$ 1% tolerance) parallel resonant crystal and two tuning capacitors Cx. The actual values of the capacitors may depend on the recommendations of the manufacturer of the resonator. Typically, capacitors in the range of 100 pF to 470 pF are used.

Figure 12. Crystal Oscillator

#### **External Clock Option**

It may be desirable to use an external 460.8 kHz clock as shown in Figure 13 rather than the internal oscillator. In addition, the A5191HRT consumes less current when an external clock is used. Minimum current consumption occurs with the clock connected to XOUT and XIN connected to  $V_{SS}$ .

Figure 13. Oscillator with External Clock

#### **Power On Reset**

During start–up the RESETB pin should be kept low until the voltage level on  $V_{DD}$  is above the minimum level  $V_{DDH}$ = 2.5 V to guarantee correct operation of the digital circuitry. As illustrated in Figure 14 RESETB should be kept low for at least t<sub>POR</sub> = 10 ns after this threshold level is reached.

Figure 14. Power On Reset Timing

#### **Ordering Information**

The A5191HRT is available in a 28-pin plastic leaded chip carrier (PLCC), 32-pin quad flat no-lead (QFN) and 32-pin low-profile quad flat pack (LQFP). Use the following part numbers when ordering. Contact your local sales representative for more information: <u>www.onsemi.com</u>.

#### Table 9. ORDERING INFORMATION

| Part Number                    | Temperature Range | Package                               | Shipping Configuration <sup>†</sup> |

|--------------------------------|-------------------|---------------------------------------|-------------------------------------|

| A5191HRTLG-XTP<br>(Industrial) | -40°C to +85°C    | 32-pin LQFP<br>Green / RoHS compliant | 2500 Units / Tape & Reel            |

| A5191HRTPG-XTP<br>(Industrial) | -40°C to +85°C    | 28-pin PLCC<br>Green / RoHS compliant | 750 Units / Tape & Reel             |

| A5191HRTNG-XTP<br>(Industrial) | -40°C to +85°C    | 32–pin QFN<br>Green / RoHS compliant  | 5000 Units / Tape & Reel            |

#### DISCONTINUED (Note 5)

| A5191HRTLG-XTD<br>(Industrial) | −40°C to +85°C | 32-pin LQFP<br>Green / RoHS compliant | 250 Units / Tray     |

|--------------------------------|----------------|---------------------------------------|----------------------|

| A5191HRTNG-XTD<br>(Industrial) | −40°C to +85°C | 32–pin QFN<br>Green / RoHS compliant  | 60 Units / Tube/Tray |

| A5191HRTPG-XTD<br>(Industrial) | –40°C to +85°C | 28-pin PLCC<br>Green / RoHS compliant | 37 Units / Tube      |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

5. **DISCONTINUED:** These devices are not recommended for new design. Please contact your **onsemi** representative for information. The most current information on these devices may be available on <u>www.onsemi.com</u>.

# <u>Onsemi</u>

| DOCUMENT NUMBER: | 98AON20032D                                                                                                                                                                                                                                                                                                                                                           | 98AON20032D Electronic versions are uncontrolled except when accessed directly from the Document Reposit<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|

| DESCRIPTION:     | QFN32 5x5 0.5P                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                             | PAGE 1 OF 1 |  |  |  |

|                  | onsemi and ONSEMI. are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular |                                                                                                                                                                                             |             |  |  |  |

the right to make changes without further notice to any products herein. **onsemi** makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. **onsemi** does not convey any license under its patent rights or the rights of others.

LQFP-32, 7x7 CASE 561AB-01 ISSUE O

DATE 19 JUN 2008

| DOCUMENT NUMBER:                                                                  | 98AON30893E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Electronic versions are uncontrolled except when accessed directly from the Document Repositor<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |  |

|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|

| DESCRIPTION:                                                                      | N: 32 LEAD LQFP, 7X7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                   | PAGE 1 OF 1 |  |  |  |

| ON Semiconductor reserves the right<br>the suitability of its products for any pa | ON Semiconductor and ()) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries.<br>ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding<br>the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically<br>disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the |                                                                                                                                                                                   |             |  |  |  |

rights of others.

ON

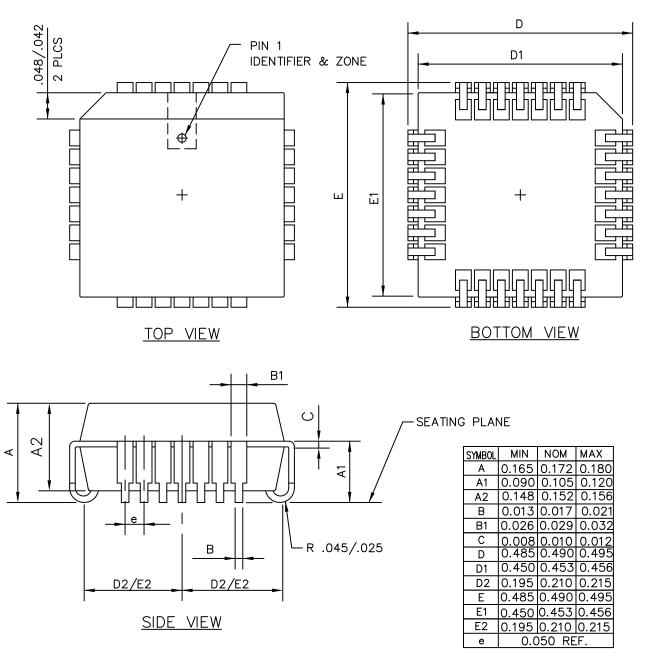

PLCC 28 LEAD CASE 776AA-01 ISSUE O

DATE 19 JUN 2008

ALL DIMENSIONS ARE IN INCHES.

DOCUMENT NUMBER:

98AON30890E

Electronic versions are uncontrolled except when accessed directly from the Document Repository. Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red.

DESCRIPTION:

PLCC 28 LEAD

PAGE 1 OF 1

ON Semiconductor and ()) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

© Semiconductor Components Industries, LLC, 2019

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent\_Marking.pdf</u>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or indental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification. Buyer shall indemnify and hold onsemi and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs,

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

Technical Library: www.onsemi.com/design/resources/technical-documentation onsemi Website: www.onsemi.com

ONLINE SUPPORT: <u>www.onsemi.com/support</u> For additional information, please contact your local Sales Representative at <u>www.onsemi.com/support/sales</u>