## 2.4GHz FSK/GFSK SoC

## **Document Title**

A8106 Data Sheet, 2.4GHz FSK/GFSK SOC

## **Revision History**

| Rev. No. | <u>History</u>                                                 | Issue Date | <u>Remark</u> |

|----------|----------------------------------------------------------------|------------|---------------|

| 0.1      | Initial issue.                                                 | Dec., 2013 | Objective     |

| 0.2      | Add OTP version                                                | Aug., 2014 | Preliminary   |

| 0.3      | Update Spec. Update Section 18.2 -12bit ADC Updated RSSI curve | Sep., 2014 | Preliminary   |

### **Important Notice**:

AMICCOM reserves the right to make changes to its products or to discontinue any integrated circuit product or service without notice. AMICCOM integrated circuit products are not designed, intended, authorized, or warranted to be suitable for use in life-support applications, devices or systems or other critical applications. Use of AMICCOM products in such applications is understood to be fully at the risk of the customer.

## 2.4GHz FSK/GFSK SoC

| Table of Contents                                                |                                        |

|------------------------------------------------------------------|----------------------------------------|

| 1. General Description                                           |                                        |

| 2. Typical Applications                                          | ······································ |

| 3. Feature                                                       |                                        |

| 4. Pin Configurations                                            |                                        |

| 5. Pin Description (I: input; O: output, I/O: input or output)   |                                        |

| 6. Chip Block Diagram                                            |                                        |

| 7. Absolute Maximum Ratings                                      |                                        |

| 8. Electrical Specification                                      |                                        |

| 9.1 SFR & RFR(Radio Frequency Register)                          |                                        |

| 9.2 RFR Overview                                                 |                                        |

| 9.2.1 Mode Register (Address: 0x800h)                            |                                        |

| 9.2.2 Mode Control Register 1 (Address: 0x801h)                  |                                        |

| 9.2.3 Mode Control Register 2 (Address: 0x802h)                  |                                        |

| 9.2.4 Calibration Control Register (Address: 0x803h)             |                                        |

| 9.2.5FIFO Register I (Address: 0x804h)                           |                                        |

| 9.2.6 FIFO Register II (Address: 0x805h)                         |                                        |

| 9.2.7 RC OSC Register I (Address: 0x806h)                        |                                        |

| 9.2.8 RC OSC Register II (Address: 0x807h)                       |                                        |

| 9.2.9 RC OSC Register III (Address: 0x808h)                      |                                        |

| 9.2.10 CKO Pin Control Register (Address: 0x809h)                | 1                                      |

| 9.2.11 GIO1 Pin Control Register I (Address: 0x80Ah)             | 16                                     |

| 9.2.12 GIO2 Pin Control Register II (Address: 0x80Bh)            | 16                                     |

| 9.2.13 Clock Register (Address: 0x80Ch)                          | 1                                      |

| 9.2.14 Data Rate Register (Address: 0x80Dh)                      |                                        |

| 9.2.15 PLL Register I (Address: 0x80Eh)                          |                                        |

| 9.2.16 PLL Register II (Address: 0x80Fh)                         |                                        |

| 9.2.17 PLL Register III (Address: 0x810h)                        |                                        |

| 9.2.18 PLL Register IV (Address: 0x811h)                         | ۱۰۰۰۰۰۰۰۱ م                            |

| 9.2.19 PLE Register V (Address: 0x812h)                          |                                        |

| 9.2.21 TX Register I (Address: 0x814h)                           |                                        |

| 9.2.22 Delay Register I (Address: 0x815h)                        |                                        |

| 9.2.23 Delay Register II (Address: 0x816h)                       |                                        |

| 9.2.24 RX Register (Address: 0x817h)                             |                                        |

| 9.2.25 RX Gain Register I (Address: 0x818h)                      |                                        |

| 9.2.26 RX Gain Register II (Address: 0x819h)                     |                                        |

| 9.2.27 RX Gain Register III (Address: 0x81Ah)                    | 2                                      |

| 9.2.28 RX Gain Register IV (Address: 0x81Bh)                     |                                        |

| 9.2.29 RSSI Threshold Register (Address: 0x81Ch)                 |                                        |

| 9.2.30 ADC Control Register (Address: 0x81Dh)                    |                                        |

| 9.2.31 Code Register I (Address: 0x81Eh)                         |                                        |

| 9.2.32 Code Register II (Address: 0x81Fh)                        |                                        |

| 9.2.33 Code Register III (Address: 0x820h)                       |                                        |

| 9.2.34 IF Calibration Register I (Address: 0x821h)               |                                        |

| 9.2.35 IF Calibration Register II (Address: 0x822h)              |                                        |

| 9.2.36 VCO current Calibration Register (Address: 0x823h)        |                                        |

| 9.2.38 VCO Single band Calibration Register I (Address: 0x824ff) |                                        |

| 9.2.39 Battery detect Register (Address: 0x826h)                 |                                        |

| 9.2.40 TX test Register (Address: 0x827h)                        |                                        |

| 9.2.41 Rx DEM test Register I (Address: 0x828h)                  |                                        |

| 9.2.42 Rx DEM test Register II (Address: 0x829h)                 |                                        |

| 9.2.43 Charge Pump Current Register (Address: 0x82Ah)            |                                        |

| 9.2.44 Crystal test Register (Address: 82Bh)                     |                                        |

| 9.2.45 PLL test Register (Address: 0x82Ch)                       |                                        |

| 9.2.46 VCO test Register I (Address: 0x82Dh)                     |                                        |

| 9.2.47 VCO test Register II (Address: 0x82Eh)                    |                                        |

| 9.2.48 IFAT Register (Address: 0x82Fh)                           | 20                                     |

| 9.2.49 RScale Register (Address: 0x830h)                         |                                        |

| 9.2.50 Filter test Register (Address: 0x831h)                    | 26                                     |

аміссом 笙科電子總代理 深圳奇翰電子

## 2.4GHz FSK/GFSK SoC

| 9.2.51 RX Gain Register II (Address: 0x832h)            |    |

|---------------------------------------------------------|----|

| 9.2.52 RX Detection Register (Address: 0x833h)          | 27 |

| 9.2.53 DC_SHIFT (Address: 0x834h)                       | 27 |

| 9.2.54 ID Register 0 (Address: 0x835h)                  | 27 |

| 9.2.55 ID Register 1 (Address: 0x836h)                  |    |

| 9.2.56 ID Register 2 (Address: 0x837h)                  |    |

| 9.2.57 ID Register 3 (Address: 0x838h)                  |    |

| 9.2.58 DID Register 0 (Address: 0x839h)                 |    |

| 9.2.59 DID Register 1 (Address: 0x83Ah)                 |    |

| 9.2.60 DID Register 2 (Address: 0x83Bh)                 |    |

| 9.2.61 DID Register 3 (Address: 0x83Ch)                 |    |

| 9.2.62 Power Control Register 0 (Address: 0x83Dh)       |    |

| 9.2.63 Power Control Register 1 (Address: 0x83Eh)       |    |

| 9.2.64 Power Control Register 2 (Address: 0x83Fh)       |    |

| 9.2.65 RC OSC Register IV (Address: 0x840h)             |    |

| 9.2.66 RC OSC Register V (Address: 0x841h)              |    |

| 9.2.67 RC OSC Register VI (Address: 0x842h)             |    |

| 9.2.68 RC OSC Register VII (Address: 0x843h)            |    |

| 9.2.69 RC OSC Register VIII (Address: 0x646h)           |    |

| 9.2.70 Timer Interval Register 1 (Address: 0x845h)      |    |

| 9.2.71 Timer Interval Register 2 (Address: 0x846h)      |    |

| 9.2.72 Timer Wake On Radio Register 1 (Address: 0x847h) |    |

| 9.2.73 Timer Control Register (Address: 0x848h)         |    |

| 9.2.74 RFT Test Register IV (Address: 0x849h)           |    |

| 9.2.75 RFT Test Register III (Address: 0x84Ah)          |    |

| 9.2.76 ADC Control Register (Address: 0x84Bh)           |    |

| 9.2.77 ADC Value Register 1 (Address: 0x84Ch)           |    |

| 9.2.78 ADC Value Register 2 (Address: 0x84Dh)           |    |

| 9.2.79 ADC Value Register 3 (Address: 0x84Eh)           |    |

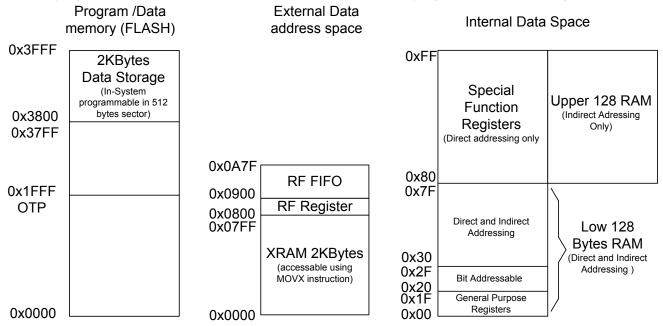

| 10.SOC Architectural Overview                           |    |

| 10.1 Pipeline 8051 CPU                                  |    |

| 10.2 Memory Organization                                |    |

| 10.2.1 Program memory                                   |    |

| 10.2.2 Data memory                                      |    |

| 10.2.3 General Purpose Registers                        |    |

| 10.2.4 Bit Addressable Locations                        | 3. |

| 10.2.5 Special Function Registers                       |    |

| 10.2.6 Stack                                            |    |

| 10.2.7 Data Pointer Register                            | 35 |

| 10.2.8 RF Registers and RF FIFO                         | 37 |

| 10.3 Instruction set                                    |    |

| 10.4 Interrupt handler                                  |    |

| 10.4.1 FUNCTIONALITY                                    |    |

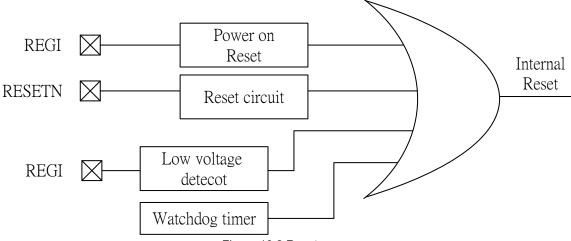

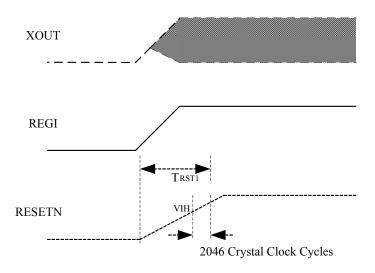

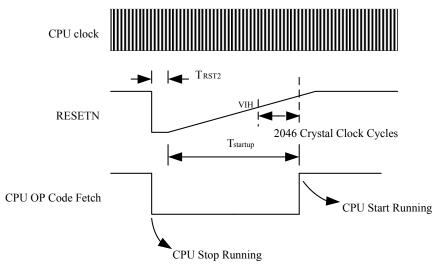

| 10.5 Reset source                                       |    |

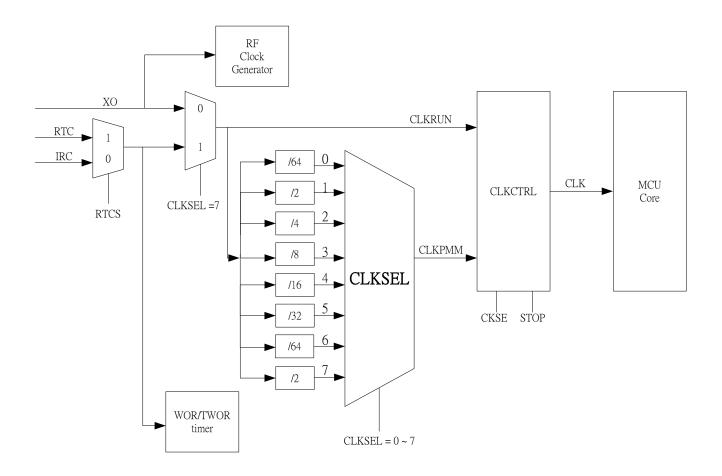

| 10.6 Clock source                                       |    |

| 11. I/O Ports                                           |    |

| 11.1 FUNCTIONALITY                                      |    |

| 11.2 Key interrupt                                      |    |

| 12 Timer0,1 and Timer2                                  |    |

| 12.1 Timer 0 & 1 PINS DESCRIPTION.                      |    |

| 12.2 Timer 0 & 1 FUNCTIONALITY                          |    |

| 12.2.1 OVERVIEW                                         |    |

| 12.2.2 Timer 0 & 1 Registers                            |    |

| M[1:0]: Mode select bits.                               |    |

| 12.3 Timer2 PINS DESCRIPTION                            |    |

| 12.4 Timer2 FUNCTIONALITY                               |    |

| 12.4.1 OVERVIEW                                         |    |

| 12.4.2 Timer 2 Registers                                |    |

| 13. UART                                                |    |

| 13.1 UART PINS DESCRIPTION                              |    |

| 13.2 FUNCTIONALITY                                      |    |

| 13.3 OPERATING MODES                                    |    |

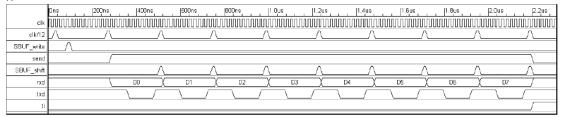

| 13.3.1 UART MODE 0, SYNCHRONOUS                         |    |

|                                                         |    |

**АМІССОМ 笙科電子總代理** 深圳奇翰電子

## 2.4GHz FSK/GFSK SoC

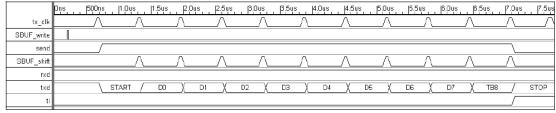

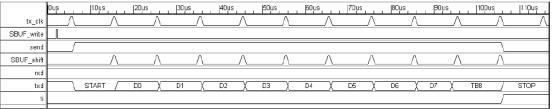

| 13.3.2 UART MODE 1, 8-BIT UART, VARIABLE BAUD RATE, TIMER CLOCK SOURCE |           |

|------------------------------------------------------------------------|-----------|

| 13.3.4 UART MODE 3, 9-BIT UART, VARIABLE BAUD RATE, TIMER CLOCK SOURCE | 61        |

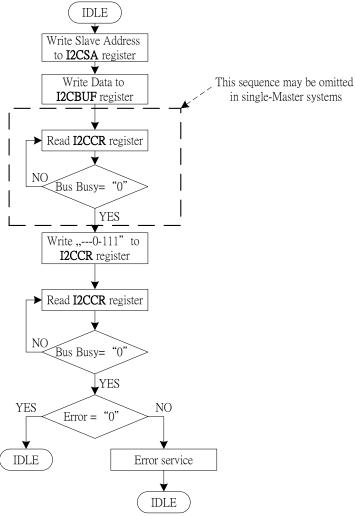

| 14. IIC interface                                                      |           |

| 14.1 Master mode I <sup>2</sup> C                                      | 62        |

| 14.1.1 I <sup>2</sup> C REGISTERS                                      | 62        |

| 14.2.4 I2C MASTER MODULE AVAILABLE SPEED MODES                         | 65        |

| 14.3 I2C MASTER MODULE INTERRUPT GENERATION                            | 73        |

| 14.5 Slave mode I <sup>2</sup> C                                       |           |

| 14.5.112C MODULE INTERNAL REGISTERS                                    |           |

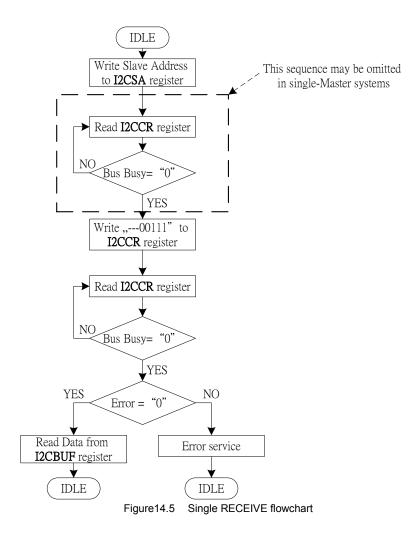

| 14.7.1 I <sup>2</sup> C module SINGLE RECEIVE                          |           |

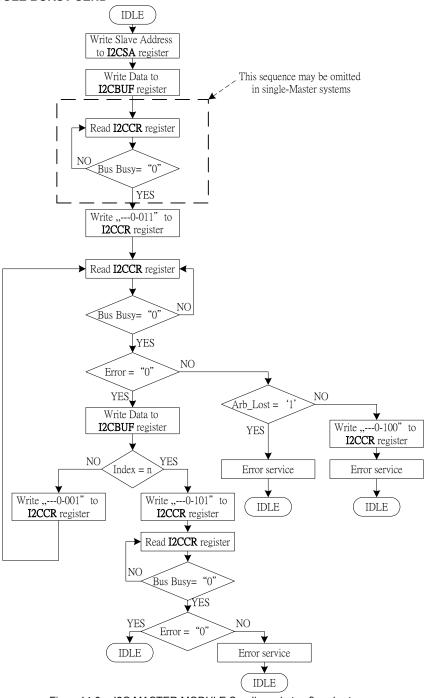

| 14.7.2 I <sup>2</sup> C module SINGLE SEND                             | 75        |

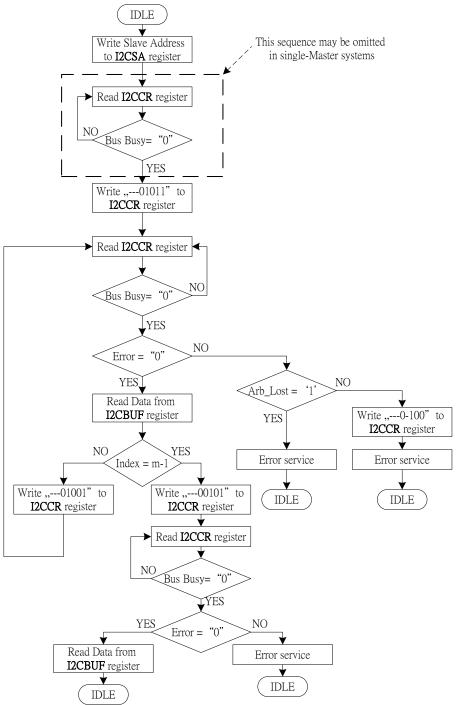

| 14.7.3 I <sup>2</sup> C module BURST RECEIVE                           | 75        |

| 14.7.4 I <sup>2</sup> C module BURST SEND                              | 76        |

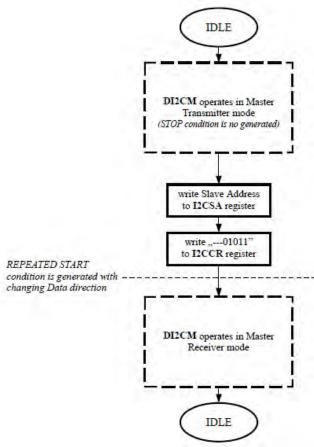

| 14.7.5 AVAILABLE I <sup>2</sup> C module COMMAND SEQUENCES FLOWCHART   | 76        |

| 14.8 I2C MODULE INTERRUPT GENERATION                                   |           |

| 15. SPI interface                                                      |           |

| 15.1 KEY FEATURES                                                      |           |

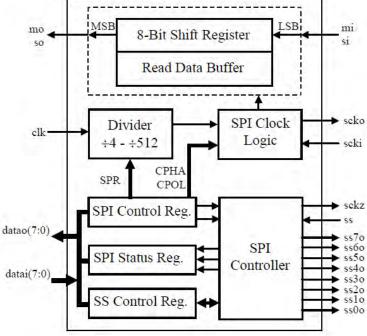

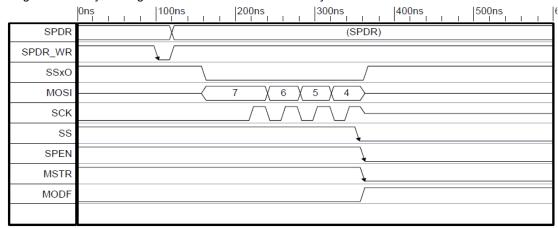

| 15.3 SPI HARDWARE DESCRIPTION                                          |           |

| 15.3.1 BLOCK DIAGRAM                                                   |           |

| 15.3.2 INTERNAL REGISTERS                                              |           |

| 15.4 MASTER OPERATIONS                                                 |           |

| 15.4.1 MASTER MODE ERRORS                                              |           |

| 15.5 SLAVE OPERATIONS                                                  |           |

| 15.5.1 SLAVE MODE ERRORS                                               |           |

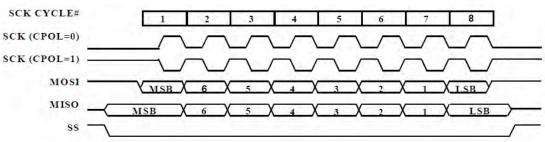

| 15.6 CLOCK CONTROL LOGIC                                               | 84        |

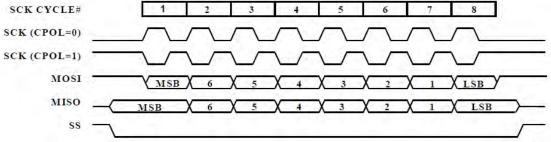

| 15.6.1 SPI CLOCK PHASE AND POLARITY CONTROLS                           |           |

| 15.6.2 SPI MODULE TRANSFER FORMATS                                     |           |

| 15.6.3 CPHA EQUALS ZERO TRANSFER FORMAT                                | 84<br>9.5 |

| 15.7 SPI DATA TRANSFER                                                 |           |

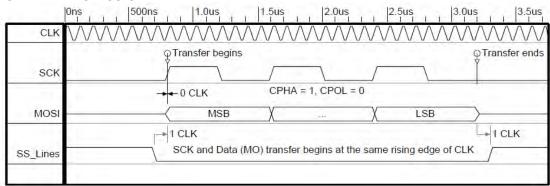

| 15.7.1 TRANSFER BEGINNING PERIOD ( INITIATION DELAY )                  |           |

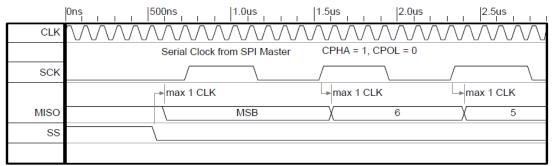

| 15.7.2 TRANSFER ENDING PERIOD.                                         |           |

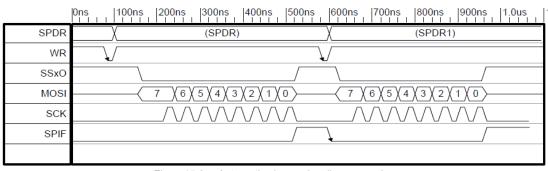

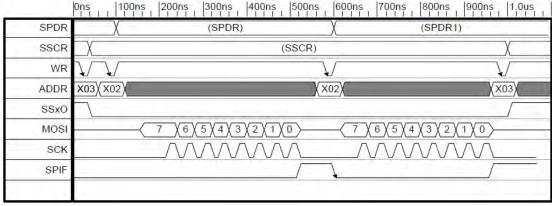

| 15.8 TIMING DIAGRAMS                                                   |           |

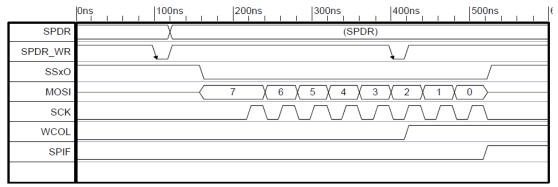

| 15.8.1 MASTER TRANSMISSION                                             |           |

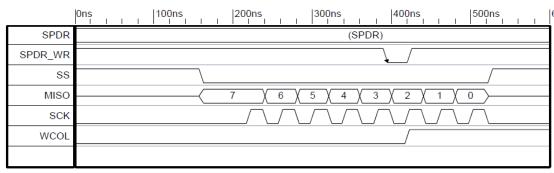

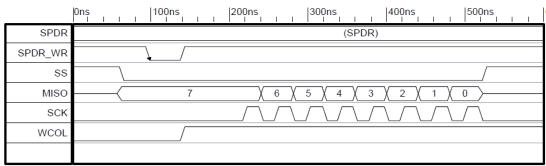

| 15.8.2 SLAVE TRANSMISSION                                              | 86        |

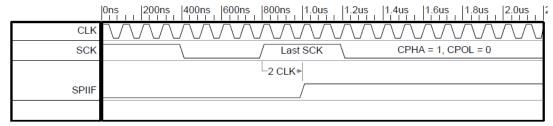

| 15.9 SPI MODULE INTERRUPT GENERATION                                   |           |

| 16. PWM                                                                |           |

| 16.1 PWM FUNCTIONALITY                                                 |           |

| 17. Watchdog Timer                                                     |           |

| 17.1 Watchdog timer overview                                           |           |

| 17.2 Watchdog interrupt                                                |           |

| 17.3 Watchdog Timer reset                                              |           |

| 17.4 SIMPLE TIMER                                                      |           |

| 17.5 SYSTEM MONITOR                                                    |           |

| 17.6 WATCHDOG RELATED REGISTERS                                        |           |

| 17.7 TIMED ACCESS REGISTERS                                            |           |

| 18. ADC (Analog to Digital Converter)                                  |           |

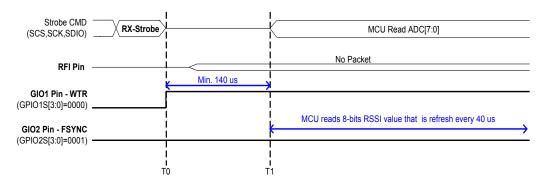

| 18.1.1 RSSI Measurement                                                |           |

| 18.1.2 Carrier Detect                                                  |           |

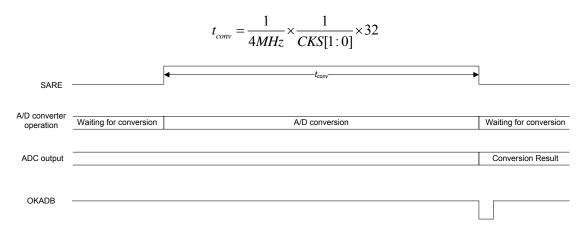

| 18.2 12-bits SAR ADC                                                   |           |

| 19. Battery Detect                                                     |           |

| 20 Power Management                                                    |           |

| 21 A8106 RF                                                            | 101       |

| 21.1 Mode Control Register 1 (Address: 0x801h)                         |           |

| 21.1.1 Strobe Command - Sleep Mode                                     |           |

| 21.1.2 Strobe Command - Idle Mode                                      |           |

| 21.1.3 Strobe Command - Standby Mode                                   |           |

| 21.1.4 Strobe Command - PLL Mode                                       | 101       |

## 2.4GHz FSK/GFSK SoC

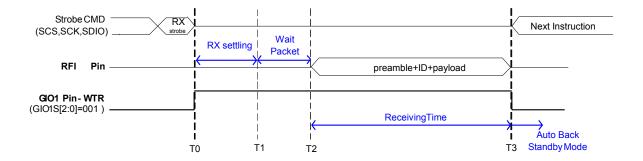

| 21.1.5 Strobe Command - RX Mode              | 101 |

|----------------------------------------------|-----|

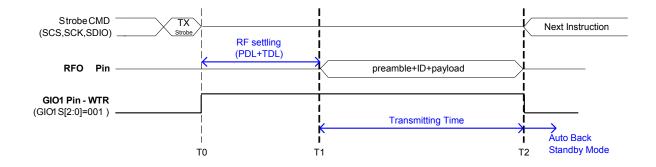

| 21.1.6 Strobe Command - TX Mode              | 102 |

| 21.2 RF Reset Command                        | 102 |

| 21.3 FIFO Accessing Command                  | 102 |

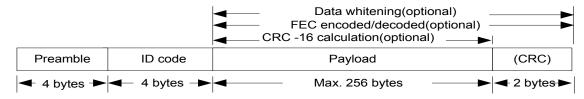

| 21.4 Packet Format of FIFO mode              | 102 |

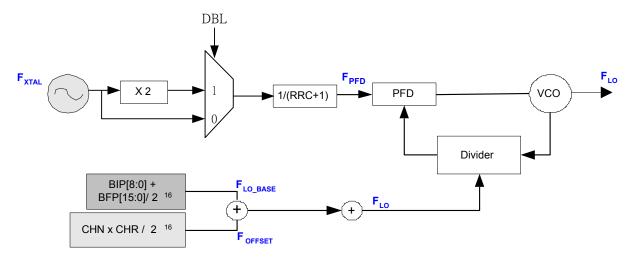

| 21.5 Transceiver Frequency                   | 103 |

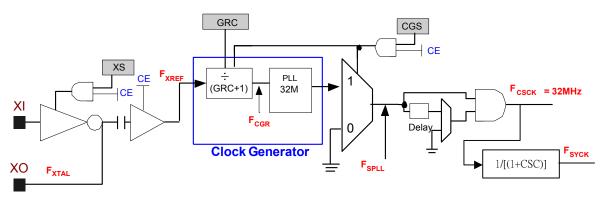

| 21.5.1 RF Clock                              |     |

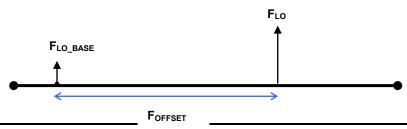

| 21.5.2 LO Frequency Setting                  |     |

| 21.5.2.1 How to set F <sub>LO BASE</sub>     | 105 |

| 21.5.2.2 How to set FLO = FLO_BASE + FOFFSET | 105 |

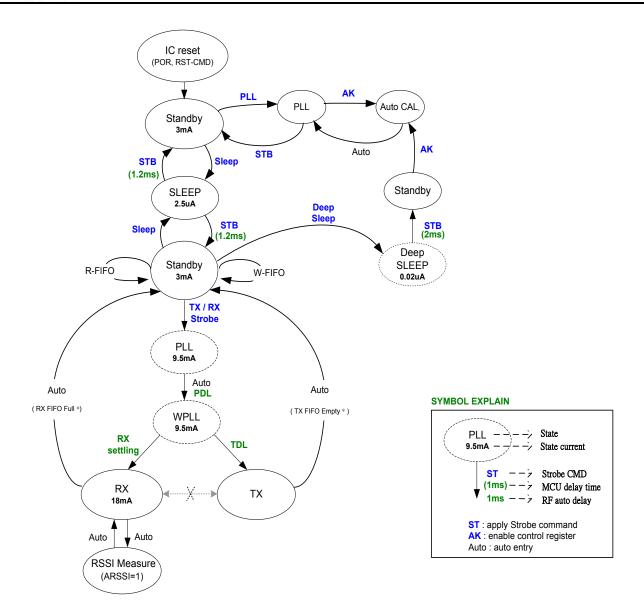

| 21.6 State machine                           |     |

| 21.6.1 Key states                            | 105 |

| 21.6.2 FIFO mode                             | 106 |

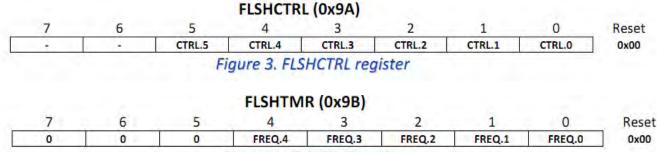

| 22. Flash memory controller                  | 108 |

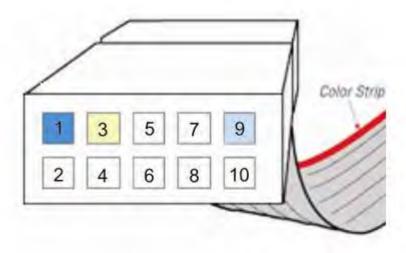

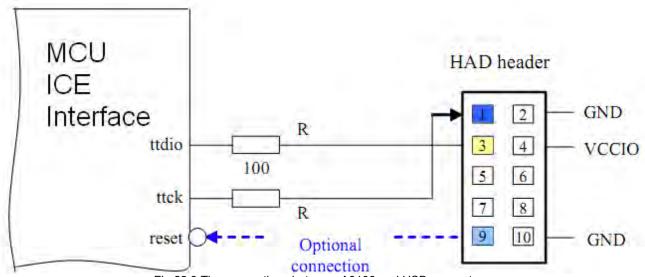

| 23 In Circuit Emulator (ICE)                 | 110 |

| 23.1 PIN define                              | 110 |

| 23.2 ICE Key feature                         | 111 |

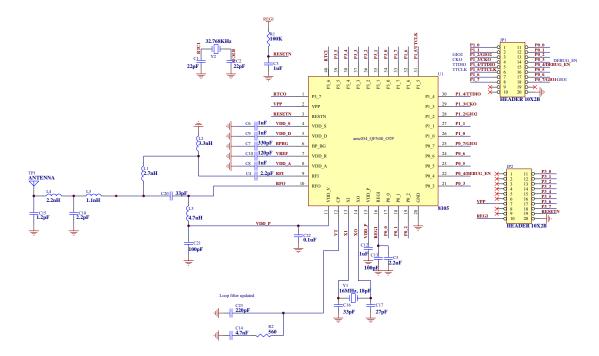

| 24. Application circuit                      | 112 |

| 25. Abbreviations                            | 113 |

| 26. Ordering Information                     | 114 |

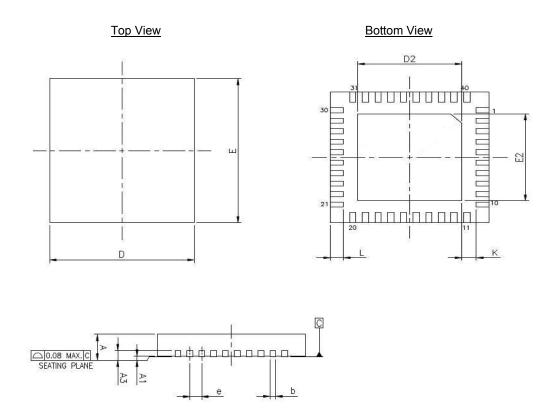

| 27. Package Information                      | 115 |

| 28. Top Marking Information                  | 116 |

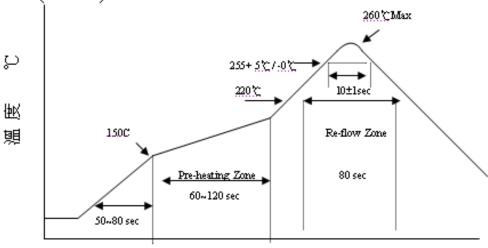

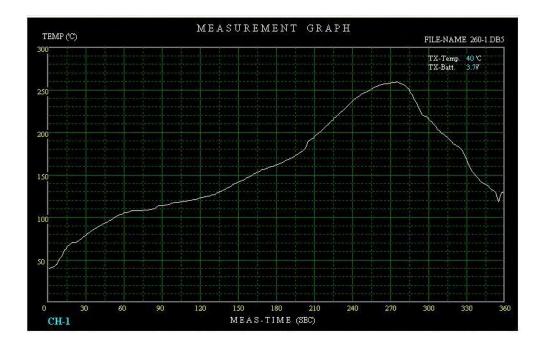

| 29. Reflow Profile                           |     |

| 30. Tape Reel Information                    |     |

| 31 Product Status                            | 120 |

**АМІССОМ 笙科電子總代理** 深圳奇翰電子

### 2.4GHz FSK/GFSK SoC

### 1. General Description

A8106 is a high performance and low cost 2.4GHz FSK/GFSK system-on-chip (SOC) wireless transceiver. With on chip fraction-N synthesizer, it can support the application of data rate from 4 Kbps to 500 Kbps and frequency hopping system. This device integrates high speed pipeline 8051 MCU, 16KBytes In-system programmable flash memory or 8Kbytes OTP (One Time Programmable) memory, 2KB SRAM, various powerful functions and excellent performance of a leading 2.4GHz FSK/GFSK RF transceiver. It can be operated with wide voltage from 2.0V ~ 3.6V. A8106 has various operating modes, making it highly suited for systems where ultra-low power consumption is required. The device is in QFN5X5 40 pin package. Beside, A8106 has two memory types. One is 16Kbytes flash memory (A8106F4) and the other is 8Kbytes OTP memory (A8106T3).

### 2. Typical Applications

- 2400 ~ 2483.5 MHz ISM frequency hopping system

- Smart remote controller

- Home and building automation

- Wireless keyboard and mouse

- Wireless toy and gaming

- Helicopter and airplane radio controller

### 3. Feature

- Package size (QFN5 X5, 40 pins).

- High performance pipeline complicated 8051

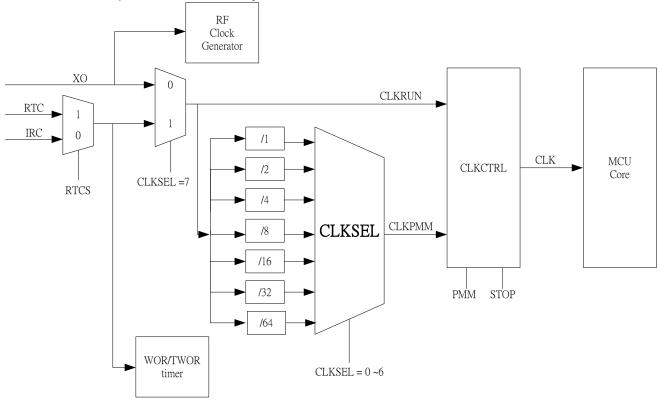

- Operation clock: 1, 1/2, 1/4, 1/8, 1/16, 1/32, 1/64 of crystal oscillator.

- 16KB Flash memory or 8KB OTP memory with copy protection, 2KB SARM

- UART, I<sup>2</sup>C, SPI serial communication

- Three 16/8-bit counter/timers

- Two Channel PWM

- Watchdog timer

- Sleep timer

- In-Circuit Debugger

- In-System programming/ In-Application programming

- 24 GPIO

- RX current consumption with MCU in operation mode :16mA

- TX current consumption with MCU in operation mode (20mA @ 2dBm).

- Deep sleep current (0.8 uA/ PM3 without Sleep timer)

- Low sleep current (3 uA)

- Frequency band: 2400 2483MHz.

- FSK and GFSK modulation

- High sensitivity:

- -95dBm at 500Kbps data rate

- ◆ -104dBm at 25Kbps data rate

- -107dBm at 2Kbps data rate

- Programmable data rate 2K ~ 500Kbps.

- Fast settling time synthesizer for frequency hopping system.

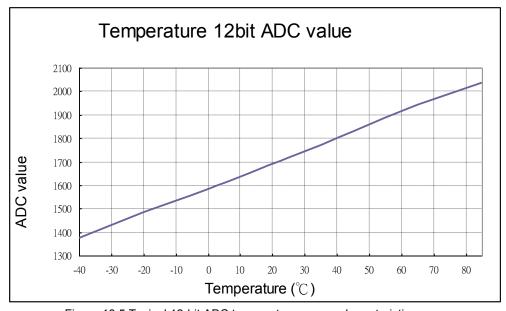

- Built-in thermal sensor for monitoring relative temperature.

- Built-in one channel 8-bits ADC for external analog voltage (0V ~ 1.2V).

- Built-in eight channels 12-bits ADC for general purpose analog input (0V ~ 1.8 V).

- Built-in Low Battery Detector.

- Support low cost crystal (8 /12 / 16 / 24MHz).

- Easy to use.

- Change frequency channel by ONE register setting.

- ♦ 8-bits Digital RSSI for clear channel indication.

- Auto RSSI measurement.

- ◆ Auto WOR (wake up when receive RX packet).

- Auto WOT (wake up to transmit TX packet).

- Auto Calibrations.

- Auto IF function.

- ◆ Auto Frequency Compensation.

- Auto CRC Check.

- ◆ Auto FEC by (7, 4) Hamming code (1 bit error correction / code word).

- Data Whitening for encryption and decryption.

- Separated 64 bytes RX and TX FIFO.

## 2.4GHz FSK/GFSK SoC

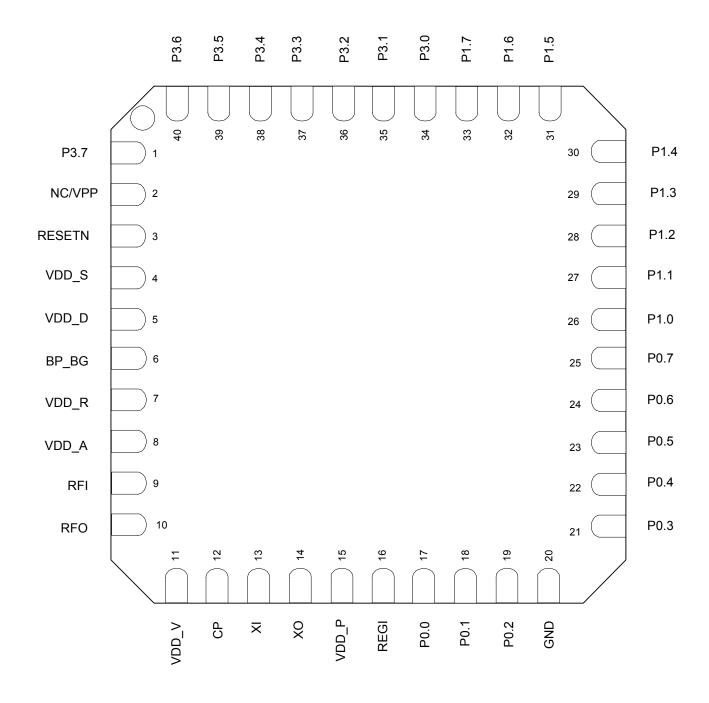

## 4. Pin Configurations

Fig 4-1. A8106 QFN 5x5 Package Top View

## 2.4GHz FSK/GFSK SoC

5. Pin Description (I: input; O: output, I/O: input or output)

|         |         |        | output, I/O: Input or output)                                                              |

|---------|---------|--------|--------------------------------------------------------------------------------------------|

| Pin No. | Symbol  | I/O    | Function Description                                                                       |

| 1       | P3.7    | DIO/AI | RTC_O                                                                                      |

| 2       | NC/VPP  | Al     | No connection for A8105F4 / High voltage for OTP program for A8105T3 ( VPP = 6.5V typical) |

| 3       | RESETN  | DI     | RESETN                                                                                     |

| 4       | VDD_S   | AO     | Voltage supply for SARM                                                                    |

| 5       | VDD_D   | AO     | VDD_D                                                                                      |

| 6       | BP_BG   | AO     | BP_BG                                                                                      |

| 7       | VDD_R   | AO     | VDD_R                                                                                      |

| 8       | VDD_A   | AO     | VDD_A                                                                                      |

| 9       | RFI     | Al     | RFI                                                                                        |

| 10      | RFO     | AO     | RFO                                                                                        |

| 11      | VDD_VCO | Al     | VDD_VCO                                                                                    |

| 12      | CP      | AO     | CP                                                                                         |

| 13      | ΧI      | Al     | XI                                                                                         |

| 14      | XO      | AO     | XO                                                                                         |

| 15      | VDD_PLL | AO     | VDD_PLL                                                                                    |

| 16      | REGI    | Al     | REGI                                                                                       |

| 17      | P0.0    | DIO    | SPI_SCLK                                                                                   |

| 18      | P0.1    | DIO    | SPI_MOSI                                                                                   |

| 19      | P0.2    | DIO    | SPI_MISO                                                                                   |

| 20      | GND     | DIO    | GND                                                                                        |

| 21      | P0.3    | DIO    | SPI_SSEL                                                                                   |

| 22      | P0.4    | DIO    | GPIO/ ICE mode                                                                             |

| 23      | P0.5    | DIO    | I2C_SCL                                                                                    |

| 24      | P0.6    | DIO    | I2C_SDA                                                                                    |

| 25      | P0.7    | DIO    | INT2 /GIO1                                                                                 |

| 26      | P1.0    | DIO    | Timer2_T2                                                                                  |

| 27      | P1.1    | DIO    | Timer2_T2EX                                                                                |

| 28      | P1.2    | DIO    | INT3 /GIO2                                                                                 |

| 29      | P1.3    | DIO    | INT4/ CKO                                                                                  |

| 30      | P1.4    | DIO    | TTAG_TTDIO                                                                                 |

| 31      | P1.5    | DIO    | TTAG_TTCK                                                                                  |

| 32      | P1.6    | DIO    | PWM0/ADC4                                                                                  |

| 33      | P1.7    | DIO    | PWM1/ADC5                                                                                  |

| 34      | P3.0    | DIO    | UART0_RX/ADC6                                                                              |

| 35      | P3.1    | DIO    | UART0_TX/ADC7                                                                              |

| 36      | P3.2    | DIO/AI | INT0/ADC0                                                                                  |

| 37      | P3.3    | DIO/AI | INT1/ADC1                                                                                  |

| 38      | P3.4    | DIO/AI | Timer0_T0/ADC2                                                                             |

| 39      | P3.5    | DIO/AI | Timer1_T1/ADC3                                                                             |

| 40      | P3.6    | DIO/AI | RTC_I                                                                                      |

аміссом 笙科電子總代理 深圳奇翰電子

## 2.4GHz FSK/GFSK SoC

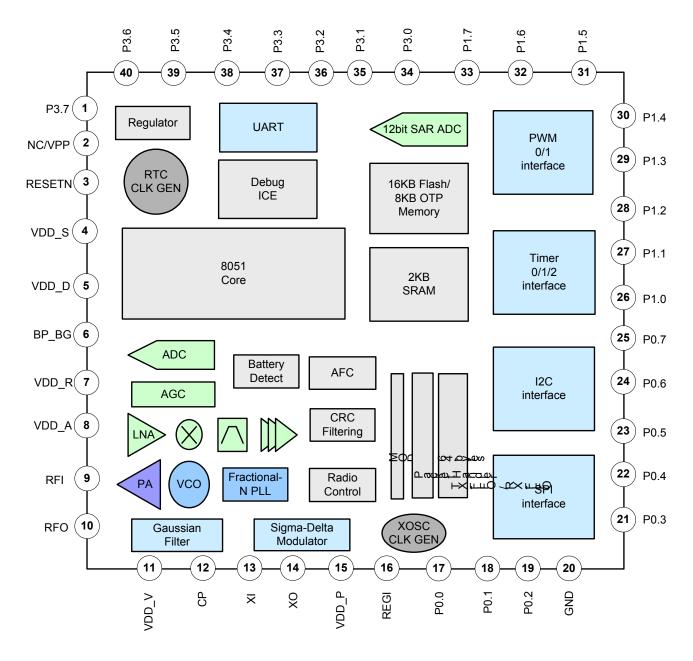

## 6. Chip Block Diagram

Fig 6-1. A8106 Block Diagram

## 2.4GHz FSK/GFSK SoC

## 7. Absolute Maximum Ratings

| Parameter                        | With respect to | Rating         | Unit |

|----------------------------------|-----------------|----------------|------|

| Supply voltage range (VDD)       | GND             | -0.3 ~ 3.6     | V    |

| Digital IO pins range            | GND             | -0.3 ~ VDD+0.3 | V    |

| Voltage on the analog pins range | GND             | -0.3 ~ 2.1     | V    |

| Input RF level                   |                 | 14             | dBm  |

| Storage Temperature range        |                 | -55 ~ 125      | °C   |

| ESD Rating                       | НВМ             | ± 2K           | V    |

|                                  | MM              | ± 100          | V    |

<sup>\*</sup>Stresses above those listed under "Absolute Maximum Rating" may cause permanent damage to the device. These are stress ratings only; functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

<sup>\*</sup>Device is ESD sensitive. Use appropriate ESD precautions. HBM (Human Body Mode) is tested under MIL-STD-883F Method 3015.7. MM (Machine Mode) is tested under JEDEC EIA/JESD22-A115-A. \*Device is Moisture Sensitivity Level III (MSL 3).

**АМІССОМ** 笙科電子總代理 深圳奇翰電子

## 2.4GHz FSK/GFSK SoC

## 8. Electrical Specification

(Ta=25 $^{\circ}$ C, **REGI = 3.3V, internal regulator voltage = 1.8V,** unless otherwise noted)

| Parameter                               | Description                                           | Min. | Type            | Max.   | Unit     |

|-----------------------------------------|-------------------------------------------------------|------|-----------------|--------|----------|

| General                                 |                                                       |      |                 |        |          |

| Operating Temperature                   |                                                       | -40  |                 | 85     | °C       |

| Supply Voltage (VDD)                    | Regulator supply input                                | 2.0  | 3.3             | 3.6    | V        |

| Current Consumption                     | PM3 without Sleep timer                               |      | 0.8             |        | uA       |

| (MCU only, RF in sleep mode)            | PM3 with Sleep timer                                  |      | 2               |        | uA       |

|                                         | PM2 with Sleep timer                                  |      | 3               |        | uA       |

|                                         | PM1 with Sleep timer                                  |      | 3               |        | uA       |

|                                         | Normal                                                |      | 2.5             |        | mA       |

| Current Consumption                     | Standby Mode                                          |      | 3.8             |        | mA       |

| (RF with MCU in normal mode)            | PLL Mode                                              |      | 10              |        | mA       |

|                                         | RX Mode                                               |      | 16              |        | mA       |

|                                         | TX Mode (@-6dBm output)                               |      | 16.5            |        | mA       |

|                                         | TX Mode (@2dBm output)                                |      | 20              |        | mA       |

|                                         | TX Mode (@4dBm output)                                |      | 24              |        | mA       |

| Synthesizer block (includes cry         | stal oscillator, PLL and VCO.)                        |      |                 |        |          |

| Crystal start up time                   | Idle to standby (Xtal, 49US type, is stable at 40ppm) |      | 0.6             |        | ms       |

| Crystal frequency                       |                                                       |      | 16              |        | MHz      |

| Crystal ESR                             |                                                       |      |                 | 80     | ohm      |

| VCO Operation Frequency                 |                                                       | 2400 |                 | 2483.5 | MHz      |

| PLL phase noise                         | Offset 100k<br>Offset 500K<br>Offset 1M               |      | 80<br>95<br>105 |        | dBc      |

| PLL settling time                       | @Loop BW = 100Khz                                     |      | 75              |        | μS       |

| тх                                      |                                                       |      | <u> </u>        |        | <u> </u> |

| Output power range                      |                                                       | -10  | 0               | +4     | dBm      |

| Out Band Spurious Emission <sup>1</sup> | 30MHz~1GHz                                            |      |                 | -36    | dBm      |

| ·                                       | 1GHz~12.75GHz                                         |      |                 | -30    | dBm      |

|                                         | 1.8GHz~ 1.9GHz                                        |      |                 | -47    | dBm      |

|                                         | 5.15GHz~ 5.3GHz                                       |      |                 | -47    | dBm      |

| Frequency deviation                     | 500Kbps                                               |      | 186K            |        | Hz       |

| . ,                                     | 250Kbps                                               |      | 93K             |        | Hz       |

| Data rate                               | ·                                                     | 4K   |                 | 500K   | Bps      |

| TX settling time                        | Loop bandwidth 100K                                   |      | 70              |        | μS       |

| RX                                      |                                                       |      |                 |        |          |

|                                         | Data rate 500K (F <sub>IF</sub> = 1MHz)               |      | -99             |        | dBm      |

|                                         | Data rate 25K (F <sub>IF</sub> = 1MHz)                |      | -104            |        | dBm      |

|                                         | Data rate 4K (F <sub>IF</sub> = 500KHz)               |      | -107            |        | dBm      |

| IF frequency bandwidth                  |                                                       |      | 300/600         |        | KHz      |

| IF center frequency                     |                                                       |      | 250/1000        |        | KHz      |

| Interference                            | Co-Channel (C/I <sub>0</sub> )                        |      | 11              |        | dB       |

|                                         | ±1MHz Adjacent Channel                                |      | -20             |        | dB       |

## 2.4GHz FSK/GFSK SoC

|                                              | ±2MHz Adjacent Channel     |         | -30   |         | dB  |

|----------------------------------------------|----------------------------|---------|-------|---------|-----|

|                                              | > ±5MHz Adjacent Channel   |         | -40   |         | dB  |

|                                              | Image (C/I <sub>IM</sub> ) |         | -12   |         | dB  |

| Maximum Operating Input Power                | @RF input (BER=0.1%)       |         |       | 0       | dBm |

| Spurious Emission                            | 30MHz~1GHz                 |         |       | -52     | dBm |

|                                              | 1GHz~12.75GHz              |         |       | -47     | dBm |

| RSSI Range with AGC turn on                  | @RF input                  | -100    |       | -10     | dBm |

| 12Bit SAR ADC                                |                            |         |       |         |     |

| Input voltage range                          |                            | 0       |       | 1.8     | V   |

| External reference voltage                   |                            |         | 1.8   |         | V   |

| Input capacitor                              |                            |         | 25    |         | pF  |

| Bandwidth                                    |                            |         | 200   |         | KHz |

| EOB, effective number of bits                |                            |         | 10    |         | bit |

| INL                                          |                            |         | +/- 2 |         | LSB |

| DNL                                          |                            |         | +/-1  |         | LSB |

| Conversion time                              |                            | 128     |       | 8       | uS  |

| Current consumption                          |                            |         | 0.4   |         | mA  |

| Regulator                                    |                            |         |       |         |     |

| Regulator settling time                      | Pin 19 connected to 1nF    |         | 200   |         | μS  |

| Band-gap reference voltage                   |                            |         | 1.21  |         | V   |

| Regulator output voltage                     |                            |         | 1.8   |         | V   |

| Digital IO DC characteristics                |                            |         |       |         |     |

| High Level Input Voltage (V <sub>IH</sub> )  |                            | 0.8*VDD |       | VDD     | V   |

| Low Level Input Voltage (V <sub>IL</sub> )   |                            | 0       |       | 0.2*VDD | V   |

| High Level Output Voltage (V <sub>OH</sub> ) | @I <sub>OH</sub> = -0.5mA  | VDD-0.4 |       | VDD     | V   |

| Low Level Output Voltage (V <sub>OL</sub> )  | @I <sub>OL</sub> = 0.5mA   | 0       |       | 0.4     | V   |

**АМІССОМ 笙科電子總代理** 深圳奇翰電子

### 2.4GHz FSK/GFSK SoC

## 9. SFR & RFR(Radio Frequency Register)

A8106 contains standard 8051 SFRs(special function registers) and RFR (RF control registers). A8051's SFR location is almost the same as the standard 8052 SFR location. RFR is Radio Frequency Registers are located in XDATA spaces and located in 0x0800 ~ 0x08FF. For more detail information, please reference Section 9.2.

### 9.1 SFR Overview

Table 9.1 A8106 Special Function Registers (SFRs) table

|      | 0/8   | 1/9     | 2/A       | 3/B     | 4/C    | 5/D    | 6/E     | 7/F    |

|------|-------|---------|-----------|---------|--------|--------|---------|--------|

| 0xF8 | EIP   | OSCCON  |           |         |        |        |         |        |

| 0xF0 | В     | I2CSADR | I2CSCR    | I2CSBUF | I2CMSA | I2CMCR | I2CMBUF | I2CMTP |

| 0xE8 | EIE   |         |           |         | SPCR   | SPSR   | SPDR    | SSCR   |

| 0xE0 | ACC   | P3OE    | P3PUN     | P3WUN   | SPCR1  | SPSR1  | SPDR1   | SSCR1  |

| 0xD8 | WDCON | P1OE    | P1PUN     | P1WUN   |        |        |         |        |

| 0xD0 | PSW   | P0OE    | P0PUN     | P0WUN   |        |        |         |        |

| 0xC8 | T2CON | T2IF    | RLDL      | RLDH    | TL2    | TH2    |         |        |

| 0xC0 |       |         |           |         |        |        |         |        |

| 0xB8 | IP    | PCONE   | RSFLAG    | IOSEL   | ADCCH  |        |         |        |

| 0xB0 | P3    | PWM1CON | PWM1H     | PWM1L   |        |        |         |        |

| 0xA8 | IE    | PWM0CON | PWM0H     | PWM0L   |        |        |         |        |

| 0xA0 | P2    |         |           |         |        |        |         |        |

| 0x98 | SOCN0 | SBUF0   | FLASHCTRL | FLASHMR |        |        |         |        |

| 0x90 | P1    | EIF     |           |         |        |        |         |        |

| 0x88 | TCON  | TMOD    | TL0       | TL1     | TH0    | TH1    | CKCON   |        |

| 0x80 | P0    | SP      | DPL0      | DPH0    | DPL1   | DPH1   | DPS     | PCON   |

: It means bit-addressable :: It means reserved.

Following are description of SFRs related to the operation of A8106 System Controller. Detailed descriptions of the remaining SFRs are including the sections of the datasheet associated with their corresponding system function. The arithmetic section of the processor performs extensive data manipulation and is comprised of the 8-bit arithmetic logic unit (ALU), an ACC(0xE0) register, B(0xF0) register and PSW(0xD0) register.

PSW (Address: D0h)

| Address/Name | R/W | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|--------------|-----|-------|-------|-------|-------|-------|-------|-------|-------|

| D0h<br>PSW   | R/W | CY    | AC    | F0    | RS1   | RS2   | OV    | F1    | Р     |

| Reset        |     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

Program Status Word register

The ALU performs typical arithmetic operations as: addition, subtraction, multiplication, division and additional operations such as: increment, decrement, BCD-decimal-add-adjust and compare. Within logic unit are performance: AND, OR, Exclusive OR, complement and rotation. The Boolean processor performance the bit operations as: set, clear, complement, jump-if-not-set, jump-if-set-and-clear and move to/from carry.

## 2.4GHz FSK/GFSK SoC

CY - Carry flag

AC - Auxiliary carry

F0 - General purpose flag 0

RS[1:0] - Register bank select bits

| RS[1:0] | Function description             |

|---------|----------------------------------|

| 00      | - Bank 0, data address 0x00-0x07 |

| 01      | - Bank 1, data address 0x08-0x0F |

| 10      | - Bank 2, data address 0x10-0x17 |

| 11      | - Bank 3, data address 0x18-0x1F |

**OV** - Overflow flag

F1 - General purpose flag 1

P - Parity flag

The PSW contains several bits that reflect the current state of the CPU.

ACC (Address: E0h)

| Address/Name | R/W | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|--------------|-----|-------|-------|-------|-------|-------|-------|-------|-------|

| E0h<br>ACC   | R/W |       |       |       |       |       |       |       |       |

| Reset        |     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

Accumulator ACC Register

B (Address: F0h)

| Address/Name | R/W | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|--------------|-----|-------|-------|-------|-------|-------|-------|-------|-------|

| F0h<br>B     | R/W |       |       |       |       |       |       |       |       |

| Reset        |     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

B Register

The B register is used during multiply and divide operations. In other cases may be used as normal SFR.

# 2.4GHz FSK/GFSK SoC

## 9.2 RFR Overview

| Address /<br>Name      | R/W | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1    | Bit 0   |

|------------------------|-----|---------|---------|---------|---------|---------|---------|----------|---------|

| 0x800h                 | W   | RESETN  | FWPRN   | FRPRN   | ADC12RN |         | BFCRN   |          |         |

| MODE                   | R   | 1       | FECF    | CRCF    | CER     | XER     | PLLER   | TRSR     | TRER    |

| 0x801h                 | W   | STRB7   | STRB6   | STRB5   | STRB4   | STRB3   | STRB2   | STRB1    | STRB0   |

| MODEC1                 | R   | ARCWTR  | P_CKO   | P_G01   | P_G02   | FPF     |         |          |         |

| 0x802h                 | W   | DDPC    | ARSSI   | AIF     | DFCD    | WWSE    | FMT     | FMS      | ADCM    |

| MODEC2                 | R   | DDPC    | ARSSI   | AIF     | CD      | WWSE    | FMT     | FMS      | ADCM    |

| 0x803h<br>CALC         | R/W | -       | -       | -       | -       | RSSC    | VCC     | VBC      | FBC     |

| 0x804h<br>FIFO I       | W   | FEP7    | FEP6    | FEP5    | FEP4    | FEP3    | FEP2    | FEP1     | FEP0    |

| 0x805h<br>FIFO II      | W   | FPM1    | FPM0    | PSA5    | PSA4    | PSA3    | PSA2    | PSA1     | PSA0    |

| 0x806h                 | W   | WWS_SL7 | WWS_SL6 | WWS_SL5 | WWS_SL4 | WWS_SL3 | WWS_SL2 | WWS_SL1  | WWS_SL0 |

| RC OSCI                | R   | _       | _       | _       | _       | _       | _       | _        | _       |

| 0x807h<br>RC OSC II    | W   | WWS_SL9 | WWS_SL8 | WWS_AC5 | WWS_AC4 | WWS_AC3 | WWS_AC2 | WWS_AC1  | WWS_AC0 |

| 0x808h<br>RC OSC III   | W   | BBCKS1  | BBCKS0  | WWS_AC8 | WWS_AC7 | WWS_AC6 | RCTS    | TSEL     | TWOR_E  |

| 0x809h<br>CKO Pin      | W   | ECKOE   | CKOS3   | CKOS2   | CKOS1   | CKOS0   | CKOI    | WAKEBBIE | INTT1IE |

| 0x80Ah<br>GPIO1 Pin I  | W   | -       | -       | GIO1S3  | GIO1S2  | GIO1S1  | GIO1S0  | GIO1I    | GIO10E  |

| 0x80Bh<br>GPIO2 Pin II | W   | -       | -       | GIO2S3  | GIO2S2  | GIO2S1  | GIO2S0  | GIO2I    | GIO2OE  |

| 0x80Ch<br>Clock        | R/W | GRC3    | GRC2    | GRC1    | GRC0    | CSC1    | CSC0    | CGS      | XS      |

| 0x80Dh<br>Data rate    | R/W | SDR7    | SDR6    | SDR5    | SDR4    | SDR3    | SDR2    | SDR1     | SDR0    |

| 0x80Eh<br>PLL I        | R/W | CHN7    | CHN6    | CHN5    | CHN4    | CHN3    | CHN2    | CHN1     | CHN0    |

| 0x80Fh<br>PLL II       | R/W | DBL     | RRC1    | RRC0    | CHR3    | CHR2    | CHR1    | CHR0     | IP8     |

| 0x810h<br>PLL III      | R/W | IP7     | IP6     | IP5     | IP4     | IP3     | IP2     | IP1      | IP0     |

| 0x811h                 | W   | FP15    | FP14    | FP13    | FP12    | FP11    | FP10    | FP9      | FP8     |

| PLL IV                 | R   | RAC15   | RAC14   | RAC13   | RAC12   | RAC11   | RAC10   | RAC9     | RAC8    |

| 0x812h                 | W   | FP7     | FP6     | FP5     | FP4     | FP3     | FP2     | FP1      | FP0     |

| PLL V                  | R   | RAC7    | RAC6    | RAC5    | RAC4    | RAC3    | RAC2    | RAC1     | RAC0    |

| 0x813h<br>TX I         | W   | TXSM1   | TXSM0   | TXDI    | TME     | FS      | FDP2    | FDP1     | FDP0    |

| 0x814h<br>TX II        | W   | FD5     | PDV1    | PDV0    | FD4     | FD3     | FD2     | FD1      | FD0     |

| 0x815h<br>Delay I      | W   | DPR2    | DPR1    | DPR0    | TDL1    | TDL0    | PDL2    | PDL1     | PDL0    |

| 0x816h<br>Delay II     | W   | WSEL2   | WSEL1   | WSEL0   | AGC_D1  | AGC_D0  | RS_DLY2 | RS_DLY1  | RS_DLY0 |

| 0x817h<br>RX           | W   | QDLS    | RXSM1   | RXSM0   | AFC     | RXDI    | DMG     | BWS      | ULS     |

| 0x818h<br>RX Gain I    | R/W | MVGS    | AGLNE   | IGC     | MGC1    | MGC0    | LGC2    | LGC1     | LGC0    |

| 0x819h                 | W   | RH7     | RH6     | RH5     | RH4     | RH3     | RH2     | RH1      | RH0     |

| RX Gain II             | R   | RHR7    | RHR6    | RHR5    | RHR4    | RHR3    | RHR2    | RHR1     | RHR0    |

| 0x81Ah                 | W   | RL7     | RL6     | RL5     | RL4     | RL3     | RL2     | RL1      | RL0     |

| RX Gain III            | R   | RLR7    | RLR6    | RLR5    | RLR4    | RLR3    | RLR2    | RLR1     | RLR0    |

| 0x81Bh                 |     |         |         |         |         |         |         |          |         |

| RX Gain IV             | W   | ENGC    | CRCD    | MVSEL1  | MVSEL0  | MHC     | LHC1    | LHC0     | VGCE    |

## 2.4GHz FSK/GFSK SoC

| 0x81Ch                                      | W      | RTH7    | RTH6                     | RTH5    | RTH4    | RTH3   | RTH2   | RTH1   | RTH0   |  |  |

|---------------------------------------------|--------|---------|--------------------------|---------|---------|--------|--------|--------|--------|--|--|

| RSSI Threshold                              | R      | ADC7    | ADC6                     | ADC5    | ADC4    | ADC3   | ADC2   | ADC1   | ADC0   |  |  |

| 0x81Dh<br>ADC                               | W      | RSM1    | RSM0                     | ERSS    | FSARS   | -      | XADS   | RSS    | CDM    |  |  |

| 0x81Eh<br>Code I                            | W      | CRC16   | MCS                      | WHTS    | FECS    | CRCS   | IDL    | PML1   | PML0   |  |  |

| 0x81Fh<br>Code II                           | W      | ETH2    | DCL2                     | DCL1    | DCL0    | ETH1   | ETH0   | PMD1   | PMD0   |  |  |

| 0x820h<br>Code III                          | W      | WHT9    | WS6                      | WS5     | WS4     | WS3    | WS2    | WS1    | WS0    |  |  |

| 0x821h                                      | W      | -       | -                        | -       | MFBS    | MFB3   | MFB2   | MFB1   | MFB0   |  |  |

| IF Calibration I                            | R      | -       | -                        | -       | FBCF    | FB3    | FB2    | FB1    | FB0    |  |  |

| 0x822h<br>IF Calibration II                 | R      | -       | -                        |         | FCD4    | FCD3   | FCD2   | FCD1   | FCD0   |  |  |

| 0x823h                                      | W      | -       | -                        | VCCS    | MVCS    | VCOC3  | VCOC2  | VCOC1  | VCOC0  |  |  |

| VCO current<br>Calibration                  | R      | -       | -                        | -       | FVCC    | VCB3   | VCB2   | VCB1   | VCB0   |  |  |

| 0x824h                                      | W      | -       | -                        | -       | -       | MVBS   | MVB2   | MVB1   | MVB0   |  |  |

| VCO Single band<br>Calibration I            | R      | -       | -                        | DVT1    | DVT0    | VBCF   | VB2    | VB1    | VB0    |  |  |

| 0x825h<br>VCO Single band<br>Calibration II | W      | -       | -                        | VTH2    | VTH1    | VTH0   | VTL2   | VTL1   | VTL0   |  |  |

| 0x826h                                      | W      |         | RGV1                     | RGV0    | QDS     | BVT2   | BVT1   | BVT0   | BDS    |  |  |

| Battery detect                              | R      |         | RGV1                     | RGV0    | BDF     | BVT2   | BVT1   | BVT0   | BDS    |  |  |

| 0x827h<br>TX test                           | W      | FD7     | FD6                      | TXCS    | PAC1    | PAC0   | TBG2   | TBG1   | TBG0   |  |  |

| 0x828h<br>Rx DEM test I                     | W      | DMT     | DCM1                     | DCM0    | MLP1    | MLP0   | SLF2   | SLF1   | SLF0   |  |  |

| 0x829h<br>Rx DEM test II                    | W      | DCV7    | DCV6                     | DCV5    | DCV4    | DCV3   | DCV2   | DCV1   | DCV0   |  |  |

| 0x82Ah<br>CPC                               | W      | RCOSCS  |                          |         |         |        | LVR    | CPC1   | CPC0   |  |  |

| 0x82Bh<br>Crystal test                      | W      | RSIS    | PKT1                     | PKT0    | PKS     | DBD    | XCC    | XCP1   | XCP0   |  |  |

| 0x82Ch<br>PLL test                          | W      | PRS     | PMPE                     | PRIC1   | PRIC0   | PRRC1  | PRRC0  | SDPW   | NSDO   |  |  |

| 0x82Dh<br>VCO test I                        | W      | MQDL    | FIFOREV                  | IDREV   | TLB     | TLB    | RLB    | RLB    | VCBS   |  |  |

| 0x82Eh<br>VCO test II                       | W      | BREV    |                          |         | XEC     | RFT3   | RFT2   | RFT1   | RFT0   |  |  |

| 0x82Fh<br>IFAT                              | W      | IGFI2   | IGFI1                    | IGFI0   | IGFQ2   | IGFQ1  | IGFQ0  | IFBC   | LIMC   |  |  |

| 0x830h<br>Rscale                            | R/W    | RSC7    | RSC6                     | RSC5    | RSC4    | RSC3   | RSC2   | RSC1   | RSC0   |  |  |

| 0x831h<br>TMV                               | W      | PRES    | TRT2                     | TRT1    | TRT0    | ASMV2  | ASMV1  | ASMV0  | AMVS   |  |  |

| 0x832h<br>SYNC                              | W      | RNUM1_2 | RNUM1_1                  | RNUM1_0 | RCK_sel | CKSEL1 | CKSEL0 | MRCKS  | SYNCS  |  |  |

| 0x833h<br>DET                               | W      | DC_SEL  | RXDCS                    | PREDN2  | PREDN1  | PREDN0 | PREUP2 | PREUP1 | PREUP0 |  |  |

| 0x834h<br>DC                                | W<br>R |         | DC_SHIFT[7:0] DCOUT[7:0] |         |         |        |        |        |        |  |  |

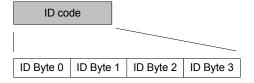

| 0x835h<br>ID0                               | W/R    | ID31    | ID30                     | ID29    | ID28    | ID27   | ID26   | ID25   | ID24   |  |  |

| 0x836h<br>ID1                               | W/R    | ID23    | ID22                     | ID21    | ID20    | ID19   | ID18   | ID17   | ID16   |  |  |

| 0x837h<br>ID2                               | W/R    | ID15    | ID14                     | ID13    | ID12    | ID11   | ID10   | ID9    | ID8    |  |  |

## 2.4GHz FSK/GFSK SoC

| 0x838h<br>ID3      | W/R    | ID7     | ID6                                 | ID5     | ID4      | ID3            | ID2      | ID1      | ID0          |  |  |

|--------------------|--------|---------|-------------------------------------|---------|----------|----------------|----------|----------|--------------|--|--|

| 0x839h<br>DID0     | R      | DID31   | DID30                               | DID29   | DID28    | DID27          | DID26    | DID25    | DID24        |  |  |

| 0x83Ah<br>DID1     | R      | DID23   | DID22                               | DID21   | DID20    | DID19          | DID18    | DID17    | DID16        |  |  |

| 0x83Bh<br>DID2     | R      | DID15   | DID14                               | DID13   | DID12    | DID11          | DID10    | DID9     | DID8         |  |  |

| 0x83Ch<br>DID3     | R      | DID7    | DID6                                | DID5    | DID4     | DID3           | DID2     | DID1     | DID0         |  |  |

| 0x83Dh<br>PWRCTL0  | W      | CBG2    | CBG1                                | CBG0    | PDNS     | STA            | ENDL2    | ENDL1    | ENDL0        |  |  |

| 0x83Eh<br>PWRCTL1  | W      | EBOD    | ENAV                                | QDSA    | ENDV     | QDSD           | CEL      | SVREF    | CELA         |  |  |

| 0x83Fh<br>PWRCTL2  | W      | P3PUNIE |                                     | RGS     |          |                | RGC1     | RGC0     | RCHC         |  |  |

| 0x840h             | W      |         | RCOT[2:0]                           |         | WCKS     | EI [1·0]       | MVS      | :[1:0]   | ENCAL        |  |  |

|                    |        |         |                                     | 1[44.0] | WORG     | [1.0]          |          |          |              |  |  |

| RC OSC 4           | R      |         | NUMLI                               | H[11:8] | 1        |                | RCO      | J[9:8]   | ENCAL        |  |  |

| 0x841h<br>RC OSC 5 | W      | MRCT9   | MRCT8                               | GPDFL2  | GQDSFL2  | OTP1M_S<br>EL  | TMRE     | MAN      | MCALS        |  |  |

| KC 030 3           | R      | NUMLH7  | NUMLH6                              | NUMLH5  | NUMLH4   | NUMLH3         | NUMLH2   | NUMLH1   | NUMLH0       |  |  |

| 0x842h             | W      | MRCT7   | MRCT6                               | MRCT5   | MRCT4    | MRCT3          | MRCT2    | MRCT1    | MRCT0        |  |  |

| RC OSC 6           | R      | RCOC7   | RCOC6                               | RCOC5   | RCOC4    | RCOC3          | RCOC2    | RCOC1    | RCOC0        |  |  |

| 0x843h             | 11     | 110007  |                                     |         |          |                |          |          |              |  |  |

| RC OSC 7           | W      | PDNFHR  | IR QDSFHR PDNFLR QDSFLR TGNUM[11:8] |         |          |                |          |          |              |  |  |

| 0x844h<br>RC OSC 8 | W      |         |                                     |         | TGNU     | M[7:0]         |          |          |              |  |  |

| 0x845h<br>TMRITV1  | W      |         |                                     |         | TMR_IT   | TV[15:8]       |          |          |              |  |  |

| 0x846h<br>TMRITV2  | W      |         |                                     |         | TMR_I    | TV[7:0]        |          |          |              |  |  |

| 0x847h<br>TMRWOR1  | W      |         |                                     | -       | TMR_OFS4 | TMR_OFS3       | TMR_OFS2 | TMR_OFS1 | TMR_OFS0     |  |  |

| 0x848h             | W      | TMRON   | TMRIE                               | TMRIF   | TMRCOR   | TMRWOR         | TMRCKS1  | TMRCKS0  | TMR_CE       |  |  |

| TMRCTL             | R      |         | TMRIE                               | TMRIF   |          |                | TMRCKS1  | TMRCKS0  | TMR_CE       |  |  |

| 0x849h<br>RF Test1 | W      |         |                                     |         | FBG4     | FBG3           | FBG2     | FBG1     | FBG0         |  |  |

| 0x84Ah<br>RF Test2 |        |         |                                     | STM5    | STM4     | STM3           | STM2     | STM1     | STM0         |  |  |

| 0x84Bh             | W      | BUFS    | CKS1                                | CKS0    | MODE     | MVS2           | MVS1     | MVS0     | ADCE         |  |  |

| ADCCTL             | R      |         |                                     |         | MODE     | MVS2           | MVS1     | MVS0     | ADCE         |  |  |

| l                  |        | ADCIE   |                                     |         |          | ADIVL          | ADCYC    | ENADC    |              |  |  |

| 0x84Ch<br>ADCAVG1  | W<br>R | MVADC11 | MVADC10                             | MVADC9  | MVADC8   | ADIVL<br>ADC11 | ADC10    | ADC9     | DTMP<br>ADC8 |  |  |

| 0x84Dh<br>ADCAVG2  | R      | MVADC7  | MVADC6                              | MVADC5  | MVADC4   | MVADC3         | MVADC2   | MVADC1   | MVADC0       |  |  |

| 0x84Eh<br>ADCAVG3  | R      | ADC7    | ADC6                                | ADC5    | ADC4     | ADC3           | ADC2     | ADC1     | ADC0         |  |  |

|                    |        |         |                                     |         |          |                |          |          |              |  |  |

Legend: - = unimplemented

## 2.4GHz FSK/GFSK SoC

### 9.2.1 Mode Register (Address: 0x800h)

| Name  | R/W | Bit 7  | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-----|--------|-------|-------|---------|-------|-------|-------|-------|

| Mode  | R   | RESETN | FWPRN | FRPRN | ADC12RN |       | BFCRN |       |       |

| Mode  | W   | -      | FECF  | CRCF  | CER     | XER   | PLLER | TRSR  | TRER  |

| Reset |     |        |       |       |         |       |       |       |       |

RESETN: Write to this register by 0x00 to issue reset command, then it is auto clear

FWPRN: FIFO Write Point Software Reset.

FRPRN: FIFO Read Point Software Reset.

ADC12RN: 12-bits ADC Software Reset.

BFCRN: IF Filter Bank Calibration Software Reset.

FECF: FEC flag.

[0]: FEC pass. [1]: FEC error.

CRCF: CRC flag.

[0]: CRC pass. [1]: CRC error.

CER: RF chip enable status.

[0]: RF chip is disabled. [1]: RF chip is enabled.

XER: Internal crystal oscillator enabled status.

[0]: Crystal oscillator is disabled. [1]: Crystal oscillator is enabled.

PLLER: PLL enabled status.

[0]: PLL is disabled. [1]: PLL is enabled.

TRSR: TRX Status Register.

[0]: RX state. [1]: TX state.

Serviceable if TRER=1 (TRX is enable).

TRER: TRX state enabled status.

[0]: TRX is disabled. [1]: TRX is enabled.

#### 9.2.2 Mode Control Register 1 (Address: 0x801h)

| Name   | R/W | Bit 7  | Bit 6 | Bit 5   | Bit 4   | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|--------|-----|--------|-------|---------|---------|-------|-------|-------|-------|

| MODEC1 | W   | STRB7  | STRB6 | STRB5   | STRB4   | STRB3 | STRB2 | STRB1 | STRB0 |

| MODECT | R   | ARCWTR | P_CKO | P_IRQ10 | P_IRQ20 | FPF   |       |       |       |

| Reset  |     | 1      | 0     | 1       | 0       | 0     | 0     | 0     | 0     |

STRB[7:0]: Strobe command register.

[80]: Sleep mode.

[90]: Idle mode.

[A0]: Standby mode.

[B0]: PLL mode.

[C0]: TX mode.

[D0]: RX mode.

Reverse for other settings.

ARCWTR: Read ARCWTR output signal.

P\_CKO: Read P\_CKO pin output signal.

P\_IRQ10: Read P\_IRQ10 pin output signal.

### 2.4GHz FSK/GFSK SoC

P\_IRQ2O: Read P\_IRQ2O pin output signal.

FPF: Read FIFO pointer flag output singal.

#### 9.2.3 Mode Control Register 2 (Address: 0x802h)

| Name           | R/W | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------------|-----|-------|-------|-------|-------|-------|-------|-------|-------|

| Mode Control I | R   | DDPC  | ARSSI | AIF   | DFCD  | WWSE  | FMT   | FMS   | ADCM  |

|                | W   | DDPC  | ARSSI | AIF   | CD    | WWSE  | FMT   | FMS   | ADCM  |

| Reset          |     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

DDPC (Direct mode data pin control): Direct mode modem data can be accessed via SDIO pin when this register is enabled.

[0]: Disable. [1]: Enable.

ARSSI: Auto RSSI measurement while entering RX mode.

[0]: Disable. [1]: Enable.

AIF (Auto IF Offset): RF LO frequency will auto offset one IF frequency while entering RX mode.

[0]: Disable. [1]: Enable.

CD / DFCD:

DFCD (Data Filter by CD): The received package will be filtered out if Carrier Detector signal is inactive.

[0]: Disable. [1]: Enable.

CD (Read): Carrier detector signal.

[0]: Input power below threshold. [1]: Input power above threshold.

WWSE: Reserved for internal usage only. Shall be set to [0].

FMT: Reserved for internal usage only. Shall be set to [0].

FMS: Direct/FIFO mode select. [0]: Direct mode. [1]: FIFO mode.

ADCM: ADC measurement enable (Auto clear when done).

[0]: Disable measurement or measurement finished. [1]: Enable measurement.

| ADCM | A8106 @ Standby mode                                 | A8106 @ RX mode              |

|------|------------------------------------------------------|------------------------------|

| [0]  | Disable ADC                                          | Disable ADC                  |

| [1]  | Measure temperature, external Analog Digital Convert | Measure RSSI, carrier detect |

#### 9.2.4 Calibration Control Register (Address: 0x803h)

|                 |     | <u> </u> |       |       | ,     |       |       |       |       |

|-----------------|-----|----------|-------|-------|-------|-------|-------|-------|-------|

| Name            | R/W | Bit 7    | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| Mode Control II | R/W |          |       |       |       | RSSC  | VCC   | VBC   | FBC   |

| Reset           |     |          |       |       |       | 0     | 0     | 0     | 0     |

VCC: VCO Current calibration enable (Auto clear when done).

[0]: Disable. [1]: Enable.

VBC: VCO Bank calibration enable (Auto clear when done).

[0]: Disable. [1]: Enable.

FBC: IF Filter Bank calibration enable (Auto clear when done).

[0]: Disable. [1]: Enable.

RSSC: RSSI calibration enable (Auto clear when done).

[0]: Disable. [1]: Enable.

### 9.2.5FIFO Register I (Address: 0x804h)

| Name   | R/W | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|--------|-----|-------|-------|-------|-------|-------|-------|-------|-------|

| FIFO I | W   | FEP7  | FEP6  | FEP5  | FEP4  | FEP3  | FEP2  | FEP1  | FEP0  |

## 2.4GHz FSK/GFSK SoC

| Deset | ^ | ^ | 1   | 1 | 4 | 4 | 4   | 4 |

|-------|---|---|-----|---|---|---|-----|---|

| Reset | U | U | l l |   | I | I | l l | 1 |

FEP [7:0]: FIFO End Pointer for TX FIFO and Rx FIFO.

#### 9.2.6 FIFO Register II (Address: 0x805h)

| Name    | R/W | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-----|-------|-------|-------|-------|-------|-------|-------|-------|

| FIFO II | W   | FPM1  | FPM0  | PSA5  | PSA4  | PSA3  | PSA2  | PSA1  | PSA0  |

| Reset   |     | 0     | 1     | 0     | 0     | 0     | 0     | 0     | 0     |

FPM [1:0]: FIFO Pointer Margin PSA [5:0]: Used for Segment FIFO.

### 9.2.7 RC OSC Register I (Address: 0x806h)

| Name     | R/W | Bit 7       | Bit 6       | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |

|----------|-----|-------------|-------------|---------|---------|---------|---------|---------|---------|

| RC OSC I | W   | WWS_SL<br>7 | WWS_SL<br>6 | WWS_SL5 | WWS_SL4 | WWS_SL3 | WWS_SL2 | WWS_SL1 | WWS_SL0 |

|          | R   |             |             |         |         |         |         |         |         |

| Reset    |     | 0           | 0           | 0       | 0       | 0       | 0       | 0       | 0       |

WWS\_SL [9:0]: 10-bits WWS\_SL Timer for TWWS Function (7.8ms ~ 7.99s).

WWS SL [9:0] are from address (0x806h) and (0x807h).

9.2.8 RC OSC Register II (Address: 0x807h)

| Name      | R/W | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |

|-----------|-----|---------|---------|---------|---------|---------|---------|---------|---------|

| RC OSC II | W   | WWS_SL9 | WWS_SL8 | WWS_AC5 | WWS_AC4 | WWS_AC3 | WWS_AC2 | WWS_AC1 | WWS_AC0 |

| Reset     |     | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       |

WWS SL [9:0]: 10-bits WWS SL Timer for TWWS Function (7.8ms ~ 7.99s).

WWS\_SL [9:0] are from address (0x806h) and (0x807h).

WWS\_AC [8:0]: 9-bits WWS\_AC Timer for TWWS Function (244us ~ 15.6ms).

### 9.2.9 RC OSC Register III (Address: 0x808h)

| Name       | R/W | Bit 7  | Bit 6  | Bit 5   | Bit 4   | Bit 3   | Bit 2 | Bit 1 | Bit 0  |

|------------|-----|--------|--------|---------|---------|---------|-------|-------|--------|

| RC OSC III | W   | BBCKS1 | BBCKS0 | WWS_AC8 | WWS_AC7 | WWS_AC6 | RCTS  | TSEL  | TWOR_E |

| Reset      |     | 0      | 0      | 0       | 0       | 0       | 1     | 0     | 1      |

BBCKS [1:0]: Clock select for internal digital block

[00]: F<sub>SYCK</sub> / 8. [01]: F<sub>SYCK</sub> / 16. [10]: F<sub>SYCK</sub> / 32. [11]: F<sub>SYCK</sub> / 64.

F<sub>SYCK</sub> is A8106's System clock.

RCOSC\_E: RC-oscillator enable.

[0]: Disable. [1]: Enable.

RCTS: Internal / External 32.768k Hz oscillator selection.

[0]: Internal. [1]: External.

TSEL: Timer select for TWWS function.

[0]: Use WWS\_AC. [1]: Use WWS\_SL.

TWWS\_E: Enable TWWS function.

[0]: Disable. [1]: Enable.

### 9.2.10 CKO Pin Control Register (Address: 0x809h)

| Name            | R/W | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1    | Bit 0   |

|-----------------|-----|-------|-------|-------|-------|-------|-------|----------|---------|

| CKO Pin Control | W   | ECKOE | CKOS3 | CKOS2 | CKOS1 | CKOS0 | CKOI  | WAKEBBIE | INTT1IE |

| Reset           |     | 1     | 0     | 1     | 1     | 1     | 0     | 1        | 0       |

ECKOE: External Clock Output Enable for CKOS [3:0]= [0100] ~ [0111].

[0]: Disable. [1]: Enable.

**АМІССОМ 笙科電子總代理** 深圳奇翰電子

CKOS [3:0]: CKO pin output select.

[0000]: DCK (TX data clock).

### 2.4GHz FSK/GFSK SoC

[0001]: RCK (RX recovery clock).

[0010]: FPF (FIFO pointer flag).

[0011]: EOP, EOVBC, EOFBC, EOADC, EOVCC, OKADC (Internal usage only).

[0100]: External clock output= F<sub>SYCK</sub>.

[0101]: External clock output / 2= F<sub>SYCK</sub> / 2.

[0110]: External clock output / 4= F<sub>SYCK</sub> / 4.

[0111]: External clock output / 8= F<sub>SYCK</sub> / 8.

[1000]: WCK. [1001]: RCOSC.

[1010]: EOADC. [1011]: OKADC.

[1100]: TMRCK OVF(Timer clock)

[1101]: Reserved. [111x]: Reserved.

CKOI: CKO pin output signal invert.

[0]: Non-inverted output. [1]: Inverted output.

WAKEBBIE: Wake BB interrupt enable.

[0]: Disable. [1]: Enable.

INTT1IE: ARCWTR interrupt enable.

[0]: Disable. [1]: Enable.

9.2.11 GIO1 Pin Control Register I (Address: 0x80Ah)

| Name               | R/W | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0  |

|--------------------|-----|-------|-------|--------|--------|--------|--------|-------|--------|

| GIO1 Pin Control I | W   | -     |       | GIO1S3 | GIO1S2 | GIO1S1 | GIO1S0 | GIO1I | GIO10E |

| Reset              |     | -     |       | 0      | 0      | 0      | 0      | 0     | 1      |

GIO1S [3:0]: GIO1 pin function select.

| GIO1S [3:0] | TX state                        | RX state            |  |  |  |  |

|-------------|---------------------------------|---------------------|--|--|--|--|

| [0000]      | WTR (Wait until T)              | X or RX finished)   |  |  |  |  |

| [0001]      | EOAC (end of access code)       | FSYNC (frame sync)  |  |  |  |  |

| [0010]      | TMEO (TX modulation enable)     | CD (carrier detect) |  |  |  |  |

| [0011]      | Preamble Detect Output (PMDC    | 0)                  |  |  |  |  |

| [0100]      | MCU wakeup signal (TWWS)        |                     |  |  |  |  |

| [0101]      | In phase demodulator input (DM  | III)                |  |  |  |  |

| [0110]      | Reserved                        |                     |  |  |  |  |

| [0111]      | TRXD In/Out (Direct mode)       |                     |  |  |  |  |

| [1000]      | RXD (Direct mode)               |                     |  |  |  |  |

| [1001]      | TXD (Direct mode)               |                     |  |  |  |  |

| [1010]      | In phase demodulator external i | nput (EXDI0)        |  |  |  |  |

| [1011]      | External FSYNC input in RX dire | ect mode            |  |  |  |  |

| [1100]      | INC                             |                     |  |  |  |  |

| [1101]      | FPF                             |                     |  |  |  |  |

| [1110]      | MCU_BB_INT5                     | ·                   |  |  |  |  |

| [1111]      | PDN_TX                          | <u> </u>            |  |  |  |  |

GIO1I: GIO1 pin output signal invert.

[0]: Non-inverted output. [1]: Inverted output.

GIO10E: GIO1pin output enable.

[0]: High Z. [1]: Enable.

9.2.12 GIO2 Pin Control Register II (Address: 0x80Bh)

| Name                | R/W | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0  |

|---------------------|-----|-------|-------|--------|--------|--------|--------|-------|--------|

| GIO2 Pin Control II | W   |       |       | GIO2S3 | GIO2S2 | GIO2S1 | GIO2S0 | GIO2I | GIO2OE |

| Reset               |     | -     | -     | 0      | 1      | 0      | 0      | 0     | 1      |

GIO2S [3:0]: GIO2 pin function select.

| GIO2S | TX state | RX state |

|-------|----------|----------|

## 2.4GHz FSK/GFSK SoC

| [0000]       | WTR (Wait until TX or RX finished)                  |

|--------------|-----------------------------------------------------|

| [0001]       | EOAC (end of access code) FSYNC (frame sync)        |

| [0010]       | TMEO (TX modulation enable) CD (carrier detect)     |

| [0011]       | Preamble Detect Output (PMDO)                       |

| [0100]       | MCU wakeup signal (TWWS)                            |

| [0101]       | Quadrature phase demodulator input (DMIQ)           |

| [0110]       | Reserved                                            |

| [0111]       | TRXD In/Out (Direct mode)                           |

| [1000]       | RXD (Direct mode)                                   |

| [1001]       | TXD (Direct mode)                                   |

| [1010]       | Quadrature phase demodulator external input (EXDI1) |

| [1011]       | External FSYNC input in RX direct mode              |

| [1100]       | DEC                                                 |

| [1101]       | FPF                                                 |

| [1110]       | PDN_RX                                              |

| [1111]       | PDN_TX                                              |

| CIONI, CION. | dis autout alamat invent                            |

GIO2I: GIO2 pin output signal invert.

[0]: Non-inverted output. [1]: Inverted output.

GIO2OE: GIO2 pin Output Enable.

[0]: High Z. [1]: Enable.

9.2.13 Clock Register (Address: 0x80Ch)

| Name  | R/W | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-----|-------|-------|-------|-------|-------|-------|-------|-------|

| Clock | R/W | GRC3  | GRC2  | GRC1  | GRC0  | CSC1  | CSC0  | CGS   | XS    |

| Reset |     | 1     | 1     | 1     | 1     | 0     | 1     | 0     | 1     |

### GRC [3:0]: Clock generation reference counter.

| GRC[3:0]                                 | Note                   |

|------------------------------------------|------------------------|

| Don't care                               | Recommend when CGS = 0 |

| $F_{XTAL} \times (DBL+1) / (GRC+1) = 2M$ | When CGS = 1           |

CSC [1:0]: system clock F<sub>SYCK</sub> divider select.

[00]: F<sub>CSCK</sub> / 1. [01]: F<sub>CSCK</sub> / 2. [10]: F<sub>CSCK</sub> / 2. [11]: F<sub>CSCK</sub> / 4.

### CSC [1:0]: system clock F<sub>SYCK</sub> divider select.

| CSC [1:0]      | System Clock F <sub>SYCK</sub> | Note                                               |

|----------------|--------------------------------|----------------------------------------------------|

| 00             | F <sub>MCLK</sub>              | F <sub>SYCK</sub> is used to determine             |

| 01 (Recommend) | F <sub>MCLK</sub> / 2          | 1. Data rate (0Dh)                                 |

| 10             | F <sub>MCLK</sub> / 2          | 2. ADC clock (1Dh) 3. Internal digital clock (08h) |

| 11             | F <sub>MCLK</sub> / 4          | 4. CKO pin (09h)                                   |

# CGS: Clock generator enable. Recommend CGS = [0] [0]: Disable. [1]: Enable.

| CGS = 1                    |

|----------------------------|

| F <sub>MCLK</sub> = 32 MHz |

|                            |

### XS: Crystal oscillator select.

[0]: Use external clock. [1]: Use external crystal.

| Master clock frequency | CGS = 0             | CGS = 1 |

|------------------------|---------------------|---------|

| DBL = 0                | Crystal frequency   | 32 MHz  |

| DBL = 1                | 2*crystal frequency | 32 MHz  |

## 2.4GHz FSK/GFSK SoC

9.2.14 Data Rate Register (Address: 0x80Dh)

| Name      | R/W | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-----------|-----|-------|-------|-------|-------|-------|-------|-------|-------|

| Data Rate | R/W | SDR7  | SDR6  | SDR5  | SDR4  | SDR3  | SDR2  | SDR1  | SDR0  |

| Reset     |     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

SDR [7:0]: Data rate division selection. Data rate =  $F_{SYCK}$  / (32\*(SDR [7:0] +1)).

9.2.15 PLL Register I (Address: 0x80Eh)

| Name  | R/W | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-----|-------|-------|-------|-------|-------|-------|-------|-------|

| PLL I | R/W | CHN7  | CHN6  | CHN5  | CHN4  | CHN3  | CHN2  | CHN1  | CHN0  |

| Reset |     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

CHN [7:0]: LO channel number select.

9.2.16 PLL Register II (Address: 0x80Fh)

| Name   | R/W | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|--------|-----|-------|-------|-------|-------|-------|-------|-------|-------|

| PLL II | R   | DBL   | RRC1  | RRC0  | CHR3  | CHR2  | CHR1  | CHR0  | IP8   |

|        | W   | DBL   | RRC1  | RRC0  | CHR3  | CHR2  | CHR1  | CHR0  | BIP8  |

| Reset  |     | 1     | 0     | 0     | 1     | 1     | 1     | 1     | 0     |

DBL: Crystal frequency doubler selection.

[0]: Disable.  $F_{XREF} = F_{XTAL}$ . [1]: Enable.  $F_{XREF} = 2 * F_{XTAL}$ .

RRC [1:0]: RF PLL reference counter setting.

CHR [3:0]: PLL channel step setting.

9.2.17 PLL Register III (Address: 0x810h)

| Name    | R/W | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-----|-------|-------|-------|-------|-------|-------|-------|-------|

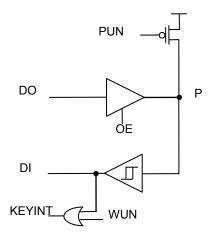

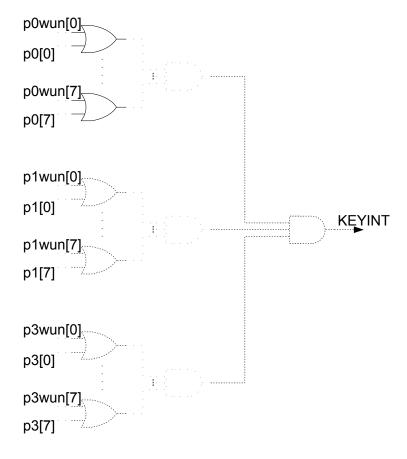

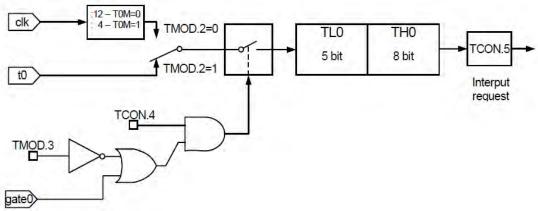

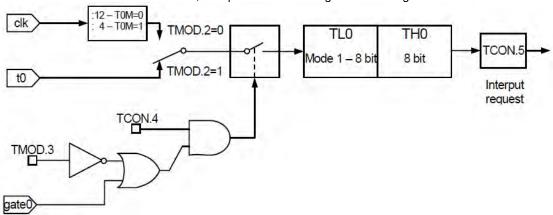

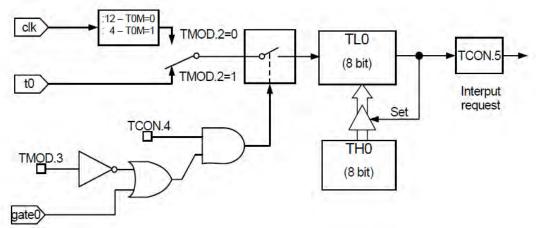

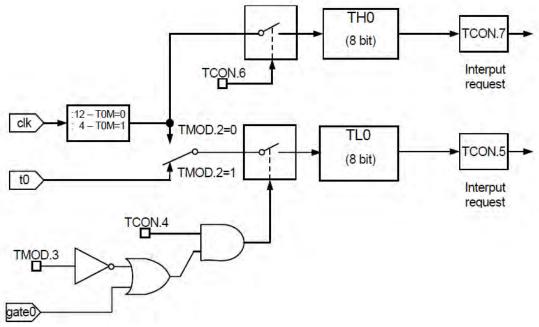

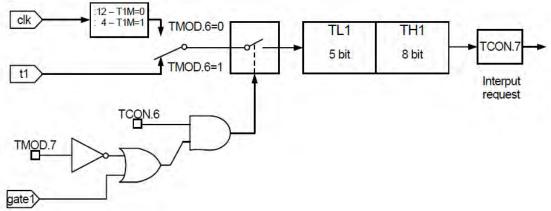

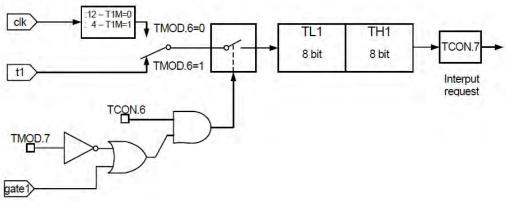

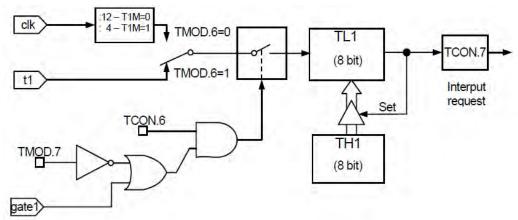

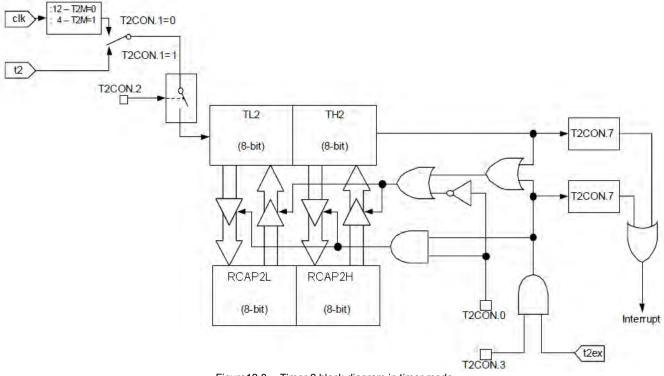

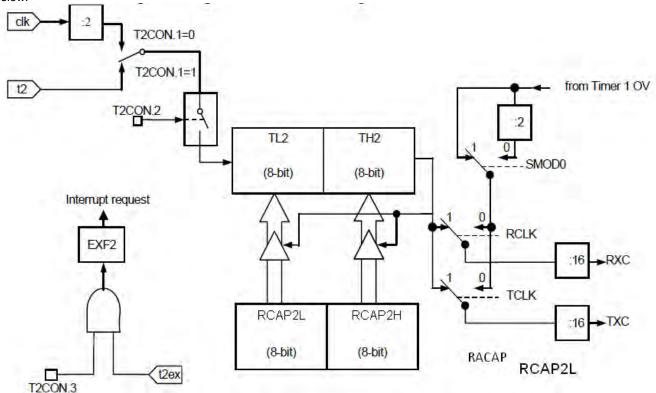

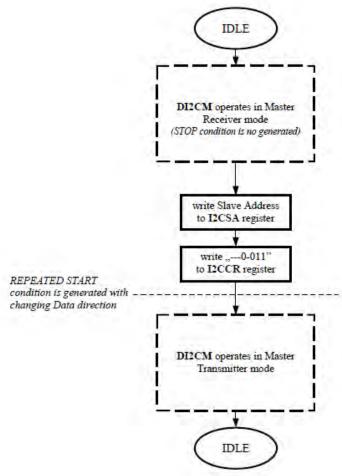

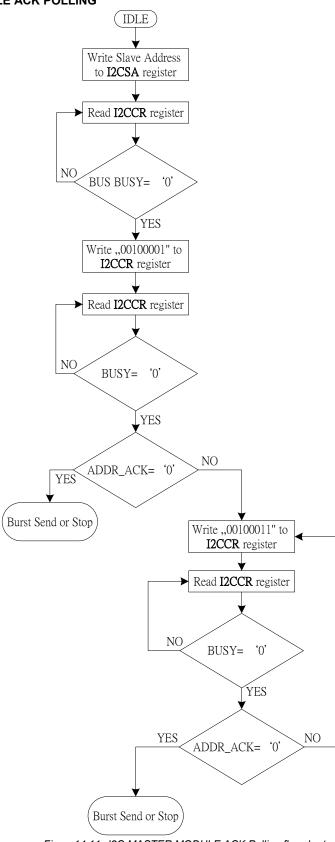

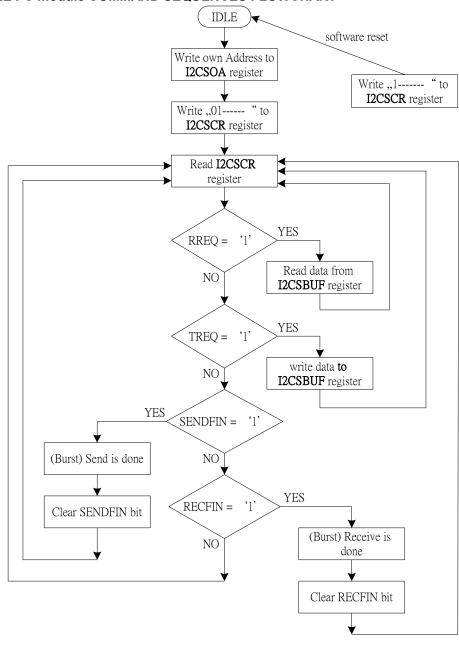

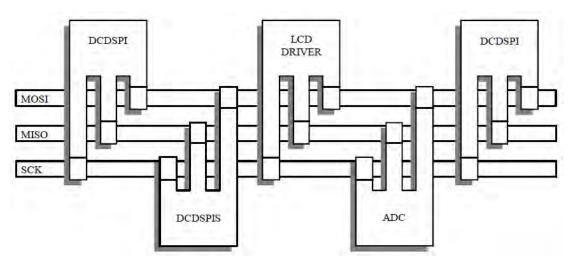

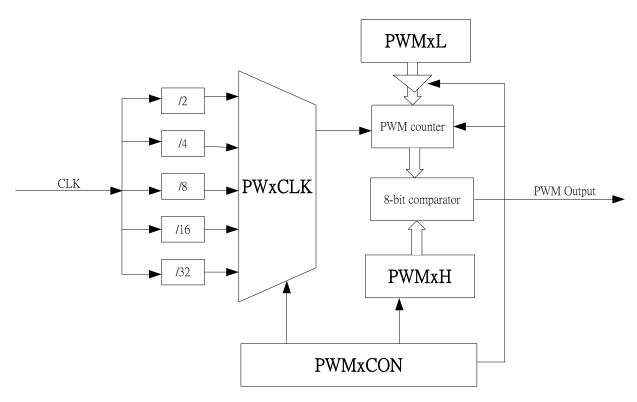

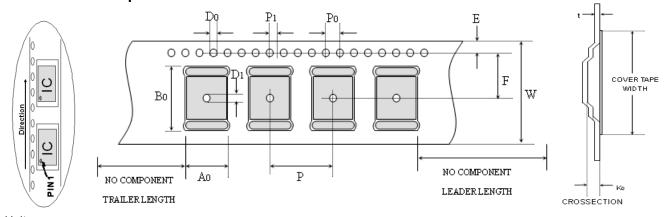

| PLL III | R   | IP7   | IP6   | IP5   | IP4   | IP3   | IP2   | IP1   | IP0   |