## **Document Title**

A8107M0 Data Sheet, Bluetooth Low Energy SoC

## **Revision History**

| <u>Rev. No.</u> | History                                                                                     | Issue Date               | <u>Remark</u>              |

|-----------------|---------------------------------------------------------------------------------------------|--------------------------|----------------------------|

| 0.0             | Initial issue.                                                                              | Aug., 2016               | Objective                  |

| 0.1             | Revise TFT LCD driver to TFT LCD controller                                                 | Sep., 2016               | Preliminary                |

| 0.1<br>0.2      | Revise TFT LCD driver to TFT LCD controller<br>Update Features and Electrical Specification | Sep., 2016<br>Oct., 2016 | Preliminary<br>Preliminary |

|                 |                                                                                             |                          |                            |

### Important Notice:

AMICCOM reserves the right to make changes to its products or to discontinue any integrated circuit product or service without notice. AMICCOM integrated circuit products are not designed, intended, authorized, or warranted to be suitable for use in life-support applications, devices or systems or other critical applications. Use of AMICCOM products in such applications is understood to be fully at the risk of the customer.

# Table of Contents

| 1. General Description                                            |          |

|-------------------------------------------------------------------|----------|

| 2. Typical Applications                                           |          |

| 3. Features                                                       |          |

| 4. Pin Configurations                                             |          |

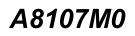

| 4.1 QFN40 5x5                                                     |          |

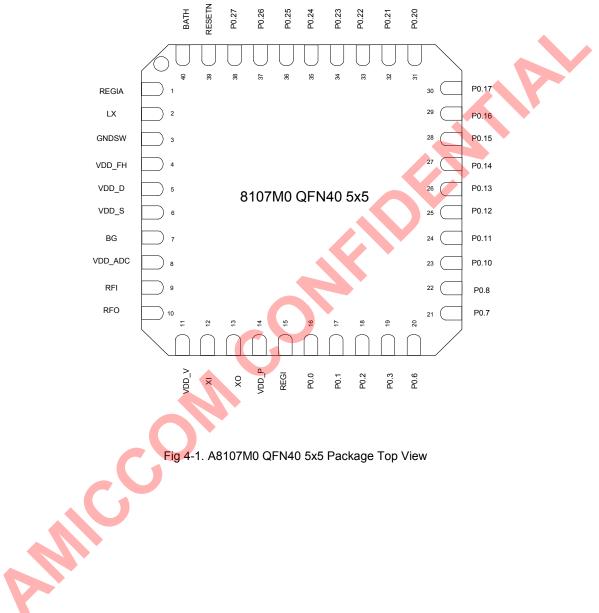

| 4.2 QFN48 6x6                                                     |          |

| 5. Pin Descriptions (I: input; O: output, I/O: input or output)   |          |

| 5.1 A8107M0 QFN40 5x5 Package                                     | 8        |

| 5.2 A8107M0 QFN48 6x6 Package                                     |          |

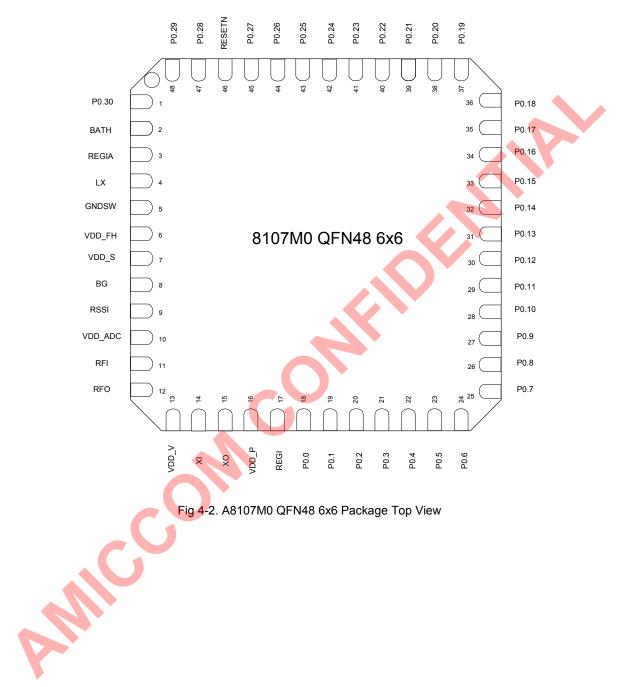

| 6. Chip Block Diagram                                             |          |

| 7. Absolute Maximum Ratings                                       |          |

| 8. Electrical Specification                                       |          |

| 9. Register List                                                  |          |

| 9.1 Peripheral Register Overview                                  |          |

| 9.2 Register Overview                                             |          |

| Follow the instructions below to setup the register.              |          |

| 9.2.1 Battery detect Register (Address: 0x5000000h)               |          |

| 9.2.2 Power control Register 1 (Address: 0x5000008h)              | 16       |

| 9.2.3 Power control Register 2 (Address: 0x5000000Ch)             |          |

| 9.2.4 Reset Register (Address: 0x50001000h)                       | 17       |

| 9.2.5 Strobe Register (Address: 0x50001004h)                      |          |

| 9.2.6 Status Register (Address: 0x50001010h)                      |          |

| 9.2.7 FIFO Register (Address: 0x50001020h)                        |          |

| 9.2.8 RSSI Register (Address: 0x50001244h)                        |          |

| 9.2.9 ADC Control Register I (Address: 0x50008000h)               |          |

| 9.2.10 ADC Control Register II (Address: 0x50008004h)             | 21       |

| 9.2.11 ADC Channel Register (Address: 0x50008008h)                | 21       |

| 10.SOC Architectural Overview                                     |          |

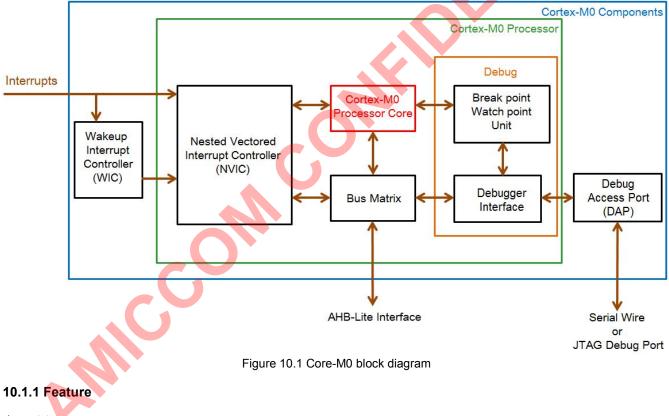

| 10.1 ARM Cortex-M0                                                |          |

| 10.1.1 Feature                                                    |          |

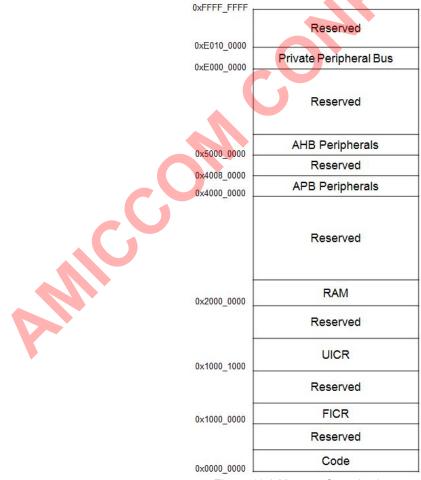

| 10.2 Memory Organization                                          |          |

| 10.3 Nested Vectored Interrupt Controller (NVIC)                  |          |

| 10.3.1 Feature                                                    |          |

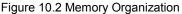

| 10.3.2 Exception Types and Interrupt Map<br>10.4 Reset source     | 25<br>27 |

| 10.5 Clock source                                                 |          |

| 10.6 System Timer (SysTick)                                       |          |

| 10.6.1 Register Overview .                                        |          |

| 10.6.2 SysTick Control and Status Register (Address: 0xE000E010h) | 20<br>28 |

| 10.6.3 SysTick Reload Value Register (Address: 0xE000E0101)       | 20<br>20 |

| 10.6.4 SysTick Current Value Register (Address: 0xE000E014h)      |          |

| 10.6.5 SysTick Calibration Value Register (Address: 0xE000E01Ch)  | 20       |

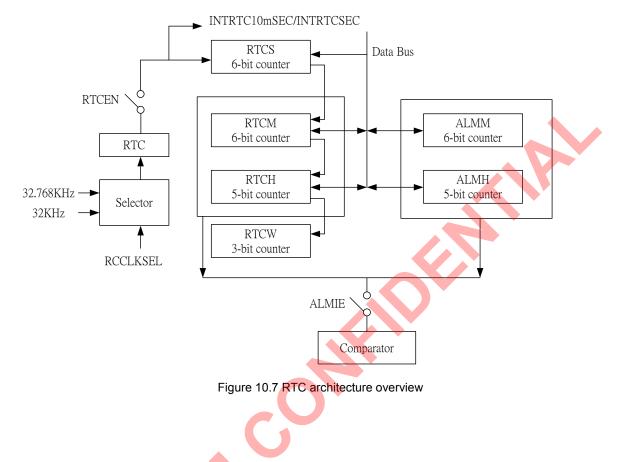

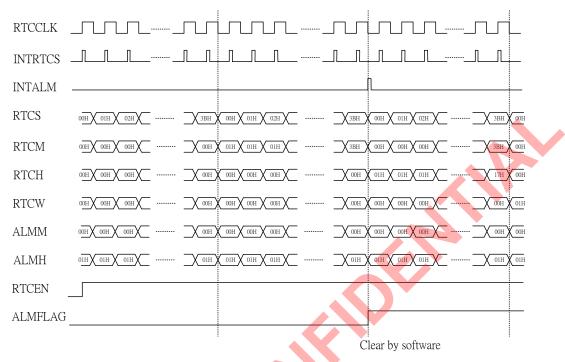

| 10.7 RTC (REAL TIMER CLOCK) TIMER WITH ALARM                      |          |

| 10.7.1 REAL TIME CLOCK TIMER WITH ALARM FUNCTION                  | 30       |

| 10.7.2 REAL TIME CLOCK TIMER WITH ALARM OPERATION                 |          |

| 10.7.3 REAL TIME CLOCK TIMER WITH ALARM CONTROL REGISTER          |          |

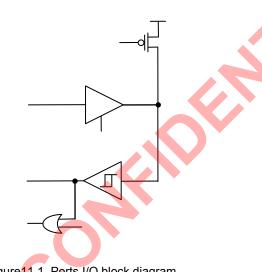

| 11. I/O Ports                                                     |          |

| 11.1 FUNCTIONALITY                                                |          |

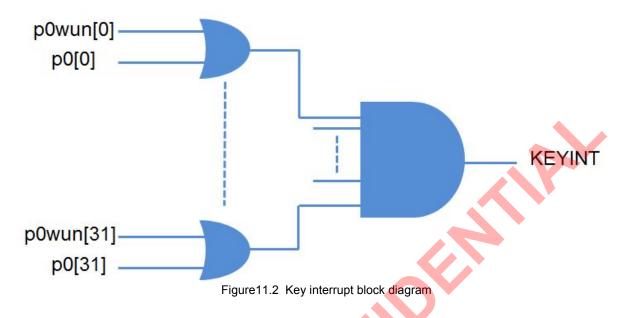

| 11.2 Key interrupt                                                |          |

| 11.3 GPIO interrupt trigger                                       |          |

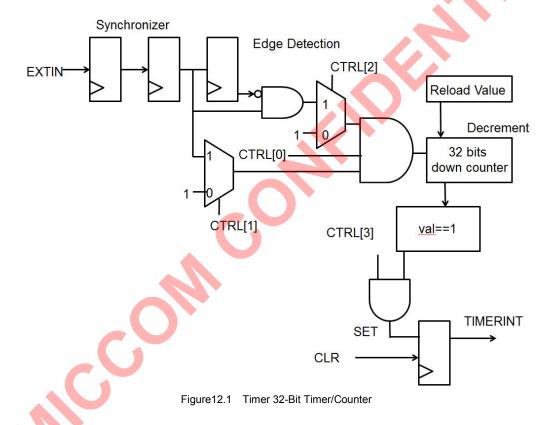

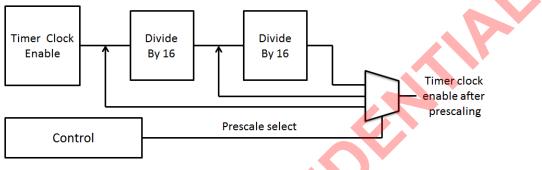

| 12 Timer 0 & 1                                                    |          |

| 12.1 Overview                                                     |          |

| 12.2 Timer 0 & 1 Register                                         |          |

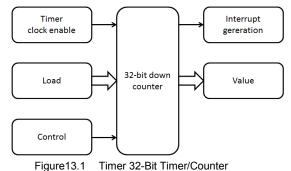

| 13 Dual Timer                                                     |          |

| 13.1 Dual Timer FUNCTIONALITY                                     |          |

| 13.2 Dual Timer Operation                                         |          |

| 13.3 Dual Timer Register                                          |          |

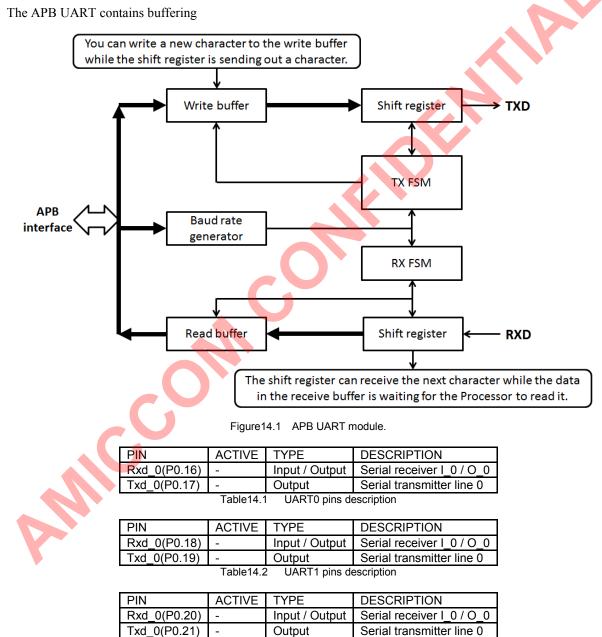

| 14. UART 0 & 1 & 2                                                |          |

| 14.1 Overview                                                     |          |

| 14.2 UART 0 Register                                              | 52       |

# Bluetooth Low Energy SoC

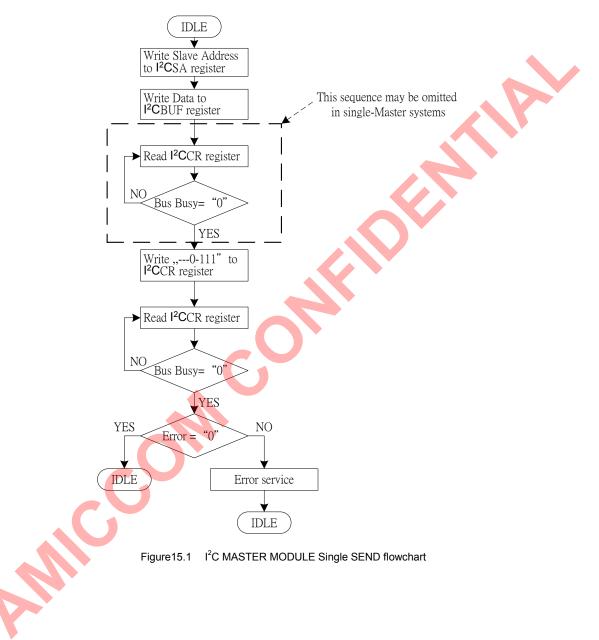

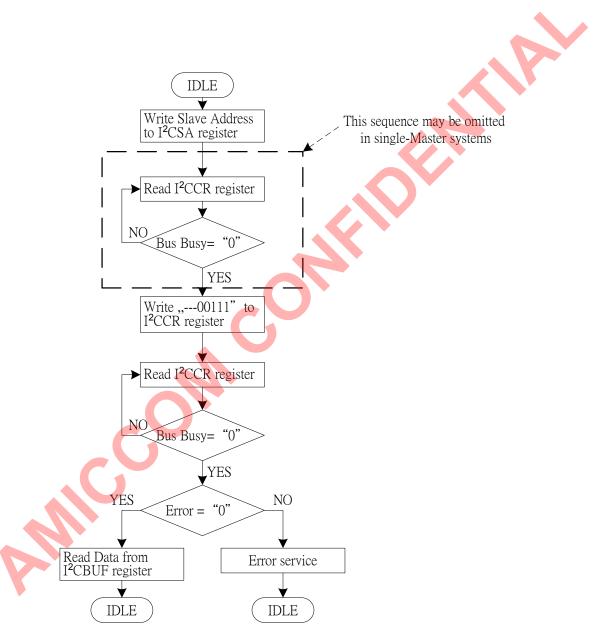

| 15. IIC interface                                                     | 55    |

|-----------------------------------------------------------------------|-------|

| 15.1 Master MODE I <sup>2</sup> C                                     | 55    |

| 15.1.1 I <sup>2</sup> C REGISTERS                                     | 55    |

| 15.1.2 I <sup>2</sup> C MASTER MODULE AVAILABLE SPEED MODES           | 59    |

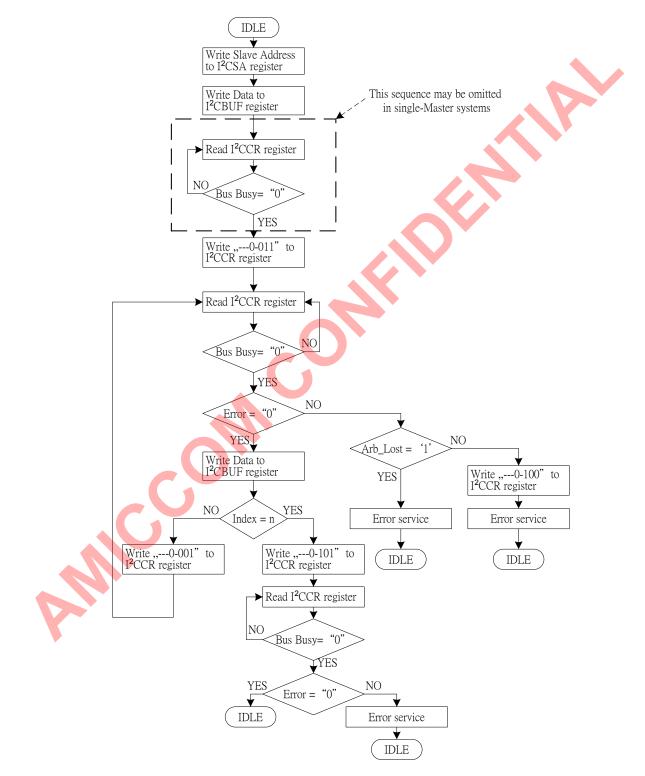

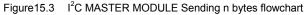

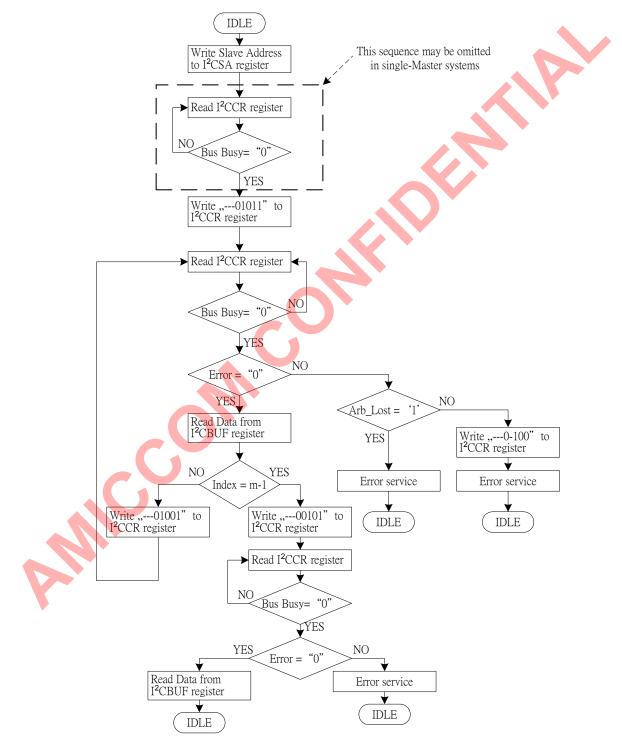

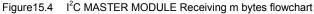

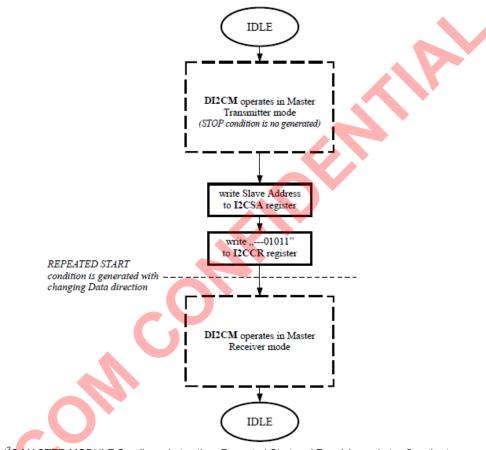

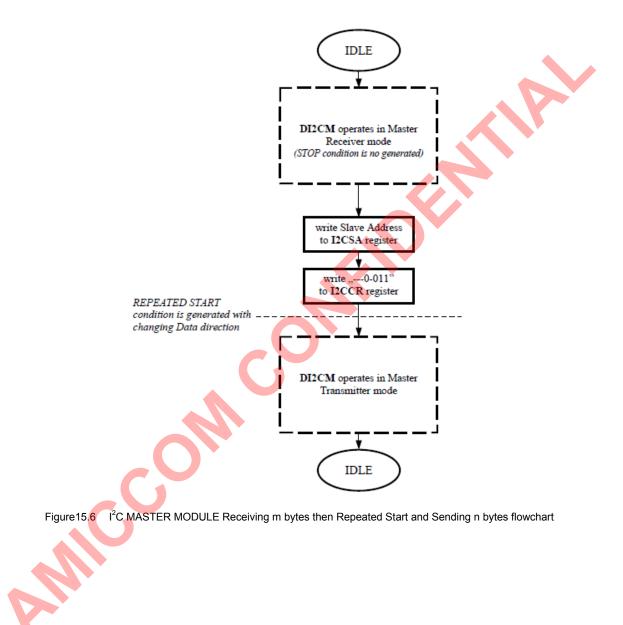

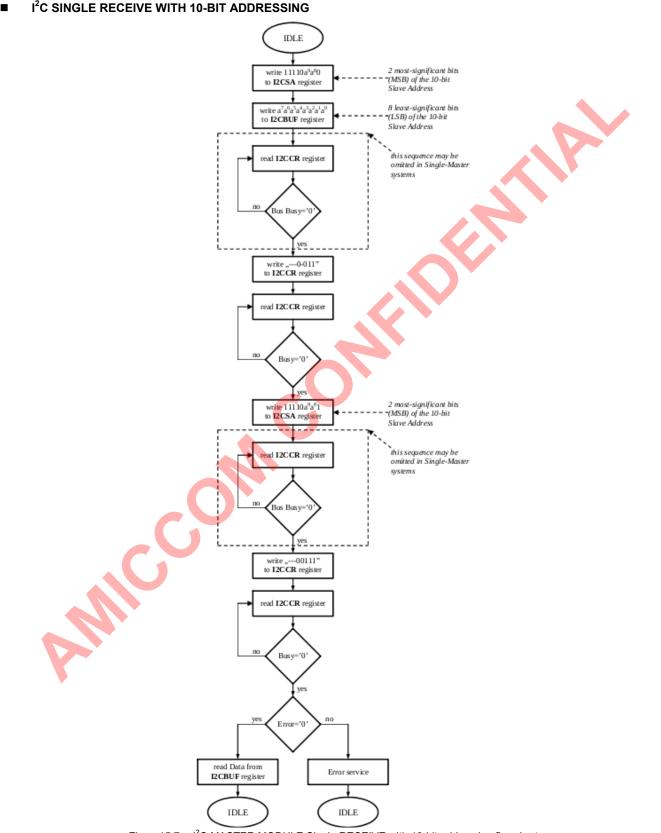

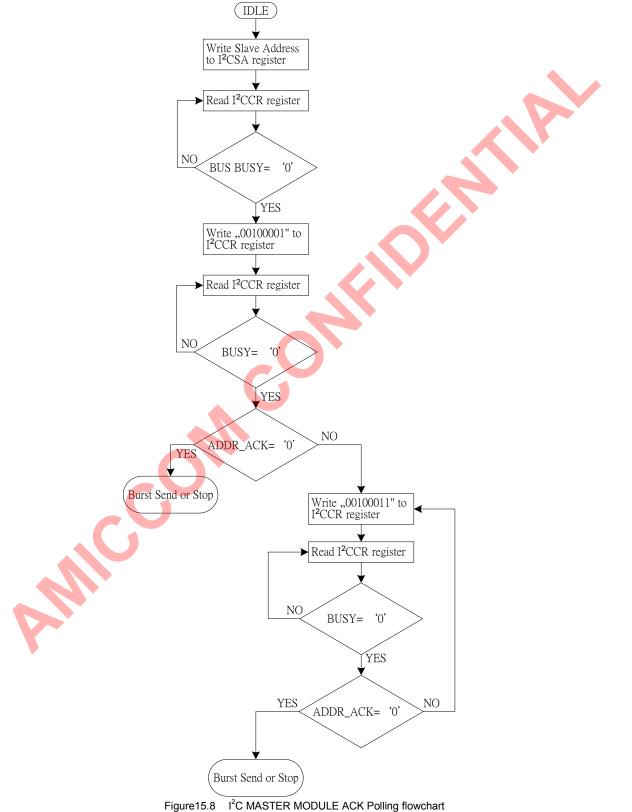

| 15.1.3 I <sup>2</sup> C MASTER MODULE AVAILABLE COMMAND SEQUENCES     | 60    |

| 15.2 I <sup>2</sup> C MASTER MODULE INTERRUPT GENERATION              | 68    |

| 15.3 Slave MODE I <sup>2</sup> C                                      | 68    |

| 15.3.1 I <sup>2</sup> C MODULE INTERNAL REGISTERS                     | 68    |

| 15.4 AVAILABLE I <sup>2</sup> C MODULE TRANSMISSION MODES             | 70    |

| 15.4.1 I <sup>2</sup> C module SINGLE RECEIVE                         | 70    |

| 15.4.2 I <sup>2</sup> C module SINGLE SEND                            |       |

| 15.4.3 I <sup>2</sup> C module BURST RECEIVE                          |       |

| 15.4.4 I <sup>2</sup> C module BURST SEND                             |       |

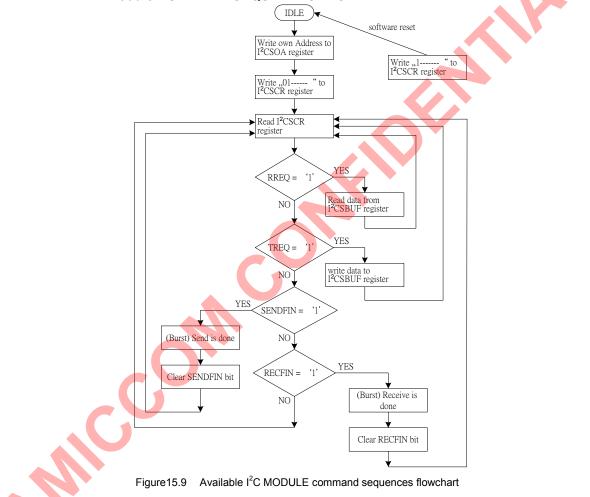

| 15.4.5 AVAILABLE I <sup>2</sup> C module COMMAND SEQUENCES FLOWCHART. | 71    |

| 115.5 I <sup>2</sup> C MODULE INTERRUPT GENERATION                    | 71    |

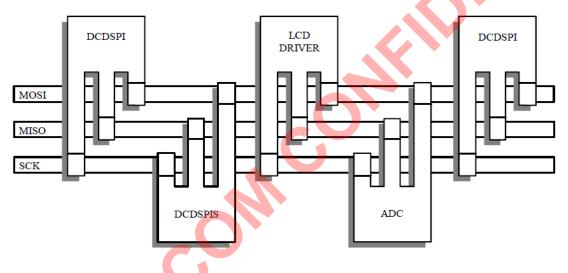

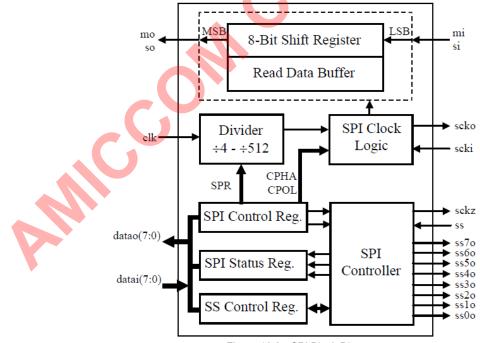

| 16. SPI interface                                                     |       |

| 16.1 KEY FEATURES                                                     |       |

| 16.2 SPI PINS DESCRIPTION                                             |       |

| 16.3 SPI HARDWARE DESCRIPTION                                         |       |

| 16.3.1 BLOCK DIAGRAM                                                  | 74    |

| 16.3.2 INTERNAL REGISTERS                                             | 75    |

| 16.4 MASTER OPERATIONS                                                |       |

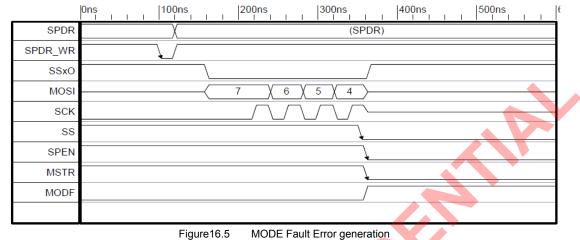

| 16.4.1 MASTER MODE ERRORS                                             |       |

| 16.5 SLAVE OPERATIONS                                                 | 70    |

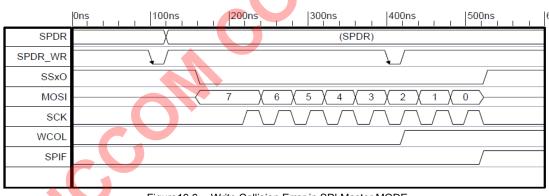

| 16.5.1 SLAVE MODE ERRORS                                              | 79    |

| 16.5.1 SLAVE MODE ERRORS                                              |       |

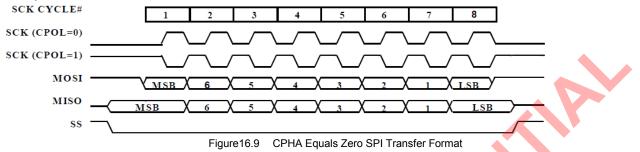

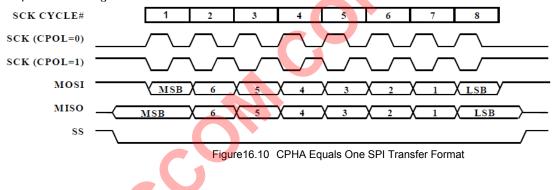

| 16.6.1 SPI CLOCK PHASE AND POLARITY CONTROLS                          | 00    |

|                                                                       |       |

| 16.6.2 SPI MODULE TRANSFER FORMATS                                    | 80    |

| 16.6.3 CPHA EQUALS ZERO TRANSFER FORMAT                               | 80    |

| 16.6.4 CPHA EQUALS ONE TRANSFER FORMAT                                | 81    |

| 16.7 SPI DATA TRANSFER                                                | 81    |

| 16.7.1 TRANSFER BEGINNING PERIOD (INITIATION DELAY)                   |       |

| 16.7.2 TRANSFER ENDING PERIOD.                                        |       |

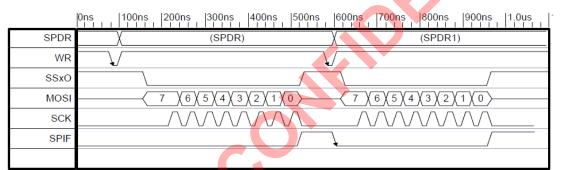

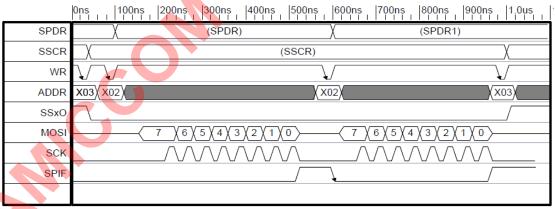

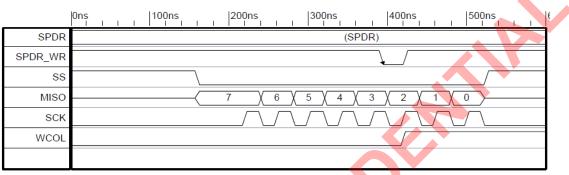

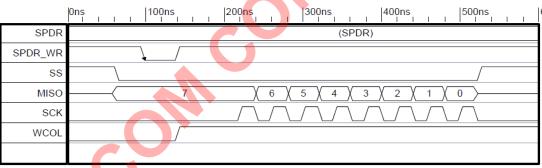

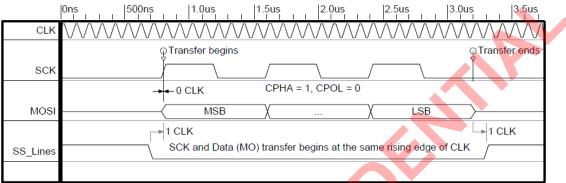

| 16.8 TIMING DIAGRAMS                                                  | 82    |

| 16.8.1 MASTER TRANSMISSION                                            |       |

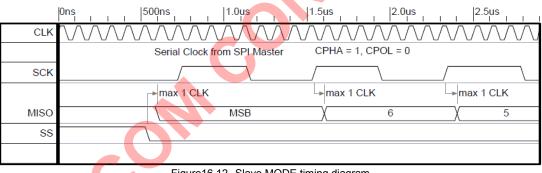

| 16.8.2 SLAVE TRANSMISSION                                             | 82    |

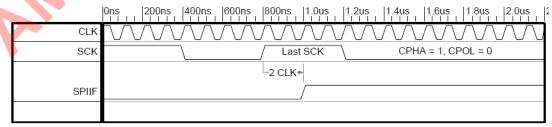

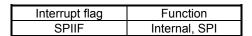

| 16.9 SPI MODULE INTERRUPT GENERATION                                  | 82    |

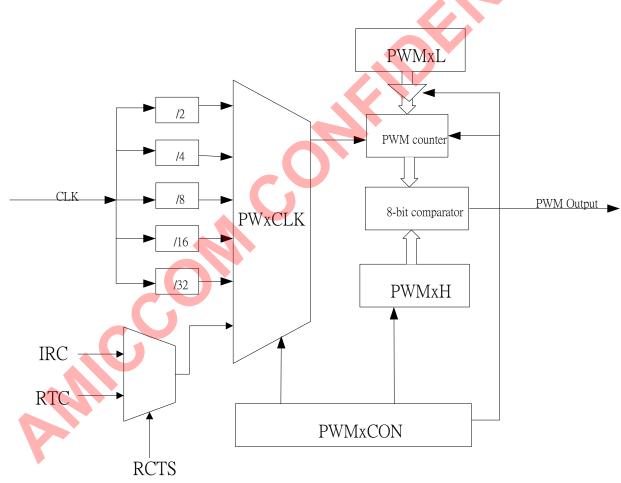

| 17. PWM                                                               |       |

| 17.1 PWM FUNCTIONALITY                                                |       |

| 17.1.1 PWM0 Regis <mark>te</mark> rs                                  |       |

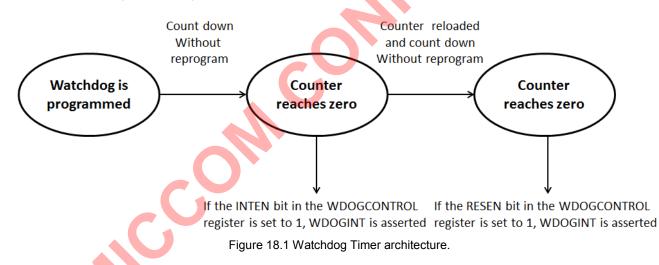

| 18. Watchdog Timer                                                    |       |

| 18.1 Watchdog timer overview                                          | 89    |

| 18.2 Watchdog Register                                                | 89    |

| 19. ADC (Analog to Digital Converter)                                 | 93    |

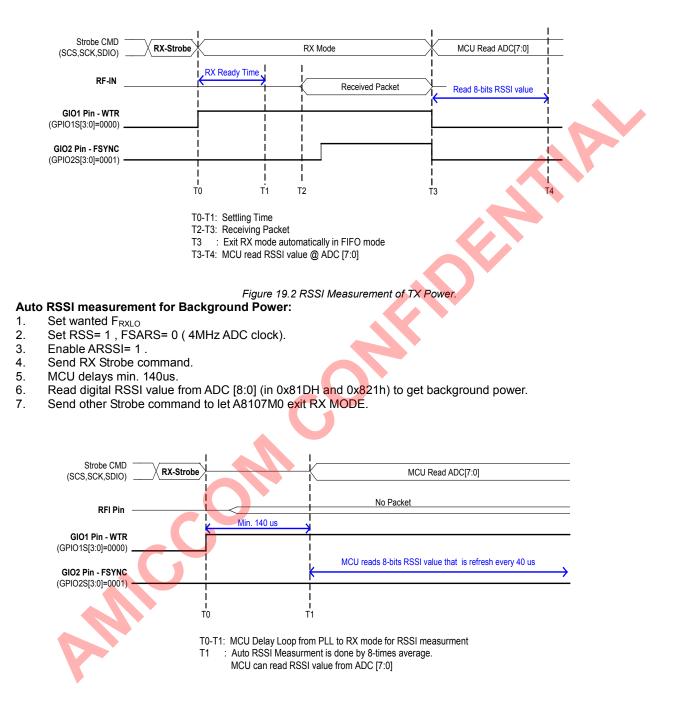

| 19.1 8-bits ADC                                                       | 93    |

| 19.1.1 RSSI Measurement                                               | 93    |

| 19.1.2 Carrier Detect                                                 | 94    |

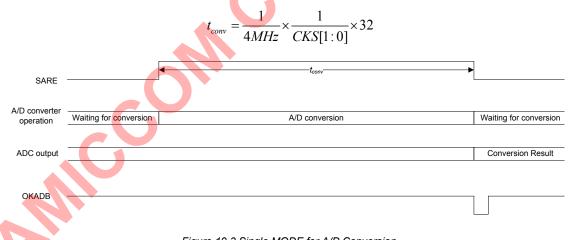

| 19.2 12-bits SAR ADC                                                  | 95    |

| 20. Battery Detect                                                    |       |

| 21 Power Management                                                   |       |

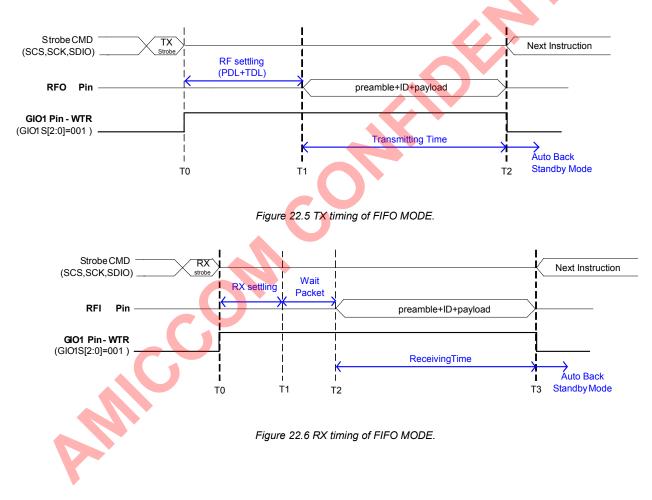

| 22 A8107M0 RF                                                         | 99    |

| 22.1Strobe Command Register 1 (Address: 0x50001004h)                  |       |

| 22.1.1 Strobe Command - Sleep MODE                                    |       |

| 22.1.2 Strobe Command - Idle MODE                                     |       |

| 22.1.3 Strobe Command - Standby MODE                                  |       |

| 22.1.3 Strobe Command - OLL MODE                                      |       |

| 22.1.4 Strobe Command - RX MODE                                       |       |

| 22.1.5 Strobe Command - TX MODE                                       |       |

|                                                                       |       |

| 22.2 RF Reset Command                                                 |       |

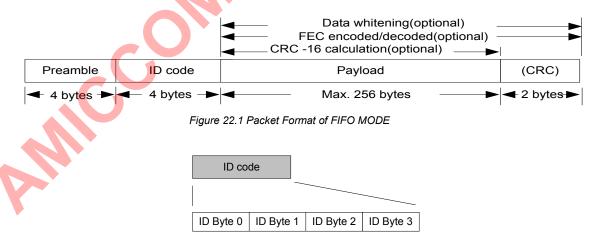

| 22.4 Packet Format of FIFO MODE                                       |       |

| 22.5 Transceiver Frequency                                            |       |

| 22.0 Hanaceiver Hiequelloy                                            | . 101 |

# Bluetooth Low Energy SoC

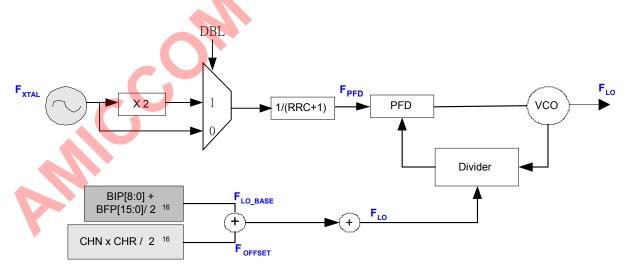

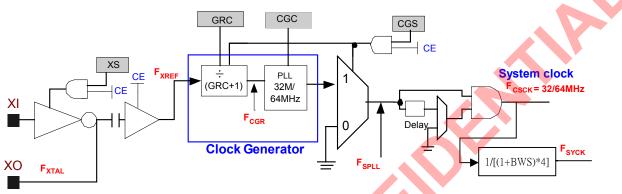

| 22.5.1 RF Clock       10         22.5.2 LO Frequency Setting       10         22.5.2 LO w to set F <sub>LO BASE</sub> 10         22.5.2.2 How to set F <sub>LO BASE</sub> 10         22.6 State machine       10         22.6.1 Key states       10         22.6.2 FIFO MODE       10         23. TFT LCD Controller       10         23. TFT LCD overview       10         23.2 TFT LCD SRAM format       10         23.3 TFT LCD DMA flow       10         23.4 TFT LCD BA80 output interface(I80)       10         24. Encryption and Autherfication       11         24.1 A AES       11         24.1.3 ShiftRows       11         24.1.4 MixColumns       11         24.1.5 CCM       11         25. Flash memory controller       11         25. Flash memory controller       11         25. Flash memory controller       11         25. Plash controller command       11         25. Plash controller com | 02<br>03<br>03<br>03<br>03<br>03<br>03<br>03<br>04<br>06<br>06<br>06<br>06<br>07<br>10<br>10<br>10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22.5.2.1 How to set F <sub>LO_BASE</sub> 10         22.5.2.2 How to set F <sub>LO</sub> = F <sub>LO_BASE</sub> + F <sub>OFFSET</sub> 10         22.6 State machine       10         22.6.1 Key states       10         22.6.2 FIFO MODE       10         23. TFT LCD Controller       10         23.1 TFT LCD overview       10         23.2 TFT LCD SRAM format       10         23.3 TFT LCD DMA flow       10         23.4 TFT LCD B& 00 output interface(180)       10         24.1 AES       11         24.1.2 SubBytes       11         24.1.3 ShiftRows       11         24.1.5 CCM       11         25. Flash memory controller       11         25.1 Flash controller command       11                                                                                                                                                                                                                                                                                                                                                                                                                                                           | )3         )3         )3         )3         )3         )3         )3         )3         )3         )3         )3         )3         )3         )3         )3         )3         )3         )3         )3         )3         )3         )3         )3         )3         )4         )5         )6         )6         )6         )6         )6         )6         )6         )6         )6         )6         )6         )6         )6         )6         )6         )7         10         10         10         10         10         10           10          10          10          10          10          10< |

| 22.5.2.2 How to set FLO_= FLO_BASE + FOFFSET.       10         22.6 State machine       10         22.6.1 Key states       10         22.6.2 FIFO MODE       10         23. TFT LCD Controller.       10         23.1 TFT LCD overview       10         23.2 TFT LCD SRAM format.       10         23.3 TFT LCD SRAM format.       10         23.4 TFT LCD SRAM format.       10         23.3 TFT LCD BMA flow       10         23.4 TFT LCD BMA flow       10         24.1 AES       11         24.1.1 AddRoundKey.       11         24.1.2 SubBytes       11         24.1.3 ShiftRows       11         24.1.4 MixColumns       11         24.1.5 CCM       11         25. Flash memory controller       11         25.1 Flash controller command       11                                                                                                                                                                                                                                                                                                                                                                                               | D3         D3         D3         D4         D6         D6         D6         D6         D7         10         10         10         10                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

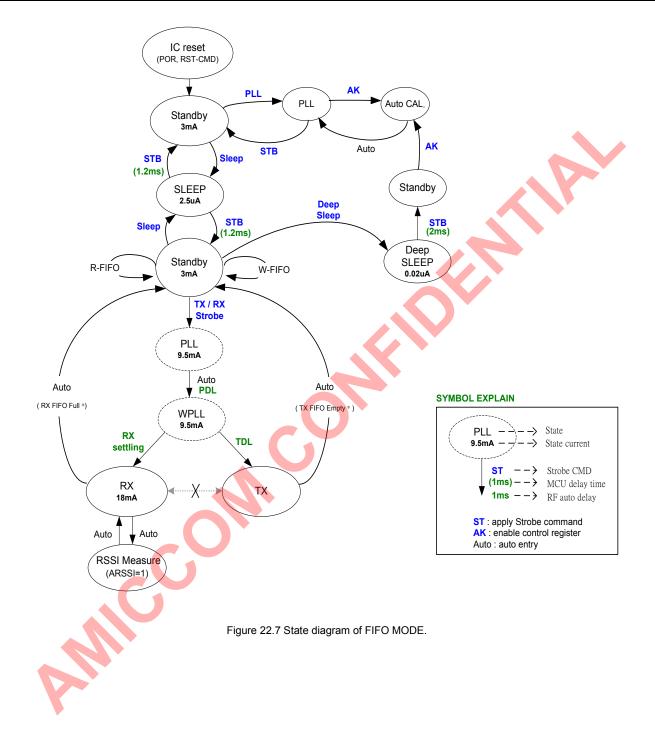

| 22.6 State machine       10         22.6.1 Key states       10         22.6.2 FIFO MODE       10         23. TFT LCD Controller       10         23.1 TFT LCD overview       10         23.2 TFT LCD SRAM format       10         23.3 TFT LCD BRAM format       10         23.4 TFT LCD BMA flow       10         23.4 TFT LCD 8080 output interface(I80)       10         24.1 AES       11         24.1.1 AddRoundKey       11         24.1.2 SubBytes       11         24.1.3 ShiftRows       11         24.1.4 MixColumns       11         24.1.5 CCM       11         25. Flash memory controller       11         25.1 Flash controller command       11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | D3         D3         D4         D6         D7         10         10         10                                                                                                                                                                                                                                                           |

| 22.6.1 Key states       10         22.6.2 FIFO MODE       10         23. TFT LCD Controller       10         23.1 TFT LCD overview       10         23.2 TFT LCD SRAM format       10         23.3 TFT LCD BRAM format       10         23.3 TFT LCD DMA flow       10         23.4 TFT LCD B8080 output interface(I80)       10         24. Encryption and Autherfication       11         24.1 AES       11         24.1.1 AddRoundKey       11         24.1.2 SubBytes       11         24.1.3 ShiftRows       11         24.1.4 MixColumns       11         24.1.5 CCM       11         25. Flash memory controller       11         25.1 Flash controller command       11                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <ul> <li>D3</li> <li>D4</li> <li>D6</li> <li>D6</li> <li>D6</li> <li>D6</li> <li>D7</li> <li>10</li> <li>10</li> <li>10</li> <li>10</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 22.6.2 FIFO MODE.       10         23. TFT LCD Controller.       10         23.1 TFT LCD overview       10         23.2 TFT LCD SRAM format.       10         23.3 TFT LCD DMA flow       10         23.4 TFT LCD 8080 output interface(I80)       10         24. Encryption and Autherfication       11         24.1 AES       11         24.1.1 AddRoundKey       11         24.1.2 SubBytes       11         24.1.3 ShiftRows       11         24.1.4 MixColumns       11         24.1.5 CCM       11         25. Flash memory controller       11         25.1 Flash controller command       11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 04<br>06<br>06<br>06<br>06<br>07<br>10<br>10<br>10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

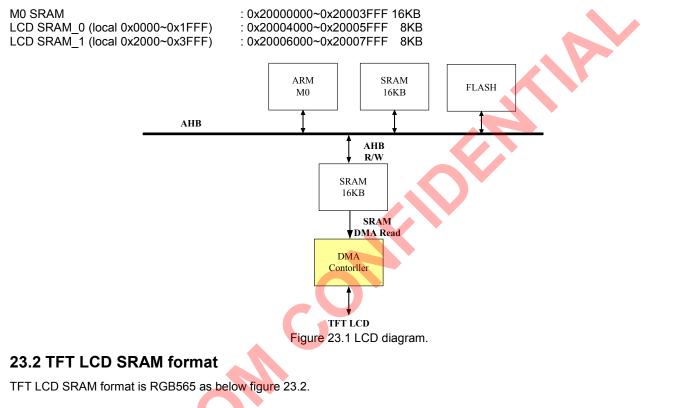

| 23. TFT LCD Controller.       10         23.1 TFT LCD overview       10         23.2 TFT LCD SRAM format.       10         23.3 TFT LCD DMA flow       10         23.4 TFT LCD 8080 output interface(I80)       10         24. Encryption and Autherfication       11         24.1 AES       11         24.1.2 SubBytes       11         24.1.3 ShiftRows       11         24.1.4 MixColumns       11         24.1.5 CCM       11         25. Flash memory controller       11         25.1 Flash controller command       11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <ul> <li>D6</li> <li>D6</li> <li>D6</li> <li>D6</li> <li>D7</li> <li>10</li> <li>10</li> <li>10</li> <li>10</li> <li>10</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 23.1 TFT LCD overview       10         23.2 TFT LCD SRAM format.       10         23.3 TFT LCD DMA flow       10         23.4 TFT LCD 8080 output interface(I80)       10         24. Encryption and Autherfication       11         24.1 AES       11         24.1.2 SubBytes       11         24.1.3 ShiftRows       11         24.1.4 MixColumns       11         24.1.5 CCM       11         25. Flash memory controller       11         25.1 Flash controller command       11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 06<br>06<br>07<br>10<br>10<br>10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

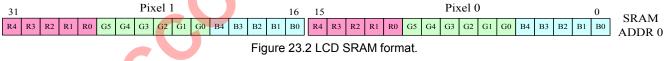

| 23.2 TFT LCD SRAM format.       10         23.3 TFT LCD DMA flow       10         23.4 TFT LCD 8080 output interface(I80)       10         24. Encryption and Autherfication       11         24.1 AES       11         24.1.1 AddRoundKey       11         24.1.2 SubBytes       11         24.1.3 ShiftRows       11         24.1.4 MixColumns       11         24.1.5 CCM       11         25. Flash memory controller       11         25.1 Flash controller command       11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 06<br>06<br>07<br>10<br>10<br>10<br>10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

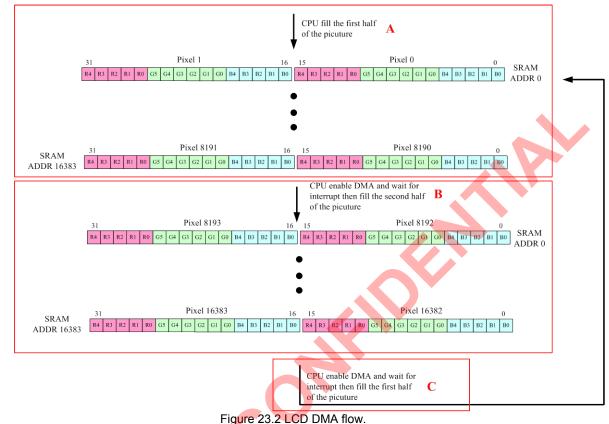

| 23.3 TFT LCD DMA flow       10         23.4 TFT LCD 8080 output interface(I80)       10         24. Encryption and Autherfication       11         24.1 AES       11         24.1.1 AddRoundKey       11         24.1.2 SubBytes       11         24.1.3 ShiftRows       11         24.1.4 MixColumns       11         24.1.5 CCM       11         25. Flash memory controller       11         25.1 Flash controller command       11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 06<br>07<br>10<br>10<br>10<br>10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

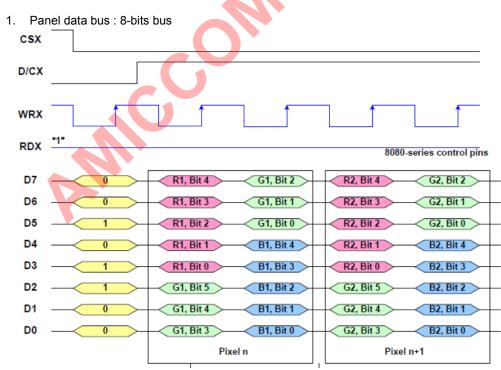

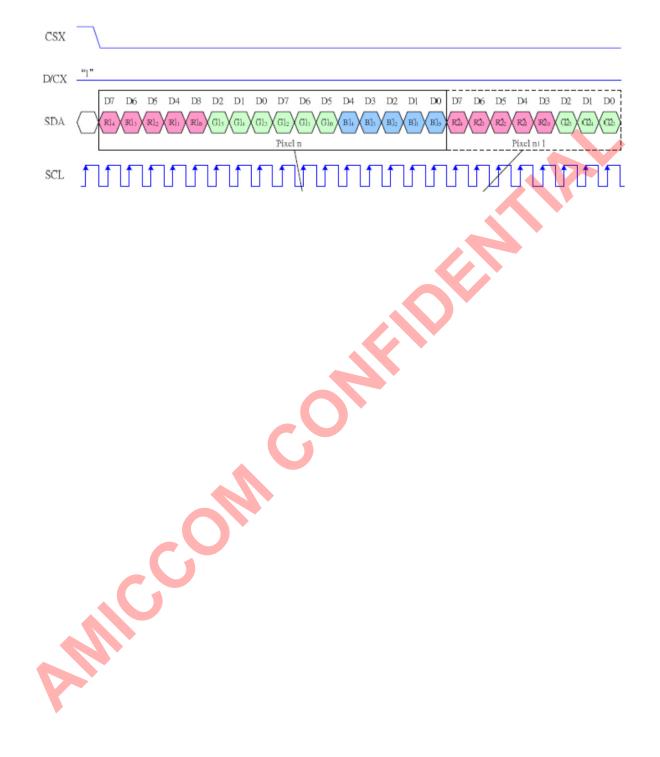

| 23.4 TFT LCD 8080 output interface(I80)       10         24. Encryption and Autherfication       11         24.1 AES       11         24.1.1 AddRoundKey       11         24.1.2 SubBytes       11         24.1.3 ShiftRows       11         24.1.4 MixColumns       11         24.1.5 CCM       11         25. Flash memory controller       11         25.1 Flash controller command       11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 07<br>10<br>10<br>10<br>10<br>10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 24. Encryption and Autherfication       11         24.1 AES       11         24.1.1 AddRoundKey       11         24.1.2 SubBytes       11         24.1.3 ShiftRows       11         24.1.4 MixColumns       11         24.1.5 CCM       11         25. Flash memory controller       11         25.1 Flash controller command       11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10<br>10<br>10<br>10<br>10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

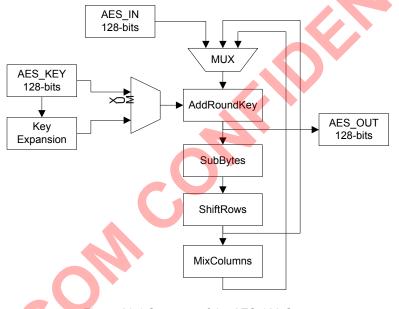

| 24.1 AES       11         24.1.1 AddRoundKey       11         24.1.2 SubBytes       11         24.1.3 ShiftRows       11         24.1.4 MixColumns       11         24.1.5 CCM       11         25. Flash memory controller       11         25.1 Flash controller command       11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10<br>10<br>10<br>10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 24.1.1 AddRoundKey       11         24.1.2 SubBytes       11         24.1.3 ShiftRows       11         24.1.4 MixColumns       11         24.1.5 CCM       11         25. Flash memory controller       11         25.1 Flash controller command       11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 10<br>10<br>10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 24.1.2 SubBytes       11         24.1.3 ShiftRows       11         24.1.4 MixColumns       11         24.1.5 CCM       11         25. Flash memory controller       11         25.1 Flash controller command       11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 10<br>10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 24.1.3 ShiftRows       11         24.1.4 MixColumns       11         24.1.5 CCM       11         25. Flash memory controller       11         25.1 Flash controller command       11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 24.1.4 MixColumns         11           24.1.5 CCM         11           25. Flash memory controller         11           25.1 Flash controller command         11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

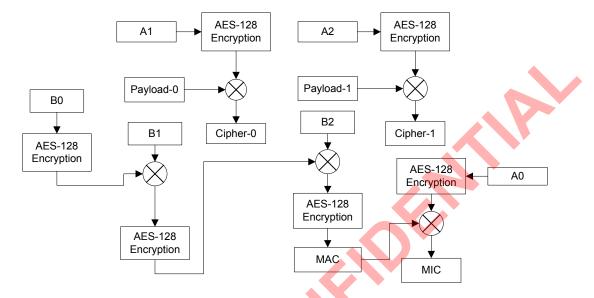

| 24.1.5 CCM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 25. Flash memory controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 25.1 Flash controller command                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 25.2 Flash controller operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 27. Abbreviations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 28. Ordering Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

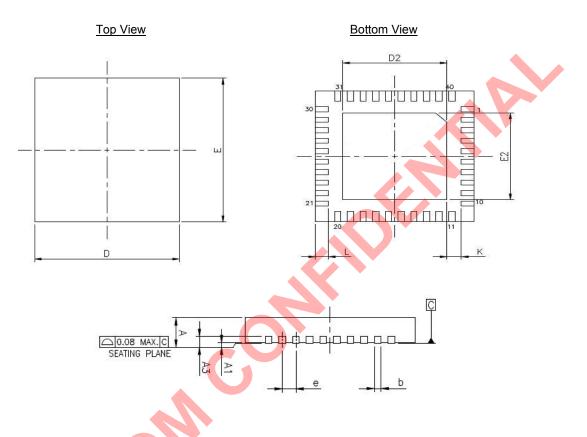

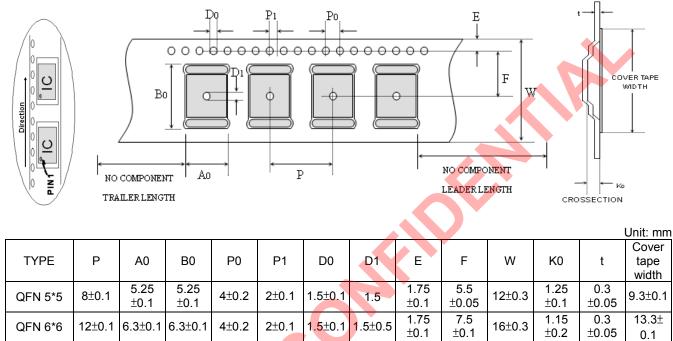

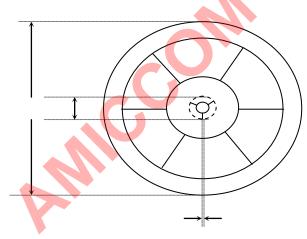

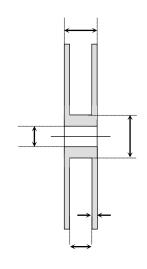

| 29. Package Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

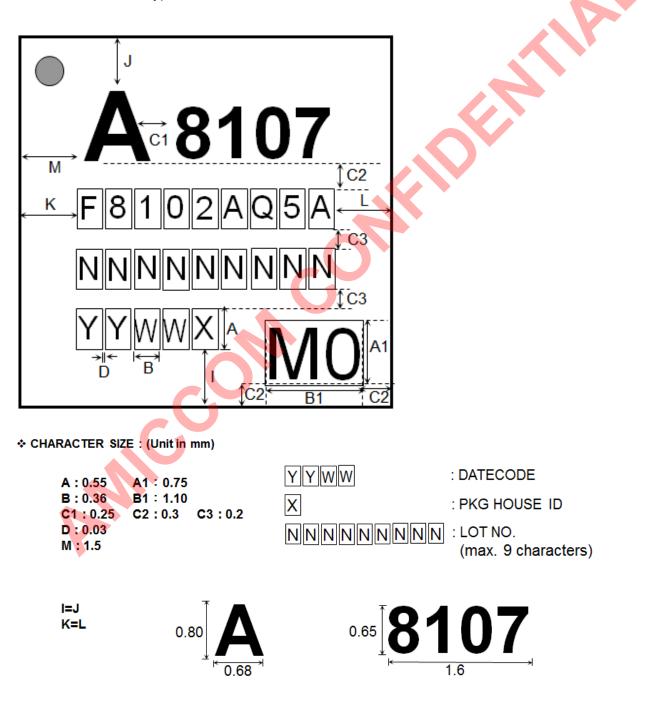

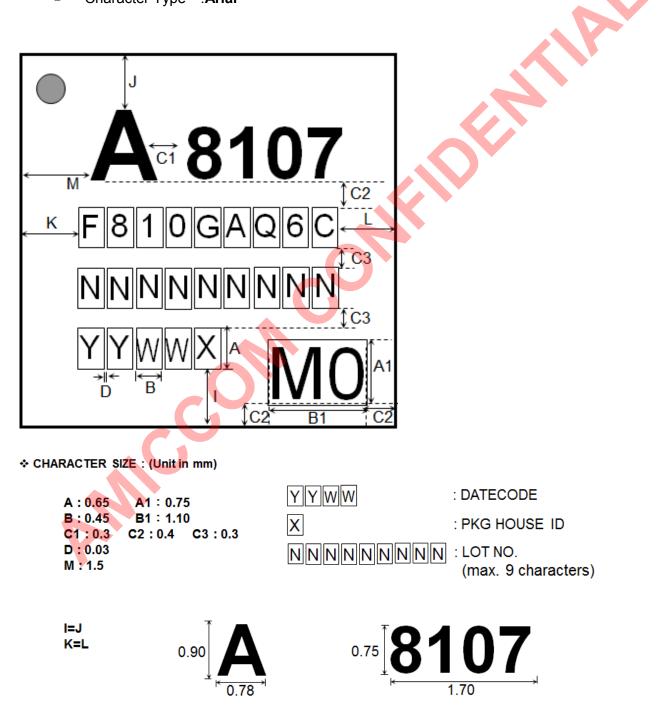

| 30. Top Marking Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

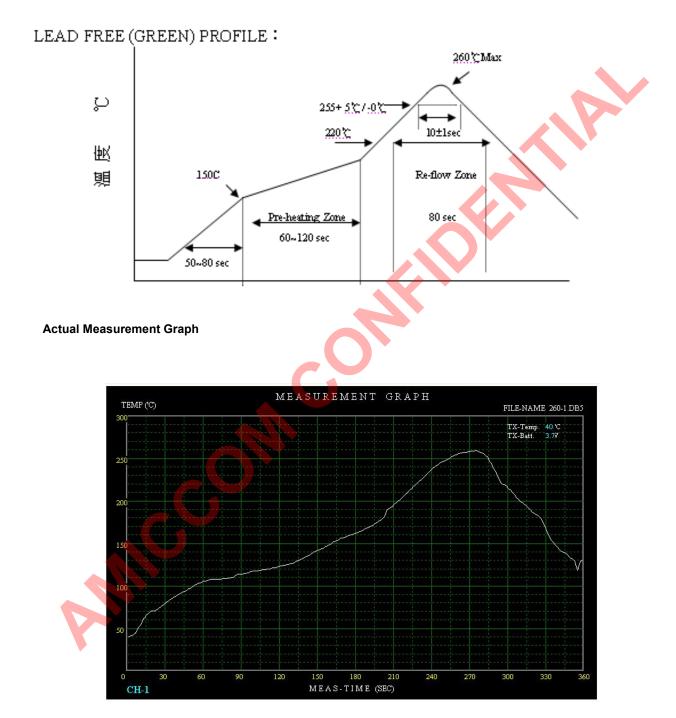

| 31. Reflow Profile                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 32. Tape Reel Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 33. Product Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

# Bluetooth Low Energy SoC

## 1. General Description

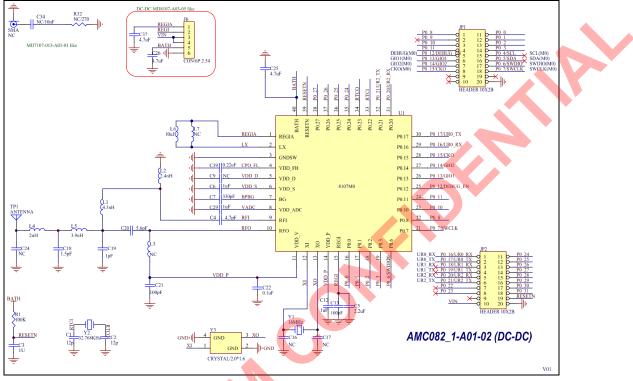

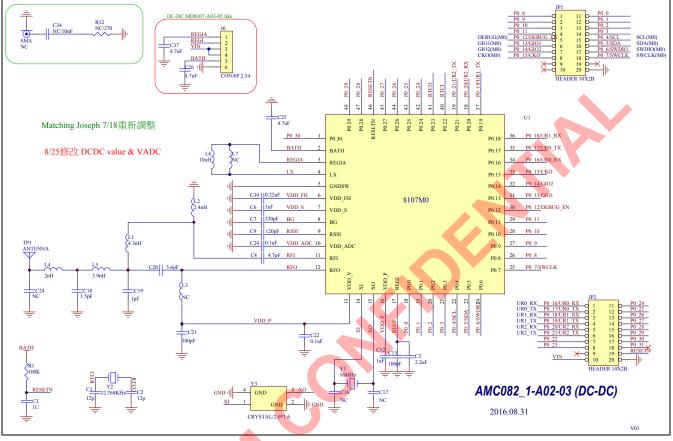

A8107M0 is a high performance and low cost 2.4GHz FSK/GFSK system-on-chip (SOC) wireless transceiver. With on chip fraction-N synthesizer, it can support the application of data rate from 5Kbps to 2Mbps and frequency hopping system and it is designed for Bluetooth Low Energy (Bluetooth 4.0 Single MODE). It is a Bluetooth smart device. This device integrates high ARM-M0 MCU, 256K Bytes In-system programmable flash memory, 32KB SRAM, various powerful functions and excellent performance of a leading 2.4GHz FSK/GFSK RF transceiver. It can be operated with wide voltage from 2.0V ~ 3.6V. A8107M0 has various operating MODEs, making it highly suited for systems where ultra-low power consumption is required. A8107M0 has 256K bytes flash that supports AES128 engine and CCM. For low current consumption, A8107M0 is integrated with both LDO and DC-DC (buck) so that this device can be operated more efficient when VDD voltage range from 2.7 to 3.6V. User can configure one of them (LDO or DC-DC) as a powered source for device operations. The device has 2 package sizes: QFN5X5 40 pin package and QFN6x6 48pin package.

Wireless toy and gaming

Bluetooth smart device

Helicopter and airplane radio controller

## 2. Typical Applications

- 2400 ~ 2483.5 MHz ISM frequency hopping system

- Smart remote controller

- Home and building automation

- Wireless keyboard and mouse

## 3. Features

- Package size (QFN5X5, 40 pins/ QFN6X6 48 pins).

- High performance ARM-M0 MCU

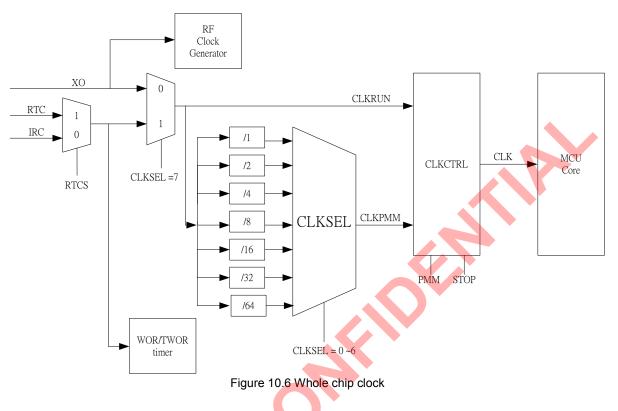

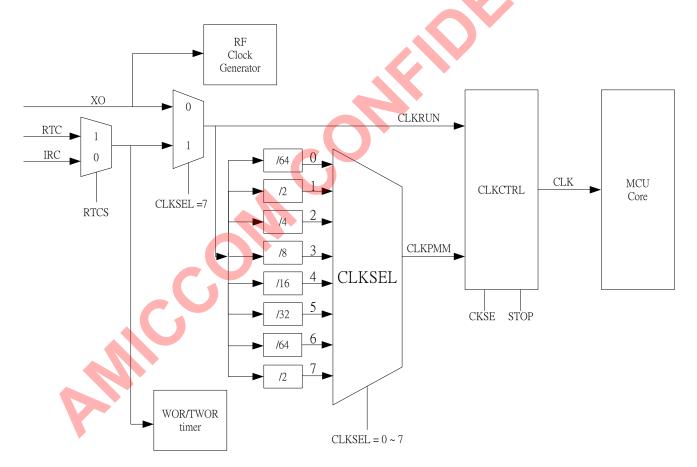

- Operation clock: 1, 1/2, 1/4, 1/8, 1/16, 1/32, 1/64 of crystal oscillator.

- TFT DMA controller and 8080 output interface(I80)

- 256KB Flash memory with copy protection, 32KB SARM

- UART, I<sup>2</sup>C, SPI serial communication

- Two 32-bit timers and one 32-bit dual MODE timer.

- Four Channel PWM

- Watchdog timer

- Two 16-bit Sleep timer

- In-Circuit Debugger

- In-System programming/ In-Application programming

- 23/31 GPIO for QFN40/48

- RX current consumption with MCU stop and DC-DC turn on: 6.4mA @BATH= 3.3V

- TX current consumption with MCU stop and DC-DC turn on: 9mA @ 5dBm, BATH=3.3V.

- Power saving MODE without sleep timer, no SRAM retention (1.3 uA)

- Power saving MODE with sleep timer, 16K SRAM retentio (2.1uA)

- Frequency band: 2400 2483MHz.

- FSK and GFSK modulation

- High sensitivity:

- -97dBm at 500Kbps data rate

- -94dm at 1Mbps data rate

- -91dBm at 2Mbps data rate

- Programmable data rate 5K ~ 2Mbps.

- Fast settling time synthesizer for frequency hopping system.

- Built-in thermal sensor for monitoring relative temperature.

- Built-in one channel 8-bits ADC for external analog voltage. (0V ~ 0.9V).

- Built-in eight channels 12-bits ADC for general purpose analog input (0V ~ 1.8 V).

- Built-in Low Battery Detector.

- Support 16MHz crystal

- Easy to use.

- Change frequency channel by one register setting.

- 8-bits Digital RSSI for clear channel indication.

- Auto RSSI measurement.

- Auto WOR (wake up when receive RX packet).

- Auto WOT (wake up to transmit TX packet).

- Auto Calibrations.

- Auto IF function.

- Auto Frequency Compensation.

- Auto CRC Check.

Separated 256 bytes RX and TX FIFO.

## 4. Pin Configurations

### 4.1 QFN40 5x5

Bluetooth Low Energy SoC

### 4.2 QFN48 6x6

## 5. Pin Descriptions (I: input; O: output, I/O: input or output)

## 5.1 A8107M0 QFN40 5x5 Package

| Pin No. | Symbol  | I/O     | Function Description                 |  |

|---------|---------|---------|--------------------------------------|--|

| 1       | REGIA   | AO      | DC-DC regulator output for buck      |  |

| 2       | LX      | AI      | DC-DC Inductor connection pin        |  |

| 3       | GNDSW   | AI      | Ground                               |  |

| 4       | VDD_FH  | AO      | Flash high voltage output            |  |

| 5       | VDD_D   | AO      | VDD_D supply voltage output          |  |

| 6       | VDD_S   | AO      | VDD_S supply voltage output          |  |

| 7       | BG      | AO      | Band gap output                      |  |

| 8       | VDD_ADC | AO      | /DD_ADC supply voltage output        |  |

| 9       | RFI     | AI      | RF input                             |  |

| 10      | RFO     | AO      | RF output                            |  |

| 11      | VDD_V   | AI      | VCO supply voltage input             |  |

| 12      | XI      | AI      | Crystal oscillator input             |  |

| 13      | XO      | AO      | Crystal oscillator output            |  |

| 14      | VDD_P   | AO      | PLL supply voltage output            |  |

| 15      | REGI    | AI      | Regulator input                      |  |

| 16      | P0.0    | DIO/AIO | SPI_CS                               |  |

| 17      | P0.1    | DIO/AIO | SPI_MISO                             |  |

| 18      | P0.2    | DIO/AIO | SPI_MOSI                             |  |

| 19      | P0.3    | DIO/AIO | SPI_SCK                              |  |

| 20      | P0.6    | DIO     | SWDIOTMS                             |  |

| 21      | P0.7    | DIO     | SWCLKTCK                             |  |

| 22      | P0.8    | DIO/AIO | timer0_EIN / ADC2 / BB_GIO1          |  |

| 23      | P0.10   | DIO/AIO | PWM2 / I <sup>2</sup> C_SCL          |  |

| 24      | P0.11   | DIO/AIO | PWM3 / I <sup>2</sup> C_SDA / LCD_TE |  |

| 25      | P0.12   | DIO/AIO | ADC4 / ICE_MODE / LCD_nRD            |  |

| 26      | P0.13   | DIO/AIO | ADC5/BB_GIO1 / LCD_Data[2]           |  |

| 27      | P0.14   | DIO/AIO | ADC6/BB_GIO2 / LCD_Data[1]           |  |

| 28      | P0.15   | DIO/AIO | ADC7/BB_CKO / LCD_Data[0]            |  |

| 29      | P0.16   | DIO/AIO | UART0_RX/LCD_nCS                     |  |

| 30      | P0.17   | DIO/AIO | UART0_TX / LCD_A0                    |  |

| 31      | P0.20   | DIO/AIO | UART2_RX / PWM0 / LCD_nWR/ s_LCD_SCL |  |

| 32      | P0.21   | DIO/AIO | UART2_TX / PWM1 / LCD_Data[7]        |  |

| 33      | P0.22   | DIO/AIO | RTCI                                 |  |

| 34      | P0.23   | DIO/AIO | RTCO                                 |  |

| 35      | P0.24   | DIO     | General IO / LCD_Data[6]             |  |

| 36      | P0.25   | DIO     | General IO / LCD_Data[5]             |  |

| 37      | P0.26   | DIO     | General IO / LCD_Data(4)             |  |

| 38 | P0.27  | DIO     | General IO / LCD_Data[3]                    |

|----|--------|---------|---------------------------------------------|

| 39 | RESETN | AI      | RESETN input                                |

| 40 | BATH   | DIO/AIO | DC-DC converter voltage input for buck mode |

### 5.2 A8107M0 QFN48 6x6 Package

| Pin No. | Symbol  | I/O     | Function Description                        |

|---------|---------|---------|---------------------------------------------|

| 1       | P0.30   | DIO     | General IO                                  |

| 2       | BATH    | DIO/AIO | DC-DC converter voltage input for buck mode |

| 3       | REGIA   | AO      | DC-DC regulator output voltage              |

| 4       | LX      | AI      | DC-DC Inductor connection pin               |

| 5       | GNDSW   | AI      | Ground                                      |

| 6       | VDD_FH  | AO      | Flash high voltage output                   |

| 7       | VDD_S   | AO      | VDD_S supply voltage output                 |

| 8       | BG      | AO      | Band gap output                             |

| 9       | RSSI    | AO      | RSSI Bypass                                 |

| 10      | VDD_ADC | AO      | VDD_ADC supply voltage output               |

| 11      | RFI     | AI      | RF input                                    |

| 12      | RFO     | AO      | RF output                                   |

| 13      | VDD_V   | AI      | VCO supply voltage input                    |

| 14      | XI      | AI      | Crystal oscillator input                    |

| 15      | XO      | AO      | Crystal o <mark>scill</mark> ator output    |

| 16      | VDD_P   | AO      | PLL sup <mark>ply volta</mark> ge output    |

| 17      | REGI    | AI      | Regulator input                             |

| 18      | P0.0    | DIO/AIO | SPI_CS                                      |

| 19      | P0.1    | DIO/AIO | SPI_MISO                                    |

| 20      | P0.2    | DIO/AIO | SPI_MOSI                                    |

| 21      | P0.3    | DIO/AIO | SPI_SCK                                     |

| 22      | P0.4    | DIO/AIO | I <sup>2</sup> C_SCL                        |

| 23      | P0.5    | DIO/AIO | I <sup>2</sup> C_SDA                        |

| 24      | P0.6    | DIO     | SWDIOTMS                                    |

| 25      | P0.7    | DIO     | SWCLKTCK                                    |

| 26      | P0.8    | DIO/AIO | Timer0_EIN / ADC2 / BB_GIO1                 |

| 27      | P0.9    | DIO/AIO | Timer1_EIN / ADC3 / BB_GIO2                 |

| 28      | P0.10   | DIO/AIO | PWM2 / I <sup>2</sup> C_SCL                 |

| 29      | P0.11   | DIO/AIO | PWM3 / I <sup>2</sup> C_SDA / LCD_TE        |

| 30      | P0.12   | DIO/AIO | ADC4 / ICE_MODE / LCD_nRD                   |

| 31      | P0.13   | DIO/AIO | ADC5/BB_GIO1 / LCD_Data[2]                  |

| 32      | P0.14   | DIO/AIO | ADC6/BB_GIO2 / LCD_Data[1]                  |

| 33      | P0.15   | DIO/AIO | ADC7/BB_CKO / LCD_Data[0] / s_LCD_SDA       |

| 34      | P0.16   | DIO/AIO | UART0_RX/LCD_nCS                            |

| 35      | P0.17   | DIO/AIO | UART0_TX/LCD_A0                             |

| 36      | P0.18   | DIO/AIO | UART1_RX / BB_GIO1                          |

Oct., 2016, Version 0.2 (Preliminary)

# Bluetooth Low Energy SoC

Oct., 2016, Version 0.2 (Preliminary)

## 6. Chip Block Diagram

Fig6-1, A8107M0 Block Diagram

## 7. Absolute Maximum Ratings

| Parameter                        | With respect to        | Rating     | Unit    |  |

|----------------------------------|------------------------|------------|---------|--|

| Supply voltage range (VDD)       | oltage range (VDD) GND |            | V       |  |

| Digital IO pins range            | GND -0.3 ~ VDD+0.3     |            | V       |  |

| Voltage on the analog pins range | GND                    | -0.3 ~ 2.1 | ~ 2.1 V |  |

| Input RF level                   |                        | 14         | dBm     |  |

| Storage Temperature range        |                        | -55 ~ 125  | °C      |  |

| ESD Rating HBM                   |                        | ± 2K       | V       |  |

|                                  | MM                     | ± 100      | V       |  |

\*Stresses above those listed under "Absolute Maximum Rating" may cause permanent damage to the device. These are stress ratings only; functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

\*Device is ESD sensitive. Use appropriate ESD precautions. HBM (Human Body MODE) is tested under MIL-STD-883F Method 3015.7. MM (Machine MODE) is tested under JEDEC EIA/JESD22-A115-A. \*Device is Moisture Sensitivity Level III (MSL 3).

## 8. Electrical Specification

(Ta=25°C, **BATH = 3.3V**, unless otherwise noted)

| Parameter                               | Description                              | Min. | Тур. | Max.   | Unit |

|-----------------------------------------|------------------------------------------|------|------|--------|------|

| General                                 |                                          |      |      |        |      |

| Operating Temperature                   |                                          | -40  |      | 85     | °C   |

| Supply Voltage (BATH)                   | BATH supply input 2.0 3.6                |      | 3.6  | V      |      |

| Current Consumption                     | PM1 with sleep timer                     |      | 3.3  |        | uA   |