**AA88349**

PRELIMINARY 8-BIT DAC

### DESCRIPTION

The AA88349 is a CMOS processed digital to analog converter (DAC) with 8-bit resolution, low leakage and operating current. The AA88349 has 3 channels with build in operational amplifier output buffers which could operate in the full-swing voltage range from VCC to GND and enhance the Drive/Sink ability up to max. 1mA. Digital data (DI) input serially in a max. 2.5MHz clock (CLK) rate. The latched 12-bit digital data is converted into an analog DC voltage in the range from GND to VCC with 8-bit resolution in one of the 3 channels by the D/A converter in a max. 100  $\mu$  s settling time. AA88349 is a single 5V power DAC. Analog DC output could be full voltage swing as the analog power is equal to the system power. In addition to normal D/A converter applications, AA88349 is also available for electronic volume and instead of potentio- meters for adjustment due to its high stability on the capacitive load. 8 pins TSSOP package type are available for AA88349. Its operational temper- nature range is specified over  $-20^{\circ}\text{C}$  to  $85^{\circ}\text{C}$ .

### **■ FEATURES**

- 12 bits serial data input (3 wire serial data transfer method, DI, CLK, LD)

- R-2R resistor ladder used for D/A conversion

- 3 channels with 8-bit resolution monotonic D/A converter

- 3 channels buffer operational amplifiers operating in the full voltage range from VCC to GND

- Max. 2.5 MHz serial digital data input

- Serial I/O for cascade application

- Max. 1.0 mA output drive/sink current

- Single +5 V system power supply

#### APPLICATION

DVD, CD-R, CD-RW, DVC, digital camera, and other industrial equipments

## **AA88349**

PRELIMINARY 8-BIT DAC

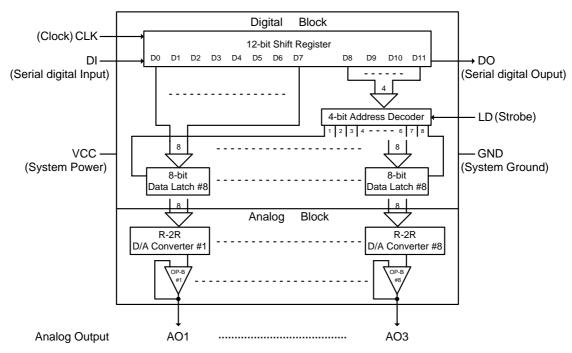

### BLOCK DIAGRAM

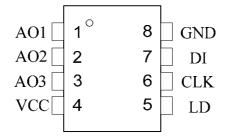

### **■ PIN DESCRIPTIONS**

Top View

| PIN NO. | PIN NAME | PIN FUNCTION                                                                                                                                                             |

|---------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4       | VCC      | +5V system power supply pin .                                                                                                                                            |

| 8       | GND      | System ground pin                                                                                                                                                        |

| 6       | CLK      | Serial clock input pin. At its rising edge, DI data shift into the Shift-Register.                                                                                       |

| 5       | LD       | Data Strobe pin. When it's on high, upper 4-bit and lower 8-bit of the 12-bit in the Shift-Register be latched into the Address Decoder and the Data-Latch, respectively |

# **AA88349**

### PRELIMINARY 8-BIT DAC

| PIN NO.    | PIN NAME                           | PIN FUNCTION                     |  |  |  |  |  |

|------------|------------------------------------|----------------------------------|--|--|--|--|--|

| Data Input |                                    |                                  |  |  |  |  |  |

| 7          | 7 D1 Serial Digital Data input pin |                                  |  |  |  |  |  |

| DAC Outp   | ut                                 |                                  |  |  |  |  |  |

| 1          | AO1                                | 8-bit D/A converter outputs      |  |  |  |  |  |

| 2          | AO2                                | Output range is from GND to VCC  |  |  |  |  |  |

| 3          | AO3                                | Output range is noin Give to voc |  |  |  |  |  |

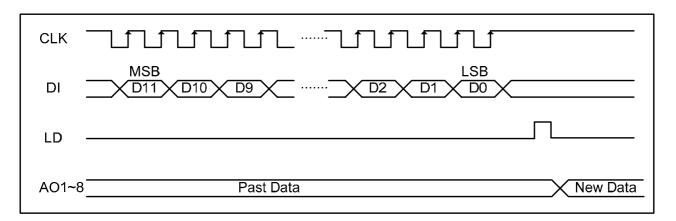

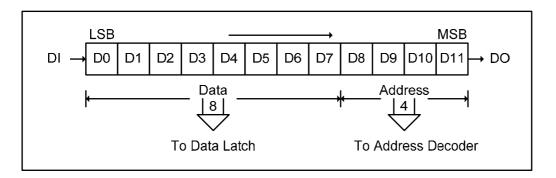

### DATA INPUT FORMAT

### DATA FORMAT IN SHIFT REGISTER

## **AA88349**

PRELIMINARY 8-BIT DAC

### DATA CONVERSION

| DATA |    |          |          |    |    |    | DAC OUTPUT LEVEL |              |

|------|----|----------|----------|----|----|----|------------------|--------------|

| D7   | D6 | D5       | D4       | D3 | D2 | D1 | D0               | AOX          |

| 0    | 0  | 0        | 0        | 0  | 0  | 0  | 0                | GND          |

| 0    | 0  | 0        | 0        | 0  | 0  | 0  | 1                | GND + LSB*   |

| 0    | 0  | 0        | 0        | 0  | 0  | 1  | 0                | GND+ 2 * LSB |

| {    | {  | <b>\</b> | <b>\</b> | {  | {  | {  | <b>\</b>         | <b>w</b>     |

| 1    | 1  | 1        | 1        | 1  | 1  | 1  | 0                | VCC - LSB    |

| 1    | 1  | 1        | 1        | 1  | 1  | 1  | 1                | VCC          |

● LSB = (VCC-GND)/255

#### CHANNEL MAP

| ADDRES | 3     |           |            |          |          |          |     |

|--------|-------|-----------|------------|----------|----------|----------|-----|

| 1H     | D-L#1 | <b></b>   | R-2R D/A#1 | <b></b>  | OP-B#1   | <b></b>  | AO1 |

| 2H     | D-L#1 | <b>├</b>  | R-2R D/A#2 | <b></b>  | OP-B#2   | <b>├</b> |     |

| 3H     | D-L#1 | <b></b> [ | R-2R D/A#3 | <b>├</b> | OP-B#3   | <b>►</b> |     |

| 4H     | D-L#1 | <b></b>   | R-2R D/A#4 | ▶ [      | OP-B#4   | <b></b>  |     |

| 5H     | D-L#1 | -         | R-2R D/A#5 |          | OP-B#5   | -        | AO2 |

| 6H     | D-L#1 | -         | R-2R D/A#6 | -        | OP-B#6   | -        | AO3 |

| 7H     | D-L#1 | -         | R-2R D/A#7 |          | OP-B#7   | -        |     |

| 8H     | D-L#1 | -         | R-2R D/A#8 | -        | OP-B#8   | <b></b>  |     |

|        |       |           | //         | ı L      | <u> </u> | J L      |     |

### ADDRESS DECODING

|    | ADDR | ESS | DATA LATCH SELECTED |                     |

|----|------|-----|---------------------|---------------------|

| D8 | D9   | D10 | D11                 | DATA EATON OLLEGIED |

| 0  | 0    | 0   | 0                   | NA                  |

| 0  | 0    | 0   | 1                   | Data Latch #1       |

| 0  | 0    | 1   | 0                   | NA                  |

| 0  | 0    | 1   | 1                   | NA                  |

| 0  | 1    | 0   | 0                   | NA                  |

| 0  | 1    | 0   | 1                   | Data Latch #2       |

| 0  | 1    | 1   | 0                   | Data Latch #3       |

| 0  | 1    | 1   | 1                   | NA                  |

# **AA88349**

PRELIMINARY 8-BIT DAC

|    | ADDR | ESS |     |                     |

|----|------|-----|-----|---------------------|

| D8 | D9   | D10 | D11 | DATA LATCH SELECTED |

| 1  | 0    | 0   | 1   | NA                  |

| 1  | 0    | 1   | 0   | NA                  |

| 1  | 0    | 1   | 1   | NA                  |

| 1  | 1    | 0   | 0   | NA                  |

| 1  | 1    | 0   | 1   | NA                  |

| 1  | 1    | 1   | 0   | NA                  |

| 1  | 1    | 1   | 1   | NA                  |

### ABSOLUTE MAXIMUM RATINGS

Ta=25°C, unless otherwise noted

| PARAMETER                     | SYMBOL   |      | UNIT |           |                         |

|-------------------------------|----------|------|------|-----------|-------------------------|

| FARAIVIETER                   | STIVIBUL | MIN  | TYP  | MAX       | UNII                    |

| System Voltage                | VCC      | -0.3 | _    | +7.0      | V                       |

| Input Voltage                 | VIN      | -0.3 | _    | VCC + 0.3 | V                       |

| Output Voltage                | VOUT     | -0.3 | _    | VCC + 0.3 | V                       |

| Power Dissipation             | PD       | _    | _    | 250       | mW                      |

| Operating Ambient Temperature | TA       | -20  | _    | +85       | $^{\circ}\!\mathbb{C}$  |

| Storage Temperature           | TS       | -55  | _    | +150      | $^{\circ}\! \mathbb{C}$ |

NOTE: Stress above those listed under "Absolute Maximum Rating" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for the extended periods of time may affect device reliability.

### ■ ELECTRICAL CHARACTERISTICS

#### RECOMMENDED OPERATING CONDITIONS

| SYMBOL | PARAMETER             | CONDITIONS     | LIMITS |     |      | UNIT |

|--------|-----------------------|----------------|--------|-----|------|------|

|        |                       |                | MIN    | TYP | MAX  |      |

| VCC    | System Voltage        |                | 4.5    | 5.0 | 5.5  | V    |

| GND    | System voltage        |                | _      | 0   | _    | V    |

| IAO    | Analog Output Current | VAO shift≦0.3V | -1.0   | _   | +1.0 | mA   |

# **AA88349**

PRELIMINARY 8-BIT DAC

|        |                                                      |            |     | UNIT |      |                        |

|--------|------------------------------------------------------|------------|-----|------|------|------------------------|

| SYMBOL | PARAMETER                                            | CONDITIONS | MIN | TYP  | MAX  | Oitii                  |

| COL    | Analog Output Load Capacitance for Oscillation limit |            | _   | _    | +1.0 | μF                     |

| TA     | Operating Ambient<br>Temperature                     |            | -20 | _    | +85  | $^{\circ}\!\mathbb{C}$ |

### **◆** DC CHARACTERISTICS

Ta = 25°C

| PARAMETER                  | SYMBOL  | V            | 'ALU | E         | UNIT    | CONDITIONS            |

|----------------------------|---------|--------------|------|-----------|---------|-----------------------|

| ANAMETER                   | OTHIBOL | MIN          | TYP  | MAX       | 01111   | CONDITIONS            |

| System Voltage             | VCC     | 4.5          | 5.0  | 5.5       | V       |                       |

| System Current             | ICC     | _            | 1.2  | 2.5       | mA      | CLK = 1 MHz, No load; |

| Input Leakage Current      | IILK    | <b>-</b> 5   | _    | +5        | $\mu$ A | VIN = 0V / 5V         |

| Digital Input Low Voltage  | VIL     | _            | _    | 0.2 • VCC | V       |                       |

| Digital Input High Voltage | VIH     | 0.5 • VCC    | _    | _         | V       |                       |

| Digital Output Low         | VOL     | _            | _    | 0.4       | V       | IOL = +2.5 mA         |

| Digital Output High        | VOH     | VCC -<br>0.4 | _    | _         | V       | IOH = -400 μ A        |

NOTES: Integral Non-Linearity: The difference between the digital data converted DC analog values and a reference straight line drawn through the first and the last output values Differential Non-Linearity: The difference between the ideal and real increment value of DC analog voltage when the digital data increase 1 bit.

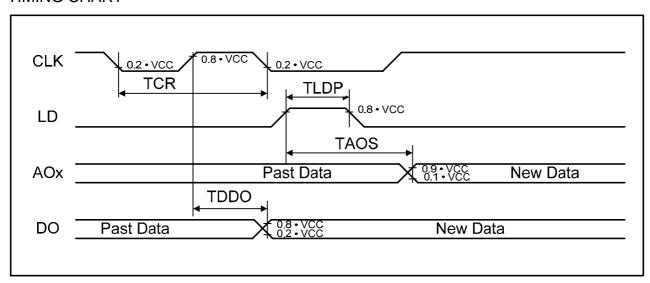

### **◆ AC CHARACTERISTICS**

Ta = 25°C

| PARAMETER                    | SYMBOL VALUE |     | UNIT | CONDITIONS |       |                                              |  |

|------------------------------|--------------|-----|------|------------|-------|----------------------------------------------|--|

| TARAMETER                    | O I WIDOL    | MIN | TYP  | MAX        | 01411 |                                              |  |

| Clock Rate                   | TCR          | 400 | 1000 |            | ns    |                                              |  |

| Load Strobe Pulse<br>Width   | TLDP         | _   | 200  |            | ns    |                                              |  |

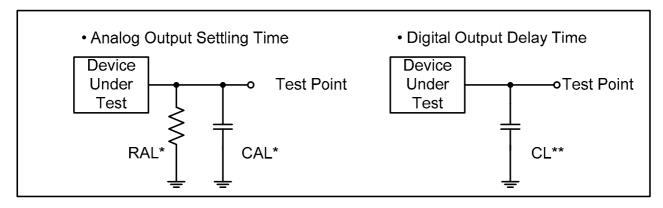

| Analog Output Settling Time  | TAOS         | _   |      | 100        | μs    | *RAL = 10 k $\Omega$ , CAL = 50pF (#00> #FF) |  |

| Digital Output Delay<br>Time | TDDO         | _   | _    | 350        | ns    | **CL = 100 pF (Max.)                         |  |

**AA88349**

PRELIMINARY 8-BIT DAC

#### AC TEST CONDITION

#### **TIMING CHART**

### ORDERING INFORMATION

| ORDER NO. | PACKAGE | PACKING     | ONE REEL Q'TY | MARK CHART         |

|-----------|---------|-------------|---------------|--------------------|

| AA88349A  | TSSOP8L | Tape & Reel | 3,000ea       | 88349<br>XXXX<br>A |

## **AA88349**

PRELIMINARY 8-BIT DAC

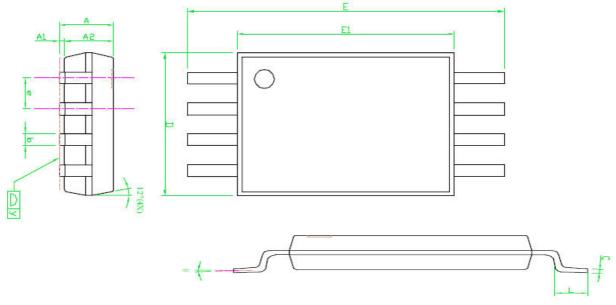

### **■ PACKAGE DIMENSIONS**

#### NOTES:

Package body sizes exclude mold flash protrusions or gate burrs

Tolerance ± 0.1 (4 mil) unless otherwise specified

Coplanarity:0.1mm

Controlling dimension is millimeter converted inch dimensions are not necessarily exact Followed from jedec mo-153

| SYMBOLS  | DIMENSIONS IN<br>MILLIMETERS |      |      | DIMENSIONS IN INCHES |       |       |

|----------|------------------------------|------|------|----------------------|-------|-------|

|          | MIN                          | NOM  | MAX  | MIN                  | NOM   | MAX   |

| A        |                              |      | 1.20 |                      |       | 0.048 |

| A1       | 0.05                         |      | 0.15 | 0.002                |       | 0.006 |

| A2       | 0.80                         | 1.00 | 1.05 | 0.031                | 0.039 | 0.041 |

| b        | 0.19                         |      | 0.30 | 0.007                |       | 0.012 |

| C        | 0.09                         |      | 0.20 | 0.004                |       | 0.008 |

| D        | 2.90                         | 3.00 | 3.10 | 0.114                | 0.118 | 0.122 |

| Е        | 6.20                         | 6.40 | 6.60 | 0.244                | 0.252 | 0.260 |

| E1       | 4.30                         | 4.40 | 4.50 | 0.169                | 0.173 | 0.177 |

| e        |                              | 0.65 |      |                      | 0.026 |       |

| L        | 0.45                         | 0.60 | 0.75 | 0.018                | 0.024 | 0.030 |

| у        |                              |      | 0.10 |                      |       | 0.004 |

| $\theta$ | 0°                           |      | 8°   | 0°                   |       | 8°    |