# **USB Type-C Port Controller**

## **General Description**

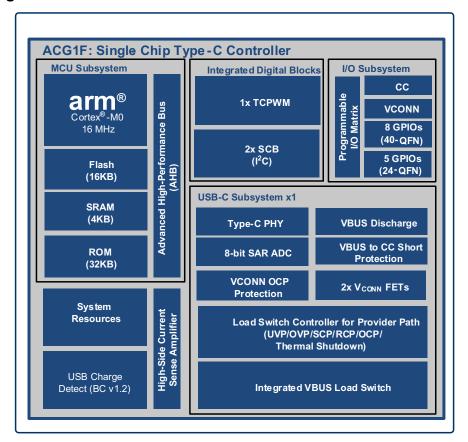

ACG1F (Type-A to Type-C Generation - 1 FET) is a single-port USB Type-C controller that complies with the latest USB Type-C specifications. ACG1F provides a complete USB Type-C control solution for notebooks and desktops. It can also be used in devices required to convert legacy Type-A data port to Type-C data port. ACG1F uses Cypress' proprietary M0S8 technology with a 32-bit Arm<sup>®</sup> Cortex<sup>®</sup>-M0 processor with 16-KB flash and integrates a Type-C controller (no Power Delivery) and a VBUS load switch (5 V/3A).

#### **Features**

#### **USB Type-C Support**

- Integrated Type-C controller supporting Type-C v1.3

- Integrated 2x VCONN FET with OCP to power EMCA cable

### **Integrated VBUS Load Switch Controller**

- Integrated VBUS load switch supports

- □ 5 V/3A VBUS NFET

- $\hfill \square$  RDSon of load switch: 45-m $\Omega$  (typ) for 40-QFN,15-m $\Omega$  (typ) for 24-QFN

- Slew rate control turn-ON on the provider VBUS switch

- Configurable hardware-controlled VBUS overvoltage protection (OVP), overcurrent protection (OCP), and reverse current protection (RCP)

- VBUS high-side current sense amplifier across external precision series resistance (Rsense) of 5 m $\Omega$ .

- Over temperature thermal shutdown

- VBUS to CC short circuit protection up to 20 V

### 2x I<sup>2</sup>C

- Supports USB Type-C Connector System Software Interface (UCSI) over I<sup>2</sup>C interface

- Controls external high-speed redriver/retimer mux interface over I<sup>2</sup>C

### **Legacy Charging**

■ Integrated Charge Detect: BC v1.2

#### 32-bit MCU Subsystem

- 16-MHz Arm Cortex-M0 CPU

- 16-KB Flash

- 4-KB SRAM

- 32-KB SROM

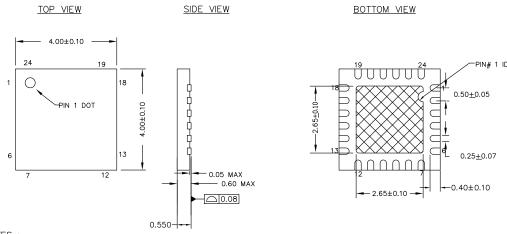

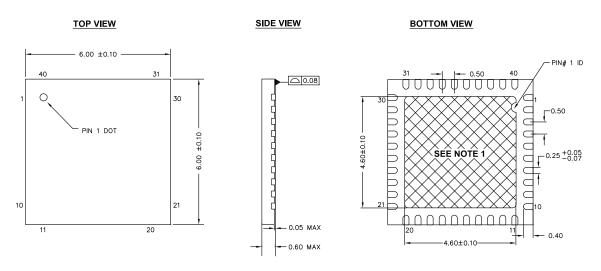

#### **Packages**

- 40-QFN, 0.5-mm pitch

- 24-QFN, 0.5-mm pitch

- Supports industrial temperature range (-40 °C to +85 °C)

Cypress Semiconductor Corporation Document Number: 002-26356 Rev. \*D

# **Logic Block Diagram**

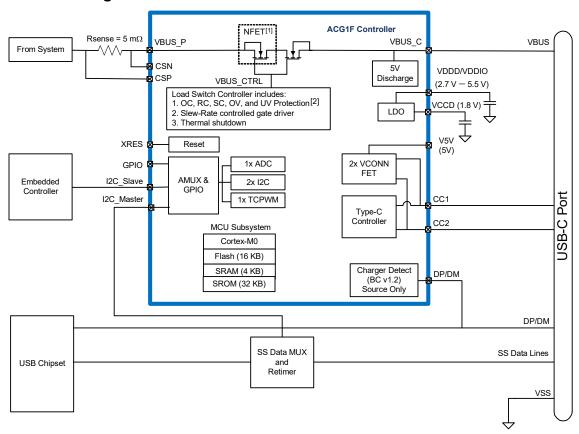

# **Functional Block Diagram**

### Notes

- 1. This NFET is available in the 40-QFN part only.

- 2. RC protection only available in 40-QFN part.

# **ACG1F Datasheet**

## **Contents**

| Functional Overview             | 5  |

|---------------------------------|----|

| USB Type-C Subsystem            | 5  |

| MCU and Memory                  |    |

| Power System Overview           | 7  |

| Power Modes                     | 7  |

| Peripherals                     | 8  |

| Timer/Counter/PWM Block (TCPWM) | 8  |

| GPIO                            | 8  |

| Pinouts                         | 9  |

| Application Diagrams            | 12 |

| Device Configuration Parameters | 14 |

| Electrical Specifications       | 15 |

| Absolute Maximum Ratings        | 15 |

| Device-Level Specifications     |    |

| Digital Peripherals             | 19 |

| System Resources                | 20 |

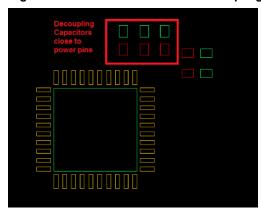

| Hardware Design Guidelines      | 26 |

| ESD and EMI/EMC Protection      | 26 |

| TVS Diode on VBUS C Pin         | 26 |

|                                 |    |

| Placement of Bulk and Decoupling Capacitors | ∠¢ |

|---------------------------------------------|----|

| Placement of Power and Ground Planes        | 27 |

| Voltage Regulation                          | 27 |

| Power Domain Routing                        |    |

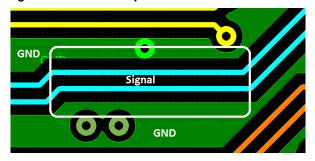

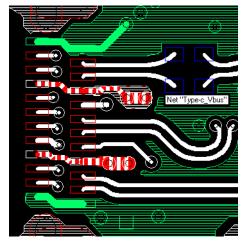

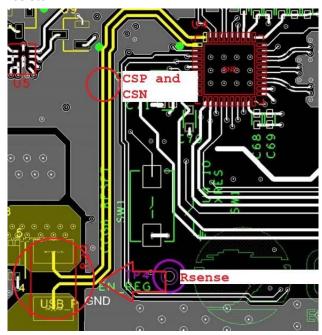

| Routing of Type-C (USB Data and CC) Lines   | 27 |

| Routing of CSP and CSN Lines                |    |

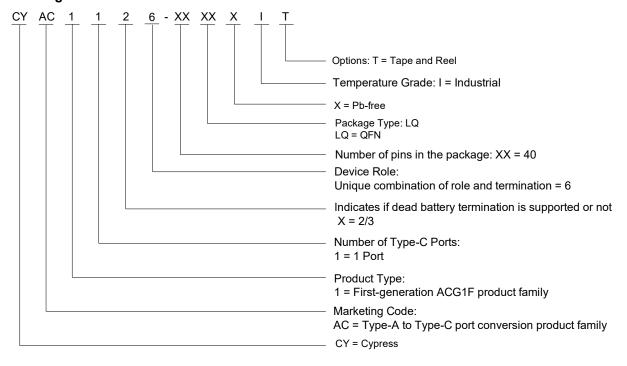

| Ordering Information                        |    |

| Ordering Code Definitions                   |    |

| Packaging                                   |    |

| Acronyms                                    |    |

| Document Conventions                        | 32 |

| Units of Measure                            | 32 |

| Document History Page                       | 33 |

| Sales, Solutions, and Legal Information     | 34 |

| Worldwide Sales and Design Support          |    |

| Products                                    |    |

| PSoC® Solutions                             | 34 |

| Cypress Developer Community                 | 34 |

| Technical Support                           |    |

#### **Functional Overview**

#### **USB Type-C Subsystem**

This subsystem provides the interface to the Type-C USB port and comprises the following:

- USB-PD Physical Layer (only Rp terminations and Line-Comparators)

- VCONN FETs

- ADC

- Undervoltage, overvoltage, and reverse-current protection on VBUS

- High-side current sense amplifier for VBUS with OCP and short-circuit protection (SCP)

- VBUS Discharge

- Gate Driver for VBUS NFET

- Charger Detect

#### USB-PD Physical Layer

The USB Type-C subsystem contains the USB-PD physical layer block and supporting circuits. The USB-PD Physical Layer consists of only two Deep Sleep comparators that are used to detect Type-C attach/detach, CC line activity events, and determine the voltage range on the chosen CC line. In addition, the block includes Rp termination and their switches as required by the USB Type-C spec. The Rp termination is implemented using current sources to indicate the current profiles supported by DFP.

#### **VCONN FET**

ACG1F has power supply input V5V pin for providing power to EMCA cables through integrated VCONN FETs. There are two VCONN FETs in ACG1F to power either CC1 or CC2 pins. These FETs are capable of sourcing maximum of 1.0W on the CC1 or CC2 pin to power active EMCA cables. At any given time, only one of the VCONN FETs shall be ON. The floating V5V pin should not cause ACG1F to malfunction and draw more current.

#### ADC

ACG1F has one low-footprint 8-bit SAR ADC available for general purpose A-D conversion applications in the chip. The ADC can be accessed from the GPIOs through an on-chip analog mux.

#### Undervoltage and Overvoltage Protection on VBUS

The chip implements an undervoltage/overvoltage (UVOV) detection circuit for the VBUS supply. The thresholds for both OCP and UVOV are made programmable.

#### High-side Current Sense Amplifier for VBUS

The chip supports the programmable threshold VBUS current sensing through the VBUS path. External resistor (5  $\mbox{m}\Omega$ ) placed in the connector VBUS path connects to the chip, and the drop across this resistor is monitored to sense the magnitude of current.

#### VBUS Reverse Current Protection

ACG1F restricts reverse current to zero on the VBUS provider path when Type-C VBUS is greater than VIN (provider voltage before the VBUS NFET). ACG1F reacts quickly (less then 1  $\mu s$  - Typ) and turns off the VBUS provider NFET.

#### VBUS Discharge

The chip supports 21.5-V VBUS discharge circuitry inside the 40-QFN package and 5-V VBUS discharge circuitry inside the 24-QFN package. After cable removal detection, the chip will discharge the residual charge and bring the floating VBUS back to 0.8 V.

#### VBUS Load Switch

ACG1F has an integrated VBUS provider load switch, which includes OVP, OCP, SCP, RCP protection, and high-side current sense amplifier. ACG1F supports thermal protection where the load switch is turned OFF when the on-chip temperature rises above the threshold temperature and turns ON the load switch when the device temperature falls below threshold temperature.

#### Gate Driver for VBUS NFET

ACG1F has an integrated gate driver to drive NFETs on the VBUS provider path.

#### Charger Detect

The chip implements battery charger emulation (source) for USB BC.1.2.

#### High-Voltage Tolerant CC Lines

The chip supports high-voltage tolerant CC lines. In the case of CC short to VBUS through connectors, these lines will be protected internally.

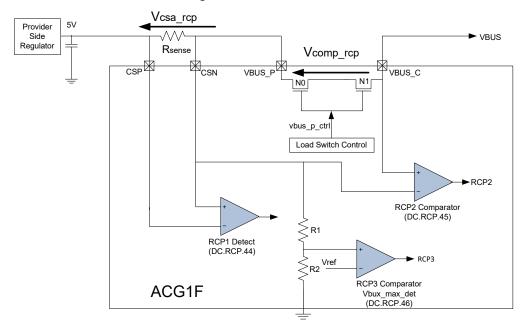

#### Reverse Current Protection (RCP)

ACG1F controller supports RCP in 40-QFN package. ACG1F integrates the RCP circuitry that has the capability of sensing reverse current that lasts for more than 10 µs and protects the system by shutting down the Gate automatically upon detection of such events. ACG1F provides RCP circuitry that can detect reverse current flow from connector VBUS\_C to provider VBUS\_P. The RCP event is recognized whenever VBUS\_C > VBUS\_P while provider FET is ON, causing current to flow from connector VBUS to provider VBUS. After recognizing the RCP event, the provider FET is shut down thus isolating the provider and connector VBUS. ACG1F has three distinct mechanisms to detect the reverse current as shown in Figure 1.

Figure 1. RCP Mechanism

- Mechanism 1: A comparator senses the voltage drop across external Rsense through pins CSP and CSN. This comparator signals an RCP event whenever CSN > CSP by the Vcsa\_rcp voltage given in Table 28. The output of this comparator RCP1 is shown in Figure 1.

- Mechanism 2: A comparator senses the voltage drop across provider FET through CSN and VBUS pin of ACG1F. This comparator signals an RCP event whenever VBUS > CSN by the Vcomp\_rcp voltage given in Table 28. The output of this comparator RCP2 is shown in Figure 1.

- Mechanism 3: A comparator senses the 33.33% voltage of the CSN pin and compares it against Vref = 1.79 V for 5-V provider VBUS application. This comparator signals an RCP event whenever CSN voltage goes above Vbus\_max\_det voltage given in Table 28 for a 5-V application. The output of this comparator RCP3 is shown in Figure 1. Note that Vref is programmable and the voltage divider has an option to use 25% or 33.33% value which is configurable only through firmware. To change the Vref value to 25%, contact local Cypress Sales Representative.

When any one of the three comparator outputs show an RCP event, then the provider FET is turned OFF.

#### **MCU and Memory**

#### CPU

The Cortex M0 in ACG1F is part of a 32-bit MCU subsystem, which is optimized for low-power operation with extensive clock gating. The CPU also includes a serial wire debug (SWD) interface, which is a 2-wire form of JTAG. The debug configuration used for ACG1F has 4 break-point (address) comparators and two watchpoint (data) comparators.

#### Flash

The 16-KB integrated Flash memory shall store the firmware implementing Type-C functionality. The 16-KB flash shall support in-system firmware upgrade through the SWD or I<sup>2</sup>C interface A section of Flash can be used for storing Device/System power parameters. The flash row size is 64 Bytes.

#### **SROM**

The 32-KB SROM contains boot and configuration routines. The SROM will also be used for storing frequently-used functionalities in the firmware.

## SRAM

The 4-KB RAM is used under software control to store temporary status of system variables and parameters.

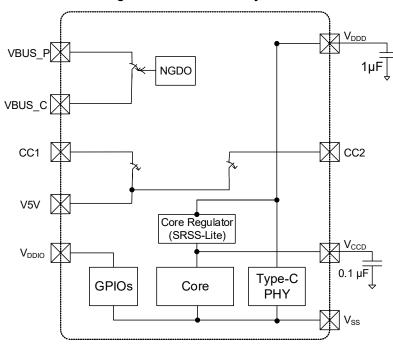

## **Power System Overview**

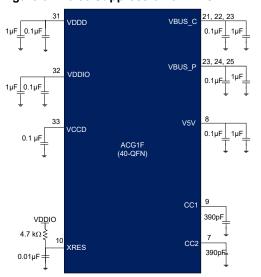

ACG1F operates on a single power-supply input VDDD with a valid range of (2.7 V-5.5 V). In addition, there is a V5V supply pin that sources the VCONN supply to the Type-C connector; the valid levels on the V5V supply can range from 4.85 V-5.5 V. V5V does not power the chip. The V5V supply support operation over 4.85 V-5.5 V while the VDDD input supports operation over 2.7 V-5.5 V. ACG1F has two different power modes: Active and Deep Sleep, transitions between which are managed by the Power System. A separate power domain VDDIO is provided for the GPIOs. VDDD should be shorted to VDDIO at system level. The VCCD pin, the output of the core (1.8 V) regulator, is brought out for connecting a 0.1- $\mu$ F capacitor for the regulator stability only. The VCCD pin is not supported as a power supply.

Figure 2. ACG1F Power System

#### **Power Modes**

Table 1 lists the power modes of the device, accessible and observable by the user.

Table 1. ACG1F Power Modes

| Mode       | Description                                                                                                                                              |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET      | Power is valid and XRES is not asserted. An internal reset source is asserted or SleepController is sequencing the system out of reset.                  |

| ACTIVE     | Power is valid and CPU is executing instructions.                                                                                                        |

| DEEP SLEEP | Main regulator and most hard-IPs are shut down. DeepSleep regulator powers logic, but only low-frequency clock is available.                             |

| SCAN       | System is in Scan mode. Scan mode is entered by applying DFT key during XRES and exited by applying something other than the DFT key (at least one bit). |

#### **Peripherals**

ACG1F has two SCBs, which can each implement only an I<sup>2</sup>C.

**I<sup>2</sup>C Mode:** The hardware I<sup>2</sup>C block implements a full multi-master and slave interface (it is capable of multimaster arbitration). This block is capable of operating at speeds of up to 1 Mbps (Fast Mode Plus) and has flexible buffering options to reduce interrupt overhead and latency for the CPU.

The SCB blocks support 8-deep FIFOs for Receive and Transmit, which, by increasing the time given for the CPU to read data, greatly reduces the need for clock stretching caused by the CPU not having read data on time. The FIFO mode is available in all channels and is very useful in the absence of DMA. Data throughput is not a critical consideration for I<sup>2</sup>C.

The I<sup>2</sup>C peripheral is compatible with the I<sup>2</sup>C Standard-mode, Fast-mode, and Fast-Mode Plus devices as defined in the NXP I<sup>2</sup>C bus specification and user manual (UM10204). The I<sup>2</sup>C bus I/O is implemented with GPIO in open-drain modes. The I<sup>2</sup>C bus uses open-drain drivers for clock and data with pull-up resistors on the bus for clock and data connected to all nodes. The required Rise and Fall times for different I<sup>2</sup>C speeds are guaranteed by using appropriate pull-up resistor values depending on VDDD, bus capacitance, and resistor tolerance. For detailed information on how to calculate the optimum pull-up resistor value for your design, refer to the UM10204 I<sup>2</sup>C bus specification and user manual (the latest revision is available at www.nxp.com).

One of the SCB (typically SCB1) blocks is used to implement the Host Processor Interface (HPI) slave, which allows an external MCU to control the firmware operation.

The HPI I<sup>2</sup>C slave address is configurable using the I2C\_CFG\_EC pin for ACG1F 40-QFN as shown in Table 2. The default address for ACG1F 24-QFN will be 0x66.

Table 2. I<sup>2</sup>C Slave Address Configuration

| I2C_CFG_EC Configuration | I <sup>2</sup> C Slave |

|--------------------------|------------------------|

| Floating                 | 0x60                   |

| Pulled up with 1 kΩ      | 0x64                   |

| Pulled down with 1 kΩ    | 0x62                   |

### Timer/Counter/PWM Block (TCPWM)

The timer block of ACG1F supports one timer or counter or pulse-width modulator. The timer is available for internal timer use by firmware or for providing PWM-based functions on the GPIOs.

#### **GPIO**

The ACG1F die has eight GPIOs in 40-QFN and five GPIOs in 24-QFN including the I<sup>2</sup>C and SWD pins, which can also be used as GPIOs. The GPIO block shall implement the following:

- Eight drive strength modes including strong push-pull, resistive pull-up and pull-down, weak (resistive) pull-up and pull-down, open drain and open source, input only, and disabled.

- Input threshold select (CMOS or LVTTL)

- Individual control of input and output disables.

- Hold mode for latching previous state (used for retaining I/O state in Deep Sleep mode).

- Selectable slew rates for dV/dt related noise control.

During power-on and reset, the blocks are forced to the Disable state so as not to crowbar any inputs and/or cause excess turn-on current. A multiplexing network known as a high-speed I/O matrix is used to multiplex between various signals that may connect to an I/O pin. Pin locations for fixed-function peripherals, such as the USB Type-C port, are also fixed in order to reduce internal multiplexing complexity. Data Output Registers and Pin State Registers store, respectively, the values to be driven on the pins and the states of the pins themselves. The pins can be configured by programming of registers through software for each digital I/O Port.

Every I/O pin can generate an interrupt if so enabled and each I/O Port has an Interrupt Request (IRQ) and Interrupt Service Routine (ISR) Vector associated with it.

The I/O ports can retain their state during Deep Sleep mode or remain ON. If the operation is restored using reset, then the pins shall go the High-Z state. If operation is restored by an interrupt event, then the pin drivers shall retain their state until firmware chooses to change it. The I/Os (on data bus) do not draw current on power down.

# **Pinouts**

Table 3. 24-QFN Pin List

| Group Name                  | Pin Name | Port   | Pin         | Description                                                                       |

|-----------------------------|----------|--------|-------------|-----------------------------------------------------------------------------------|

| LICE Type C                 | CC1      | Analog | 24          | USB PD connector detect/Configuration Channel 1                                   |

| USB Type-C                  | CC2      | Analog | 22          | USB PD connector detect/Configuration Channel 2                                   |

| Mux                         | DPLUS    | Analog | 13          | USB 2.0 DP for BC1.2                                                              |

| iviux                       | DMINUS   | Analog | 12          | USB 2.0 DM for BC1.2                                                              |

| VBUS OCP                    | CSP      | Analog | 17          | Current Sense Positive Input for VBUS side external Rsense                        |

| VB03 OCP                    | CSN      | Analog | 18          | Current Sense Negative input for other side of external Rsense                    |

|                             |          | P0.0   | 19          | SWD Clock / SCB2 I <sup>2</sup> C Data / GPIO                                     |

|                             |          | P0.3   | 20          | GPIO                                                                              |

| GPIOs and Serial Interfaces |          | P0.4   | 21          | SWD Data / SCB2 I <sup>c</sup> C clock / GPIO                                     |

|                             |          | P1.1   | 2           | SCB1 I <sup>2</sup> C Data / GPIO                                                 |

|                             |          | P1.2   | 3           | SCB1 I <sup>2</sup> C clock / GPIO                                                |

| Reset                       | XRES     | Analog | 1           | Reset input                                                                       |

|                             | VBUS_C   | Power  | 7, 8, 9, 10 | Connector VBUS Output from Power NFET                                             |

|                             | VBUS_P   | Power  | 11          | Provider VBUS Input to Power NFET (Same as CSN at system Level)                   |

| Power                       | VDDD     | Power  | 15          | Supply for the System                                                             |

|                             | VCCD     | Power  | 16          | 1.8-V regulator output for filter capacitor. This pin cannot drive external load. |

|                             | V5V      | Power  | 23          | Supply for VCONN FET of Type-C                                                    |

| Ground                      | VSS      | Ground | 4, 5, 14    | Ground                                                                            |

| EPAD                        | VBUS_P   | Power  | -           | Provider VBUS Input to Power NFET (Same as CSN at system Level)                   |

Table 4. 40-QFN Pin List

| Group Name       | Pin Name | Port   | Pin        | Description                                                                       |

|------------------|----------|--------|------------|-----------------------------------------------------------------------------------|

| LICD Type C      | CC1      | Analog | 9          | USB PD connector detect/Configuration Channel 1                                   |

| USB Type-C       | CC2      | Analog | 7          | USB PD connector detect/Configuration Channel 2                                   |

| Mux              | DPLUS    | Analog | 28         | USB 2.0 DP for BC1.2                                                              |

| IVIUX            | DMINUS   | Analog | 27         | USB 2.0 DM for BC1.2                                                              |

| VBUS OCP         | CSP      | Analog | 1          | Current Sense Positive Input for VBUS side external Rsense                        |

| VBUS OCP         | CSN      | Analog | 40         | Current Sense Negative input for other side of external Rsense                    |

|                  |          | P0.0   | 2          | SWD Clock / GPIO                                                                  |

|                  |          | P0.1   | 3          | SCB2 I <sup>2</sup> C Data / GPIO                                                 |

|                  |          | P0.2   | 4          | SCB2 I <sup>2</sup> C Clock / GPIO                                                |

| GPIOs and Serial |          | P0.3   | 5          | GPIO                                                                              |

| Interfaces       |          | P0.4   | 6          | SWD Data / GPIO                                                                   |

|                  |          | P1.0   | 15         | Embedded Controller interrupt / GPIO                                              |

|                  |          | P1.1   | 16         | SCB1 I <sup>2</sup> C Data / GPIO                                                 |

|                  |          | P1.2   | 17         | SCB1 I <sup>2</sup> C Clock / GPIO                                                |

| Reset            | XRES     | Analog | 10         | Reset input                                                                       |

|                  | VBUS_C   | Power  | 21, 22, 23 | Connector VBUS Output from Power NFET                                             |

| -                | VBUS_P   | Power  | 24, 25, 26 | Provider VBUS Input to Power NFET (Same as CSN at system Level)                   |

| Power            | VDDD     | Power  | 31         | Supply for the System                                                             |

| Power            | VDDIO    | Power  | 32         | At system-level short the VDDD to VDDIO                                           |

|                  | VCCD     | Power  | 33         | 1.8-V regulator output for filter capacitor. This pin cannot drive external load. |

|                  | V5V      | Power  | 8          | Supply for VCONN FET of Type-C                                                    |

| EPAD             | VSS      | Ground | _          | Ground                                                                            |

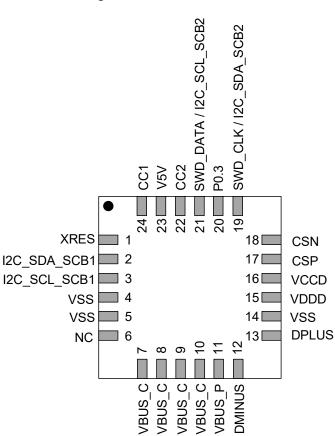

Figure 3. 24-Pin QFN Pinout

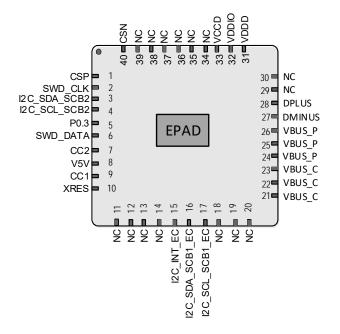

Figure 4. 40-Pin QFN Pinout

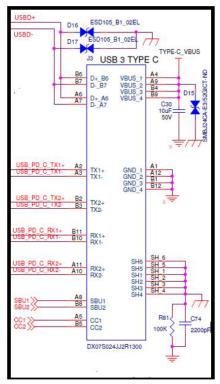

## **Application Diagrams**

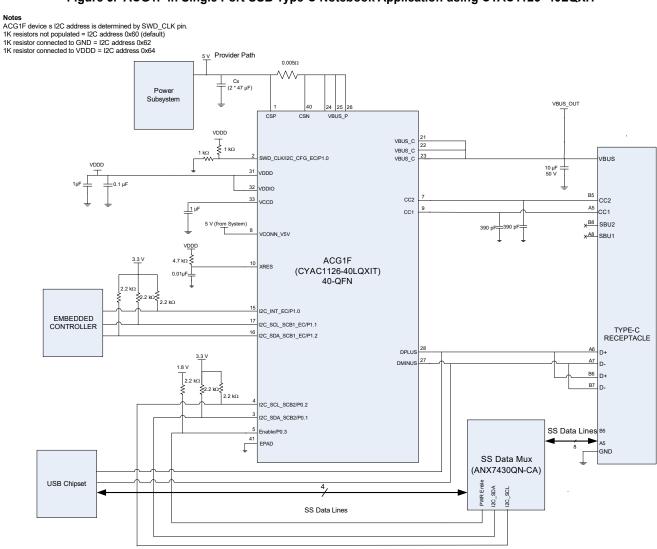

Figure 5 illustrates a Type-C port DFP application diagram using ACG1F. The Type-C port can be used as a Type-A to Type-C converter. The ACG1F device communicates with the embedded controller (EC) over  $I^2C$  bus, which manages the ACG1F operation. It also updates external analog mux Controller via  $I^2C$  to route the SuperSpeed signals coming from the Type-C port to the USB host. The ACG1F device supports battery charger detection (BC 1.2) through USB 2.0 DPLUS and DMINUS lines of the Type-C receptacle which is connected to the controller and to the DPLUS and DMINUS lines of the USB Host controller. ACG1F offers VBUS Short protection on CC lines. The ACG1F device has integrated VCONN FETs for applications that need to provide power for accessories and cables using the VCONN pin of the Type-C receptacle. The integrated VBUS load switch is used for providing power over VBUS. The 5-m $\Omega$  resistor between the 5-V supply and provider FETs is used for overcurrent detection on the VBUS.

Figure 5 illustrates Single Port Type-C port DFP application diagram using CYAC1126-40LQXIT.

Figure 5. ACG1F in Single Port USB Type-C Notebook Application using CYAC1126- 40LQXIT

Follow recommendations from manufacturer for AMUX connections

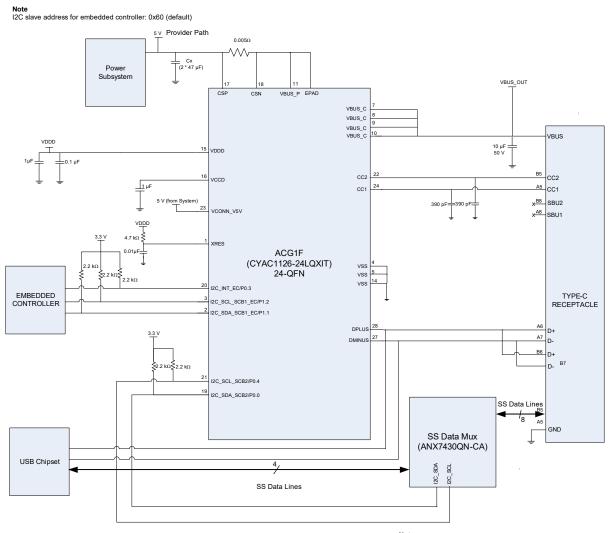

Figure 6 illustrates single port Type-C port DFP application diagram using CYAC1126-24LQXIT.

Figure 6. ACG1F in Single Port USB Type-C Notebook Application using CYAC1126- 24LQXIT

Note

Follow recommendations from manufacturer for AMUX connections.

# **Device Configuration Parameters**

ACG1F supports the following configuration parameters, which can be modified using EZ-PD configuration utility.

**Table 5. ACG1F Device Configuration Parameters**

|                 | Options                    | Description                                                                                                |

|-----------------|----------------------------|------------------------------------------------------------------------------------------------------------|

| Rp_Supported    |                            | Bitmap of Rp Supported by ACG1F                                                                            |

|                 | Rp for default USB Current | Enable or disable                                                                                          |

|                 | Rp for 1.5A USB Current    | Enable or disable                                                                                          |

|                 | Rp for 3.0A USB Current    | Enable or disable                                                                                          |

| VConn_Enable    |                            | Vconn Enable Parameters                                                                                    |

|                 | Enable options             | Yes – Turn ON VConn only if Ra termination is seen. No – Turn ON VConn even if Ra termination is not seen. |

| VBUS_OVP        | V                          | /BUS Over Voltage Protection Parameters                                                                    |

|                 | Enable                     | Can be enabled or disabled                                                                                 |

|                 | Threshold                  | Voltage threshold percentage above the contract voltage to trigger the fault.                              |

|                 | Debounce                   | Fault event debounce period in µs [0 – 255]                                                                |

|                 | Retry Count                | Number of times to retry recovery from fault [0 – 255].                                                    |

| VBUS_OCP        | •                          | VBUS Over Current Protection Parameters                                                                    |

|                 | Enable                     | Can be enabled or disabled                                                                                 |

|                 | Threshold                  | Current threshold percentage above the contract current to trigger the fault.                              |

|                 | Debounce                   | Fault event debounce period in µs [0 – 255]                                                                |

|                 | Retry Count                | Number of times to retry recovery from fault [0 – 255].                                                    |

| VBUS_SCP        |                            | VBUS Short Circuit Protection Parameters                                                                   |

|                 | Enable                     | Can be enabled or disabled                                                                                 |

|                 | Threshold                  | Threshold is fixed to 6A.                                                                                  |

|                 | Debounce                   | Fault event debounce period in μs [0 – 255]                                                                |

|                 | Retry Count                | Number of times to retry recovery from fault [0 – 255].                                                    |

| VBUS_RCP        | •                          | VBUS Reverse Current Protection Parameters                                                                 |

|                 | Enable                     | Can be enabled or disabled                                                                                 |

|                 | Retry Count                | Number of times to retry recovery from fault [0 – 255].                                                    |

| Vconn_OCP       | V                          | /conn Over Current Protection Parameters                                                                   |

|                 | Enable                     | Can be enabled or disabled                                                                                 |

|                 | Debounce                   | Fault event debounce period in μs [0 – 255]                                                                |

| VBUS_OTP        | •                          | VBUS Over Temperature Protection Parameters                                                                |

|                 | Enable                     | Can be enabled or disabled                                                                                 |

|                 | Therm_type                 | CCGx internal bipolar junction transistor (BJT)                                                            |

|                 | Cutoff_val                 | Reading/temperature at which device operation should be cut-off. Expressed in °C for internal BJT.         |

|                 | Restart_val                | Reading/temperature at which normal operation should be resumed.                                           |

| Battery Chargin | g I                        | Battery Charging Source Mode of Operation                                                                  |

|                 | BC 1.2 Enable              | Can be enabled or disabled                                                                                 |

# **Electrical Specifications**

# **Absolute Maximum Ratings**

# **Table 6. Absolute Maximum Ratings**

| Parameter                          | Description                                                                                                              | Min  | Тур | Max                     | Unit | Details/Conditions                                                                                |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------|-----|-------------------------|------|---------------------------------------------------------------------------------------------------|

| V <sub>5V_MAX</sub>                | Max supply voltage relative to V <sub>SS</sub>                                                                           | _    | _   | 6                       | V    | –40 °C to +85 °C T <sub>A</sub> ,<br>Absolute maximum                                             |

| V <sub>DDD_MAX</sub>               | Max supply voltage relative to V <sub>SS</sub>                                                                           | _    | _   | 6                       | V    | –40 °C to +85 °C T <sub>A</sub> ,<br>Absolute maximum                                             |

| V <sub>BUS_P_MAX</sub>             | Max Provider V <sub>BUS</sub> in the system                                                                              | _    | _   | 6                       | V    | –40 °C to +85 °C T <sub>A</sub>                                                                   |

| V <sub>BUS_C_MAX</sub>             | Max Connector side VBUS in the system with 40-QFN package                                                                | _    | -   | 24                      | V    | -40 °C to +85 °C T <sub>A</sub> peaks up to 30 V for duration less than 1 μs at room temperature. |

| V <sub>BUS_C_MAX</sub><br>(24-QFN) | Max Connector side VBUS in the system with 24-QFN package                                                                | _    | _   | 6                       | V    | –40 °C to +85 °C T <sub>A</sub>                                                                   |

| V <sub>DDIO_MAX</sub>              | Max supply voltage relative to V <sub>SS</sub>                                                                           | _    | _   | $V_{DDD}$               | V    | -                                                                                                 |

| V <sub>GPIO_ABS</sub>              | Inputs to GPIO                                                                                                           | -0.5 | _   | V <sub>DDIO</sub> + 0.5 | V    | _                                                                                                 |

| V <sub>DP-DM_abs</sub>             | Inputs to DPLUS and DMINUS                                                                                               | -0.5 | _   | V <sub>DDD</sub> + 0.5  | V    | _                                                                                                 |

| I <sub>GPIO_ABS</sub>              | Maximum current per GPIO                                                                                                 | -25  | _   | 25                      | mA   | _                                                                                                 |

| I <sub>GPIO_INJECTION</sub>        | GPIO injection current,<br>Max for V <sub>IH</sub> > V <sub>DDD</sub> , and<br>Min for V <sub>IL</sub> < V <sub>SS</sub> | -0.5 | _   | 0.5                     | mA   | Absolute max, current injected per pin                                                            |

| ESD_HBM_VBUS                       | Electrostatic discharge human body model for VBUS_C, VBUS_P pins                                                         | 500  | _   | _                       | V    | Only applicable to VBUS_C, VBUS_P pins                                                            |

| ESD_CDM                            | Electrostatic discharge charged device model                                                                             | 500  | -   | -                       | V    | Charged Device Model ESD                                                                          |

| ESD_HBM                            | Electrostatic discharge human body model                                                                                 | 2200 | -   | -                       | V    | Applicable for all pins except CC1, CC2, VBUS_C, and VBUS_P pins                                  |

| ESD_HBM_CC                         | Electrostatic discharge human body model for CC1, CC2 pins                                                               | 1100 | _   | -                       | V    | Only applicable to CC1, CC2 pins                                                                  |

| LU                                 | Pin current for latch-up                                                                                                 | -200 | _   | 200                     | mA   | -                                                                                                 |

| V <sub>CC_PIN_ABS</sub>            | Max voltage on CC1 and CC2 pins                                                                                          | _    | _   | 6                       | V    | _                                                                                                 |

## **Device-Level Specifications**

All specifications are valid for –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C and T<sub>J</sub>  $\leq$  100 °C, except where noted. Specifications are valid for 3.0 V to 5.5 V except where noted.

Table 7. DC Specifications

| Spec ID        | Parameter                   | Description                                                                      | Min       | Тур   | Max                    | Unit | Details/Conditions                                                                                                                     |

|----------------|-----------------------------|----------------------------------------------------------------------------------|-----------|-------|------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------|

| SID.PWR#1      | $V_{DDD}$                   | Power supply input voltage                                                       | 2.7       | 1     | 5.5                    | V    | –40 °C to +85 °C T <sub>A</sub>                                                                                                        |

| SID.PWR#2      | V <sub>BUS_P</sub>          | Provider V <sub>BUS</sub> from the system                                        | 4.0       | _     | 5.5                    | V    | –40 °C to +85 °C T <sub>A</sub>                                                                                                        |

| SID.PWR#2B     | V <sub>BUS_C</sub>          | Connector VBUS from the system                                                   | 1         | -     | V <sub>BUS_P</sub>     | V    | –40 °C to +85 °C T <sub>A</sub>                                                                                                        |

| SID.PWR#26     | V5V                         | Power supply for V <sub>CONN</sub>                                               | 4.85      | _     | 5.5                    | V    | –40 °C to +85 °C T <sub>A</sub>                                                                                                        |

| SID.PWR24      | V <sub>CCD</sub>            | Output voltage for core Logic                                                    | ı         | 1.8   | _                      | V    | _                                                                                                                                      |

| SID.PWR#4      | I <sub>DD</sub>             | Supply current                                                                   | 1         | 10    | _                      | mA   | T <sub>A</sub> = 25 °C, no I/O sourcing current, CPU at 16 MHz                                                                         |

| SID.PWR#7      | V <sub>DDWRITE</sub>        | Supply voltage for flash write                                                   | 2.7       | _     | 5.5                    | V    | –40 °C to +85 °C T <sub>A</sub> ,<br>All V <sub>DDD</sub> .                                                                            |

| SID.PWR#13     | $V_{DDIO}$                  | Supply voltage for I/O                                                           | $V_{DDD}$ | ı     | V <sub>DDD</sub>       | V    | $-40~^{\circ}\text{C}$ to +85 $^{\circ}\text{C}$ T <sub>A</sub> , All V <sub>DDD</sub>                                                 |

| SID.PWR#15     | C <sub>EFC</sub>            | External Regulator voltage bypass for V <sub>CCD</sub>                           | 80        | 100   | 120.0                  | nF   | X5R ceramic or better                                                                                                                  |

| SID.PWR#16     | C <sub>EXC</sub>            | Power supply decoupling capacitor for V <sub>DDD</sub>                           | 1         | 1     | -                      | μF   | X5R ceramic or better                                                                                                                  |

| SID.PWR#27     | C <sub>EXV</sub>            | Power supply decoupling capacitor for V5V, V <sub>DDIO</sub>                     | -         | 0.1   | -                      | μF   | X5R ceramic or better                                                                                                                  |

| SID.PWR#18     | V <sub>GPIO_ABS</sub>       | Inputs to GPIO                                                                   | -0.5      | _     | V <sub>DDIO</sub> +0.5 | V    | Absolute Maximum                                                                                                                       |

| SID.PWR#18A    | V <sub>DP-DM_ABS</sub>      | Inputs to DPLUS and DMINUS                                                       | -0.5      | _     | V <sub>DDD</sub> +0.5  | V    | Absolute Maximum                                                                                                                       |

| SID.PWR#19     | I <sub>GPIO_ABS</sub>       | Current per GPIO                                                                 | -25.0     | _     | 25                     | mA   | Absolute Maximum                                                                                                                       |

| SID.PWR#19A    | I <sub>GPIO_INJECTION</sub> | GPIO injection current, Max for $V_{IH} > V_{DDD}$ and min for $V_{IL} < V_{SS}$ | -0.5      | _     | 0.5                    | mA   | Absolute Maximum current injection per pin                                                                                             |

| SID.PWR#21     | T <sub>DEEPSLEEP</sub>      | Wakeup from Deep Sleep Mode                                                      | -         | 35    | -                      | μs   | -                                                                                                                                      |

| SID.PWR#50     | V <sub>CC_PIN_ABS</sub>     | Max voltage on CC1 & CC2 pins                                                    | ı         |       | 6                      | V    | Absolute Maximum                                                                                                                       |

| Current Consur | nption for ACG1F            | in Deep Sleep Mode. Typical valu                                                 | es mea    | sured | at 25 °C.              |      |                                                                                                                                        |

| SID_DS1        | I <sub>DD_DS1</sub>         | V <sub>DDD</sub> = 3.3 V. CC wakeup on,<br>Type-C not connected                  | _         | 150   | -                      | μΑ   | Power source = V <sub>DDD</sub> ,<br>Type-C Not attached, CC<br>enabled for wakeup. Rp<br>connection should be<br>enabled for PD port. |

| SID_DS3        | I <sub>DD_DS2</sub>         | V <sub>DDD</sub> = 3.3 V. CC wakeup on, with CSA/UVOV On                         | 1         | 500   | -                      | μΑ   | I <sub>DD_DS1</sub> + CC ON,<br>CSA/UVOV ON                                                                                            |

| SID34          | I <sub>DD29</sub>           | $V_{DDD}$ = 2.7 to 3.6 V. I <sup>2</sup> C Wakeup and WDT on.                    | I         | 150   | _                      | μΑ   | V <sub>DDD</sub> = 3.3 V, T <sub>A</sub> = 25 °C                                                                                       |

| SID307         | I <sub>DD_XR</sub>          | Supply current while XRES asserted                                               | _         | 50    | -                      | μΑ   | Power Source = V <sub>DDD</sub> = 3.3 V, Type-C not attached, T <sub>A</sub> = 25 °C                                                   |

CPU

Table 8. CPU Specifications (Guaranteed by Characterization)

| Spec ID    | Parameter              | Description                                               | Min | Тур | Max | Unit | Details/Conditions   |

|------------|------------------------|-----------------------------------------------------------|-----|-----|-----|------|----------------------|

| SID.CLK#4  | F <sub>CPU</sub>       | CPU input frequency                                       | _   | _   | 16  | MHz  | All V <sub>DDD</sub> |

| SID.PWR#21 | T <sub>DEEPSLEEP</sub> | Wakeup from Deep Sleep mode                               | _   | 35  | _   | μs   | Guaranteed by        |

| SYS.XRES#5 | T <sub>XRES</sub>      | External reset pulse width                                | 5   | _   | ı   | μs   | characterization     |

| SYS.FES#1  | T_ <sub>PWR_RDY</sub>  | Power-up to "Ready to accept I <sup>2</sup> C/CC command" | _   | 5   | 25  | ms   |                      |

**GPIO**

Table 9. GPIO DC Specifications

| Spec ID     | Parameter                  | Description                               | Min                         | Тур | Max                        | Unit | Details/Conditions                                                                                      |

|-------------|----------------------------|-------------------------------------------|-----------------------------|-----|----------------------------|------|---------------------------------------------------------------------------------------------------------|

| SID.GIO#37  | V <sub>IH_CMOS</sub>       | Input voltage HIGH threshold              | 0.7 ×<br>V <sub>DDIO</sub>  | _   | _                          | V    | CMOS input                                                                                              |

| SID.GIO#38  | V <sub>IL_CMOS</sub>       | Input voltage LOW threshold               | _                           | _   | 0.3 ×<br>V <sub>DDIO</sub> | ٧    | CMOS input                                                                                              |

| SID.GIO#39  | V <sub>IH_VDDIO2.7</sub> - | LVTTL input, V <sub>DDIO</sub> < 2.7 V    | 0.7 ×<br>V <sub>DDIO</sub>  | _   | _                          | V    | _                                                                                                       |

| SID.GIO#40  | V <sub>IL_VDDIO2.7</sub> - | LVTTL input, V <sub>DDIO</sub> < 2.7 V    | _                           | _   | 0.3 ×<br>V <sub>DDIO</sub> | ٧    | _                                                                                                       |

| SID.GIO#41  | V <sub>IH_VDDIO2.7+</sub>  | LVTTL input, $V_{DDIO} \ge 2.7 \text{ V}$ | 2.0                         | _   | _                          | V    | _                                                                                                       |

| SID.GIO#42  | V <sub>IL_VDDIO2.7+</sub>  | LVTTL input, $V_{DDIO} \ge 2.7 \text{ V}$ | _                           | _   | 0.8                        | V    | _                                                                                                       |

| SID.GIO#33  | V <sub>OH</sub>            | Output voltage HIGH level                 | V <sub>DDIO</sub> – 0.6     | _   | -                          | V    | $I_{OH} = -4 \text{ mA at } 3\text{-V V}_{DDIO}$                                                        |

| SID.GIO#34  | V <sub>OH</sub>            | Output voltage HIGH level                 | V <sub>DDIO</sub> – 0.5     | _   | -                          | V    | $I_{OH} = -1$ mA at 1.8-V $V_{DDIO}$                                                                    |

| SID.GIO#35  | V <sub>OL</sub>            | Output voltage LOW level                  | _                           | _   | 0.6                        | V    | $I_{OL}$ = 4 mA at 1.8-V $V_{DDIO}$                                                                     |

| SID.GIO#35A | V <sub>OL_I2C_2</sub>      | Output low voltage                        | _                           | _   | 0.4                        | V    | $I_{OL}$ = 3 mA, $V_{DDIO}$ > 2 V                                                                       |

| SID.GIO#35B | V <sub>OL_I2C_3</sub>      | Output low voltage                        | _                           | _   | 0.6 <sup>[3]</sup>         | V    | I <sub>OL</sub> = 6 mA, V <sub>DDIO</sub> > 1.71 V                                                      |

| SID.GIO#35C | V <sub>OL1_20mA</sub>      | Output low voltage                        | _                           | _   | 0.4                        | V    | I <sub>OL</sub> = 20 mA, V <sub>DDIO</sub> > 3.0 V,<br>Applicable for<br>overvoltage-tolerant pins only |

| SID.GIO#36  | V <sub>OL</sub>            | Output voltage LOW level                  | _                           | _   | 0.6                        | V    | I <sub>OL</sub> = 10 mA (IOL_LED) at 3-V<br>V <sub>DDIO</sub>                                           |

| SID.GIO#5   | Rpu                        | Pull-up resistor when enabled             | 3.5                         | 5.6 | 8.5                        | kΩ   | +25 °C T <sub>A</sub> , All V <sub>DDIO</sub>                                                           |

| SID.GIO#6   | Rpd                        | Pull-down resistor when enabled           | 3.5                         | 5.6 | 8.5                        | kΩ   | +25 °C T <sub>A</sub> , All V <sub>DDIO</sub>                                                           |

| SID.GIO#16  | I <sub>IL</sub>            | Input leakage current (absolute value)    | _                           | _   | 2                          | nA   | +25 °C T <sub>A</sub> , 3-V V <sub>DDIO</sub>                                                           |

| SID.GIO#17  | C <sub>PIN</sub>           | Max pin capacitance                       | _                           | 3   | 7                          | pF   | _                                                                                                       |

| SID.GIO#43  | V <sub>HYSTTL</sub>        | Input hysteresis, LVTTL                   | 15                          | 40  | _                          | mV   | V <sub>DDIO</sub> > 2.7 V. Guaranteed by characterization.                                              |

| SID.GIO#44  | V <sub>HYSCMOS</sub>       | Input hysteresis CMOS                     | 0.05 ×<br>V <sub>DDIO</sub> | _   | -                          | mV   | V <sub>DDIO</sub> < 4.5 V                                                                               |

| SID.GIO#44A | V <sub>HYSCMOS55</sub>     | Input hysteresis CMOS                     | 200                         | _   | _                          | mV   | V <sub>DDIO</sub> > 4.5 V                                                                               |

#### Note

Document Number: 002-26356 Rev. \*D

<sup>3.</sup> To drive full bus load at 400 kHz, 6-mA I<sub>OL</sub> is required at 0.6-V V<sub>OL</sub>. Parts not meeting this specification can still function, but not at 400 kHz and 400 pF.

Table 10. GPIO AC Specifications (Guaranteed by Characterization)

| Spec ID    | Parameter              | Description                                                                  | Min | Тур | Max | Unit | Details/Conditions                                   |

|------------|------------------------|------------------------------------------------------------------------------|-----|-----|-----|------|------------------------------------------------------|

| SID70      | T <sub>RISEF</sub>     | Rise time in Fast Strong mode                                                | 2   | _   | 12  | ns   | 3.3-V V <sub>DDIO</sub> , C <sub>load</sub> = 25 pF  |

| SID71      | T <sub>FALLF</sub>     | Fall time in Fast Strong mode                                                | 2   | _   | 12  | ns   | 3.3-V V <sub>DDIO</sub> , C <sub>load</sub> = 25 pF  |

| SID.GIO#46 | T <sub>RISES</sub>     | Rise time in Slow Strong mode                                                | 10  | _   | 60  | ns   | 3.3-V V <sub>DDIO</sub> , C <sub>load</sub> = 25 pF  |

| SID.GIO#47 | T <sub>FALLS</sub>     | Fall time in Slow Strong mode                                                | 10  | ı   | 60  | ns   | $3.3\text{-V V}_{DDIO}$ , $C_{load} = 25 \text{ pF}$ |

| SID.GIO#48 | F <sub>GPIO_OUT1</sub> | GPIO $F_{OUT}$ ; 3.3 $V \le V_{DDIO} \le 5.5 V$ . Fast Strong mode.          | -   | -   | 16  | MHz  | 90/10%, 25-pF load                                   |

| SID.GIO#49 | F <sub>GPIO_OUT2</sub> | GPIO $F_{OUT}$ ; 1.7 $V \le V_{DDIO} \le 3.3 \text{ V.}$ Fast Strong mode.   | -   | 1   | 16  | MHz  | 90/10%, 25-pF load                                   |

| SID.GIO#50 | F <sub>GPIO_OUT3</sub> | GPIO $F_{OUT}$ ; 3.3 $V \le V_{DDIO} \le 5.5 V$ . Slow Strong mode.          | -   | -   | 7   | MHz  | 90/10%, 25-pF load                                   |

| SID.GIO#51 | F <sub>GPIO_OUT4</sub> | GPIO $F_{OUT}$ ; 1.7 $V \le V_{DDIO} \le 3.3 V$ . Slow Strong mode.          | -   | -   | 3.5 | MHz  | 90/10%, 25-pF load                                   |

| SID.GIO#52 | F <sub>GPIO_IN</sub>   | GPIO input operating frequency; 1.7 V $\leq$ V <sub>DDIO</sub> $\leq$ 5.5 V. | -   | -   | 16  | MHz  | 90/10% V <sub>IO</sub>                               |

## XRES

# Table 11. XRES DC Specifications

| Spec ID    | Parameter            | Description                  | Min                        | Тур                         | Max                        | Unit | Details/Conditions             |

|------------|----------------------|------------------------------|----------------------------|-----------------------------|----------------------------|------|--------------------------------|

| SID.XRES#1 | V <sub>IH</sub>      | Input voltage HIGH threshold | 0.7 ×<br>V <sub>DDIO</sub> | 1                           | -                          | ٧    | CMOS input                     |

| SID.XRES#2 | V <sub>IL</sub>      | Input voltage LOW threshold  | -                          | 1                           | 0.3 ×<br>V <sub>DDIO</sub> | ٧    | CMOS input                     |

| SID.XRES#3 | C <sub>IN</sub>      | Input capacitance            | _                          | -                           | 7                          | pF   | _                              |

| SID.XRES#4 | V <sub>HYSXRES</sub> | Input voltage hysteresis     | _                          | 0.05 ×<br>V <sub>DDIO</sub> | Ι                          | mV   | Guaranteed by characterization |

## **Digital Peripherals**

The following specifications apply to the Timer/Counter/PWM peripherals in the Timer mode.

Pulse Width Modulation (PWM) for GPIO Pins

Table 12. PWM AC Specifications (Guaranteed by Characterization)

| Spec ID      | Parameter             | Description                  | Min  | Тур | Max | Unit | Details/Conditions                                                                                    |

|--------------|-----------------------|------------------------------|------|-----|-----|------|-------------------------------------------------------------------------------------------------------|

| SID.TCPWM.3  | T <sub>CPWMFREQ</sub> | Operating frequency          | 1    | -   | Fc  |      | Fc max = CLK_SYS.<br>Maximum = 16 MHz.                                                                |

| SID.TCPWM.4  | T <sub>PWMENEXT</sub> | Input trigger pulse width    | 2/Fc | _   | -   | ns   | For all trigger events                                                                                |

| SID.TCPWM.5  | T <sub>PWMEXT</sub>   | Output trigger pulse width   | 2/Fc | -   | -   | ns   | Minimum possible width of<br>Overflow, Underflow, and CC<br>(Counter equals Compare value)<br>outputs |

| SID.TCPWM.5A | T <sub>CRES</sub>     | Resolution of counter        | 1/Fc | _   | _   | ns   | Minimum time between successive counts                                                                |

| SID.TCPWM.5B | PWM <sub>RES</sub>    | PWM resolution               | 1/Fc | -   | -   | ns   | Minimum pulse width of PWM output                                                                     |

| SID.TCPWM.5C | Q <sub>RES</sub>      | Quadrature inputs resolution | 1/Fc | _   | -   | ns   | Minimum pulse width between quadrature-phase inputs                                                   |

РC

# Table 13. Fixed I<sup>2</sup>C AC Specifications

(Guaranteed by Characterization)

| Spec ID | Parameter         | Description | Min | Тур | Max | Unit | Details/Conditions |

|---------|-------------------|-------------|-----|-----|-----|------|--------------------|

| SID153  | F <sub>I2C1</sub> | Bit rate    | _   | ı   | 1   | Mbps | -                  |

#### Memory

## Table 14. Flash AC Specifications

| Spec ID   | Parameter               | Description                                                 | Min  | Тур | Max | Unit   | Details/Conditions                   |

|-----------|-------------------------|-------------------------------------------------------------|------|-----|-----|--------|--------------------------------------|

| SID.MEM#4 | T <sub>ROW_WRITE</sub>  | Row (Block) write time (erase and program)                  | -    | -   | 20  | ms     | _                                    |

| SID.MEM#3 | T <sub>ROW_ERASE</sub>  | Row erase time                                              | _    | ı   | 13  | ms     | _                                    |

| SID.MEM#8 | T <sub>ROWPROGRAM</sub> | Row program time after erase                                | ı    | ı   | 7   | ms     | 25 °C to 55 °C, All V <sub>DDD</sub> |

| SID178    | T <sub>BULKERASE</sub>  | Bulk erase time (128 KB)                                    | ı    | ı   | 35  | ms     | Guaranteed by design                 |

| SID180    | T <sub>DEVPROG</sub>    | Total device program time                                   | ı    | ı   | 25  | s      | Guaranteed by design                 |

| SID.MEM#6 | F <sub>END</sub>        | Flash endurance                                             | 100k | ı   | ı   | cycles | _                                    |

| SID182    | F <sub>RET1</sub>       | Flash retention, T <sub>A</sub> ≤ 55 °C,<br>100K P/E cycles | 20   | ı   | -   | years  | _                                    |

| SID182A   | F <sub>RET2</sub>       | Flash retention, T <sub>A</sub> ≤ 85 °C,<br>10K P/E cycles  | 10   | _   | -   | years  | _                                    |

| SID182B   | F <sub>RET3</sub>       | Flash retention, T <sub>A</sub> ≤ 105 °C,<br>10K P/E cycles | 3    | -   | _   | years  | _                                    |

# **System Resources**

Power-on-Reset (POR) with Brown Out

## Table 15. Imprecise Power On Reset (IPOR)

| Spec ID | Parameter             | Description          | Min  | Тур | Max  | Unit | Details/Conditions             |

|---------|-----------------------|----------------------|------|-----|------|------|--------------------------------|

| SID185  | V <sub>RISEIPOR</sub> | Rising trip voltage  | 0.80 | -   | 1.50 |      | Guaranteed by characterization |

| SID186  | V <sub>FALLIPOR</sub> | Falling trip voltage | 0.70 | -   | 1.4  | V    | Guaranteed by characterization |

## Table 16. Precise Power-on Reset (POR)

| Spec ID | Parameter              | Description                                               | Min  | Тур | Max  | Unit | Details/Conditions             |

|---------|------------------------|-----------------------------------------------------------|------|-----|------|------|--------------------------------|

| SID190  |                        | Brown-out Detect (BOD) trip voltage in active/sleep modes | 1.48 | -   | 1.62 | V    | Guaranteed by characterization |

| SID192  | V <sub>FALLDPSLP</sub> | BOD trip voltage in Deep Sleep mode                       | 1.1  | _   | 1.5  | V    | Guaranteed by characterization |

#### SWD Interface

## Table 17. SWD Interface Specifications

| Spec ID   | Parameter    | Description                                             | Min      | Тур | Max      | Unit | Details/Conditions               |

|-----------|--------------|---------------------------------------------------------|----------|-----|----------|------|----------------------------------|

| SID.SWD#1 | F_SWDCLK1    | $3.3~V \leq V_{DDIO} \leq 5.5~V$                        | _        | -   | 5        |      | SWDCLK ≤ 1/3 CPU clock frequency |

| SID.SWD#2 | F_SWDCLK2    | $1.8 \text{ V} \leq \text{V}_{DDIO} \leq 3.3 \text{ V}$ | _        | -   | 5        | MHz  | SWDCLK ≤ 1/3 CPU clock frequency |

| SID.SWD#3 | T_SWDI_SETUP | T = 1/f SWDCLK                                          | 0.25 × T | -   | _        | ns   | Guaranteed by characterization   |

| SID.SWD#4 | T_SWDI_HOLD  | T = 1/f SWDCLK                                          | 0.25 × T | -   | _        | ns   | Guaranteed by characterization   |

| SID.SWD#5 | T_SWDO_VALID | T = 1/f SWDCLK                                          | _        | -   | 0.50 × T | ns   | Guaranteed by characterization   |

| SID.SWD#6 | T_SWDO_HOLD  | T = 1/f SWDCLK                                          | 1        | -   | _        | ns   | Guaranteed by characterization   |

Internal Main Oscillator

## Table 18. IMO AC Specifications

(Guaranteed by Design)

| Spec ID    | Parameter             | Description                             | Min | Тур | Max | Unit | Details/Conditions                                                    |

|------------|-----------------------|-----------------------------------------|-----|-----|-----|------|-----------------------------------------------------------------------|

| SID.CLK#13 | F <sub>IMOTOL</sub>   | Frequency variation at 48 MHz (trimmed) | -   | -   | ±2  |      | 2.7 V ≤ V <sub>DDD</sub> < 5.5 V. –<br>25 °C ≤ T <sub>A</sub> ≤ 85 °C |

| SID226     | T <sub>STARTIMO</sub> | IMO start-up time                       | _   | _   | 7   | μs   | _                                                                     |

| SID.CLK#1  | F <sub>IMO</sub>      | IMO frequency                           | -   | 48  | -   | MHz  | _                                                                     |

# Internal Low-speed Oscillator

# Table 19. ILO AC Specifications

| Spec ID   | Parameter              | Description                   | Min | Тур | Max | Unit | Details/Conditions |

|-----------|------------------------|-------------------------------|-----|-----|-----|------|--------------------|

| SID234    | T <sub>STARTILO1</sub> | I <sub>LO</sub> start-up time | _   | _   | 2   | ms   | Guaranteed by      |

| SID238    | T <sub>ILODUTY</sub>   | I <sub>LO</sub> duty cycle    | 40  | 50  | 60  | %    | characterization   |

| SID.CLK#5 | F <sub>ILO</sub>       | I <sub>LO</sub> frequency     | 20  | 40  | 80  | kHz  | _                  |

## PD

## Table 20. PD DC Specifications

| Spec ID            | Parameter       | Description                                   | Min   | Тур | Max   | Unit | Details/Conditions |

|--------------------|-----------------|-----------------------------------------------|-------|-----|-------|------|--------------------|

| SID.DC.acg1f.cc.5  | Idac_std        | Source current for USB standard advertisement | 64    | _   | 96    | μΑ   | _                  |

| SID.DC.acg1f.cc.6  | ldac_1p5a       | Source current for 1.5A @ 5-V advertisement   | 165.6 | _   | 194.4 | μΑ   | _                  |

| SID.DC.acg1f.cc.7  | Idac_3a         | Source current for 3A @ 5-V advertisement     | 303.6 | _   | 356.4 | μΑ   | _                  |

| SID.DC.acg1f.cc.10 | zOPEN           | CC impedance to ground when disabled          | 108   | -   |       | kΩ   | _                  |

| SID.DC.acg1f.cc.11 | DFP_default_0p2 | CC Voltages on DFP side-Standard USB          | 0.15  | _   | 0.25  | V    | _                  |

| SID.DC.acg1f.cc.12 | DFP_1.5A_0p4    | CC Voltages on DFP side-1.5A                  | 0.35  | -   | 0.45  | V    | _                  |

| SID.DC.acg1f.cc.13 | DFP_3A_0p8      | CC Voltages on DFP side-3A                    | 0.75  | -   | 0.85  | V    | _                  |

| SID.DC.acg1f.cc.14 | DFP_3A_2p6      | CC Voltages on DFP side-3A                    | 2.45  | -   | 2.75  | V    | _                  |

| SID.DC.acg1f.cc.17 | Vattach_ds      | Deep sleep attach threshold                   | 0.3   | ı   | 0.6   | %    | _                  |

| SID.DC.acg1f.cc.18 | Rattach_ds      | Deep sleep pull-up resistor                   | 10    | _   | 50    | kΩ   | _                  |

# Analog-to-Digital Converter

# Table 21. ADC DC Specifications

| Spec ID   | Parameter  | Description                | Min          | Тур | Max          | Unit | Details/Conditions                                             |

|-----------|------------|----------------------------|--------------|-----|--------------|------|----------------------------------------------------------------|

| SID.ADC.1 | Resolution | ADC resolution             | -            | 8   | _            | Bits | _                                                              |

| SID.ADC.2 | INL        | Integral non-linearity     | -1.5         | _   | 1.5          | LSB  | _                                                              |

| SID.ADC.3 | DNL        | Differential non-linearity | -2.5         | _   | 2.5          | LSB  | _                                                              |

| SID.ADC.4 | Gain Error | Gain error                 | -1.5         | _   | 1.5          | LSB  | _                                                              |

| SID.ADC.5 | VREF_ADC1  | Reference voltage of ADC   | $V_{DDDmin}$ | _   | $V_{DDDmax}$ | V    | Reference voltage<br>generated from<br>V <sub>DDD</sub>        |

| SID.ADC.6 | VREF_ADC2  | Reference voltage of ADC   | 1.96         | 2.0 | 2.04         | V    | Reference voltage<br>generated from<br>Deep Sleep<br>reference |

# Charger Detect

Table 22. Charger Detect DC Specifications

| Spec ID          | Parameter | Description                                         | Min   | Тур | Max   | Unit | Details/Conditions |

|------------------|-----------|-----------------------------------------------------|-------|-----|-------|------|--------------------|

| DC.CHGDET.1      | VDAT_REF  | Data detect voltage in charger detect mode          | 250   | -   | 400   | mV   | _                  |

| DC.CHGDET.2      | VDM_SRC   | Dn voltage source in charger detect mode            | 500   | -   | 700   | mV   | _                  |

| DC.CHGDET.3      | VDP_SRC   | Dp voltage source in charger detect mode            | 500   | -   | 700   | mV   | _                  |

| DC.CHGDET.4      | IDM_SINK  | Dn sink current in charger detect mode              | 25    | -   | 175   | μA   | _                  |

| DC.CHGDET.5      | IDP_SINK  | Dp sink current in charger detect mode              | 25    | -   | 175   | μA   | _                  |

| DC.CHGDET.6      | IDP_SRC   | Data contact detect current source                  | 7     | _   | 13    | μA   | _                  |

| DC.CHGDET.32     | RDM_UP    | Dp/Dn pull-up resistance                            | 0.9   | _   | 1.575 | kΩ   | _                  |

| DC.CHGDET.31     | RDM_DWN   | Dp/Dn pull-down resistance                          | 14.25 | _   | 24.8  | kΩ   | _                  |

| DC.CHGDET.29     | RDAT_LKG  | Data line leakage on Dp/Dn                          | 300   | _   | 500   | kΩ   | _                  |

| DC.CHGDET.34     | VSETH     | Logic Threshold                                     | 1.26  | _   | 1.54  | V    | _                  |

| DC.acg1f.dpdm.14 | RDCP_DAT  | Dedicated charging port resistance across DP and DN | _     | -   | 40    | Ω    |                    |

## CSA

# Table 23. CSA DC Specifications

| Spec ID       | Parameter                | Description                                                                             | Min | Тур                                                                    | Max | Unit                                                                         | Details/Conditions                                                                     |

|---------------|--------------------------|-----------------------------------------------------------------------------------------|-----|------------------------------------------------------------------------|-----|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| DC.csa_scp.42 | SCP_6A                   | Short circuit current detect @ 6A                                                       | _   | ±10                                                                    | _   | %                                                                            | _                                                                                      |

| DC.csa_scp.43 | SCP_10A                  | Short circuit current detect @10A                                                       | -   | ±10                                                                    | -   | %                                                                            | _                                                                                      |

| OP.csa_scp.11 | Rsense                   | External sense register                                                                 | -   | 5                                                                      | -   | mΩ                                                                           | 1% accuracy                                                                            |

| DC cca ccn 44 | locp_1A                  |                                                                                         | %   | 1A PD contracts OCP set at 130% of contract value or user programmable |     |                                                                              |                                                                                        |

| ВС.сsа_scp.44 | locp_1A                  | OCP Trip threshold for 1A with Rsense = $10 \text{ m}\Omega$ - $\frac{130}{\pm 10\%}$ - |     | _                                                                      | %   | 1A PD contracts OCP set<br>at 130% of contract value<br>or user programmable |                                                                                        |

| DC.csa_scp.45 | locp_5A                  | OCP Trip threshold for 2A, 3A, 4A and 5A contracts with Rsense = $5/10 \text{ m}\Omega$ | ı   | 130<br>±10%                                                            | -   | %                                                                            | 2A, 3A, 4A, and 5A PD contracts OCP set at 130% of contract value OR user programmable |

| DC.rcp_scp.7a | I_csainn_lk              | CSP pin input leakage when RCP and CSA blocks are OFF                                   | _   | _                                                                      | 10  | μΑ                                                                           | For provider V <sub>BUS</sub> = 5 V                                                    |

| DC.rcp_scp.6a | I_csainp_lk              | CSN pin input leakage when RCP and CSA blocks are OFF                                   | _   | -                                                                      | 80  | μΑ                                                                           | For provider V <sub>BUS</sub> = 5 V                                                    |

| DC.sys.1      | I_CSP_RCP_ON<br>_CSA_OFF | CSP pin current when RCP block is ON and SCP is OFF                                     | _   | _                                                                      | 20  | μΑ                                                                           | For provider V <sub>BUS</sub> = 5 V                                                    |

| DC.sys.2      | I_CSN_RCP_ON<br>_CSA_OFF | CSN pin current when RCP block is ON and SCP is OFF                                     | _   | -                                                                      | 100 | μA                                                                           | For provider V <sub>BUS</sub> = 5 V                                                    |

| DC.sys.3      | I_CSP_CSA_ON             | CSP pin current when RCP block is OFF and SCP is ON                                     | _   | _                                                                      | 30  | μΑ                                                                           | For provider V <sub>BUS</sub> = 5 V                                                    |

| DC.sys.4      | I_CSN_CSA_ON             | CSN pin current when RCP block is OFF and SCP is ON                                     | ı   | _                                                                      | 100 | μA                                                                           | For provider V <sub>BUS</sub> = 5 V                                                    |

## Table 23. CSA DC Specifications (continued)

| Spec ID  | Parameter | Description                                        | Min | Тур | Max | Unit | Details/Conditions                                            |

|----------|-----------|----------------------------------------------------|-----|-----|-----|------|---------------------------------------------------------------|

| DC.sys.5 |           | CSP pin current when RCP block is ON and SCP is ON | -   | _   | 50  |      | For provider V <sub>BUS</sub> = 5 V.<br>Guaranteed by design. |

| DC.sys.6 |           | CSN pin current when RCP block is ON and SCP is ON | _   | _   | 120 |      | For provider V <sub>BUS</sub> = 5 V.<br>Guaranteed by design. |

V<sub>BUS</sub> UV/OV

# Table 24. $V_{BUS}$ UV/OV Specifications

| Spec ID      | Parameter            | Description                                                              | Description Min Typ |    |    | Unit | Details/Conditions |

|--------------|----------------------|--------------------------------------------------------------------------|---------------------|----|----|------|--------------------|

| SID.UVOV.1   | V <sub>THUVOV1</sub> | Voltage threshold accuracy in active mode using bandgap reference        | -                   | ±3 | -  | %    | _                  |

| SID.UVOV.2   | V <sub>THUVOV2</sub> | Voltage threshold accuracy in deep sleep mode using deep sleep reference | _                   | ±5 | _  | %    | -                  |

| SID.COMP_ACC | COMP_ACC             | Comparator input offset at 4s                                            | -15                 | _  | 15 | mV   | _                  |

VCONN Switch

## Table 25. VCONN Switch DC Specifications

| Spec ID             | Parameter        | Description                                                                                                                                                | Min                                                                 | Тур | Max  | Unit | Details/Conditions   |

|---------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-----|------|------|----------------------|

| DC.acg1f.20VCONN.1  | Ron              | Switch ON resistance at $-$ 1.4 2 $\Omega$ V5V = 5 V with 215-mA load current                                                                              |                                                                     |     |      |      | _                    |

| DC.acg1f.20VCONN.9  | I <sub>OCP</sub> | Overcurrent detection range for CC1/CC2                                                                                                                    | 550                                                                 | _   | -    | mA   | _                    |

| DC.acg1f.20VCONN.10 | OVP_threshold    | CC1, CC2 overvoltage protection detection threshold above V <sub>DDD</sub> or V5V, whichever is higher                                                     | otection detection threshold ove V <sub>DDD</sub> or V5V, whichever |     | 1200 | mV   | -                    |