# DATASHEET

### PORTBLE CONSUMER DEVICE

LOWER-POWER, HIGH-FIDELITY, CLASS-D AMPLIFIER

ACS32201

The ACS32201 is a low-power, high-fidelity Class-D amplifier targeted at portable applications such as tablet computers, personal navigation devices, portable projectors and speaker docks. Built-in audio processing and a DDX<sup>TM</sup> Class-D digital speaker amplifier provide high fidelity audio for portable systems with enriched "audio presence".

#### TARGET APPLICATIONS

- Tablet Computers

- Portable Navigation Devices

- Personal Media Players

- Portable Projectors

- Speaker Docks

#### **FEATURES**

Filterless Stereo DDX<sup>TM</sup> Class D Speaker Driver

- Tri-state DDX<sup>TM</sup> Class D achieves low EMI and high efficiency

- >80% efficiency at 1W

- Spread spectrum support for reduced EMI output power mode

- Anti-Pop circuitry

#### Built in audio controls and processing

- 3D stereo enhancement

- Dual (cascaded) stereo 6-band parametric equalizers

- Programmable Compressor/Limiter/Expander

- Psychoacoustic Bass and Treble enhancement processing

- I2S data interface

- Low power with built in power management

- Very low standby and no-signal power consumption

- 1.8V digital / 1.7V analog supply for low power

- 2-wire (I<sup>2</sup>C compatible) control interface

- Package Options

- 36-pin single row 5x5 mm HLA package

- 68-pin dual row 6x6 mm TLA package

# TABLE OF CONTENTS

| 1. (       | OVERVIEW                                                             | 7  |

|------------|----------------------------------------------------------------------|----|

|            | 1.1. Block Diagrams                                                  | 7  |

|            | 1.2. Audio Outputs                                                   | 7  |

| 2. I       | POWER MANAGEMENT                                                     | 8  |

|            | 2.1. Control Registers                                               | 8  |

|            | 2.2. Stopping the Master Clock                                       |    |

| 3. (       | DUTPUT AUDIO PROCESSING                                              |    |

|            | 3.1. DC Removal                                                      |    |

|            | 3.2. Volume Control                                                  |    |

|            | 3.3. Digital DAC Volume Control                                      |    |

|            | 3.4. Parametric Equalizer                                            |    |

|            | 3.4.1. Prescaler & Equalizer Filter                                  |    |

|            | 3.4.2. EQ Registers                                                  |    |

|            | 3.4.3. Equalizer, Bass, Treble Coefficient & Equalizer Prescaler RAM |    |

|            | 3.5. Gain and Dynamic Range Control                                  |    |

|            | 3.6. Limiter                                                         |    |

|            | 3.7. Compressor                                                      | 18 |

|            | 3.7.1. Configuration                                                 | 19 |

|            | 3.7.2. Controlling parameters                                        | 19 |

|            | 3.7.3. Overview                                                      | 20 |

|            | 3.7.4. Limiter/Compressor Registers                                  | 22 |

|            | 3.7.5. Expander Registers                                            | 24 |

|            | 3.8. Output Effects                                                  | 25 |

|            | 3.9. Stereo Depth (3-D) Enhancement                                  | 25 |

|            | 3.10. Psychoacoustic Bass Enhancement                                | 26 |

|            | 3.11. Psychoacoustic Treble Enhancement                              |    |

|            | 3.12. Mute and De-Emphasis                                           |    |

|            | 3.13. Mono Operation and Phase Inversion                             |    |

|            | 3.13.1. DAC Control Register                                         |    |

|            | 3.14. Analog Outputs                                                 |    |

|            | 3.14.1. Speaker Outputs                                              | 27 |

|            | 3.14.2. Class D Audio Processing                                     |    |

|            | 3.15. Other Output Capabilities                                      |    |

|            | 3.15.1. Audio Output Control                                         |    |

|            | 3.15.2. Speaker Enable                                               |    |

|            | 3.15.3. Speaker Operation                                            |    |

|            | 3.16. Thermal Shutdown                                               |    |

|            | 3.16.1. Algorithm description:                                       |    |

|            | 3.16.2. Thermal Trip Points                                          |    |

|            | 3.16.4. Short Circuit Protection                                     |    |

|            | 3.16.5. Thermal Shutdown Registers                                   |    |

| <i>1</i> I | DIGITAL AUDIO AND CONTROL INTERFACES                                 |    |

| 4. 1       | 4.1. Data Interface                                                  |    |

|            | 4.2. Master and Slave Mode Operation                                 |    |

|            | 4.3. Audio Data Formats                                              |    |

|            | 4.4. Left Justified Audio Interface                                  |    |

|            | 4.5. Right Justified Audio Interface (assuming n-bit word length)    |    |

|            | 4.6. I2S Format Audio Interface (assuming 11-bit word length)        |    |

|            | 4.7. Data Interface Registers                                        |    |

|            | 4.7.1. Audio Data Format Control Register                            |    |

|            | 4.7.2. Audio Data romat Control Register                             |    |

|            | 4.7.3. Audio Interface Control 3 Register                            |    |

|            | 4.8. Bit Clock Mode                                                  |    |

|            | 4.9. Control Interface                                               |    |

|            | 4.9.1. Register Write Cycle                                          |    |

|            | ·                                                                    | 43 |

# ACS32201

# LOWER-POWER, HIGH-FIDELITY, CLASS-D AMPLIFIER

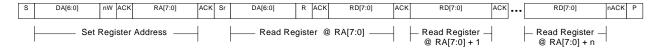

| 4.9.3. Register Read Cycle                                        | 43 |

|-------------------------------------------------------------------|----|

| 4.9.4. Multiple Read Cycle                                        | 43 |

| 4.9.5. Device Addressing and Identification                       |    |

| 5. AUDIO CLOCK GENERATION                                         | 45 |

| 5.1. Internal Clock Generation (ACLK)                             | 45 |

| 5.1.1. External MCLK                                              | 45 |

| 5.2. ACLK Clocking and Sample Rates                               | 45 |

| 6. CHARACTERISTICS                                                | 47 |

| 6.1. Electrical Specifications                                    | 47 |

| 6.1.1. Absolute Maximum Ratings                                   | 47 |

| 6.1.2. Recommended Operating Conditions                           |    |

| 6.2. Device Characteristics                                       | 48 |

| 6.3. PLL Electrical Characteristics                               |    |

| 7. REGISTER MAP                                                   | 50 |

| 8. PIN INFORMATION                                                | 52 |

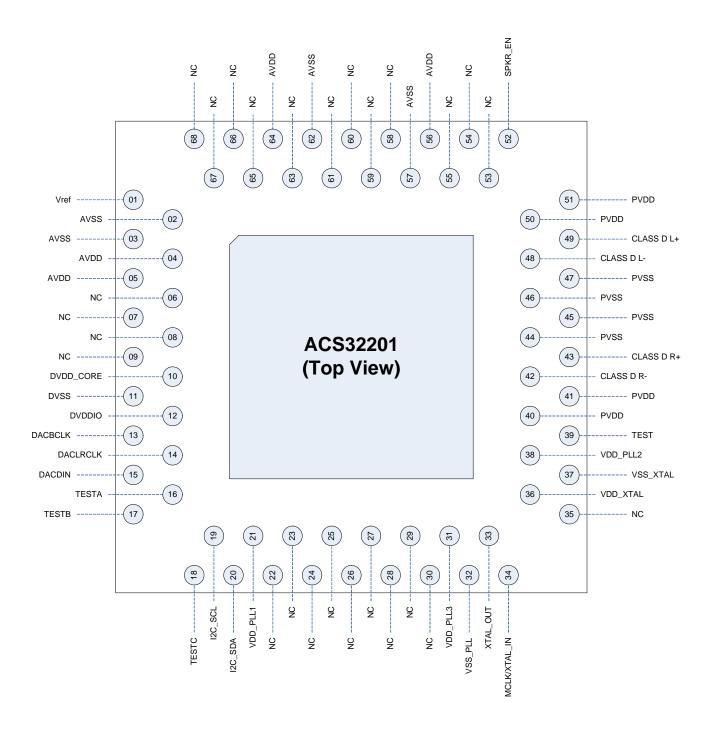

| 8.1. ACS32201 TAG/TLA Pin Diagram                                 | 52 |

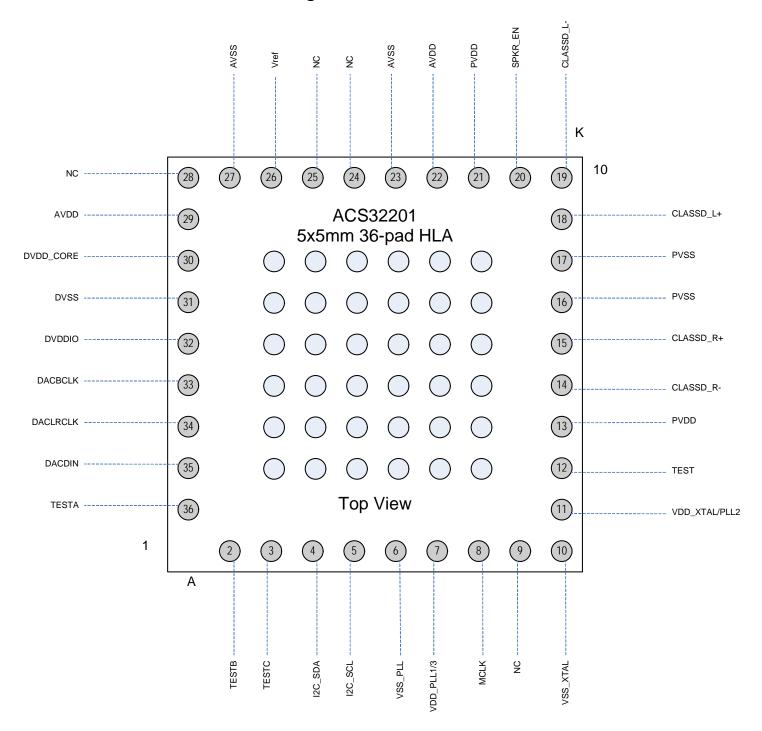

| 8.2. ACS32201 NAG/HLA Pin Diagram                                 |    |

| 8.3. ACS32201 TAG Pin Tables                                      | 54 |

| 8.3.1. ACS32201 TAG Power Pins                                    |    |

| 8.3.2. ACS32201 TAG Reference Pins                                |    |

| 8.3.3. ACS32201 TAG Analog Output Pins                            |    |

| 8.3.4. ACS32201 TAG Data and Control Pins                         |    |

| 8.3.5. ACS32201 TAG Clock Pins                                    |    |

| 8.4. ACS32201 NAG Pin Tables                                      |    |

| 8.4.1. ACS32201 NAG Power Pins                                    |    |

| 8.4.2. ACS32201 NAG Reference Pins                                |    |

| 8.4.3. ACS32201 NAG Analog Output Pins                            |    |

| 8.4.4. ACS32201 NAG Data and Control Pins                         |    |

| 8.4.5. ACS32201 NAG Clock Pins                                    |    |

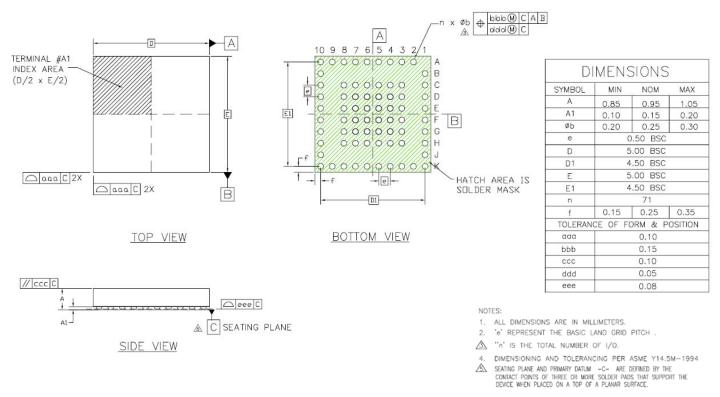

| 9. PACKAGE INFORMATION                                            |    |

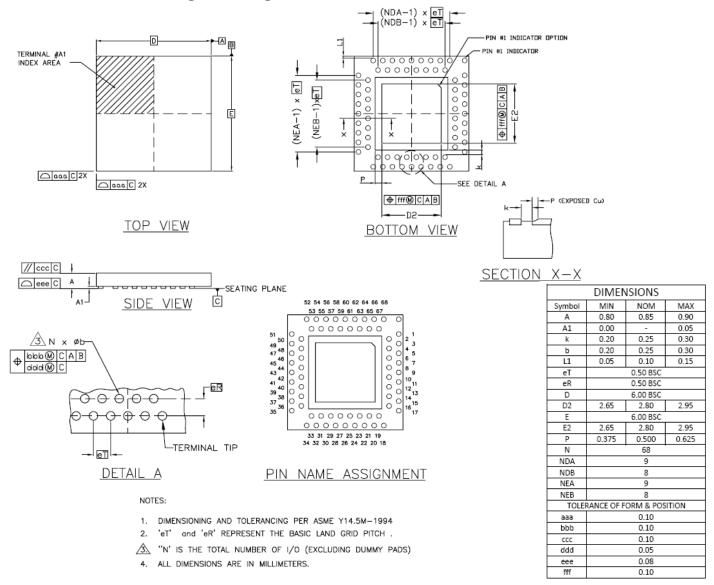

| 9.1. TAG/TLA Package Drawing                                      |    |

| 9.2. Pb Free Process- Package Classification Reflow Temperatures  |    |

| 10. NAG/HLA PACKAGE INFORMATION                                   |    |

| 10.1. NAG/HLA Package Drawing                                     |    |

| 10.2. Pb Free Process- Package Classification Reflow Temperatures |    |

| 11. ORDERING INFORMATION                                          |    |

| 12. DISCLAIMER                                                    | 60 |

| 13 DOCUMENT REVISION HISTORY                                      | 61 |

#### LIST OF TABLES

Power Management Register 1 8

Power Management Register 2 8

Power Management Register1 -- Master Clock Disable 8

DC\_COEF\_SEL Register 9

CONFIG0 Register 9

Volume Update Control Register 10

Gain Control Register 10

**DAC Volume Control Registers 11**

CONFIG1 Register 12

DACCRAM Read/Write Registers 13

**DACCRAM Address Register 13**

DACCRAM Status Register 13

DACCRAM EQ Addresess 16

DACCRAM Bass/Treble Addresses 17

**CLECTL Register 22**

MUGAIN Register 22

**COMPTH Register 22**

CMPRAT Register 22

CATKTCL Register 22

**CATKTCH Register 23**

**CRELTCL Register 23**

**CRELTCH Register 23**

LIMTH Register 23

LIMTGT Register 23

LATKTCL Register 23

LATKTCH Register 23

LRELTCL Register 23

LRELTCH Register 24

**EXPTH Register 24**

EXPRAT Register 24

XATKTCL Register 24

XATKTCH Register 24

XRELTCL Register 24

XRELTCH Register 24

FX Control Register 25 CNVRTR1 Register 26

SPKVOL L/R Registers 27

Constant Output Power 1 Register 30

Constant Output Power 2 Register 31

Constant Output Power 3 Register 31

CONFIG0 Register 31

PWM0 Register 32

PWM1 Register 32

PWM2 Register 32

PWM3 Register 32

Power Management 2 Register 33

Additional Control Register 34

Speaker Operation 34

Additional Control Register 36

THERMTS Register 36

THERMTSPKR1 Register 37

THERMTSPKR2 Register 37

AIC1 Register 40

AIC2 Register 41

AIC3 Register 41

Master Mode BCLK Frequency Control Register 41

**DEVADRI** Register 44

DEVID H&L Registers 44

#### ACS32201

### LOWER-POWER, HIGH-FIDELITY, CLASS-D AMPLIFIER

**REVID Register 44**

**RESET Register 44**

DACSR Register 45

ACLK and Sample Rates 46

Electrical Specification: Maximum Ratings 47

**Recommended Operating Conditions 47**

**Device Characteristics 48**

PLL Section DC Characteristics 49

Register Map 50

ACS32201 TAG Power Pins 54

ACS32201 TAG Reference Pins 54

ACS32201 TAG Analog Output Pins 54

ACS32201 TAG Data and Control Pins 55

ACS32201 TAG Clock Pins 55

ACS32201 NAG Power Pins 56

ACS32201 NAG Reference Pins 56

ACS32201 NAG Analog Output Pins 56

ACS32201 NAG Data and Control Pins 57

ACS32201 NAG Clock Pins 57

**Reflow Temperatures 58**

**Reflow Temperatures 59**

#### **LIST OF FIGURES**

ACS32201 Block Diagram 7

Output Audio Processing 9

Prescaler & EQ Filters 11

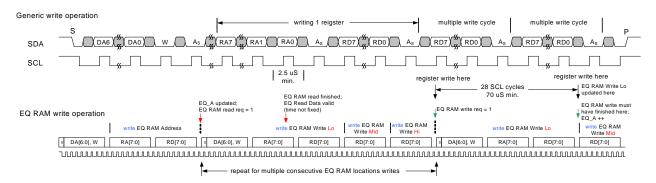

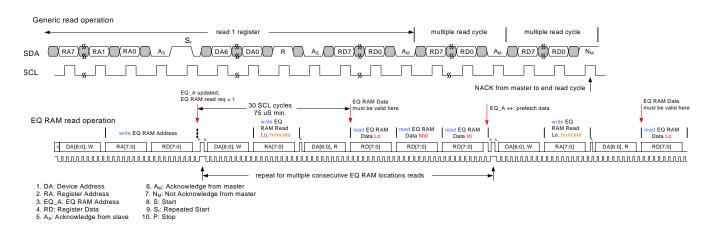

DAC Coefficient RAM Write Sequence 14

DAC Coefficient RAM Read Sequence 15

Gain Compressor, Output vs Input 18

Compressor block diagram 20

3-D Channel Inversion 25

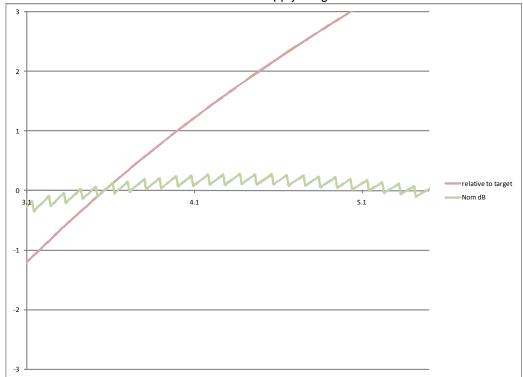

Constant Output Power Error 29

Constant Output Power nominal and high/low 30

35

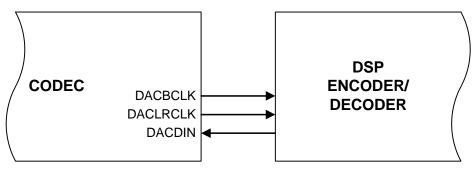

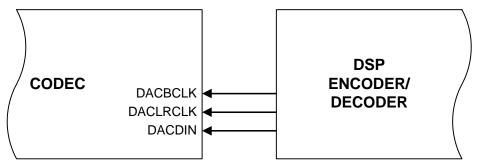

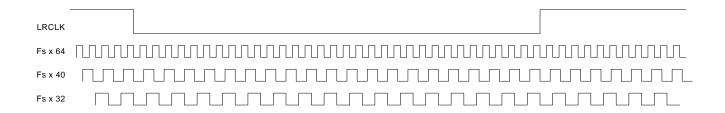

Master mode 38

Slave mode 38

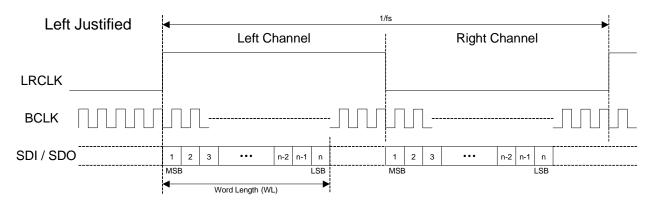

Left Justified Audio Interface (assuming n-bit word length) 39

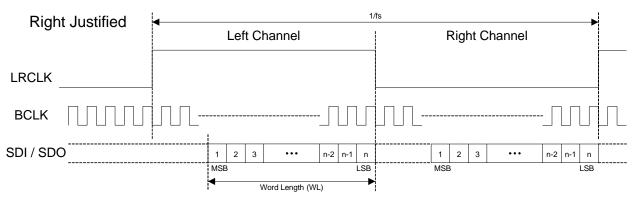

Right Justified Audio Interface (assuming n-bit word length) 39

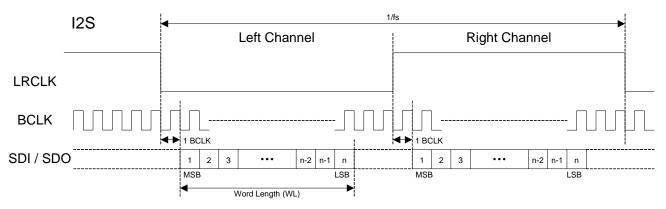

12S Justified Audio Interface (assuming n-bit word length) 40

Bit Clock mode 42

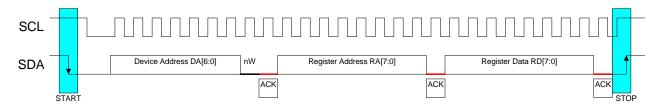

2-Wire Serial Control Interface 42

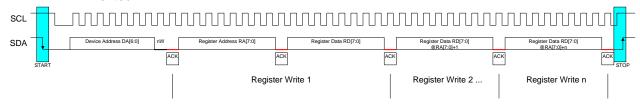

Multiple Write Cycle 43

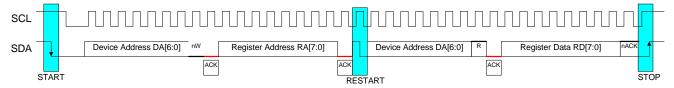

Read Cycle 43

Multiple Read Cycle 44

ACS32201 TLA/TAG Pinout 52

ACS32201 NAG/HLA Pinout 53

Package Outline 58

NAG/HLA Package Outline 59

V 1.7 4/18

6

#### 1. OVERVIEW

### 1.1. Block Diagrams

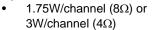

The ACS32201 is an advanced digital Class-D amplifier. To support the design of audio subsystems in a portable device, the ACS32201 features an intelligent architecture with advanced audio processing algorithms and a 1.75W/channel filterless stereo class D amplifier.

Figure 1. ACS32201 Block Diagram

### 1.2. Audio Outputs

To enhance the sound available from the small, low-power speakers typically found in a portable device, the ACS32201 provides numerous audio enhancement capabilities. The ACS32201 features dual, independent, programmable left/right 6-band equalization, allowing the system designer to provide an advanced system equalizer to accommodate the specific speakers and enclosure design. A compressor/limiter features programmable attack and release thresholds, enabling the system designer to attenuate loud noise excursions to avoid speaker artifacts, thus allowing the underlying content to be played at a louder volume without distortion. For compressed audio, a programmable expander is available to help restore the dynamic range of the original content. A stereo depth enhancement algorithm allows common left/right content (e.g. dialog) to be attenuated separately from other content, providing a perceived depth separation between background and foreground audio. Psychoacoustic bass and treble enhancement algorithms achieve a rich, full tone even from originally compressed content, and even with speakers generally unable to play low-frequency sounds.

#### 1. POWER MANAGEMENT

# 1.1. Control Registers

The ACS32201 has control registers to enable system software to control which functions are active. To minimize power consumption, unused functions should be disabled. To avoid audio artifacts, it is important to enable or disable functions in the correct order.

| Register Address   | Bit | Label  | Type | Default | Description                                                            |

|--------------------|-----|--------|------|---------|------------------------------------------------------------------------|

| 0x1A               | 7:1 | RSVD   | RW   | 0       | Reserved                                                               |

| Power Management 1 | 0   | DIGENB | RW   | 0       | Master clock disable 0: master clock enabled, 1: master clock disabled |

**Table 1. Power Management Register 1**

| Register Address           | Bit | Label | Туре | Default | Description                                                           |

|----------------------------|-----|-------|------|---------|-----------------------------------------------------------------------|

|                            | 7:5 | RSVD  | RW   | 0       | Reserved                                                              |

|                            | 4   | SPKL  | RW   | 0       | LSPK Output Buffer<br>0 = Power down, 1 = Power up                    |

| 0x1B<br>Power Management 2 | 3   | SPKR  | RW   | 0       | RSPK Output Buffer<br>0 = Power down, 1 = Power up                    |

|                            | 2:1 | RSVD  | RW   | 0       | Reserved                                                              |

|                            | 0   | VREF  | RW   | 0       | VREF (necessary for all other functions) 0 = Power down, 1 = Power up |

Table 2. Power Management Register 2

### 1.2. Stopping the Master Clock

In order to minimize digital core power consumption, the master clock may be stopped in Standby and OFF modes by setting the DIGENB bit (R25, bit 0).

| Register Address           | Bit | Label  | Туре | Default | Description                                                              |

|----------------------------|-----|--------|------|---------|--------------------------------------------------------------------------|

| 0x1A<br>Power Management 1 | 0   | DIGENB | RW   | 0       | Master clock disable 0 = master clock enabled, 1 = master clock disabled |

Table 3. Power Management Register1 -- Master Clock Disable

8

Note: Before DIGENB can be set, the control bits SPKL and SPKR must be set to zero and a waiting time of 100ms must be observed to allow port ramping/gain fading to complete. Any failure to follow this procedure may cause pops or, if less than 1mS, may prevent the DACs from re-starting correctly.

#### 1. OUTPUT AUDIO PROCESSING

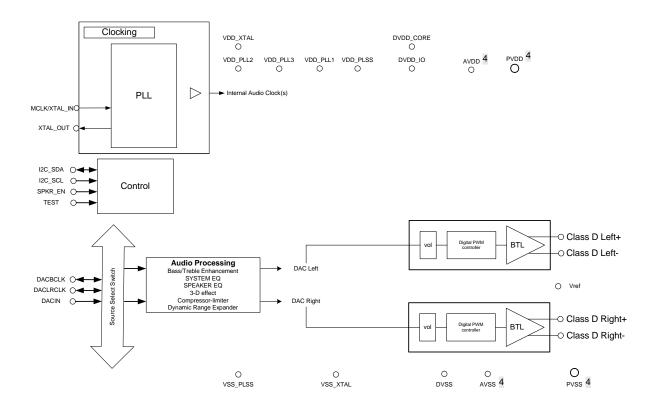

Figure 1. Output Audio Processing

#### 1.1. DC Removal

Before processing, a DC removal filter removes the DC component from the incoming audio data. The DC removal filter is programmable.

| Register Address     | Bit | Label | Type | Default | Description                                                                                                                                                                                                                                                              |

|----------------------|-----|-------|------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      | 7:3 | _     | R    | 0       | Reserved for future use.                                                                                                                                                                                                                                                 |

| R65 (41h)<br>DCOFSEL | 2:0 | -     | RW   | 5       | 0: dc_coef = 24'h100000; //2^-3 = 0.125<br>1: dc_coef = 24'h040000;<br>2: dc_coef = 24'h010000;<br>3: dc_coef = 24'h004000;<br>4: dc_coef = 24'h001000;<br>5: dc_coef = 24'h000400;<br>6: dc_coef = 24'h000100; //2^-15 = 0.00030517<br>7: dc_coef = 24'h000040; //2^-17 |

Table 1. DC\_COEF\_SEL Register

| Register Address     | Bit | Label     | Type | Default | Description                                                           |

|----------------------|-----|-----------|------|---------|-----------------------------------------------------------------------|

|                      | 7:2 | RSVD      | RW   | 10h     | Reserved                                                              |

| R31 (1Fh)<br>CONFIG0 | 1   | dc_bypass | RW   | 0       | 1 = bypass DC removal filter (WARNING DC content can damage speakers) |

|                      | 0   | RSVD      | R    | 0       | Reserved                                                              |

Table 2. CONFIG0 Register

9

#### 1.2. Volume Control

The signal volume can be controlled digitally, across a gain and attenuation range of -95.25dB to 0dB (0.375dB steps). The level of attenuation is specified by an eight-bit code, 'DACVOL\_x', where 'x' is L, or R. The value "00000000" indicates mute; other values select the number of 0.375dB steps above -95.625dB for the volume level.

The Volume Update bits control the updating of volume control data; when a bit is written as '0', the Left Volume control associated with that bit is updated whenever the left volume register is written and the Right Volume control is updated when ever the right volume register is written. When a bit is written as '1', the left volume data is placed into an internal holding register when the left volume register is written and both the left and right volumes are updated when the right volume register is written. This enables a simultaneous left and right volume update

| Register Address   | Bit | Label   | Type | Default | Description                                                                                                           |

|--------------------|-----|---------|------|---------|-----------------------------------------------------------------------------------------------------------------------|

|                    | 7   | RSVD    | RW   | 1       | Reserved                                                                                                              |

|                    | 6   | DACFade | RW   | 1       | 1 = volume fades between old/new value<br>0 = volume/mute changes immediately                                         |

|                    | 5:3 | RSVD    | R    | 0       | Reserved for future use.                                                                                              |

| R10 (0Ah)<br>VUCTL | 2   | DACVOLU | RW   | 0       | 0 = Left DAC volume updated immediately 1 = Left DAC volume held until right DAC volume register written.             |

|                    | 1   | SPKVOLU | RW   | 0       | 0 = Left speaker volume updated immediately 1 = Left speaker volume held until right speaker volume register written. |

|                    | 0   | RSVD    | RW   | 0       | Reserved                                                                                                              |

Table 3. Volume Update Control Register

The output path may be muted automatically when a long string of zero data is received. The length of zeros is programmable and a detection flag indicates when a stream of zero data has been detected.

| Register Address | Bit | Label        | Туре | Default | Description                                                                                         |

|------------------|-----|--------------|------|---------|-----------------------------------------------------------------------------------------------------|

|                  | 7   | zerodet_flag | R    | 0       | 1 = zero detect length exceeded.                                                                    |

|                  | 6   | RSVD         | R    | 0       | Reserved for future use.                                                                            |

| R33 (21h)        | 5:4 | zerodetlen   | RW   | 2       | Enable mute if input consecutive zeros exceeds this length. 0 = 512, 1 = 1k, 2 = 2k, 3 = 4k samples |

| Gain Control     | 3   | RSVD         | R    | 0       | Reserved for future use.                                                                            |

| (GAINCTL)        | 2   | auto_mute    | RW   | 1       | 1 = auto mute if detect long string of zeros on input                                               |

|                  | 1   | RSVD         | R    | 0       | Reserved for future use.                                                                            |

|                  | 0   | RSVD         | R    | 0       | Reserved for future use.                                                                            |

|                  | 7   | zerodet_flag | R    | 0       | 1 = zero detect length exceeded.                                                                    |

Table 4. Gain Control Register

### 1.3. Digital DAC Volume Control

The signal volume can be controlled digitally, across a gain and attenuation range of -95.25dB to 0dB (0.375dB steps). The level of attenuation is specified by an eight-bit code, 'DACVOL\_x', where 'x' is L, or R. The value "00000000" indicates mute; other values select the number of 0.375dB steps above -95.625dB for the volume level.

| Register Address                        | Bit | Label             | Type | Default     | Description                                                                                                                                                                                                                                   |

|-----------------------------------------|-----|-------------------|------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R4 (04h)<br>Left DAC<br>Volume Control  | 7:0 | DACVOL_L<br>[7:0] | RW   | FF<br>(0dB) | Left DAC Volume Level 0000 0000 = Digital Mute 0000 0001 = -95.25dB 0000 0010 = -94.875dB 0.375dB steps up to 1111 1111 = 0dB Note: If DACVOLU is set, this setting will take effect after the next write to the Right Input Volume register. |

| R5 (05h)<br>Right DAC<br>Volume Control | 7:0 | DACVOL_R<br>[7:0] | RW   | FF<br>(0dB) | Right DAC Digital Volume Level<br>0000 0000 = Digital Mute<br>0000 0001 = -95.25dB<br>0000 0010 = -94.875dB<br>0.375dB steps up to<br>1111 1111 = 0dB                                                                                         |

**Table 5. DAC Volume Control Registers**

### 1.4. Parametric Equalizer

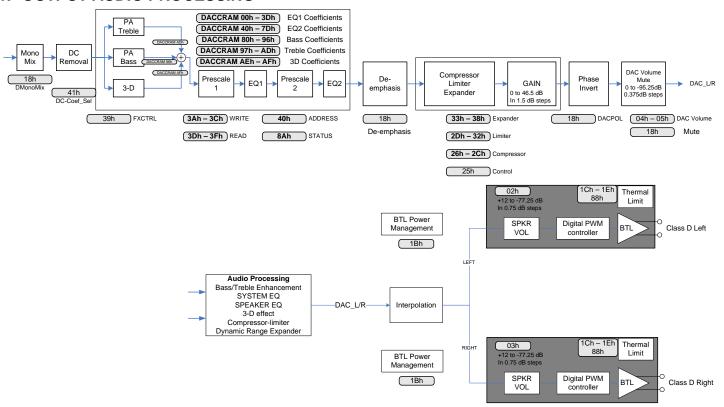

The ACS32201 has a dual 6-band digital parametric equalizer to enable fine tuning of the audio response and preferences for a given system. Each EQ may be enabled or disabled independently. Typically one EQ will be used for speaker compensation and disabled when only headphones are in use while the other EQ is used to alter the audio to make it more pleasing to the listener. This function operates on the digital audio data before it is converted back to analog by the audio DACs.

### 1.4.1. Prescaler & Equalizer Filter

The Equalizer Filter consists of a Prescaler and 6 IIR Filters. The Prescaler allows the input to be attenuated prior to the EQ filters in case the EQ filters introduce gain, and would thus clip if not prescaled.

TSI provides a tool to enable an audio designer to determine appropriate coefficients for the equalizer filters. The filters enable the implementation of a parametric equalizer with selectable frequency bands, gain, and filter characteristics (high, low, or bandpass).

Figure 2. Prescaler & EQ Filters

11

### 1.4.2. EQ Registers

# • EQ Filter Enable Register

| Register Address | Bit | Label       | Type | Default | Description                                                                                                                                                                       |

|------------------|-----|-------------|------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | 7   | EQ2_EN      | R/W  | 0       | EQ bank 2 enable<br>0 = second EQ bypassed, 1 = second EQ enabled                                                                                                                 |

| R32 (20h)        | 6:4 | EQ2_BE[2:0] | R/W  | 0       | EQ2 band enable. When the EQ is enabled the following EQ stages are executed.  0 - Prescale only 1 - Prescale and Filter Band 0 6 - Prescale and Filter Bands 0 to 5 7 - RESERVED |

| CONFIG1          | 3   | EQ1_EN      | R/W  | 0       | EQ bank 1 enable<br>0 = first EQ bypassed, 1 = first EQ enabled                                                                                                                   |

|                  | 2:0 | EQ1_BE[2:0] | R/W  | 0       | EQ1 band enable. When the EQ is enabled the following EQ stages are executed.  0 - Prescale only 1 - Prescale and Filter Band 0 6 - Prescale and Filter Bands 0 to 5 7 - RESERVED |

Table 6. CONFIG1 Register

12

# • DACCRAM Read Data (0x3D-LO, 0x3E-MID, 0x3F-HI), DACCRAM Write Data (0x3A-LO, 0x3B-MID, 0x3C-HI) Registers

These two 24-bit registers provide the 24-bit data holding registers used when doing indirect writes/reads to the DAC Coefficient RAM.

| Register Address               | Bit | Label          | Туре | Default | Description                                                                                                                                                                                 |

|--------------------------------|-----|----------------|------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R58 (3Ah)<br>DACCRAM_WRITE_LO  | 7:0 | DACCRWD[7:0]   | R/W  | 0       | Low byte of a 24-bit data register, contains the values to be written to the DACCRAM. The address written will have been specified by the DACCRAM Address fields.                           |

| R59 (3Bh)<br>DACCRAM_WRITE_MID | 7:0 | DACCRWD[15:8]  | R/W  | 0       | Middle byte of a 24-bit data register, contains the values to be written to the DACCRAM. The address written will have been specified by the DACCRAM Address fields.                        |

| R60 (3Ch)<br>DACCRAM_WRITE_HI  | 7:0 | DACCRWD[23:16] | R/W  | 0       | High byte of a 24-bit data register, contains the values to be written to the DACCRAM. The address written will have been specified by the DACCRAM Address fields.                          |

| R61 (3Dh)<br>DACCRAM_READ_LO   | 7:0 | DACCRRD[7:0]   | R    | 0       | Low byte of a 24-bit data register, contains the contents of the most recent DACCRAM address read from the RAM. The address read will have been specified by the DACCRAM Address fields.    |

| R62 (3Eh)<br>DACCRAM_READ_MID  | 7:0 | DACCRRD[15:8]  | R    | 0       | Middle byte of a 24-bit data register, contains the contents of the most recent DACCRAM address read from the RAM. The address read will have been specified by the DACCRAM Address fields. |

| R63 (3Fh)<br>DACCRAM_READ_HI   | 7:0 | DACCRRD[23:16] | R    | 0       | High byte of a 24-bit data register, contains the contents of the most recent DACCRAM address read from the RAM. The address read will have been specified by the DACCRAM Address fields.   |

Table 7. DACCRAM Read/Write Registers

#### DACCRAM Address Register

This 7-bit register provides the address to the internal RAM when doing indirect writes/reads to the DAC Coefficient RAM.

| Register Address       | Bit | Label    | Type | Default | Description                                                                                                                                                                                                                                                                                                                                                              |

|------------------------|-----|----------|------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R64 (40h)<br>DACCRADDR | 7:0 | DACCRADD | R/W  | 0       | Contains the address (between 0 and 255) of the DACCRAM to be accessed by a read or write. This is not a byte addressit is the address of the 24-bit data item to be accessed from the DACCRAM. This address is automatically incremented after writing to DACCRAM_WRITE_HI or reading from DACCRAM_READ_HI (and the 24 bit data from the next RAM location is fetched.) |

Table 8. DACCRAM Address Register

#### DACCRAM STATUS Register

This control register provides the write/read enable when doing indirect writes/reads to the DAC Coefficient RAM.

| Register Address        | Bit | Label        | Type | Default | Description                                                     |

|-------------------------|-----|--------------|------|---------|-----------------------------------------------------------------|

| R138 (8Ah)<br>DACCRSTAT | 7   | DACCRAM_Busy | R    | 0       | 1 = read/write to DACCRAM in progress, cleared by HW when done. |

| DAOOROTAT               | 6:0 | RSVD         | R    | 0       | Reserved                                                        |

Table 9. DACCRAM Status Register

13

### 1.4.3. Equalizer, Bass, Treble Coefficient & Equalizer Prescaler RAM

The DAC Coefficient RAM is a single port 161x24 synchronous RAM. It is programmed indirectly through the Control Bus in the following manner:

- Write target address to DACCRAM\_ADDR register.

- 2. Write D7:0 to the DACCRAM\_WRITE\_LO register

- 3. Write D15:8 to the DACCRAM WRITE MID register

- Write D23:16 to the DACCRAM\_WRITE\_HI register

- 5. On successful receipt of the DACCRAM\_WRITE\_HI data, the part will automatically start a write cycle. The DACCRAM\_Busy bit will be set high to indicate that a write is in progress.

- 6. On completion of the internal write cycle, the DACCRAM\_Busy bit will be 0 (when operating the control interface at high speeds TBD software must poll this bit to ensure the write cycle is complete before starting another write cycle.)

- 7. The bus cycle may be terminated by the host or steps 2-6 may be repeated for writes to consecutive EQ RAM locations.

Figure 3. DAC Coefficient RAM Write Sequence

Reading back a value from the DACCRAM is done in this manner:

- Write target address to DACCRAM\_ADDR register.(EQ data is pre-fetched for read even if we don't use it)

- 2. Start (or repeat start) a write cycle to DACCRAM\_READ\_LO and after the second byte (register address) is acknowledged, go to step 3. (Do not complete the write cycle.)

- 3. Signal a repeat start and indicate a read operation

- 4. Read D7:0 (register address incremented after ack by host)

- 5. Read D15:8 (register address incremented after ack by host)

- Read D23:16 (register address incremented and next EQ location pre-fetched after ack by host)

- 7. The host stops the bus cycle

To repeat a read cycle for consecutive EQ RAM locations:

- Start (or repeat start instead of stopping the bus cycle in step 7) a write cycle indicating DACCRAM\_RD\_LO as the target address.

- 2. After the second byte is acknowledged, signal a repeated start.

- 3. Indicate a read operation

- 4. Read the DACCRAM READ LO register as described in step 4

- Read the DACCRAM\_READ\_MID register as described in step 5

- 6. Read the DACCRAM\_READ\_HI register as described in step 6

- Repeat steps 8-13 as desired

Figure 4. DAC Coefficient RAM Read Sequence

#### DACCRAM EQ Addresess

|      | EQ                        |      |                           | EC   | ว1                        |      |                           |

|------|---------------------------|------|---------------------------|------|---------------------------|------|---------------------------|

| Addr | Channel 0<br>Coefficients | Addr | Channel 1<br>Coefficients | Addr | Channel 0<br>Coefficients | Addr | Channel 1<br>Coefficients |

| 0x00 | EQ_COEF_0F0_B0            | 0x20 | EQ_COEF_1F0_B0            | 0x40 | EQ_COEF_2F0_B0            | 0x60 | EQ_COEF_3F0_B0            |

| 0x01 | EQ_COEF_0F0_B1            | 0x21 | EQ_COEF_1F0_B1            | 0x41 | EQ_COEF_2F0_B1            | 0x61 | EQ_COEF_3F0_B1            |

| 0x02 | EQ_COEF_0F0_B2            | 0x22 | EQ_COEF_1F0_B2            | 0x42 | EQ_COEF_2F0_B2            | 0x62 | EQ_COEF_3F0_B2            |

| 0x03 | EQ_COEF_0F0_A1            | 0x23 | EQ_COEF_1F0_A1            | 0x43 | EQ_COEF_2F0_A1            | 0x63 | EQ_COEF_3F0_A1            |

| 0x04 | EQ_COEF_0F0_A2            | 0x24 | EQ_COEF_1F0_A2            | 0x44 | EQ_COEF_2F0_A2            | 0x64 | EQ_COEF_3F0_A2            |

| 0x05 | EQ_COEF_0F1_B0            | 0x25 | EQ_COEF_1F1_B0            | 0x45 | EQ_COEF_2F1_B0            | 0x65 | EQ_COEF_3F1_B0            |

| 0x06 | EQ_COEF_0F1_B1            | 0x26 | EQ_COEF_1F1_B1            | 0x46 | EQ_COEF_2F1_B1            | 0x66 | EQ_COEF_3F1_B1            |

| 0x07 | EQ_COEF_0F1_B2            | 0x27 | EQ_COEF_1F1_B2            | 0x47 | EQ_COEF_2F1_B2            | 0x67 | EQ_COEF_3F1_B2            |

| 0x08 | EQ_COEF_0F1_A1            | 0x28 | EQ_COEF_1F1_A1            | 0x48 | EQ_COEF_2F1_A1            | 0x68 | EQ_COEF_3F1_A1            |

| 0x09 | EQ_COEF_0F1_A2            | 0x29 | EQ_COEF_1F1_A2            | 0x49 | EQ_COEF_2F1_A2            | 0x69 | EQ_COEF_3F1_A2            |

| 0x0A | EQ_COEF_0F2_B0            | 0x2A | EQ_COEF_1F2_B0            | 0x4A | EQ_COEF_2F2_B0            | 0x6A | EQ_COEF_3F2_B0            |

| 0x0B | EQ_COEF_0F2_B1            | 0x2B | EQ_COEF_1F2_B1            | 0x4B | EQ_COEF_2F2_B1            | 0x6B | EQ_COEF_3F2_B1            |

| 0x0C | EQ_COEF_0F2_B2            | 0x2C | EQ_COEF_1F2_B2            | 0x4C | EQ_COEF_2F2_B2            | 0x6C | EQ_COEF_3F2_B2            |

| 0x0D | EQ_COEF_0F2_A1            | 0x2D | EQ_COEF_1F2_A1            | 0x4D | EQ_COEF_2F2_A1            | 0x6D | EQ_COEF_3F2_A1            |

| 0x0E | EQ_COEF_0F2_A2            | 0x2E | EQ_COEF_1F2_A2            | 0x4E | EQ_COEF_2F2_A2            | 0x6E | EQ_COEF_3F2_A2            |

| 0x0F | EQ_COEF_0F3_B0            | 0x2F | EQ_COEF_1F3_B0            | 0x4F | EQ_COEF_2F3_B0            | 0x6F | EQ_COEF_3F3_B0            |

| 0x10 | EQ_COEF_0F3_B1            | 0x30 | EQ_COEF_1F3_B1            | 0x50 | EQ_COEF_2F3_B1            | 0x70 | EQ_COEF_3F3_B1            |

15

|      | EQ                        | 0    |                           |      | E                         | Q1   |                           |

|------|---------------------------|------|---------------------------|------|---------------------------|------|---------------------------|

| Addr | Channel 0<br>Coefficients | Addr | Channel 1<br>Coefficients | Addr | Channel 0<br>Coefficients | Addr | Channel 1<br>Coefficients |

| 0x11 | EQ_COEF_0F3_B2            | 0x31 | EQ_COEF_1F3_B2            | 0x51 | EQ_COEF_2F3_B2            | 0x71 | EQ_COEF_3F3_B2            |

| 0x12 | EQ_COEF_0F3_A1            | 0x32 | EQ_COEF_1F3_A1            | 0x52 | EQ_COEF_2F3_A1            | 0x72 | EQ_COEF_3F3_A1            |

| 0x13 | EQ_COEF_0F3_A2            | 0x33 | EQ_COEF_1F3_A2            | 0x53 | EQ_COEF_2F3_A2            | 0x73 | EQ_COEF_3F3_A2            |

| 0x14 | EQ_COEF_0F4_B0            | 0x34 | EQ_COEF_1F4_B0            | 0x54 | EQ_COEF_2F4_B0            | 0x74 | EQ_COEF_3F4_B0            |

| 0x15 | EQ_COEF_0F4_B1            | 0x35 | EQ_COEF_1F4_B1            | 0x55 | EQ_COEF_2F4_B1            | 0x75 | EQ_COEF_3F4_B1            |

| 0x16 | EQ_COEF_0F4_B2            | 0x36 | EQ_COEF_1F4_B2            | 0x56 | EQ_COEF_2F4_B2            | 0x76 | EQ_COEF_3F4_B2            |

| 0x17 | EQ_COEF_0F4_A1            | 0x37 | EQ_COEF_1F4_A1            | 0x57 | EQ_COEF_2F4_A1            | 0x77 | EQ_COEF_3F4_A1            |

| 0x18 | EQ_COEF_0F4_A2            | 0x38 | EQ_COEF_1F4_A2            | 0x58 | EQ_COEF_2F4_A2            | 0x78 | EQ_COEF_3F4_A2            |

| 0x19 | EQ_COEF_0F5_B0            | 0x39 | EQ_COEF_1F5_B0            | 0x59 | EQ_COEF_2F5_B0            | 0x79 | EQ_COEF_3F5_B0            |

| 0x1A | EQ_COEF_0F5_B1            | 0x3A | EQ_COEF_1F5_B1            | 0x5A | EQ_COEF_2F5_B1            | 0x7A | EQ_COEF_3F5_B1            |

| 0x1B | EQ_COEF_0F5_B2            | 0x3B | EQ_COEF_1F5_B2            | 0x5B | EQ_COEF_2F5_B2            | 0x7B | EQ_COEF_3F5_B2            |

| 0x1C | EQ_COEF_0F5_A1            | 0x3C | EQ_COEF_1F5_A1            | 0x5C | EQ_COEF_2F5_A1            | 0x7C | EQ_COEF_3F5_A1            |

| 0x1D | EQ_COEF_0F5_A2            | 0x3D | EQ_COEF_1F5_A2            | 0x5D | EQ_COEF_2F5_A2            | 0x7D | EQ_COEF_3F5_A2            |

| 0x1E | -                         | 0x3E | -                         | 0x5E | -                         | 0x7E | -                         |

| 0x1F | EQ_PRESCALE0              | 0x3F | EQ_PRESCALE1              | 0x5F | EQ_PRESCALE2              | 0x7F | EQ_PRESCALE3              |

Table 10. DACCRAM EQ Addresess

### • DACCRAM Bass/Treble Addresses

| Addr | Bass<br>Coefficients <sup>1</sup> | Addr | Treble<br>Coefficients | Addr | 3D<br>Coefficients |

|------|-----------------------------------|------|------------------------|------|--------------------|

| 0x80 | BASS_COEF_EXT1_B0                 | 0x97 | TREB_COEF_EXT1_B0      | 0xAE | 3D_COEF            |

| 0x81 | BASS_COEF_EXT1_B1                 | 0x98 | TREB_COEF_EXT1_B1      | 0xAF | 3D_MIX             |

| 0x82 | BASS_COEF_EXT1_B2                 | 0x99 | TREB_COEF_EXT1_B2      |      |                    |

| 0x83 | BASS_COEF_EXT1_A1                 | 0x9A | TREB_COEF_EXT1_A1      |      |                    |

| 0x84 | BASS_COEF_EXT1_A2                 | 0x9B | TREB_COEF_EXT1_A2      |      |                    |

| 0x85 | BASS_COEF_EXT2_B0                 | 0x9C | TREB_COEF_EXT2_B0      |      |                    |

| 0x86 | BASS_COEF_EXT2_B1                 | 0x9D | TREB_COEF_EXT2_B1      |      |                    |

| 0x87 | BASS_COEF_EXT2_B2                 | 0x9E | TREB_COEF_EXT2_B2      |      |                    |

| 0x88 | BASS_COEF_EXT2_A1                 | 0x9F | TREB_COEF_EXT2_A1      |      |                    |

| 0x89 | BASS_COEF_EXT2_A2                 | 0xA0 | TREB_COEF_EXT2_A2      |      |                    |

| 0x8A | BASS_COEF_NLF_M1 <sup>2</sup>     | 0xA1 | TREB_COEF_NLF_M1       |      |                    |

| 0x8B | BASS_COEF_NLF_M2                  | 0xA2 | TREB_COEF_NLF_M2       |      |                    |

| 0x8C | BASS_COEF_LMT_B0                  | 0xA3 | TREB_COEF_LMT_B0       |      |                    |

#### LOWER-POWER, HIGH-FIDELITY, CLASS-D AMPLIFIER

| Addr | Bass<br>Coefficients <sup>1</sup> | Addr | Treble<br>Coefficients | Addr | 3D<br>Coefficients |

|------|-----------------------------------|------|------------------------|------|--------------------|

| 0x8D | BASS_COEF_LMT_B1                  | 0xA4 | TREB_COEF_LMT_B1       |      |                    |

| 0x8E | BASS_COEF_LMT_B2                  | 0xA5 | TREB_COEF_LMT_B2       |      |                    |

| 0x8F | BASS_COEF_LMT_A1                  | 0xA6 | TREB_COEF_LMT_A1       |      |                    |

| 0x90 | BASS_COEF_LMT_A2                  | 0xA7 | TREB_COEF_LMT_A2       |      |                    |

| 0x91 | BASS_COEF_CTO_B0                  | 0xA8 | TREB_COEF_CTO_B0       |      |                    |

| 0x92 | BASS_COEF_CTO_B1                  | 0xA9 | TREB_COEF_CTO_B1       |      |                    |

| 0x93 | BASS_COEF_CTO_B2                  | 0xAA | TREB_COEF_CTO_B2       |      |                    |

| 0x94 | BASS_COEF_CTO_A1                  | 0xAB | TREB_COEF_CTO_A1       |      |                    |

| 0x95 | BASS_COEF_CTO_A2                  | 0xAC | TREB_COEF_CTO_A2       |      |                    |

| 0x96 | BASS_MIX                          | 0xAD | TREB_MIX               |      |                    |

<sup>1.</sup>All B0 coefficients are set to unity (400000h) by default. All others, including M1 and M2, are 0 by default.

Table 11. DACCRAM Bass/Treble Addresses

### 1.5. Gain and Dynamic Range Control

The gain for a given channel is controlled by the DACVOL registers. The range of gain supported is from -95.625db to 0db in 0.375db steps.

If the result of the gain multiply step would result in overflow of the 24-bit output word width, the output is saturated at the max positive or negative value.

In addition to simple gain control, the ACS32201 also provides sophisticated dynamic range control. The dynamic range control processing element implements limiting, dynamic range compression, and dynamic range expansion functions.

#### 1.6. Limiter

The Limiter function will limit the output of the DSP module to the Class-D and DAC modules. If the signal is greater than 0dB it will saturate at 0dB as the final processing step within the DSP module.

There are times when the user may intentionally want the output Limiter to perform this saturation, for example +6dB of gain applied within the DSP gain control and then limited to 0dB when output to the Class-D module would result in a clipped signal driving the speaker output. This clipped signal would obviously contribute to increased distortion on the speaker output which from the user listening perception it would "sound louder".

At other times, the system implementor may wish to protect speakers from overheating or provide hearing protection by intentionally limiting the output level before full scale is reached. A limit threshold, independent of the compressor threshold is provided for this purpose. It is expected that the limit threshold is set to a higher level than the compressor threshold.

<sup>2.</sup>NLF coefficients (M1, M2) have a range defined as +/-8, with 1 sign bit, 3 integer bits, and 20 fraction bits. So, unity for these values is 100000h. This is as opposed to the rest of the coefficient RAM, which has a range defined as +/-2, with 1 sign bit, 1 integer bit, and 22 fraction bits.

#### 1.7. Compressor

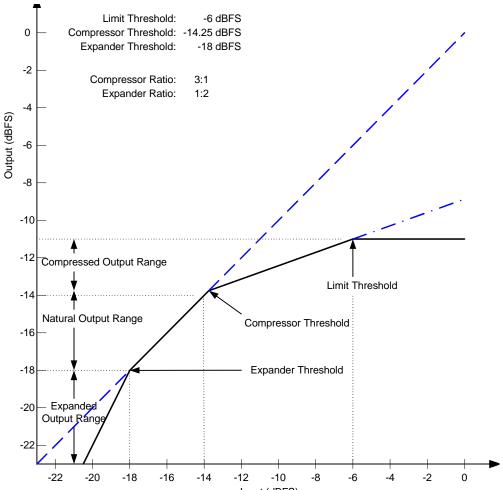

Figure 5. Gain Compressor, Output vs Input

The traditional compressor algorithm provides two functions simultaneously (depending on signal level). For higher level signals, it can provide a compression function to reduce the signal level. For lower level signals, it can provide an expansion function for either increasing dynamic range or noise gating.

The compressor monitors the signal level and, if the signal is higher than a threshold, will reduce the gain by a programmed ratio to restrict the dynamic range. Limiting is an extreme example of the compressor where, as the input signal level is increased, the gain is decreased to maintain a specific output level.

In addition to limiting the bandwidth of the compressed audio, it is common for compressed audio to also compress the dynamic range of the audio. The expansion function in the ACS32201 can help restore the original dynamics to the audio.

The expander is a close relative of the compressor. Rather than using signal dependent gain to restrict the dynamic range, the expander uses signal dependent gain to expand the dynamic range. Thus if a signal level is below a particular threshold, the expander will reduce the gain even further to extend the dynamic range of the material.

#### 1.7.1. Configuration

This compressor limiter provides the following configurable parameters.

- Compressor/limiter

- Threshold The threshold above which the compressor will reduce the dynamic range of the audio in the compression region.

- Ratio The ratio between the input dynamic range and the output dynamic range. For example, a ratio of 3 will reduce an input dynamic range of 9db to 3db.

- Attack Time The amount of time that changes in gain are smoothed over during the attack phase of the compressor.

- Release Time The amount of time that changes in gain are smoothed over during the release phase of the compressor.

- Makeup gain Used to increase the overall level of the compressed audio.

### Expander

- Threshold The threshold below which the expander will increase the dynamic range of the audio.

- Ratio The ratio between the input dynamic range and the output dynamic range of the audio in the expansion range. For example a ratio of 3 will take an input dynamic range of 9db and expand it to 27db.

- Attack Time The amount of time that changes in gain are smoothed over during the attack phase of the expander

- Release Time

- The amount of time that changes in gain are smoothed over during the release phase of the expander.

- Two level detection algorithms

- RMS Use an RMS measurement for the level.

- Peak Use a peak measurement for the level.

#### 1.7.2. Controlling parameters

In order to control this processing, there are a number of configurable parameters. The parameters and their ranges are:

- Compressor/limiter

- Threshold -40db to 0db relative to full scale.

- Ratio 1 to 20

- Attack Time typically 0 to 500ms

- Release Time typically 25ms to 2 seconds

- Makeup gain 0 to 40db

- Expander

- Threshold -30 to -60 dB

- Ratio 1 to 6

- Attack Time same as above

- Release Time same as above.

- Two level detection algorithms

- RMS

- Peak

#### 1.7.3. Overview

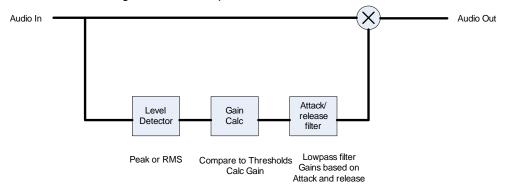

A basic block diagram of the compressor is shown below:

Figure 6. Compressor block diagram

As this diagram shows, there are 3 primary components of the compressor.

- Level Detector: The level detector, oddly enough, detects the level of the incoming signal. Since the comp/limiter is designed to work on blocks of signals, the level detector will either find the peak value of the block of samples to be processed or the rms level of the samples within a block.

- 2. **Gain Calculation:** The gain calculation block is responsible for taking the output of the level detector and calculating a target gain based on that level and the compressor and expander thresholds. The compressor recalculates the target gain value every block, typically every 10ms.

- The gain calculation operates in 3 regions:

- Linear region If the level is higher than the expander threshold and lower than the compression threshold, then the gain is 1.0

- Compression region When the level is higher than the compressor threshold, then the comp/limiter is in the compression region. The gain is a function of the compressor ratio and the signal level.

- Expansion region When the signal is lower than the expansion threshold, the comp/limiter is in the expansion region. In this region, the gain is a function of the signal level and the expansion ratio.

- Compression region gain calculation: In the compression region, the gain calculation is:

```

Atten(in db) = (1-1/ratio)(threshold(in db) - level(in db);

```

- For example,

- Ratio = 4:1 compression

- Threshold = -16db

- Level = -4 db

The required attenuation is: 9db or a gain coefficient of 0.1259.

Translating this calculation from log space to linear yields the formula:

Expansion region gain calculation: In the expansion region, the attenuation calculation is:

Atten(in db) = (1 - ratio)(threshold-level);

- For example,

- Ratio = 3:1

- Threshold = -40db

- Level = -44 db

The resulting attenuation required is 8db or a gain value of 0.1585.

The linear equation for calculating the gain is:

```

Gain =(level/threshold)<sup>ratio</sup>*(threshold/level)

```

State Transitions: In addition to calculating the new gain for the compressor, the gain calculation block will also select the filter coefficient for the attack/release filter. The rules for selecting the coefficient are as follows:

In the compression region:

- If the gain calculated is less than the last gain calculated (more compression is being applied), then the filter coefficient is the compressor attack.

- If the gain calculated is more than the last gain calculated (less compression), the filter coefficient is the compressor release.

- In the expansion region:

- If the calculated gain is less than the last gain calculated (closing expander, the filter coefficient is the expander attack.

- If the calculated gain is more than the last gain calculated, the filter coefficient is the expander release.

In the linear region:

- Modify gain until a gain of 1.0 is obtained.

- If the last non-linear state was compression, use the compressor release.

- If the last non-linear state was expansion, use the expander attack.

- 3. Attack/Release filter: In order to prevent objectionable artifacts, the gain is smoothly ramped from the current value to the new value calculated by the gain calculation block. In the PC-based comp/limiter, this is achieved using a simple tracking lowpass filter to smooth out the abrupt transitions. The calculation (using the coefficient (coeff) selected by the gain block) is:

```

Filtered_gain = coeff*last_filtered_gain + (1.0 - coeff)*target_gain;

```

This creates a exponential ramp from the current gain value to the new value.

### 1.7.4. Limiter/Compressor Registers

### General compressor/limiter/expander control

| Register Address    | Bit | Label     | Туре | Default | Description                                                                                                                                                                |

|---------------------|-----|-----------|------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | 7:5 | RSVD      | R    | 0h      | Reserved                                                                                                                                                                   |

|                     | 4   | Lvl_Mode  | RW   | 0       | CLE Level Detection Mode 0 = Average 1 = Peak                                                                                                                              |

| R37 (25h)<br>CLECTL | 3   | WindowSel | RW   | 0       | Window width selection for level detection:  0 = equivalent of 512 samples of selected Base Rate (~10-16ms)  1 = equivalent of 64 samples of selected Base Rate (~1.3-2ms) |

|                     | 2   | Exp_en    | RW   | 0       | 1 = enable expander                                                                                                                                                        |

|                     | 1   | Limit_en  | RW   | 0       | 1 = enable limiter                                                                                                                                                         |

|                     | 0   | Comp_en   | RW   | 0       | 1 = enable compressor                                                                                                                                                      |

Table 12. CLECTL Register

### Compressor/Limiter/Expander make-up gain

| Register Address | Bit | Label       | Type | Default | Description              |

|------------------|-----|-------------|------|---------|--------------------------|

| R38 (26h)        | 7:5 | RSVD        | R    | 0h      | Reserved                 |

| MUGAIN           | 4:0 | CLEMUG[4:0] | RW   | 0h      | 0dB46.5dB in 1.5dB steps |

Table 13. MUGAIN Register

### Compressor Threshold

| Register Address    | Bit | Label       | Type | Default | Description                            |

|---------------------|-----|-------------|------|---------|----------------------------------------|

| R39 (27h)<br>COMPTH | 7:0 | COMPTH[7:0] | RW   | 00h     | FFh00h = 0dB95.625dB in 0.375dB steps. |

Table 14. COMPTH Register

### • Compressor ratio register

| Register Address    | Bit | Label       | Туре | Default | Description                                                                                |

|---------------------|-----|-------------|------|---------|--------------------------------------------------------------------------------------------|

|                     | 7:5 | RSVD        | R    | 000     | Reserved                                                                                   |

| R40 (28h)<br>CMPRAT | 4:0 | CMPRAT[4:0] | RW   | 00h     | Compressor Ratio<br>00h = Reserved<br>01h = 1.5:1<br>02h14h = 2:120:1<br>15h1Fh = Reserved |

Table 15. CMPRAT Register

#### Compressor Attack Time Constant Register (Low)

| Register Address     | Bit | Label       | Туре | Default | Description                                                                                      |

|----------------------|-----|-------------|------|---------|--------------------------------------------------------------------------------------------------|

| R41 (29h)<br>CATKTCL | 7:0 | CATKTC[7:0] | RW   | 00h     | Low byte of the time constant used to ramp to a new gain value during a compressor attack phase. |

Table 16. CATKTCL Register

#### Compressor Attack Time Constant Register (High)

| Register Address     | Bit | Label        | Туре | Default | Description                                                                                       |

|----------------------|-----|--------------|------|---------|---------------------------------------------------------------------------------------------------|

| R42 (2Ah)<br>CATKTCH | 7:0 | CATKTC[15:8] | RW   | 00h     | High byte of the time constant used to ramp to a new gain value during a compressor attack phase. |

Table 17. CATKTCH Register

### Compressor Release Time Constant Register (Low)

| Register Address     | Bit | Label       | Туре | Default | Description                                                                                       |

|----------------------|-----|-------------|------|---------|---------------------------------------------------------------------------------------------------|

| R43 (2Bh)<br>CRELTCL | 7:0 | CRELTC[7:0] | RW   | 00h     | Low byte of the time constant used to ramp to a new gain value during a compressor release phase. |

#### Table 18. CRELTCL Register

#### Compressor Release Time Constant Register (High)

| Register Address     | Bit | Label        | Туре | Default | Description                                                                                        |

|----------------------|-----|--------------|------|---------|----------------------------------------------------------------------------------------------------|

| R44 (2Ch)<br>CRELTCH | 7:0 | CRELTC[15:8] | RW   | l OOn   | High byte of the time constant used to ramp to a new gain value during a compressor release phase. |

#### Table 19. CRELTCH Register

#### • Limiter Threshold Register

| Register Address   | Bit | Label      | Туре | Default | Description                            |

|--------------------|-----|------------|------|---------|----------------------------------------|

| R45 (2Dh)<br>LIMTH | 7:0 | LIMTH[7:0] | RW   | 00h     | FFh00h = 0dB95.625dB in 0.375dB steps. |

Table 20. LIMTH Register

#### Limiter Target Register

| Register Address    | Bit | Label       | Туре | Default | Description                            |

|---------------------|-----|-------------|------|---------|----------------------------------------|

| R46 (2Eh)<br>LIMTGT | 7:0 | LIMTGT[7:0] | RW   | 00h     | FFh00h = 0dB95.625dB in 0.375dB steps. |

Table 21. LIMTGT Register

### • Limiter Attack Time Constant Register (Low)

| Register Address     | Bit | Label       | Type | Default | Description                                                                                   |

|----------------------|-----|-------------|------|---------|-----------------------------------------------------------------------------------------------|

| R47 (2Fh)<br>LATKTCL | 7:0 | LATKTC[7:0] | RW   | 00h     | Low byte of the time constant used to ramp to a new gain value during a limiter attack phase. |

### Table 22. LATKTCL Register

#### Limiter Attack Time Constant Register (High)

| Register Address     | Bit | Label        | Туре | Default | Description                                                                                    |

|----------------------|-----|--------------|------|---------|------------------------------------------------------------------------------------------------|

| R48 (30h)<br>LATKTCH | 7:0 | LATKTC[15:8] | RW   | OOD     | High byte of the time constant used to ramp to a new gain value during a limiter attack phase. |

#### Table 23. LATKTCH Register

### • Limiter Release Time Constant Register (Low)

| Register Address     | Bit | Label       | Type | Default | Description                                                                                    |

|----------------------|-----|-------------|------|---------|------------------------------------------------------------------------------------------------|

| R49 (31h)<br>LRELTCL | 7:0 | LRELTC[7:0] | RW   | 00h     | Low byte of the time constant used to ramp to a new gain value during a limiter release phase. |

Table 24. LRELTCL Register

#### • Limiter Release Time Constant Register (High)

| Register Address     | Bit | Label        | Туре | Default | Description                                                                                     |

|----------------------|-----|--------------|------|---------|-------------------------------------------------------------------------------------------------|

| R50 (32h)<br>LRELTCH | 7:0 | LRELTC[15:8] | RW   | OOn     | High byte of the time constant used to ramp to a new gain value during a limiter release phase. |

Table 25. LRELTCH Register

### 1.7.5. Expander Registers

#### Expander Threshold Register

| Register Address   | Bit | Label      | Type | Default | Description                                    |

|--------------------|-----|------------|------|---------|------------------------------------------------|

| R51 (33h)<br>EXPTH | 7:0 | EXPTH[7:0] | RW   | 00h     | Expander threshold: 095.625dB in 0.375dB steps |

Table 26. EXPTH Register

#### • Expander Ratio Register

| Register Address    | Bit | Label       | Туре | Default | Description                                  |

|---------------------|-----|-------------|------|---------|----------------------------------------------|

|                     | 7:3 | RSVD        | R    | 00h     | Reserved                                     |

| R52 (34h)<br>EXPRAT |     | EXPRAT[2:0] | RW   | 000     | Expander Ratio 0h1h = Reserved 2h7h = 1:21:7 |

Table 27. EXPRAT Register

### • Expander Attack Time Constant Register (Low)

| Register Address     | Bit | Label       | Туре | Default | Description                                                                                    |

|----------------------|-----|-------------|------|---------|------------------------------------------------------------------------------------------------|

| R53 (35h)<br>XATKTCL | 7:0 | XATKTC[7:0] | RW   | 00h     | Low byte of the time constant used to ramp to a new gain value during a expander attack phase. |

Table 28. XATKTCL Register

#### Expander Attack Time Constant Register (High)

| Register Address     | Bit | Label        | Туре | Default | Description                                                                                     |

|----------------------|-----|--------------|------|---------|-------------------------------------------------------------------------------------------------|

| R54 (36h)<br>XATKTCH | 7:0 | XATKTC[15:8] | RW   | 00h     | High byte of the time constant used to ramp to a new gain value during a expander attack phase. |

Table 29. XATKTCH Register

### Expander Release Time Constant Register (Low)

| Register Address     | Bit | Label       | Туре | Default | Description                                                                                     |

|----------------------|-----|-------------|------|---------|-------------------------------------------------------------------------------------------------|

| R55 (37h)<br>XRELTCL | 7:0 | XRELTC[7:0] | RW   | 0       | Low byte of the time constant used to ramp to a new gain value during a expander release phase. |

Table 30. XRELTCL Register

#### Expander Release Time Constant Register (High)

| Register Address | Bit | Label        | Туре | Default | Description                                          |

|------------------|-----|--------------|------|---------|------------------------------------------------------|

| R56 (38h)        | 7:0 | XRELTC[15:8] | RW   | 0       | High byte of the time constant used to ramp to a new |

| XRELTCH          | 7.0 | XXLL10[10.0] | 1200 |         | gain value during a expander release phase.          |

Table 31. XRELTCH Register

### 1.8. Output Effects

The ACS32201 offers Bass enhancement, Treble enhancement, Stereo Depth enhancement. The output effects processing is outlined in the following sections.

| Register Address   | Bit | Label   | Туре | Default | Description                                                 |

|--------------------|-----|---------|------|---------|-------------------------------------------------------------|

|                    | 7:5 | RSVD    | R    | 000     | Reserved                                                    |

| DE7 (20h)          | 4   | 3DEN    | RW   | 0       | 3D Enhancement Enable<br>0 = Disabled 1 = Enabled           |

|                    | 3   | TEEN    | RW   | 0       | Treble Enhancement Enable 0 = Disabled 1 = Enabled          |

| R57 (39h)<br>FXCTL | 2   | TNLFBYP | RW   | 0       | Treble Non-linear Function Bypass: 0 = Enabled 1 = Bypassed |

|                    | 1   | BEEN    | RW   | 0       | Bass Enhancement Enable 0 = Disabled 1 = Enabled            |

|                    | 0   | BNLFBYP | RW   | 0       | Bass Non-linear Function Bypass: 0 = Enabled 1 = Bypassed   |

Table 32. FX Control Register

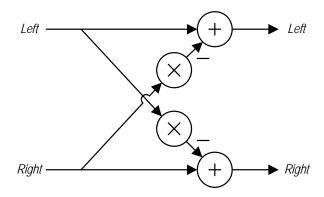

### 1.9. Stereo Depth (3-D) Enhancement

The ACS32201 has a digital depth enhancement option to artificially increase the separation between the left and right channels, by enabling the attenuation of the content common to both channels. The amount of attenuation is programmable within a range. The input is prescaled (fixed) before summation to prevent saturation.

The 3-D enhancement algorithm is a tried and true algorithm that uses two principles.

- 1. If the material common to the two channels is removed, then the speakers will sound more 3-D.

- 2. If the material for the opposite channel is presented to the current channel inverted, it will tend to cancel any material from the opposite channel on the current ear. For example, if the material from the right is presented to the left ear inverted, it will cancel some of the material from the right ear that is leaking into the right ear.

Figure 7. 3-D Channel Inversion

25

Note: 3D\_Mix specifies the amount of the common signal that is subtracted from the left and right channels. This number is a fractional amount between 0 and 1. For proper operation, this value is typically negative.

### 1.10. Psychoacoustic Bass Enhancement

One of the primary audio quality issues with small speaker systems is their inability to reproduce significant amounts of energy in the bass region (below 200Hz). While there is no magic mechanism to make a speaker reproduce frequencies that it is not capable of, there are mechanisms for fooling the ear into thinking that the bass material is being heard.

The psychoacoustic bass processor relies on a psychoacoustic principle called "missing fundamental". If the human ear hears a proper series of harmonics for a particular bass note, the listener will hear the fundamental of that series, even if it is not present.

### 1.11. PsychoacousticTreble Enhancement

One of the mechanisms used to limit the bit rate for compressed audio is to first remove high frequency information before compression. When these files like low bit rate MP3 are decompressed, this can lead to dull sounding audio. The TSI treble enhancement replaces these lost high frequencies.

The psychoacoustic bass processor relies on a psychoacoustic principle called "missing fundamental". If the human ear hears a proper series of harmonics for a particular bass note, the listener will hear the fundamental of that series, even if it is not present.

The psychoacoustic treble processor relies on a psychoacoustic principle called "missing fundamental". If the human ear hears a proper series of harmonics for a particular treble note, the listener will hear the fundamental of that series, even if it is not present.

### 1.12. Mute and De-Emphasis

The ACS32201 has a Soft Mute function, which is used to gradually attenuate the digital signal volume to zero. The gain returns to its previous setting if the soft mute is removed. At startup, the codec is muted by default; to enable audio play, the mute bit must be cleared to 0.

After the equalization filters, de-emphasis may be performed on the audio data to compensate for pre-emphasis that may be included in the audio stream. De-emphasis filtering is only available for 48kHz, 44.1kHz, and 32kHz sample rates

#### 1.13. Mono Operation and Phase Inversion

Normal stereo operation converts left and right channel digital audio data to analog in separate DACs. However, it is also possible to have the same signal (left or right) appear on both output channels by disabling one channel; alternately, there is a mono-mix mode that mixes the two channels digitally before converting to using only one converter. In this mode, the resulting mixed stream signal can appear on both PWM output channels. The DAC output defaults to non-inverted. Setting DACPOLL and DACPOLR bits will invert the DAC output phase on the left and right channels.

26

# 1.13.1. DAC Control Register

| Register Address     | Bit | Label             | Туре | Default | Description                                                                                                                                                       |

|----------------------|-----|-------------------|------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      | 7   | DACPOLR           | RW   | 0       | Invert DAC Right signal                                                                                                                                           |

|                      | 6   | DACPOLL           | RW   | 0       | Invert DAC Left signal                                                                                                                                            |

| R24 (18h)<br>CNVRTR1 | 5:4 | DMONOMIX<br>[1:0] | RW   | 00      | DAC mono mix 00: stereo 01: mono ((L/2)+(R/2)) into DACL, '0' into DACR 10: mono ((L/2)+(R/2)) into DACR, '0' into DACL 11: mono ((L/2)+(R/2)) into DACL and DACR |

|                      | 3   | DACMU             | RW   | 1       | Digital Soft Mute 1 = mute 0 = no mute (signal active)                                                                                                            |

|                      | 2   | DEEMP             | RW   | 0       | De-emphasis Enable 1 = De-emphasis Enabled 0 = No De-emphasis                                                                                                     |

|                      | 1:0 | RSVD              | R    | 00      | Reserved                                                                                                                                                          |

Table 33. CNVRTR1 Register

#### 1.14. Analog Outputs

#### 1.14.1. Speaker Outputs

The LSPKOut (L+, L-) and RSPKOut (R+, R-) pins are intended to drive an 8 ohm speaker pair. The SPKOut pins can drive a  $16\Omega$  or  $32\Omega$  headphone or alternately drive a line output. The signal volume of the speaker amplifier can be independently adjusted under software control by writing to SPKVOL\_L and SPKVOL\_R. Setting the volume to 0000000 will mute the output driver; the output remains at ground, so that no click noise is produced when muting or un-muting.

Gains above 0dB run the risk of clipping large signals.

To minimize artifacts such as clicks and zipper noise, the BTL outputs feature a volume fade function that smoothly changes volume from the current value to the target value.

| Register Address   | Bit | Label             | Туре | Default          | Description                                                                                                                                                                                                                     |

|--------------------|-----|-------------------|------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | 7   | RSVD              | R    | 0                | Reserved                                                                                                                                                                                                                        |

| R2 (2h)<br>SPKVOLL | 6:0 | SPKVOL_L<br>[6:0] | RW   | 1101111<br>(0dB) | Left Speaker Volume 1111111 = +12dB 1111110 = +11.25dB 1101111 = 0dB 0001000 to 0000001 = -77.25dB 000000= Mute Note: If SPKVOLU is set, this setting will take effect after the next write to the Right Input Volume register. |

|                    | 7   | RSVD              | R    | 0                | Reserved                                                                                                                                                                                                                        |

| R3 (3h)<br>SPKVOLR | 6:0 | SPKVOL_R<br>[6:0] | RW   | 1101111<br>(0dB) | Right Speaker Volume 1111111 = +12dB 1111110 = +11.25dB 1101111 = 0dB 0001000 to 0000001 = -77.25dB 0000000 = Mute                                                                                                              |

1.14.1.1. Speaker Volume Control Registers

Table 34. SPKVOL L/R Registers

#### 1.14.2. Class D Audio Processing

The Class D PWM Controller performs the following signal processing:

- Feedback filters are applied to shape any noise. The filters move noise from audible frequencies to frequencies above the audio range.

- The PWM block converts the data streams to tri-state PWM signals and sends them to the power stages.

- Finally, the Class-D controller block adjusts the output volume to provide constant output power across supply voltage.

The power stages boost the signals to higher levels, sufficient to drive speakers at a comfortable listening level.

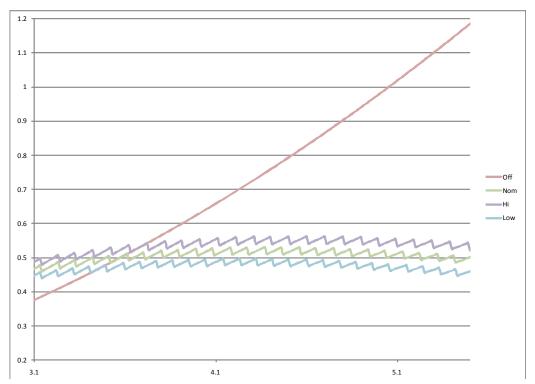

#### 1.14.2.1. Constant Output Power Mode

In normal operation the BTL amplifier is rated at 0.5W (full scale digital with 6dB BTL gain) into an 8 ohm load at 3.6V but will vary from about 0.38W to about 1.2W across a 3.1V to 5.5V supply range. However, when constant output power mode is enabled, the full scale output is held constant from 3.1V to 5.5V.

The BTL amplifier in ACS32201 will continuously adjust to power supply changes to ensure that the full scale output power remains constant. This is not an automatic level control. Rather, this function prevents sudden volume changes when switching between battery and line power. Please note, when in this mode the amplifier efficiency may be reduced and decreases with higher supply voltages and lower target values.

A simple 5-bit ADC is used to monitor PVDD. As PVDD raises or lowers, the analog circuit will send a 5-bit code to the digital section that will average and then calculate a gain adjustment. The BTL audio signal will be multiplied by this gain value (in addition to the user volume controls).

The user will select a target value for the circuit. The constant output function will calculate a gain adjustment that will provide approximately the same full scale output voltage as provided when PVDD causes the same code value. So, if the target is 9 then a PVDD voltage of about 3.7V would generate a code value of 9 and a full scale output power of about 630mW into 8 ohms. If PVDD should rise to 4V, generating a code of 13, then the constant output power circuit would reduce the gain by 0.75dB (4 codes \* 0.1875dB) to keep the full scale output at the target level.

The circuit may be configured to add gain, attenuation, or both to maintain the full-scale output level. If the needed adjustment falls outside of the range of the circuit (only attenuation is enabled and gain is needed, for example) then the circuit will apply as much correction as it is able. Through the use of gain, attenuation, and target values, different behaviors may be implemented: