### **FEATURES AND BENEFITS**

- Eliminates need for concentrator core or shield

- Contactless, lossless, noninvasive current sensing

- Suited for applications where current flows through busbar or PCB

- High operating bandwidth: DC to 250 kHz

- Overcurrent (OCF) and overtemperature (OTF) detection on the fault pin

- Differential Hall sensing rejects common-mode magnetic fields

- Very fast response time (<2 μs typ)

- Wide sensing range (3 to 28 mV/G)

- □ Ideal for sensing currents from 100 A to >4000 A

- Factory-programmed segmented linear temperature compensation (TC) provides low thermal drift

Sensitivity ±1% (typ)

- $\Box$  Offset  $\pm 3$  mV (typ)

- Customer-programmable, high-resolution offset and sensitivity trim

- Wide spacing of Hall elements for improved SNR and thermal performance

- Ultra-sensitive Hall elements for improved noise performance

Continued on the next page...

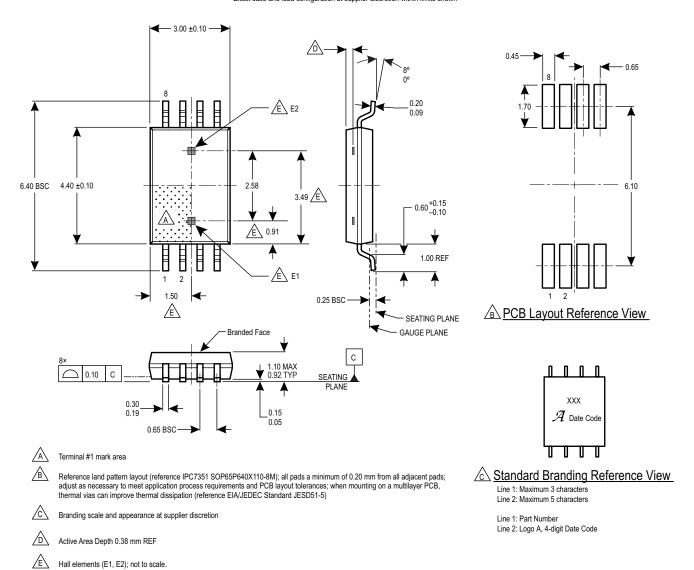

### PACKAGE:

8-pin TSSOP package (suffix LU)

Not to scale

### DESCRIPTION

The Allegro ACS37610 current sensor IC enables low-cost solutions for AC and DC current sensing without the need for an external field concentrator core or a U-shaped magnetic shield. It is designed for applications where hundreds or thousands of amperes flow through a busbar or PCB.

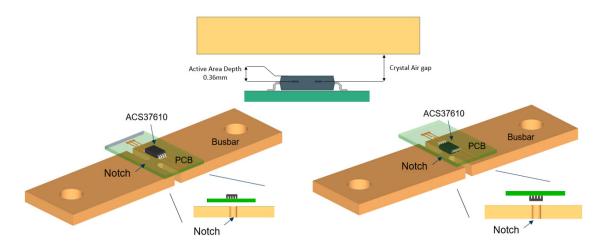

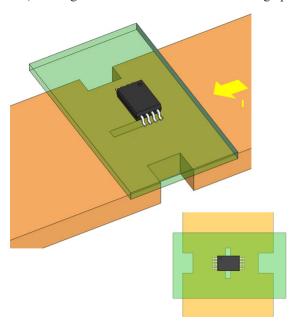

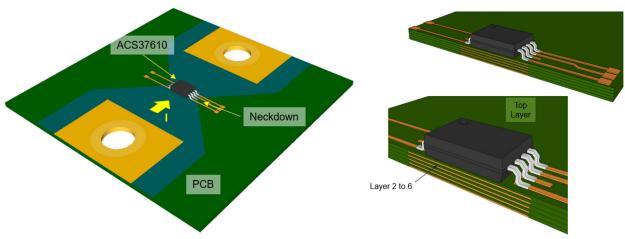

Current flowing through a busbar or PCB trace generates a magnetic field that is sensed by the monolithic, low-offset, linear Hall IC. The differential sensing topology virtually eliminates all types of error caused by common-mode stray magnetic fields. The wide spacing between the differential Hall elements (2.58 mm) coupled with the increased sensitivity of each Hall element enable the ACS37610 to achieve a superior signal-to-noise ratio (SNR) and improved resolution. While not mandatory, a notch or slit in the current-carrying busbar or PCB copper trace provides further improvements to system SNR. High isolation is achieved via the no-contact nature of this simple assembly.

The ACS37610 is offered with regular and low-power mode, enabling customers to achieve optimal SNR and power consumption. A dedicated user-programmable overcurrent and overtemperature fault pin and a slew of built-in diagnostics, including broken-ground and VCC detection, make it ideal

Continued on the next page...

### TYPICAL APPLICATIONS

- · High-voltage traction motor inverter

- 48 V/12 V auxiliary inverter

- · Heterogeneous redundant battery monitoring

- · Overcurrent detection

- DC-to-DC converter

- · Smart fuse

- Power distribution unit (PDU)

- · Power supply

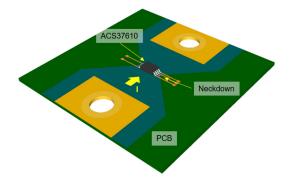

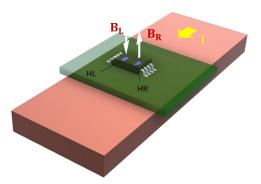

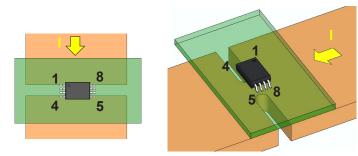

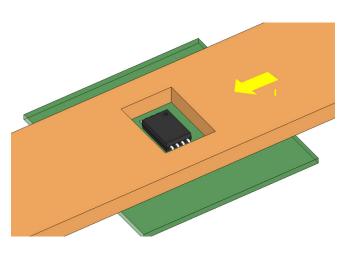

Figure 1: Current Through PCB

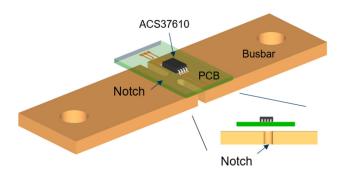

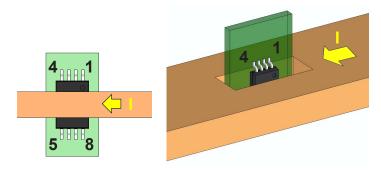

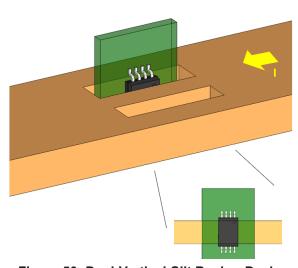

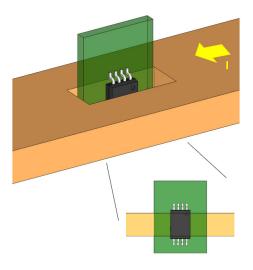

Figure 2: Current Through Busbar

# Coreless, High Precision, Hall-Effect Current Sensor IC with Common-Mode Field Rejection, Overcurrent and Overtemperature Detection

### **FEATURES AND BENEFITS (continued)**

- Wide ambient temperature range: -40°C to 150°C

- 3.3 or 5 V single supply operation

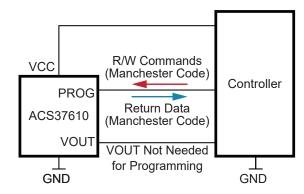

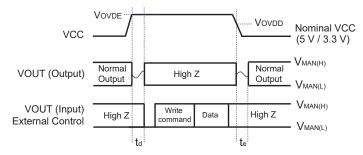

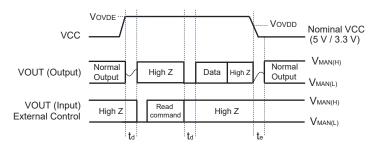

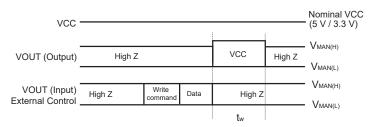

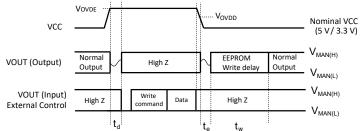

- Programmable through output pin or through dedicated programming pin for easier device programming

- AEC-Q100 Grade 0, automotive qualified

- Monolithic Hall IC for high reliability

- Surface-mount, small-footprint, low-profile TSSOP-8 package

### **DESCRIPTION** (continued)

for safety-critical applications. The accuracy and flexibility of this device is enhanced by user programmability, performed via the output pin or through the dedicated programming pin, which allows the device to be optimized in the application and cancels errors caused by mechanical assembly tolerances on the PCB. Device specifications apply across an extended ambient temperature range: –40°C to 150°C.

The ACS37610 is suitable for space-constrained applications because of its low-profile eight-pin surface-mount thin-shrink small-outline package (TSSOP) package (Allegro part number suffix -LU) that is lead (Pb) free, with 100% matte tin leadframe plating. The sensor can be mounted in a horizontal or vertical orientation relative to the busbar, providing superior flexibility in mechanical assemblies.

### **SELECTION GUIDE**

| Part Number          | Nominal Supply<br>Voltage (V) | Differential<br>Magnetic<br>Input Range, (G) | Sensitivity<br>Sens (Typ.)<br>(mV/G)[1] | Sensitivity<br>Trim Range<br>(mV/G) [1] | T <sub>A</sub><br>(°C) | Packing <sup>[2]</sup>       |

|----------------------|-------------------------------|----------------------------------------------|-----------------------------------------|-----------------------------------------|------------------------|------------------------------|

| ACS37610LLUATR-005B5 | 5                             | ±400                                         | 5                                       | 3 to 7                                  |                        |                              |

| ACS37610LLUATR-010B5 | 5                             | ±200                                         | 10                                      | 6 to 14                                 |                        |                              |

| ACS37610LLUATR-020B5 | 5                             | ±100                                         | 20                                      | 12 to 28                                | -40 to 150             | 4000 pieces per 13-inch reel |

| ACS37610LLUATR-020U5 | 5                             | 0 to 200                                     | 20                                      | 12 to 28                                | 1                      |                              |

| ACS37610LLUATR-010B3 | 3.3                           | ±132                                         | 10                                      | 6 to 14                                 |                        |                              |

<sup>[1]</sup> Measured at nominal supply voltage. Contact Allegro for other sensitivity options.

<sup>[2]</sup> Contact Allegro for additional packing options.

# Coreless, High Precision, Hall-Effect Current Sensor IC with Common-Mode Field Rejection, Overcurrent and Overtemperature Detection

### **Table of Contents**

| Features and Benefits            | 1  |

|----------------------------------|----|

| Description                      | 1  |

| Package                          | 1  |

| Typical Applications             | 1  |

| Selection Guide                  | 2  |

| Absolute Maximum Ratings         | 4  |

| ESD Ratings                      | 4  |

| Thermal Characteristics          |    |

| Typical Application Circuits     | 5  |

| Pinout Diagram and Pinout List   | 6  |

| Functional Block Diagram         | 7  |

| Common Operating Characteristics | 8  |

| Fault Characteristics            | 10 |

| Performance Characteristics      | 11 |

| Functional Description           | 16 |

| Principle of Operation           | 16 |

| Device Diagnostics               | 17 |

| Broken Wire Detection            | 18 |

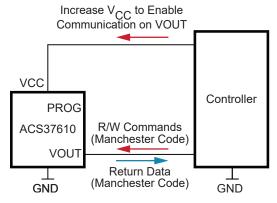

| Device Programming               | 19 |

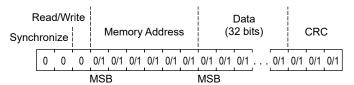

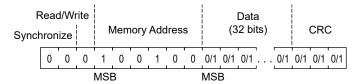

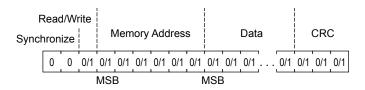

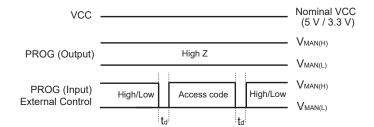

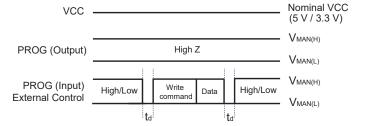

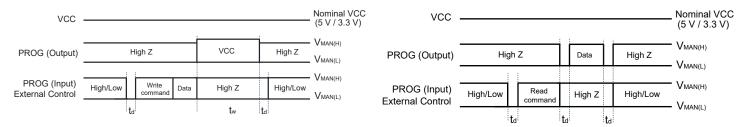

| Serial Communication             | 19 |

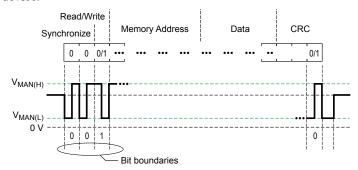

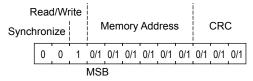

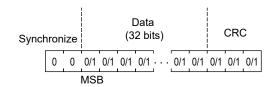

| Manchester Protocol              | 20 |

| Using the COM_LOCK bit           | 21 |

| WRITE LOCK bit                   | 21 |

| EEPROM Error Checking and Correction (ECC)             | 21 |

|--------------------------------------------------------|----|

| Detecting ECC Error                                    | 21 |

| EEPROM and Programming Parameters                      |    |

| Lock Bits Mechanism (WRITE LOCK/COM LOCK)              | 25 |

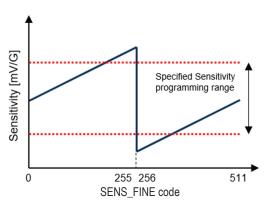

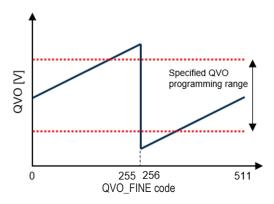

| Programming Sensitivity (SENS_FINE) and Quiescent      |    |

| Voltage Output (QVO)                                   | 25 |

| Polarity (POL)                                         | 26 |

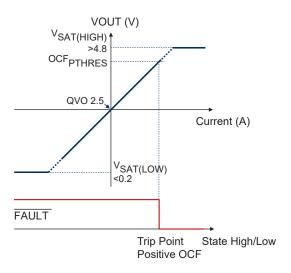

| Positive Overcurrent Fault Threshold (OCF_P_THRES)     | 26 |

| Negative Overcurrent Fault Threshold (OCF_N_THRES)     | 26 |

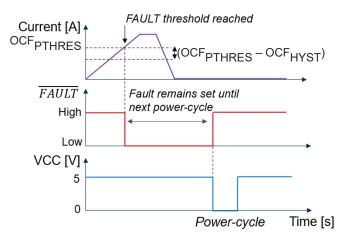

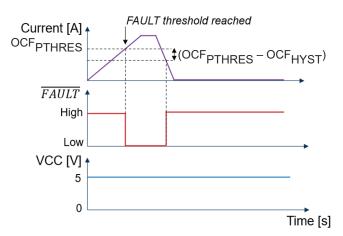

| Fault Latch (FAULT_LATCH)                              | 27 |

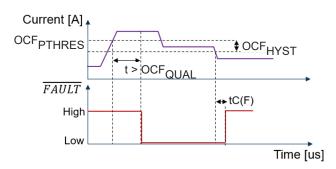

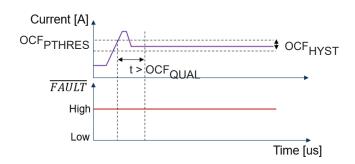

| Overcurrent Fault Qualifier (OCF_QUAL)                 | 28 |

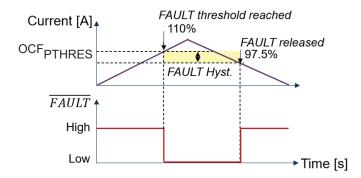

| Overcurrent Fault Hysteresis (OCF HYST)                |    |

| Temperature Output (TEMP_OUT)                          | 29 |

| Definitions of Accuracy Characteristics                |    |

| Definitions of Dynamic Response Characteristics        | 33 |

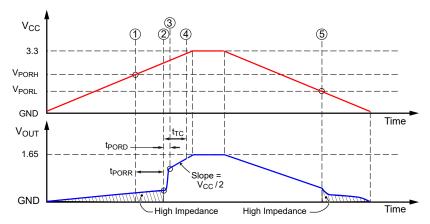

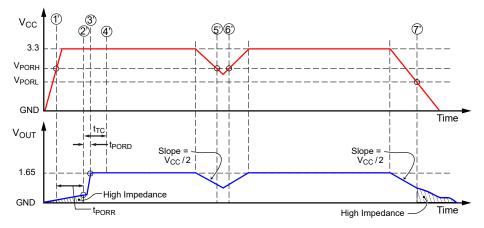

| Power-On Reset, Undervoltage and Overvoltage Detection |    |

| Operation                                              | 34 |

| Application Information                                |    |

| Typical Application—Busbar Current Sensing             | 36 |

| Multiple Busbar Design Options                         | 37 |

| Typical Application—PCB Sensing                        | 38 |

| Package Outline Drawing                                | 39 |

### **ABSOLUTE MAXIMUM RATINGS**

| Characteristic                           | Symbol                   | Notes                                                   | Rating     | Unit |

|------------------------------------------|--------------------------|---------------------------------------------------------|------------|------|

| Supply Voltage                           | V <sub>CC</sub>          | For a maximum duration of 1 minute                      | 7.5        | V    |

| Reverse Supply Voltage                   | V <sub>RCC</sub>         |                                                         | -0.5       | V    |

| Output Voltage                           | V <sub>OUT</sub>         |                                                         | 6.5        | V    |

| Reverse Output Voltage                   | V <sub>ROUT</sub>        |                                                         | -0.5       | V    |

| Fault Voltage                            | V <sub>F</sub>           |                                                         | 6.5        | V    |

| Reverse Fault Output Voltage             | V <sub>FR</sub>          |                                                         | -0.5       | V    |

| Output Source Current                    | I <sub>OUT(Source)</sub> | VOUT to GND                                             | 25         | mA   |

| Output Sink Current                      | I <sub>OUT(Sink)</sub>   | Maximum survivable sink or source current on the output | 10         | mA   |

| Nominal Operating Ambient<br>Temperature | T <sub>A</sub>           | Range L                                                 | -40 to 150 | °C   |

| Maximum Junction Temperature             | T <sub>J(max)</sub>      |                                                         | 165        | °C   |

| Storage Temperature                      | T <sub>stg</sub>         |                                                         | -65 to 165 | °C   |

### **ESD RATINGS**

| Characteristic       | Symbol           | Test Conditions  | Value | Unit |

|----------------------|------------------|------------------|-------|------|

| Human Body Model     | $V_{HBM}$        | Per JEDEC JS-001 | 9     | kV   |

| Charged Device Model | V <sub>CDM</sub> | Per JEDEC JS-002 | 1     | kV   |

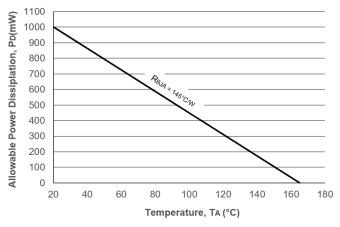

### THERMAL CHARACTERISTICS: May require derating at maximum conditions; see application information

| Characteristic             | Symbol          | Test Conditions [1]                            | Value | Unit |

|----------------------------|-----------------|------------------------------------------------|-------|------|

| Package Thermal Resistance | $R_{\theta JA}$ | TSSOP-8 on 4-layer PCB based on JEDEC standard | 145   | °C/W |

<sup>[1]</sup> Additional thermal information available on the Allegro website.

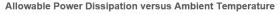

Figure 3: Allowable Power Dissipation

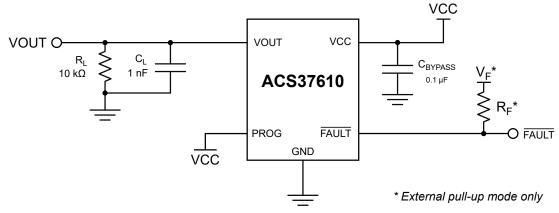

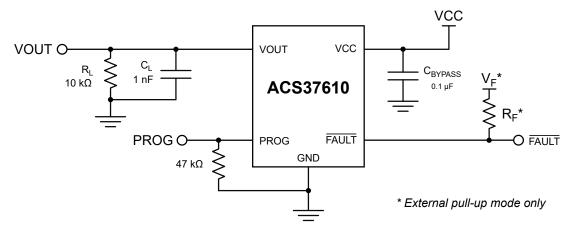

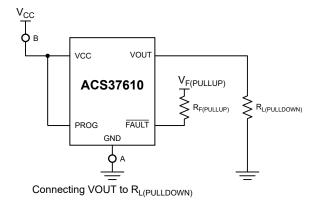

### TYPICAL APPLICATION CIRCUITS

Figure 4: Typical Application Circuit (Programming Pin Not Used)

Figure 5: Typical Application Circuit (Programming Pin Used)

The ACS37610 outputs an analog signal,  $V_{OUT}$ , that varies linearly with the bidirectional AC or DC field sensed, within the range specified.  $C_L$  is for optimal noise management, with values that depend on the application.  $R_L$  is an optional pulldown to GND or pullup to VCC for broken-wire detection. For broken-GND function, it is recommended to tie PROG pin to VCC when not used.  $R_F$  is an optional pull-up resistor to  $V_F$ , to be used when disabling the device internal pull-up in memory.

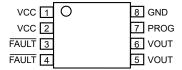

### PINOUT DIAGRAM AND PINOUT LIST

Figure 6: Pinout Diagram

### **Pinout List**

| Number | Name  | Description                                     |  |  |

|--------|-------|-------------------------------------------------|--|--|

| 1,2    | VCC   | Input power supply; also used for programming   |  |  |

| 3,4    | FAULT | Fault output; overcurrent, overtemperature      |  |  |

| 5,6    | VOUT  | Analog output signal; also used for programming |  |  |

| 7      | PROG  | Bidirectional programming pin                   |  |  |

| 8      | GND   | Ground pin                                      |  |  |

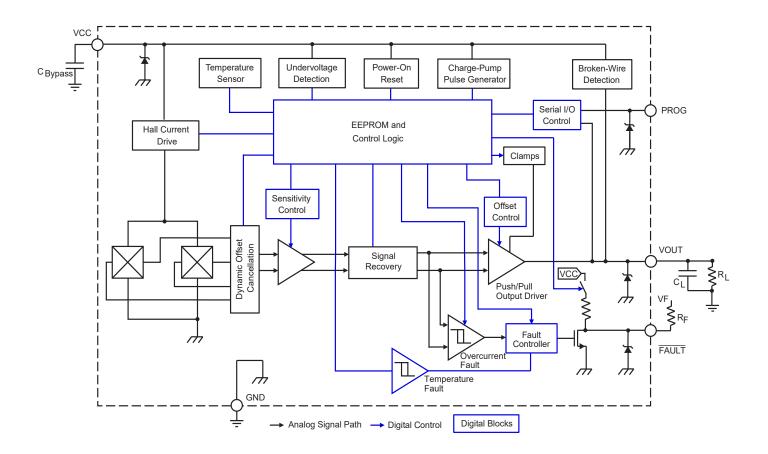

### **FUNCTIONAL BLOCK DIAGRAM**

Figure 7: Functional Block Diagram

# Coreless, High Precision, Hall-Effect Current Sensor IC with Common-Mode Field Rejection, Overcurrent and Overtemperature Detection

### $\textbf{COMMON OPERATING CHARACTERISTICS:} \ \ \text{Valid through full range of T}_{A} \ \text{and V}_{CC}, \ C_{BYPASS} = 100 \ \text{nF, unless otherwise specified}$

| Characteristic                            | Symbol                 | Test Conditions                                                                                                                                                                                         | Min. | Тур. | Max.                                                                                                   | Unit |

|-------------------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|--------------------------------------------------------------------------------------------------------|------|

| ELECTRICAL CHARACTERIS                    | TICS                   |                                                                                                                                                                                                         |      |      | ,                                                                                                      |      |

| O Valla                                   | .,                     | 5 V nominal supply voltage variant                                                                                                                                                                      | 4.5  | 5    | 5.5                                                                                                    | V    |

| Supply Voltage                            | V <sub>CC</sub>        | 3.3 V nominal supply voltage variant                                                                                                                                                                    | 3    | 3.3  | 5.5<br>3 3.6<br>.5 21<br>.5 18<br>.5 19<br>.5 14<br>0 -<br>0 -<br>9 7.2<br>6.25<br>0 -<br>0 -<br>1 4.3 | V    |

|                                           |                        | 5 V nominal supply voltage variant;<br>V <sub>CC</sub> (min) ≤ V <sub>CC</sub> ≤ V <sub>CC</sub> (max), no load on output                                                                               | -    | 16.5 | 21                                                                                                     | mA   |

| Supply Current                            |                        | 5 V nominal supply voltage variant;<br>low-power mode, no load on output                                                                                                                                | _    | 13.5 | 18                                                                                                     | mA   |

| Supply Current                            | Icc                    | 3.3 V nominal supply voltage variant; $V_{CC}(min) \le V_{CC} \le V_{CC}(max)$ , no load on output                                                                                                      | ı    | 14.5 | 19                                                                                                     | mA   |

|                                           |                        | 3.3 V nominal supply voltage variant; low-power mode, no load on output                                                                                                                                 | -    | 10.5 | 14                                                                                                     | mA   |

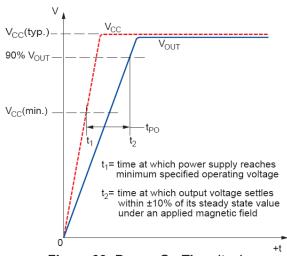

| Power-On Time                             | t <sub>PO</sub>        | $T_A = 25$ °C, $C_L$ (of test probe) = 10 pF, $C_{BYPASS}$ = open                                                                                                                                       | _    | 70   | _                                                                                                      | μs   |

| Temperature Compensation Power-On Time    | t <sub>TC</sub>        | Time after power-on time ( $t_{PO}$ ) required to obtain valid temperature-compensated output; $T_A = 150^{\circ}C$ , $C_{BYPASS} = open$ , $C_L = 1 nF$                                                | -    | 45   | _                                                                                                      | μs   |

| Fault Power-On Time                       | t <sub>PO(FAULT)</sub> | Time from when V <sub>CC</sub> > V <sub>UVLOD</sub> to when OCF reacts to overcurrent event                                                                                                             | ı    | 270  | _                                                                                                      | μs   |

|                                           | V <sub>OVDE</sub>      | T <sub>A</sub> = 25°C, V <sub>CC</sub> rising and device function disabled                                                                                                                              | 6.35 | 6.9  | 7.2                                                                                                    | V    |

| Overvoltage Detection Threshold           | V <sub>OVDD</sub>      | T <sub>A</sub> = 25°C, V <sub>CC</sub> falling and device function enabled                                                                                                                              | 5.75 | 6    | 6.25                                                                                                   | V    |

|                                           | V <sub>OVHYS</sub>     | T <sub>A</sub> = 25°C                                                                                                                                                                                   | _    | 450  | _                                                                                                      | mV   |

| OVD Enable/Disable Delay Time             | t <sub>OVDE</sub>      | T <sub>A</sub> = 25°C, C <sub>BYPASS</sub> = open, C <sub>L</sub> = 1 nF                                                                                                                                | _    | 60   | _                                                                                                      | μs   |

| OVD Enable/Disable Delay Time             | t <sub>OVDD</sub>      | T <sub>A</sub> = 25°C, C <sub>BYPASS</sub> = open, C <sub>L</sub> = 1 nF                                                                                                                                | _    | 3    | _                                                                                                      | μs   |

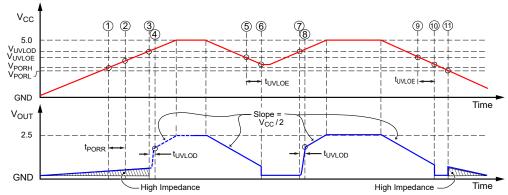

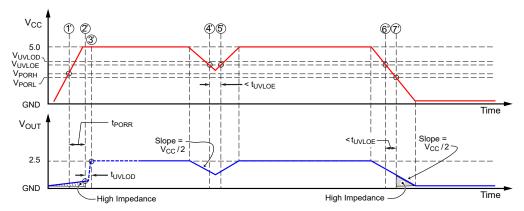

| Undervoltage Lockout (UVLO)               | V <sub>UVLOD</sub>     | V <sub>CC</sub> rising, 5 V variant only                                                                                                                                                                | _    | 4.1  | 4.3                                                                                                    | V    |

| Threshold                                 | V <sub>UVLOE</sub>     | V <sub>CC</sub> falling, 5 V variant only                                                                                                                                                               | 3.45 | 3.75 | 5.5<br>3.6<br>5 21<br>5 18<br>5 19<br>5 14<br>                                                         | V    |

| Undervoltage Lockout (UVLO)<br>Hysteresis | V <sub>UVLO(HYS)</sub> | 5 V variant only                                                                                                                                                                                        | -    | 450  | _                                                                                                      | mV   |

| UVD Enable/Disable                        | t <sub>UVLOE</sub>     | Time measured from falling $V_{CC} < V_{UVLOE}$ to UVLO enabled; $T_A = 25^{\circ}C$ , $C_{BYPASS} = open$ , $C_L = 1$ nF                                                                               | _    | 65   | _                                                                                                      | μs   |

| Delay Time                                | t <sub>UVLOD</sub>     | Time measured from rising $V_{CC} > V_{UVLOD}$ to UVLO disabled; $T_A$ = 25°C, $C_{BYPASS}$ = open, $C_L$ = 1 nF                                                                                        | -    | 8    | _                                                                                                      | μs   |

| Power On Reset Veltage                    | V <sub>PORH</sub>      | V <sub>CC</sub> rising                                                                                                                                                                                  | 2.7  | 2.9  | 3                                                                                                      | V    |

| Power-On Reset Voltage                    | V <sub>PORL</sub>      | V <sub>CC</sub> falling                                                                                                                                                                                 | 2.5  | 2.7  | 2.9                                                                                                    | V    |

| Power-On Reset Hysteresis                 | V <sub>HYS(POR)</sub>  |                                                                                                                                                                                                         | 50   | 150  | _                                                                                                      | mV   |

| Power-On Reset Release Time               | t <sub>PORR</sub>      | Time $V_{CC}$ must be held above $V_{PORH}$ to start counting for $t_{UVLOD}$ after $V_{CC} > V_{UVLOD}$ and transition from high impedance to regular operation; $T_A = 25^{\circ}C$ , $V_{CC}$ rising | -    | 65   | _                                                                                                      | μs   |

| Internal Bandwidth <sup>[1]</sup>         | BWi                    | -3 dB, C <sub>L</sub> = 1 nF, T <sub>A</sub> = 25°C                                                                                                                                                     | _    | 250  | _                                                                                                      | kHz  |

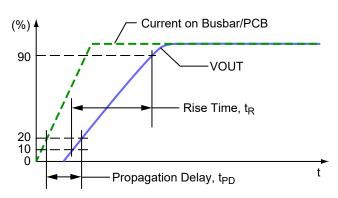

| Rise Time [1]                             | t <sub>r</sub>         | T <sub>A</sub> = 25°C, C <sub>L</sub> = 1 nF, 1 V step on output,<br>BW <sub>i</sub> = 250 kHz                                                                                                          | -    | 2.4  | _                                                                                                      | μs   |

Continued on the next page...

# Coreless, High Precision, Hall-Effect Current Sensor IC with Common-Mode Field Rejection, Overcurrent and Overtemperature Detection

## COMMON OPERATING CHARACTERISTICS (continued): Valid through full range of $T_A$ and $V_{CC}$ , $C_{BYPASS}$ = 100 nF, unless otherwise specified

| Characteristic                       | Symbol                 | Test Conditions                                                                                | Min.                  | Тур.     | Max.                                                                                             | Unit         |

|--------------------------------------|------------------------|------------------------------------------------------------------------------------------------|-----------------------|----------|--------------------------------------------------------------------------------------------------|--------------|

| Propagation Delay [1]                | t <sub>PD</sub>        | T <sub>A</sub> = 25°C, C <sub>L</sub> = 1 nF,<br>1 V step on output, BW <sub>i</sub> = 250 kHz | -                     | 1.1      | _                                                                                                | μs           |

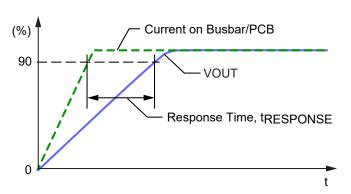

| Response Time [1]                    | t <sub>RESPONSE</sub>  | T <sub>A</sub> = 25°C, C <sub>L</sub> = 1 nF,<br>1 V step on output, BW <sub>i</sub> = 250 kHz | -                     | 1.6      | _                                                                                                | μs           |

| DC Output Impedance                  | R <sub>OUT</sub>       |                                                                                                | _                     | < 1      | _                                                                                                | Ω            |

| Output Load Resistance               | R <sub>L</sub>         | VOUT to GND                                                                                    | 4.7                   | 10       | _                                                                                                | kΩ           |

| Output Load Capacitance              | C <sub>L</sub>         | VOUT to GND                                                                                    | _                     | 1        | 10                                                                                               | nF           |

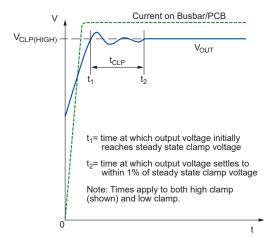

| Delay to Clamp                       | t <sub>CLP</sub>       | T <sub>A</sub> = 25°C; C <sub>L</sub> = 1 nF; Step from 75% output range to 150%               | _                     | 5        | _                                                                                                | μs           |

|                                      |                        | Full-scale output, 5 V variant, bidirectional                                                  | _                     | ±2       | _                                                                                                | V            |

| Output Full-Scale Range              | V <sub>OUT(FSR)</sub>  | Full-scale output, 3.3 V variant, bidirectional                                                | -                     | ±1.32    | _                                                                                                | V            |

|                                      |                        | Full-scale output, 5 V variant, unidirectional                                                 | _                     | 4        | _                                                                                                | V            |

|                                      | V <sub>CLP(HIGH)</sub> | $V_{CC}$ = 5 V, $R_{L(PULLDOWN)}$ = 10 kΩ to GND                                               | 4.48                  | _        | 4.75                                                                                             | V            |

| Outs. 4 ) / alta ma Olamon [2]       |                        | $V_{CC}$ = 3.3 V, $R_{L(PULLDOWN)}$ = 10 kΩ to GND                                             | 2.94                  | _        | 3.18                                                                                             | V            |

| Output Voltage Clamp <sup>[2]</sup>  |                        | $V_{CC}$ = 5 V, $R_{L(PULLUP)}$ = 10 kΩ to VCC                                                 | 0.25                  | _        | 0.5                                                                                              | V            |

|                                      | V <sub>CLP(LOW)</sub>  | $V_{CC}$ = 3.3 V, $R_{L(PULLUP)}$ = 10 kΩ to VCC                                               | 0.15                  | _        | 0.33                                                                                             | V            |

| Output Saturation Voltage            | V <sub>SAT(HIGH)</sub> | R <sub>L(PULLDOWN)</sub> = 10 kΩ to GND                                                        | V <sub>CC</sub> - 0.2 | -        | _                                                                                                | ٧            |

| Output Outaration Voltage            | V <sub>SAT(LOW)</sub>  | $R_{L(PULLUP)} = 10 \text{ k}\Omega \text{ to VCC}$                                            | _                     | -        | 1.1 -  1.6 -  1.6 -  1.0 -  1 10 -  1 10  5 -  ±2 -  ±1.32 -  4 -  - 4.75  - 3.18  - 0.5  - 0.33 | mV           |

| Broken Wire Voltage                  | V <sub>BRK(High)</sub> | $R_{L(PULLUP)} = 10 \text{ k}\Omega \text{ to VCC}$                                            | V <sub>CC</sub> – 0.1 | $V_{CC}$ | V <sub>CC</sub>                                                                                  | V            |

| Broken wire voltage                  | V <sub>BRK(Low)</sub>  | $R_{L(PULLDOWN)} = 10 \text{ k}\Omega \text{ to GND}$                                          | 0                     | 0        | 100                                                                                              | mV           |

| ERROR COMPONENTS                     |                        |                                                                                                |                       |          |                                                                                                  |              |

| Clamp Ratiometry Error               | Rat <sub>ERRCLP</sub>  | V <sub>CC</sub> = ±3% variation of nominal supply voltage                                      | _                     | < ±0.5   | _                                                                                                | %            |

| Common Mode Field<br>Rejection Ratio | CMFRR                  | Measured at 100 G uniform magnetic field                                                       | -                     | 40       | _                                                                                                | dB           |

| Noise Density                        | D                      | Normal power mode, 5 V/3.3 V variant,<br>T <sub>A</sub> = 25°C, C <sub>L</sub> = 1 nF          | -                     | 0.9      | -                                                                                                | mG<br>/√(Hz) |

| Noise Density                        | B <sub>ND</sub>        | Low-power mode, 5 V/3.3 V variant,<br>T <sub>A</sub> = 25°C, C <sub>L</sub> = 1 nF             | _                     | 1.2      | _                                                                                                | mG<br>/√(Hz) |

<sup>[1]</sup> Timing specified does not include potential effect of skin effect on conductor; value depends on busbar/PCB design.

<sup>[2]</sup> Clamps are disabled by default.

# Coreless, High Precision, Hall-Effect Current Sensor IC with Common-Mode Field Rejection, Overcurrent and Overtemperature Detection

### **FAULT CHARACTERISTICS**

| Characteristic                                            | Symbol                  | Test Conditions                                                                                                                                                                                                                                       | Min.       | Тур.            | Max.            | Unit    |

|-----------------------------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------|-----------------|---------|

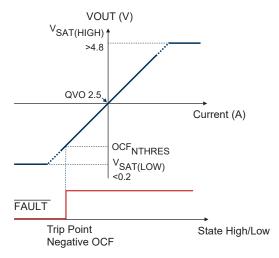

| Positive Field Fault                                      | 0050                    | Programmable using OCF positive threshold bits. In percent of full-scale positive output (2.5 to 4.5 V) on bidirectional variant.                                                                                                                     | 50         | _               | 200             | % FS(+) |

| Switch Point Range [1]                                    | OCFP <sub>THRESH</sub>  | Programmable using OCF positive threshold bits. In percent of full-scale output (0.5 to 4.5 V) on unidirectional variant.                                                                                                                             | 50         | _               |                 | % FS    |

| Negative Field Fault<br>Switch Point Range <sup>[1]</sup> | OCFN <sub>THRESH</sub>  | Programmable using OCF negative threshold bits. In percent of full-scale negative output (2 V typical, 2.5 to 0.5 V) on bidirectional variant                                                                                                         | 50         | _               | 200             | % FS(-) |

| Overcurrent Fault<br>Switch Point Step Size               | OCF <sub>STEP</sub>     | Overcurrent fault threshold programming step size                                                                                                                                                                                                     | -          | 1.6             | _               | % FS    |

| Overcurrent Fault Accuracy                                | OCF <sub>ACC</sub>      | Overcurrent fault threshold accuracy through full range of T <sub>A</sub>                                                                                                                                                                             | <b>–</b> 5 | ±2              | +5              | % FS    |

| Overcurrent Fault Response Time                           | t <sub>OCF</sub>        | $\begin{split} R_{F(PULLUP)} &= 10 \text{ k}\Omega \text{ from FAULT to V}_F, \\ \text{VOUT step from V}_{OUT(Q)} &\text{ to V}_{OUT} = (V_{OUT(Q)} + \\ \text{OCF}_{PTHRESH} [V]); BW_i = 250 \text{ kHz}, \\ \text{OCF qualifier} &= 0 \end{split}$ | -          | 2.5             | -               | μs      |

| Overtemperature Fault Sampling Rate                       | OTF <sub>S</sub>        | Rate at which the temperature is sampled                                                                                                                                                                                                              | _          | 8               | _               | ms      |

|                                                           | t <sub>C(F)</sub>       | Time to release FAULT pin (return to $V_F$ ) when fault condition is no longer present. $R_F$ = 10 k $\Omega$ , external 100 pF from FAULT to VCC                                                                                                     | _          | 8               | _               | μs      |

| Fault Clear Time                                          |                         | Time to release FAULT pin (return to V <sub>CC</sub> ) when fault condition is no longer present. Internal fault pull-up enabled                                                                                                                      | -          | 15              | _               | μs      |

| Fault Jitter                                              | OCF <sub>JITT</sub>     | T <sub>A</sub> = 25°C, 1 sigma                                                                                                                                                                                                                        | _          | 100             | _               | ns      |

|                                                           |                         | Hysteresis in percent of trip level, T <sub>A</sub> = 25°C, OCF_HYST = 0                                                                                                                                                                              | _          | 11              | _               | %       |

| Overcurrent Fault Hysteresis                              |                         | Hysteresis in percent of trip level, T <sub>A</sub> = 25°C, OCF_HYST = 1                                                                                                                                                                              | -          | 22              | _               | %       |

| Level Range [1]                                           | OCF <sub>HYST</sub>     | Hysteresis in percent of trip level, T <sub>A</sub> = 25°C, OCF_HYST = 2                                                                                                                                                                              | _          | 45              | _               | %       |

|                                                           |                         | Hysteresis in percent of trip level, T <sub>A</sub> = 25°C, OCF_HYST = 3                                                                                                                                                                              | _          | 75              | _               | %       |

| Overtemperature Fault Accuracy [1]                        | OTF <sub>ACC</sub>      |                                                                                                                                                                                                                                                       | -10        | ±3              | +10             | °C      |

| Overtemperature Fault Threshold Range [1]                 | OTF <sub>THRESH</sub>   |                                                                                                                                                                                                                                                       | 80         | 160             | 165             | °C      |

| Overtemperature Fault Step size                           |                         |                                                                                                                                                                                                                                                       | _          | 7               | _               | °C      |

| Overtemperature Fault Hysteresis [1]                      | OTF <sub>HYST</sub>     | Overtemperature fault fixed hysteresis value                                                                                                                                                                                                          | 10         | 15              | 20              | °C      |

| FAULT Pin Low Output Voltage                              | V <sub>FAULT</sub>      | $R_{F(PULLUP)}$ = 4.7 kΩ from FAULT to VCC                                                                                                                                                                                                            | _          | _               | 0.4             | V       |

| FAULT Pin Leakage Current                                 | I <sub>FLeak</sub>      | $R_{F(PULLUP)}$ = 4.7 k $\Omega$ from FAULT to VCC                                                                                                                                                                                                    | _          | _               | 1.3             | μΑ      |

| External Pull-Up Supply Voltage [1]                       | V <sub>F(PULLUP)</sub>  |                                                                                                                                                                                                                                                       | 1.65       | V <sub>CC</sub> | V <sub>CC</sub> | V       |

| External FAULT Pull-Up Resistor [1]                       | R <sub>F(PULLUP)</sub>  |                                                                                                                                                                                                                                                       | 4.7        | _               | 500             | kΩ      |

| External FAULT Capacitance [1]                            | C <sub>F</sub>          |                                                                                                                                                                                                                                                       | _          | _               | 10              | nF      |

| Internal FAULT Pull-Up Resistor                           | R <sub>IF(PULLUP)</sub> | Internal pull-up to V <sub>CC</sub> ; set FaultR_dis bit to 1 in EEPROM to disable.                                                                                                                                                                   | _          | 10              | _               | kΩ      |

$<sup>\</sup>ensuremath{^{[1]}}$  Limits guaranteed by design and characterization data, not tested in production.

# Coreless, High Precision, Hall-Effect Current Sensor IC with Common-Mode Field Rejection, Overcurrent and Overtemperature Detection

### -005B5 PERFORMANCE CHARACTERISTICS: Valid over full range of $T_A$ and $V_{CC}$ = 5 V, unless otherwise specified

| Characteristic                                                       | Symbol                  | Test Conditions                                                                              | Min.       | Тур.  | Max.  | Unit              |

|----------------------------------------------------------------------|-------------------------|----------------------------------------------------------------------------------------------|------------|-------|-------|-------------------|

| NOMINAL PERFORMANCE                                                  | `                       |                                                                                              |            |       | •     |                   |

| Differential Magnetic Range                                          | B <sub>DIFF</sub>       | Corresponding full-scale magnetic range based on typical sensitivity                         | -400       | _     | 400   | G                 |

| Initial Factory-Programmed Sensitivity                               | Sens                    | Factory-programmed sensitivity; T <sub>A</sub> = 25°C                                        | 4.925      | 5     | 5.075 | mV/G              |

| Initial Quiescent Output Voltage                                     | V <sub>OUT(Q)</sub>     | Factory-programmed quiescent output voltage; T <sub>A</sub> = 25°C                           | 2.495      | 2.5   | 2.505 | V                 |

| Noise [1]                                                            | V <sub>N</sub>          | T <sub>A</sub> = 25°C, C <sub>L</sub> = 1 nF, BW <sub>i</sub> = 250 kHz, initial sensitivity | _          | 2.8   | _     | mV <sub>RMS</sub> |

| Nonlinearity                                                         | E <sub>LIN</sub>        | Tested up to full-scale output                                                               | -0.55      | ±0.15 | 0.55  | %                 |

| SENSITIVITY ERROR                                                    | `                       |                                                                                              |            |       |       |                   |

| Sens Ratiometry Error [2]                                            | Rat <sub>ErrSens</sub>  | V <sub>CC</sub> = ±3% variation of nominal supply voltage                                    | -0.75      | ±0.25 | 0.75  | %                 |

| O was the Dark O was T                                               | A O                     | T <sub>A</sub> = 25°C to 150°C,<br>up to ±40% of sensitivity change                          | -1.5       | ±1    | 1.5   | %                 |

| Sensitivity Drift Over Temperature                                   | ΔSens <sub>TC</sub>     | T <sub>A</sub> = -40°C to 25°C,<br>up to ±40% of sensitivity change                          | -1.5       | ±1    | 1.5   | %                 |

| QUIESCENT VOLTAGE OUTPUT ER                                          | ROR                     |                                                                                              |            |       | •     |                   |

| QVO Ratiometry Error [2]                                             | V <sub>RatErrQVO</sub>  | V <sub>CC</sub> = ±3% variation of nominal supply voltage                                    | <b>–</b> 5 | ±2    | 5     | mV                |

| Quiescent Voltage Output                                             | V                       | T <sub>A</sub> = 25°C to 150°C,<br>up to ±40% of sensitivity change                          | <b>–</b> 5 | ±3    | 5     | mV                |

| Temperature Error                                                    | V <sub>OUT(Q)TC</sub>   | T <sub>A</sub> = -40°C to 25°C,<br>up to ±40% of sensitivity change                          | <b>–</b> 5 | ±3    | 5     | mV                |

| LIFETIME DRIFT CHARACTERISTIC                                        | CS [3]                  |                                                                                              |            |       |       |                   |

| QVO Lifetime Drift                                                   | V <sub>OUT(Q)LIFE</sub> | Initial sensitivity                                                                          | _          | ±4.7  | -     | mV                |

| Sens Lifetime Drift                                                  | Sens <sub>LIFE</sub>    | Initial sensitivity                                                                          | _          | ±0.75 | _     | %                 |

| Additional QVO Temperature Error<br>Relative to 25°C Due to Lifetime |                         | $T_A = -40$ °C to 150°C, initial sensitivity                                                 | _          | 1.1   | _     | mV                |

| Additional Sensitivity Error<br>Relative to 25°C Due to Lifetime     |                         | $T_A = -40$ °C to 150°C, initial sensitivity                                                 |            | 0.1   | _     | %                 |

<sup>[1]</sup> Noise scales with sensitivity.

<sup>[2]</sup> For lower V<sub>CC</sub> variations than test conditions, ratiometry error scales linearly with V<sub>CC</sub>; e.g., ±1.5% variations on V<sub>CC</sub> instead of ±3% leads to Rat<sub>ErrSens</sub> and V<sub>RatErrQVO</sub> to be divided by 2.

<sup>[3]</sup> Lifetime drift characteristics are based on the AEC-Q100 qualification results from zero-hour reads. Typical values are the worst-case observed drift, ±3 sigma, during AEC-Q100 qualification from any of the -40°C, 25°C, or 150°C temperatures.

# Coreless, High Precision, Hall-Effect Current Sensor IC with Common-Mode Field Rejection, Overcurrent and Overtemperature Detection

## -010B5 PERFORMANCE CHARACTERISTICS: Valid over full range of $T_A$ and $V_{CC}$ = 5 V, unless otherwise specified

| Characteristic                                                       | Symbol                  | Test Conditions                                                                              | Min.       | Тур.  | Max.  | Unit              |

|----------------------------------------------------------------------|-------------------------|----------------------------------------------------------------------------------------------|------------|-------|-------|-------------------|

| NOMINAL PERFORMANCE                                                  | `                       |                                                                                              |            |       | •     |                   |

| Differential Magnetic Range                                          | B <sub>DIFF</sub>       | Corresponding full-scale magnetic range based on typical sensitivity                         | -200       | _     | 200   | G                 |

| Initial Factory-Programmed Sensitivity                               | Sens                    | Factory-programmed sensitivity; T <sub>A</sub> = 25°C                                        | 9.85       | 10    | 10.15 | mV/G              |

| Initial Quiescent Output Voltage                                     | V <sub>OUT(Q)</sub>     | Factory-programmed quiescent output voltage; T <sub>A</sub> = 25°C                           | 2.495      | 2.5   | 2.505 | V                 |

| Noise [1]                                                            | V <sub>N</sub>          | T <sub>A</sub> = 25°C, C <sub>L</sub> = 1 nF, BW <sub>i</sub> = 250 kHz, initial sensitivity | _          | 5     | _     | mV <sub>RMS</sub> |

| Nonlinearity                                                         | E <sub>LIN</sub>        | Tested up to full-scale output                                                               | -0.55      | ±0.15 | 0.55  | %                 |

| SENSITIVITY ERROR                                                    | `                       |                                                                                              |            |       |       |                   |

| Sens Ratiometry Error [2]                                            | Rat <sub>ErrSens</sub>  | V <sub>CC</sub> = ±3% variation of nominal supply voltage                                    | -0.75      | ±0.25 | 0.75  | %                 |

| O                                                                    | A O                     | T <sub>A</sub> = 25°C to 150°C,<br>up to ±40% of sensitivity change                          | -1.5       | ±1    | 1.5   | %                 |

| Sensitivity Drift Over Temperature                                   | ΔSens <sub>TC</sub>     | T <sub>A</sub> = -40°C to 25°C,<br>up to ±40% of sensitivity change                          | -1.5       | ±1    | 1.5   | %                 |

| QUIESCENT VOLTAGE OUTPUT ER                                          | ROR                     |                                                                                              |            |       | •     |                   |

| QVO Ratiometry Error [2]                                             | V <sub>RatErrQVO</sub>  | V <sub>CC</sub> = ±3% variation of nominal supply voltage                                    | <b>–</b> 5 | ±2    | 5     | mV                |

| Quiescent Voltage Output                                             | V                       | T <sub>A</sub> = 25°C to 150°C,<br>up to ±40% of sensitivity change                          | <b>–</b> 5 | ±3    | 5     | mV                |

| Temperature Error                                                    | V <sub>OUT(Q)TC</sub>   | T <sub>A</sub> = -40°C to 25°C,<br>up to ±40% of sensitivity change                          | <b>–</b> 5 | ±3    | 5     | mV                |

| LIFETIME DRIFT CHARACTERISTIC                                        | CS [3]                  |                                                                                              |            |       |       |                   |

| QVO Lifetime Drift                                                   | V <sub>OUT(Q)LIFE</sub> | Initial sensitivity                                                                          | _          | ±4.7  | _     | mV                |

| Sens Lifetime Drift                                                  | Sens <sub>LIFE</sub>    | Initial sensitivity                                                                          | _          | ±0.75 | _     | %                 |

| Additional QVO Temperature Error<br>Relative to 25°C Due to Lifetime |                         | $T_A = -40$ °C to 150°C, initial sensitivity                                                 |            | 1.1   | _     | mV                |

| Additional Sensitivity Error<br>Relative to 25°C Due to Lifetime     |                         | $T_A = -40$ °C to 150°C, initial sensitivity                                                 |            | 0.1   | _     | %                 |

<sup>[1]</sup> Noise scales with sensitivity.

<sup>[2]</sup> For lower  $V_{CC}$  variations than test conditions, ratiometry error scales linearly with  $V_{CC}$ ; e.g.,  $\pm 1.5\%$  variations on  $V_{CC}$  instead of  $\pm 3\%$  leads to Rat<sub>ErrSens</sub> and  $V_{RatErrQVO}$  to be divided by 2.

<sup>[3]</sup> Lifetime drift characteristics are based on the AEC-Q100 qualification results from zero-hour reads. Typical values are the worst-case observed drift, ±3 sigma, during AEC-Q100 qualification from any of the -40°C, 25°C, or 150°C temperatures.

# Coreless, High Precision, Hall-Effect Current Sensor IC with Common-Mode Field Rejection, Overcurrent and Overtemperature Detection

### **-020B5 PERFORMANCE CHARACTERISTICS:** Valid over full range of $T_A$ and $V_{CC}$ = 5 V, unless otherwise specified

| Characteristic                                                       | Symbol                  | Test Conditions                                                                             | Min.   | Тур.  | Max.   | Unit              |

|----------------------------------------------------------------------|-------------------------|---------------------------------------------------------------------------------------------|--------|-------|--------|-------------------|

| NOMINAL PERFORMANCE                                                  | •                       |                                                                                             |        |       | •      |                   |

| Differential Magnetic Range                                          | B <sub>DIFF</sub>       | Corresponding full-scale magnetic range based on typical sensitivity                        | -100   | _     | 100    | G                 |

| Initial Factory-Programmed Sensitivity                               | Sens                    | Factory-programmed sensitivity; T <sub>A</sub> = 25°C                                       | 19.7   | 20    | 20.3   | mV/G              |

| Initial Quiescent Output Voltage                                     | V <sub>OUT(Q)</sub>     | Factory-programmed quiescent output voltage; T <sub>A</sub> = 25°C                          | 2.4925 | 2.5   | 2.5075 | V                 |

| Noise [1]                                                            | V <sub>N</sub>          | $T_A = 25^{\circ}\text{C}, C_L = 1 \text{ nF, BW}_i = 250 \text{ kHz,}$ initial sensitivity | _      | 10    | _      | mV <sub>RMS</sub> |

| Nonlinearity                                                         | E <sub>LIN</sub>        | Tested up to full-scale output                                                              | -0.55  | ±0.25 | 0.55   | %                 |

| SENSITIVITY ERROR                                                    |                         |                                                                                             |        |       |        |                   |

| Sens Ratiometry Error [2]                                            | Rat <sub>ErrSens</sub>  | V <sub>CC</sub> = ±3% variation of nominal supply voltage                                   | -1     | ±0.4  | 1      | %                 |

|                                                                      |                         | T <sub>A</sub> = 25°C to 150°C, initial sensitivity                                         | -1.5   | ±1    | 1.5    | %                 |

| Sanaitivity Drift Over Temperature                                   | ΔSens <sub>TC</sub>     | T <sub>A</sub> = -40°C to 25°C, initial sensitivity                                         | -1.5   | ±1    | 1.5    | %                 |

| Sensitivity Drift Over Temperature                                   |                         | T <sub>A</sub> = 25°C to 150°C, ±40% sensitivity change                                     | -1.6   | ±1    | 1.6    | %                 |

|                                                                      |                         | T <sub>A</sub> = -40°C to 25°C, ±40% sensitivity change                                     | -1.6   | ±1    | 1.6    | %                 |

| QUIESCENT VOLTAGE OUTPUT ER                                          | ROR                     |                                                                                             |        |       |        |                   |

| QVO Ratiometry Error [2]                                             | V <sub>RatErrQVO</sub>  | V <sub>CC</sub> = ±3% variation of nominal supply voltage                                   | -7.5   | ±3    | 7.5    | mV                |

|                                                                      |                         | T <sub>A</sub> = 25°C to 150°C, initial sensitivity                                         | -10    | ±4    | 10     | mV                |

| Quiescent Voltage Output                                             | .,                      | T <sub>A</sub> = -40°C to 25°C, initial sensitivity                                         | -10    | ±4    | 10     | mV                |

| Temperature Error                                                    | V <sub>OUT(Q)TC</sub>   | T <sub>A</sub> = 25°C to 150°C, ±40% sensitivity change                                     | -14    | ±4    | 14     | mV                |

|                                                                      |                         | T <sub>A</sub> = -40°C to 25°C, ±40% sensitivity change                                     | -14    | ±4    | 14     | mV                |

| LIFETIME DRIFT CHARACTERISTIC                                        | S [3]                   |                                                                                             |        |       |        |                   |

| QVO Lifetime Drift                                                   | V <sub>OUT(Q)LIFE</sub> | Initial sensitivity                                                                         | -      | ±10.2 | _      | mV                |

| Sens Lifetime Drift                                                  | Sens <sub>LIFE</sub>    | Initial sensitivity                                                                         | -      | ±1.1  | _      | %                 |

| Additional QVO Temperature Error<br>Relative to 25°C Due to Lifetime |                         | $T_A = -40$ °C to 150°C, initial sensitivity                                                | _      | 1     | _      | mV                |

| Additional Sensitivity Error<br>Relative to 25°C Due to Lifetime     |                         | $T_A = -40$ °C to 150°C, initial sensitivity                                                | _      | 0.1   | _      | %                 |

$<sup>\</sup>ensuremath{^{[1]}}$  Noise scales with sensitivity. Tested with initial sensitivity.

<sup>[2]</sup> For lower  $V_{CC}$  variations than test conditions, ratiometry error scales linearly with  $V_{CC}$ ; e.g.,  $\pm 1.5\%$  variations on  $V_{CC}$  instead of  $\pm 3\%$  leads to Rat<sub>ErrSens</sub> and  $V_{RatErrQVO}$  to be divided by 2.

<sup>[3]</sup> Lifetime drift characteristics are based on the AEC-Q100 qualification results from zero-hour reads. Typical values are the worst-case observed drift, ±3 sigma, during AEC-Q100 qualification from any of the -40°C, 25°C, or 150°C temperatures.

# Coreless, High Precision, Hall-Effect Current Sensor IC with Common-Mode Field Rejection, Overcurrent and Overtemperature Detection

### **-020U5 PERFORMANCE CHARACTERISTICS:** Valid over full range of $T_A$ and $V_{CC}$ = 5 V, unless otherwise specified

| Characteristic                                                    | Symbol                  | Test Conditions                                                                              | Min.  | Тур.  | Max. | Unit              |

|-------------------------------------------------------------------|-------------------------|----------------------------------------------------------------------------------------------|-------|-------|------|-------------------|

| NOMINAL PERFORMANCE                                               | ,                       |                                                                                              |       | ·     | •    |                   |

| Differential Magnetic Range                                       | B <sub>DIFF</sub>       | Corresponding full-scale magnetic range based on typical sensitivity                         | 0     | _     | 200  | G                 |

| Initial Factory-Programmed Sensitivity                            | Sens                    | Factory-programmed sensitivity; T <sub>A</sub> = 25°C                                        | 19.7  | 20    | 20.3 | mV/G              |

| Initial Quiescent Output Voltage                                  | V <sub>OUT(Q)</sub>     | Factory-programmed quiescent output voltage; T <sub>A</sub> = 25°C                           | 0.49  | 0.5   | 0.51 | V                 |

| Noise [1]                                                         | V <sub>N</sub>          | T <sub>A</sub> = 25°C, C <sub>L</sub> = 1 nF, BW <sub>i</sub> = 250 kHz, initial sensitivity | _     | 10    | _    | mV <sub>RMS</sub> |

| Nonlinearity                                                      | E <sub>LIN</sub>        | Tested up to full-scale output                                                               | -0.75 | ±0.25 | 0.75 | %                 |

| SENSITIVITY ERROR                                                 | `                       |                                                                                              |       |       |      |                   |

| Sens Ratiometry Error [2]                                         | Rat <sub>ErrSens</sub>  | V <sub>CC</sub> = ±3% variation of nominal supply voltage                                    | -1    | ±0.4  | 1    | %                 |

|                                                                   |                         | T <sub>A</sub> = 25°C to 150°C, initial sensitivity                                          | -1.5  | ±1    | 1.5  | %                 |

| Sensitivity Drift Over Temperature                                | ΔSens <sub>TC</sub>     | T <sub>A</sub> = -40°C to 25°C, initial sensitivity                                          | -1.5  | ±1    | 1.5  | %                 |

| Sensitivity Drift Over Temperature                                |                         | T <sub>A</sub> = 25°C to 150°C, ±40% sensitivity change                                      | -1.6  | ±1    | 1.6  | %                 |

|                                                                   |                         | T <sub>A</sub> = -40°C to 25°C, ±40% sensitivity change                                      | -1.6  | ±1    | 1.6  | %                 |

| QUIESCENT VOLTAGE OUTPUT ER                                       | ROR                     |                                                                                              |       |       |      |                   |

| QVO Ratiometry Error [2]                                          | V <sub>RatErrQVO</sub>  | V <sub>CC</sub> = ±3% variation of nominal supply voltage                                    | -10   | ±3    | 10   | mV                |

|                                                                   |                         | T <sub>A</sub> = 25°C to 150°C, initial sensitivity                                          | -10   | ±4    | 10   | mV                |

| Quiescent Voltage Output                                          |                         | T <sub>A</sub> = -40°C to 25°C, initial sensitivity                                          | -10   | ±4    | 10   | mV                |

| Temperature Error                                                 | V <sub>OUT(Q)TC</sub>   | T <sub>A</sub> = 25°C to 150°C, ±40% sensitivity change                                      | -14   | ±4    | 14   | mV                |

|                                                                   |                         | T <sub>A</sub> = -40°C to 25°C, ±40% sensitivity change                                      | -14   | ±4    | 14   | mV                |

| LIFETIME DRIFT CHARACTERISTIC                                     | S [3]                   |                                                                                              |       |       |      | -                 |

| QVO Lifetime Drift                                                | V <sub>OUT(Q)LIFE</sub> | Initial sensitivity                                                                          | _     | ±10.2 | _    | mV                |

| Sens Lifetime Drift                                               | Sens <sub>LIFE</sub>    | Initial sensitivity                                                                          | _     | ±1.1  | _    | %                 |

| Additional QVO Temperature Error Relative to 25°C Due to Lifetime |                         | $T_A = -40$ °C to 150°C, initial sensitivity                                                 | _     | 1     | _    | mV                |

| Additional Sensitivity Error<br>Relative to 25°C Due to Lifetime  |                         | $T_A = -40$ °C to 150°C, initial sensitivity                                                 | _     | 0.1   | _    | %                 |

<sup>[1]</sup> Noise scales with sensitivity.

<sup>[2]</sup> For lower V<sub>CC</sub> variations than test conditions, ratiometry error scales linearly with V<sub>CC</sub>; e.g.; ±1.5% variations on V<sub>CC</sub> instead of ±3% leads to Rat<sub>ErrSens</sub> and V<sub>RatErrQVO</sub> to be divided by 2.

<sup>[3]</sup> Lifetime drift characteristics are based on the AEC-Q100 qualification results from zero-hour reads. Typical values are the worst-case observed drift, ±3 sigma, during AEC-Q100 qualification from any of the -40°C, 25°C, or 150°C temperatures.

# Coreless, High Precision, Hall-Effect Current Sensor IC with Common-Mode Field Rejection, Overcurrent and Overtemperature Detection

### -010B3 PERFORMANCE CHARACTERISTICS: Valid over full range of $T_A$ and $V_{CC}$ = 3.3 V, unless otherwise specified

| Characteristic                                                       | Symbol                  | Test Conditions                                                                              | Min.       | Тур.  | Max.  | Unit              |

|----------------------------------------------------------------------|-------------------------|----------------------------------------------------------------------------------------------|------------|-------|-------|-------------------|

| NOMINAL PERFORMANCE                                                  | *                       |                                                                                              |            |       |       |                   |

| Differential Magnetic Range                                          | B <sub>DIFF</sub>       | Corresponding full-scale magnetic range based on typical sensitivity                         | -132       | _     | 132   | G                 |

| Initial Factory-Programmed Sensitivity                               | Sens                    | Factory-programmed sensitivity; T <sub>A</sub> = 25°C                                        | 9.85       | 10    | 10.15 | mV/G              |

| Initial Quiescent Output Voltage                                     | V <sub>OUT(Q)</sub>     | Factory-programmed quiescent output voltage; T <sub>A</sub> = 25°C                           | 1.645      | 1.65  | 1.655 | V                 |

| Noise [1]                                                            | V <sub>N</sub>          | T <sub>A</sub> = 25°C, C <sub>L</sub> = 1 nF, BW <sub>i</sub> = 250 kHz, initial sensitivity | _          | 6.5   | _     | mV <sub>RMS</sub> |

| Nonlinearity                                                         | E <sub>LIN</sub>        | Tested up to full-scale output                                                               | -0.55      | ±0.15 | 0.55  | %                 |

| SENSITIVITY ERROR                                                    |                         |                                                                                              |            |       |       |                   |

| Sens Ratiometry Error [2]                                            | Rat <sub>ErrSens</sub>  | V <sub>CC</sub> = ±3% variation of nominal supply voltage                                    | -0.75      | ±0.25 | 0.75  | %                 |

|                                                                      | ACono                   | T <sub>A</sub> = 25°C to 150°C,<br>up to ±40% of sensitivity change                          | -1.5       | ±1    | 1.5   | %                 |

| Sensitivity Drift Over Temperature                                   | ΔSens <sub>TC</sub>     | T <sub>A</sub> = -40°C to 25°C,<br>up to ±40% of sensitivity change                          | -1.5       | ±1    | 1.5   | %                 |

| QUIESCENT VOLTAGE OUTPUT ER                                          | ROR                     |                                                                                              |            |       |       |                   |

| QVO Ratiometry Error [2]                                             | V <sub>RatErrQVO</sub>  | V <sub>CC</sub> = ±3% variation of nominal supply voltage                                    | -10        | ±2    | 10    | mV                |

| Quiescent Voltage Output                                             |                         | T <sub>A</sub> = 25°C to 150°C,<br>up to ±40% of sensitivity change                          | -5         | ±3    | 5     | mV                |

| Temperature Error                                                    | V <sub>OUT(Q)TC</sub>   | T <sub>A</sub> = -40°C to 25°C,<br>up to ±40% of sensitivity change                          | <b>–</b> 5 | ±3    | 5     | mV                |

| LIFETIME DRIFT CHARACTERISTIC                                        | CS [3]                  |                                                                                              |            |       |       |                   |

| QVO Lifetime Drift                                                   | V <sub>OUT(Q)LIFE</sub> | Initial sensitivity                                                                          | -          | ±9.5  | _     | mV                |

| Sens Lifetime Drift                                                  | Sens <sub>LIFE</sub>    | Initial sensitivity                                                                          | _          | ±1.4  | _     | %                 |

| Additional QVO Temperature Error<br>Relative to 25°C Due to Lifetime |                         | $T_A = -40$ °C to 150°C, initial sensitivity                                                 |            | 1     | _     | mV                |

| Additional Sensitivity Error<br>Relative to 25°C Due to Lifetime     |                         | $T_A = -40$ °C to 150°C, initial sensitivity                                                 | _          | 0.1   | -     | %                 |

<sup>[1]</sup> Noise scales with sensitivity. Tested with initial sensitivity.

<sup>[2]</sup> For lower V<sub>CC</sub> variations than test conditions, ratiometry error scales linearly with V<sub>CC</sub>; e.g., ±1.5% variations on V<sub>CC</sub> instead of ±3% leads to Rat<sub>ErrSens</sub> and V<sub>RatErrQVO</sub> to be divided by 2.

<sup>[3]</sup> Lifetime drift characteristics are based on the AEC-Q100 qualification results from zero-hour reads. Typical values are the worst-case observed mean ±3 sigma drift during AEC-Q100 qualification from any of the -40°C, 25°C, or 150°C temperatures.

### **FUNCTIONAL DESCRIPTION**

### **Principle of Operation**

When AC or DC current flows through a PCB copper trace or a busbar, as shown in Figure 8, the ACS37610 device senses the magnetic-field difference induced between its two Hall elements, HL and HR, represented by the field components  $B_L$  and  $B_R$ . The device output is proportional to the differential field sensed,  $B_{\rm diff}$ , which is proportional to the applied current. The relationship between applied current and generated field is described as:

$$B_{diff} = CF \times I$$

,

where  $B_{\rm diff}$  is the differential field (HL – HR), CF is the differential coupling factor (G/A), and I is the current through the busbar/PCB trace. As can be observed from this equation, the differential coupling factor (CF) is the linear relationship between the differential field sensed and the current flowing in the conductor. Different busbar shapes can be used to best answer application requirements; for more details, refer to the Typical Application—PCB Sensing section.

Figure 8: Current-Sensing Principle

# Coreless, High Precision, Hall-Effect Current Sensor IC with Common-Mode Field Rejection, Overcurrent and Overtemperature Detection

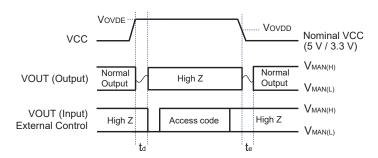

### **Device Diagnostics**

The ACS37610 device offers multiple built-in diagnostics which effects and programmability are described in Table 1.

**Table 1: Device Diagnostics Table**

| Diagnostic                                 | Effect on V <sub>OUT</sub>                                                                                                                                                                           | Effect on FAULT                                                                                                                            | Note                                                                                                                                                                                                                         |

|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Overvoltage Detection                      | If V <sub>CC</sub> is higher than V <sub>OVDE</sub> for more than t <sub>OVDE</sub> (64 µs typ.), V <sub>OUT</sub> goes to the high-impedance state.                                                 | FAULT remains in the high-impedance state (or goes to high-impedance in case of FAULT pin asserted), pulled-up to V <sub>F(PULLUP)</sub>   | NOTE 1: When $V_{OUT}$ goes to the high-impedance state, the voltage on $V_{OUT}$ is pulled down to GND or pulled up to $V_{CC}$ , depending on application wiring. If the COM_LOCK bit is set, the OVD feature is disabled. |