#### **ACT86600**

### Hybrid PMIC for Enterprise Storage and Computing

#### **BENEFITS and FEATURES**

- · Wide operating voltage range

- Vin = 2.7V to 14.4V

- Withstand input voltage up to 16V

- Vout = 0.6V to 5.26V

- Complete Integrated Power Solution

- Two 6A DC-DC buck converters

- Two 4A DC-DC buck converters

- One 0.5A DC-DC buck converter

- One 0.6A DC-DC Buck-Boost converter

- Integrated Power FETs

- High efficiency

- Up to 96% efficiency

- Single stage 12V conversion

- Low Quiescent current, <300uA</li>

- Excellent dynamic response

- Programmable switching frequency

- Small inductor sizes

- Fast transient response

- Proprietary COT control algorithm

- High current, Multi-phase functionality

- Single or multiphase phase outputs

- 8A and 12A multiphase outputs

- Staggered phasing in 2-phase operation

- Highly configurable

- 400KHz 1.9MHz Frequency Range.

- Near constant frequency operation.

- Accepts wide inductor values and sizes.

- Easy system level design

- Configurable sequencing

- Independent On & Off sequencing control.

- Sequencing with external power supplies

- Seven programmable GPIOs

- I2C Interface with password protection.

- Reset /Power Good Output

- Flexible System Level Design

- Versatile GPIO functions

- Multiple Sleep modes

- Soft / Hard Reset Functions

- Watchdog Supervision

- Interrupt function available.

- I2C Safety bits to enhance immunity against spurious I2C transactions.

#### Fault protection

- Input UV and OV Monitoring for each buck input.

- Input and Output UV and OV Detection

- Interrupt Controller and fault monitoring options.

- Resistor-less Over Current Protection (OCP)

- System voltage monitoring.

- Small form factor 6X6mm FCOL QFN Package.

#### **APPLICATIONS**

- Solid-State Drives

- Microcontroller Applications

- FPGA

- Personal Navigation Devices

#### **GENERAL DESCRIPTION**

The ACT86600 PMIC is an integrated ActivePMU power management unit. It is highly flexible and can be reconfigured via I<sup>2</sup>C for multiple applications without the need for PCB changes. The low external component count and high configurability significantly speeds time to market. Examples of configurable options include output voltage, startup time, slew rate, system level sequencing, switching frequency, sleep modes, operating modes etc.

The core of the device includes 4 high power DC/DC step down converters, a lower power step down converter and a buck-boost converter. Each regulator can be configured for a wide range of output voltages through the I<sup>2</sup>C interface.

The ACT86600 is a high voltage PMIC that is optimized for single stage voltage conversion from 12V input power sources. It operates with a 2.7V to 14.4V input voltage and can withstand 16V input voltage surges. The four high current regulators can be configured as single phase outputs, or can be paralleled for up to 12A dual phase with outputs.

The ACT86600 PMIC is available in a 6 x 6 mm 48 pin QFN package.

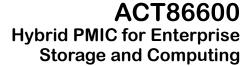

#### TYPICAL APPLICATION DIAGRAM

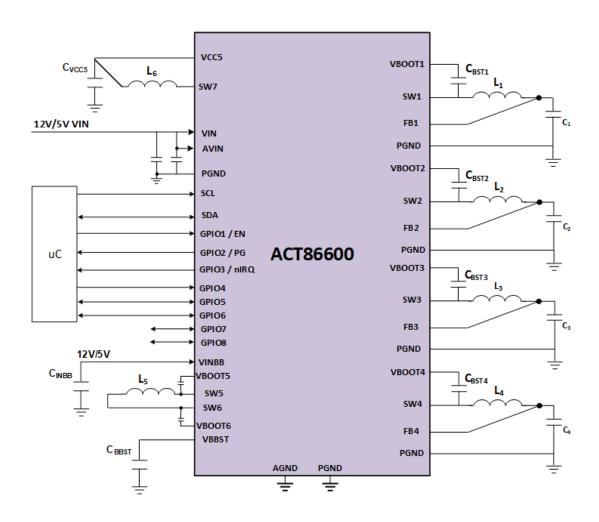

#### **FUNCTIONAL BLOCK DIAGRAM**

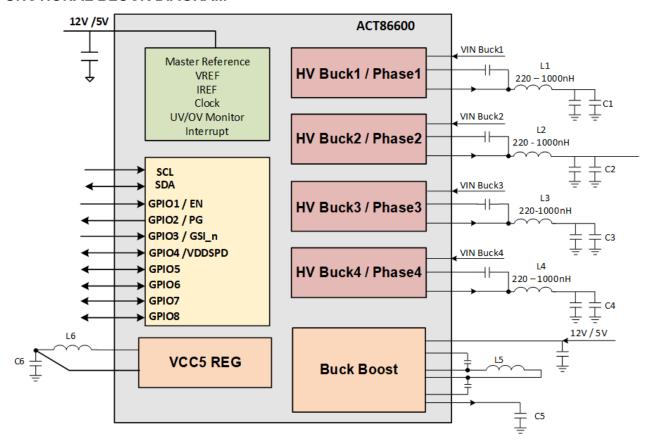

#### ORDERING INFORMATION

| PART NUMBER     | Input<br>Voltage | V <sub>BUCK1</sub> | V <sub>BUCK2</sub> | <b>V</b> вискз | V <sub>BUCK4</sub> | V <sub>CC5</sub> | V <sub>BBST</sub> |

|-----------------|------------------|--------------------|--------------------|----------------|--------------------|------------------|-------------------|

| ACT86600QM101-T | 12V              | V8.0               | 1.2V               | 1.8V           | 3.3V               | 5.0V             | 12V               |

Note 1: Standard product options are identified in this table. Contact factory for custom options, minimum order quantity required.

Note 2: All Qorvo components are RoHS Compliant and with Pb-free plating unless specified differently. The term Pb-free means semiconductor products that comply with current RoHS (Restriction of Hazardous Substances) standards.

Note 3: Package Code designator "Q" represents QFN

Note 4: Pin Count designator "M" represents 48 pins

Note 5: "xxx" represents the CMI (Code Matrix Index) option. The CMI identifies the IC's default register settings

Note 6: See the CMI Option section in the back of the datasheet for a more detailed description of each CMI's settings.

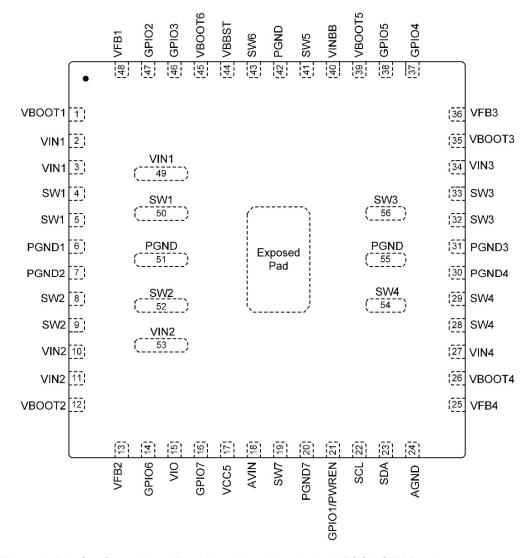

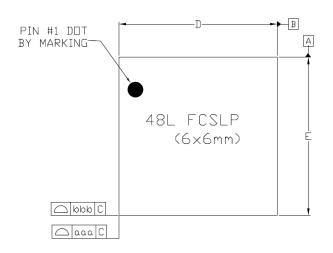

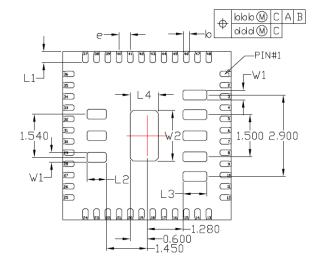

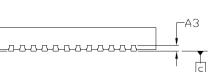

#### PIN CONFIGURATION

Figure 1: Pin Configuration - Top View (pins down) 48pin FCOL QFN Package 6mm x 6mm

#### **PIN DESCRIPTIONS**

| PIN | NAME   | DESCRIPTION                                                                                                                              |

|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | VBOOT1 | Boot strap voltage for Buck1 regulator                                                                                                   |

| 2   | VIN1   | Dedicated input power input to Buck1 regulator                                                                                           |

| 3   | VIN1   | Dedicated input power input to Buck1 regulator                                                                                           |

| 4   | SW1    | Switch pin for Buck1 regulator                                                                                                           |

| 5   | SW1    | Switch pin for Buck1 regulator                                                                                                           |

| 6   | PGND1  | Power Ground for Buck1 regulator                                                                                                         |

| 7   | PGND2  | Power Ground for Buck2 regulator                                                                                                         |

| 8   | SW2    | Switch pin for Buck2 regulator                                                                                                           |

| 9   | SW2    | Switch pin for Buck2 regulator                                                                                                           |

| 10  | VIN2   | Dedicated input power input to Buck2 regulator                                                                                           |

| 11  | VIN2   | Dedicated input power input to Buck2 regulator                                                                                           |

| 12  | VBOOT2 | Boot strap voltage for Buck2 regulator                                                                                                   |

| 13  | VFB2   | Output and feedback pin for Buck2 regulator                                                                                              |

| 14  | GPIO6  | GPIO6 pin. It is configurable with the default function based on CMI                                                                     |

| 15  | VIO    | VIO pin                                                                                                                                  |

| 16  | GPIO7  | GPIO7 pin. It is configurable with the default function based on CMI                                                                     |

| 17  | VCC5   | 5.0V Output from PMIC / PMIC power source used to power the PMIC internally.                                                             |

| 18  | AVIN   | Analog input power for the PMIC                                                                                                          |

| 19  | SW7    | Switch pin for VCC5 generating switching regulator                                                                                       |

| 20  | PGND7  | Power Ground for the VCC5 regulator. It is also used for the AVIN ground reference.                                                      |

| 21  | GPIO1  | GPIO1 pin. It is configurable with default configuration based on the CMI. This GPIO can be used as either the PWREN or Enable function. |

| 22  | SCL    | I <sup>2</sup> C Serial Clock Pin                                                                                                        |

| 23  | SDA    | I <sup>2</sup> C Serial Data pin                                                                                                         |

| 24  | AGND   | Analog Ground                                                                                                                            |

| 25  | VFB4   | Output and feedback pin for Buck4 regulator                                                                                              |

| 26  | VBOOT4 | Boot strap voltage for Buck4 regulator                                                                                                   |

| 27  | VIN4   | Dedicated input power input to Buck4 regulator                                                                                           |

| 28  | SW4    | Switch pin for Buck4 regulator                                                                                                           |

| 29  | SW4    | Switch pin for Buck4 regulator                                                                                                           |

| •   |        |                                                                                                                                          |

| 30          | PGND4  | Power Ground for Buck4 regulator                                                                |

|-------------|--------|-------------------------------------------------------------------------------------------------|

| 31          | PGND3  | Power Ground for Buck3 regulator                                                                |

| 32          | SW3    | Switch pin for Buck3 regulator                                                                  |

| 33          | SW3    | Switch pin for Buck3 regulator                                                                  |

| 34          | VIN3   | Dedicated input power input to Buck3 regulator                                                  |

| 35          | VBOOT3 | Boot strap voltage for Buck3 regulator                                                          |

| 36          | VFB3   | Output and feedback pin for Buck3 regulator                                                     |

| 37          | GPIO4  | GPIO4 pin. It is configurable with the default function based on CMI                            |

| 38          | GPIO5  | GPIO5 pin. It is configurable with the default function based on CMI                            |

| 39          | VBOOT5 | Boot strap voltage for buck boost (connect capacitor between VBOOT5 and SW5 pin)                |

| 40          | VINBB  | Dedicated input power pin for the Buck-Boost regulator                                          |

| 41          | SW5    | Switch pin for Buck-Boost regulator. SW5 is on the buck side of the regulator.                  |

| 42          | PGND   | Power Ground for Buck-Boost regulator                                                           |

| 43          | SW6    | Switch pin for Buck-Boost regulator. SW6 is on the boost side of the regulator.                 |

| 44          | VBBST  | Output of the buck boost stage. Boost followed by a step-down stage                             |

| 45          | VBOOT6 | Boot strap voltage for Buck-Boost (connect capacitor between VBOOT6 and SW6 pin)                |

| 46          | GPIO3  | GPIO3 pin. It is configurable with the default function based on CMI. Typically used for nIRQ.  |

| 47          | GPIO2  | GPIO2 pin. It is configurable with the default function based on CMI. Typically use for nRESET. |

| 48          | VFB1   | Output and feedback pin for Buck1 regulator                                                     |

| 49          | VIN1   | Dedicated input power input to Buck1 regulator                                                  |

| 50          | SW1    | Switch pin for Buck1 regulator                                                                  |

| 51          | PGND   | Power Ground                                                                                    |

| 52          | SW2    | Switch pin for Buck2 regulator                                                                  |

| 53          | VIN2   | Dedicated input power input to Buck2 regulator                                                  |

| 54          | SW4    | Switch pin for Buck4 regulator                                                                  |

| 55          | PGND   | Power Ground                                                                                    |

| 56          | SW3    | Switch pin for Buck3 regulator                                                                  |

| Exposed Pad | EP     | Exposed Pad. Must be soldered to PGND on PCB.                                                   |

#### **ABSOLUTE MAXIMUM RATINGS**

| PARAMETER                                                                                | VALUE                    | UNIT |

|------------------------------------------------------------------------------------------|--------------------------|------|

| All Pins to GND unless stated otherwise below                                            | -0.3 to 6.0              | V    |

| AVIN to AGND                                                                             | -0.3 to 18               | V    |

| VCC5 to AGND                                                                             | -0.3 to 6.0              | V    |

| SW7 to PGND                                                                              | -1.0 to AVIN + 1.0       | V    |

| VIN1,2,3,4 to PGND                                                                       | -0.3 to 16.0             | V    |

| SW1,2,3,4 to PGND                                                                        | -1.0 to VIN1,2,3,4 + 1.0 | V    |

| VBOOT1,2,3,4 to SW1,2,3,4 (VBOOT1 to SW1, VBOOT2 to SW2 etc.)                            | -0.3 to SW1,2,3,4 + 6.0  | V    |

| VFB1,2,3,4 to AGND                                                                       | -0.3 to 6.0              | V    |

| VINBB to PGND                                                                            | -0.3 to 16.0             | V    |

| VBBST to PGND                                                                            | -0.3 to 16.5             | V    |

| SW5 to PGND                                                                              | -1.0 to VINBB + 1.0      | V    |

| SW6 to PGND                                                                              | -1.0 to VBBST + 1.0      | V    |

| VBOOT5 to SW5                                                                            | -0.3 to SW5 + 6.0        | V    |

| VBOOT6 to SW6                                                                            | -0.3 to SW6 + 6.0        | V    |

| SCL, SDA to AGND                                                                         | -0.3 to 6.0              | V    |

| GPIO1,2,3,4,5,6,7 to AGND                                                                | -0.3 to 6.0              | V    |

| AGND, PGND                                                                               | -0.3 to + 0.3            | V    |

| Junction to Ambient Thermal Resistance (Note 2)                                          | 20                       | °C/W |

| Junction to Case Thermal Resistance (Note 2)                                             | 2.3                      | °C/W |

| Operating Junction Temperature                                                           | -40 to 150               | °C   |

| Storage Temperature                                                                      | -55 to 150               | °C   |

| V <sub>ESD</sub> , Electrostatic Discharge, Human Body Model (HBM) per JEDEC JS-001      | 2000                     | V    |

| V <sub>ESD</sub> , Electrostatic Discharge, Charged Device Model (CDM) per JEDEC JS-002. | 500                      | V    |

Note1: Do not exceed these limits to prevent damage to the device. Exposure to absolute maximum rating conditions for long periods may affect device reliability.

Note2: Measured on Qorvo Evaluation Kit

#### **RECOMMENDED OPERATING CONDITIONS**

| PARAMETER                                                     | Value                | UNIT |

|---------------------------------------------------------------|----------------------|------|

| All Pins to GND unless stated otherwise below                 | 0 to 5.0             | V    |

| AVIN to AGND                                                  | 5.0 to 12.0          | V    |

| VCC5 to AGND                                                  | 5.0                  | V    |

| SW7 to PGND                                                   | -0.8 to AVIN + 0.8   | V    |

| VIN1,2,3,4 to PGND                                            | 5.0 to 12.0          | V    |

| SW1,2,3,4 to VIN1,2,3,4 (SW1 to VIN1, SW2 to VIN2 etc.)       | -0.8 to VIN1-4 + 0.8 | V    |

| VBOOT1,2,3,4 to SW1,2,3,4 (VBOOT1 to SW1, VBOOT2 to SW2 etc.) | 0 to SW1-4 + 5.0     | V    |

| VFB1,2,3,4 to AGND                                            | 0.6 to 5.0           | V    |

| VINBB to PGND                                                 | 5.0 to 12.0          | V    |

| VBBST to PGND                                                 | 1.8 to 16.0          | V    |

| SW5 to PGND                                                   | -0.8 to VINBB + 0.8  | V    |

| SW6 to PGND                                                   | -0.8 to VBBST + 0.8  | V    |

| VBOOT5 to SW5                                                 | 0 to SW5 + 5.0       | V    |

| VBOOT6 to SW6                                                 | 0 to SW6 + 5.0       | V    |

| SCL, SDA to AGND                                              | 0 to 5.0             | V    |

| GPIO1,2,3,4,5,6,7 to AGND                                     | 0 to 5.0             | V    |

| AGND, PGND                                                    | 0                    | V    |

| Operating Junction Temperature                                | -10 to 105           | °C   |

#### **ELECTRICAL CHARACTERISTICS: GENERAL PURPOSE I/O**

(VIO = 1.8V,  $T_A = 25$ °C, unless otherwise specified.)

| PARAMETER                                              | TEST CONDITIONS                                                   | MIN                        | TYP | MAX  | UNIT |

|--------------------------------------------------------|-------------------------------------------------------------------|----------------------------|-----|------|------|

| GPIO1,2,3,4,5,6,7 Input Low (V <sub>IL</sub> )         | V <sub>VIO</sub> = 1.8V                                           |                            |     | 0.35 | V    |

| GPIO1,2,3,4,5,6,7 Input High (V <sub>IH</sub> )        | V <sub>VIO</sub> = 1.8V                                           | 1.25                       |     |      | V    |

| GPIO1,2,3,4,5,6,7 Input Low (V <sub>IL</sub> )         | V <sub>VIO</sub> = 3.3V                                           |                            |     | 0.5  | V    |

| GPIO1,2,3,4,5,6,7 Input High (V <sub>IH</sub> )        | V <sub>VIO</sub> = 3.3V                                           | 1.65                       |     |      | V    |

| GPIOx Open Drain Leakage Current.                      | Pulled up to 5V                                                   |                            |     | 1    | μΑ   |

| GPIOx Open Drain Output Low.                           | I <sub>OL</sub> = 1mA                                             |                            |     | 0.35 | V    |

| GPIO2,3,4,5 Output Low, (VoL)                          | I <sub>OL</sub> = 0.25mA, CMOS or push-pull output configuration. |                            |     | 0.35 | V    |

| GPIO2,3,4,5 Output High, (VoH)                         | I <sub>OH</sub> = 0.25mA, CMOS or push-pull output configuration. | V <sub>VIO</sub> -<br>0.35 |     |      | V    |

| GPIOx Deglitch Time (falling)                          | Note 1                                                            |                            | 20  |      | μs   |

| GPIOx Deglitch Time (rising)                           | Note 1                                                            |                            | 10  |      | μs   |

| VIO Operating Range                                    | Note 2                                                            | 1.6                        |     | 5.0  | V    |

| GPIOx, Pull up resistor to VIO,<br>GPIOx = GPIO1,2,37. | Note3                                                             |                            | 200 |      | kΩ   |

Note 1: Guaranteed by design only

Note 2: VIO is the reference level for GPIOs when configured as open drain outputs or as inputs.

Note 3: GPIO1 has option to connect internal pullup resistor to VCC5.

#### **ELECTRICAL CHARACTERISTICS - SYSTEM CONTROL**

(VIN = 12V, VCC5 = 5V,  $T_A$  = 25°C, unless otherwise specified.)

| PARAMETER                                             | TEST CONDITIONS                                                                                                                            | MIN  | TYP  | MAX  | UNIT |

|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| AVIN, VIN1,2,3,4 Input Voltage Range                  | HV Input pin, typical pin voltage, PMIC power from VIN1.                                                                                   | 2.7  |      | 14.4 | ٧    |

| VIN1,2,3,4 Input UV Threshold, rising                 | VIN > VIN_UV (Rising) turns on regulators                                                                                                  |      | 2.9  |      | V    |

| VIN1,2,3,4 Input UV Threshold, falling                | VIN < VIN_UV (Falling) turns off regulators                                                                                                |      | 2.7  |      | V    |

| VIN1,2,3,4 Input UV Threshold, hysteresis             |                                                                                                                                            | 0.1  | 0.2  | 0.3  | V    |

| VIN1,2,3,4 Input UV detection deglitch time           |                                                                                                                                            |      | 100  |      | μs   |

| VINA 2.2.4 Invest OV Threehold vising                 | VINOV_SEL = 0                                                                                                                              | -4%  | 5.8  | +4%  | V    |

| VIN1,2,3,4 Input OV Threshold, rising                 | VINOV_SEL = 1                                                                                                                              | -4%  | 15.0 | +4%  | V    |

| VIN1,2,3,4 Input OV Threshold, hysteresis             | As percentage of VINx voltage                                                                                                              |      | 3    |      | %    |

| AV/INI Input OV/Throohald mining /Ninta OV            | VINOV_SEL = 0                                                                                                                              | -5%  | 6.15 | +5%  | V    |

| AVIN Input OV Threshold, rising (Note 2)              | VINOV_SEL = 1                                                                                                                              | -5%  | 16.0 | +5%  | V    |

| AVIN Input OV Threshold, hysteresis.                  | percentage of AVIN Input OV voltage threshold                                                                                              |      | 3    |      | %    |

| VCC5 nPOR Rising Threshold                            | VCC5>VCC5_nPOR (Rising) allows to turn on regulators.                                                                                      | 2.45 | 2.6  | 2.75 | V    |

| VCC5 nPOR Hysteresis                                  | VCC5 <vcc5_npor (falling)="" nvm="" off="" regulators,="" reload.<="" td="" turns=""><td></td><td>200</td><td></td><td>mV</td></vcc5_npor> |      | 200  |      | mV   |

| VIN1,2,3,4 Input OV detection deglitch time.          | (Note 1)                                                                                                                                   |      | 100  |      | μs   |

| VINBB Input Voltage Range                             |                                                                                                                                            | 2.7  |      | 14.4 | V    |

| VINBB Input UV Threshold, rising                      |                                                                                                                                            |      | 3.0  |      | V    |

| VINBB Input UV Threshold, falling                     |                                                                                                                                            |      | 2.8  |      | V    |

| VINBB Input UV Threshold, hysteresis                  |                                                                                                                                            |      | 0.2  |      | V    |

| VINBB Input UV detect deglitch time                   | (Note 1)                                                                                                                                   |      | 100  |      | μs   |

| VINBB Input OV Threshold, rising (Not user            | VIN_OV_OPT = 0                                                                                                                             | -6%  | 5.8  | +6%  | V    |

| adjustable)                                           | VIN_OV_OPT = 1                                                                                                                             | -6%  | 15.0 | +6%  | V    |

| VINBB Input OV Threshold, hysteresis                  | percentage of VINBB rising OV threshold                                                                                                    |      | 3    |      | %    |

| VINBB Input OV detect deglitch time                   | (Note 1)                                                                                                                                   |      | 100  |      | μs   |

|                                                       | VINMON [2:0] = 000.                                                                                                                        |      | 3.0  |      | V    |

| AVIN UV Threshold Rising.                             | VINMON [2:0] = 001                                                                                                                         |      | 3.2  |      | V    |

| AVIN rising threshold triggers the power on sequence. | VINMON [2:0] = 010                                                                                                                         |      | 3.4  |      | V    |

|                                                       | VINMON [2:0] = 011                                                                                                                         |      | 3.6  |      | V    |

|                                                                                                | VINMON [2:0] = 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3.8                                     | V  |

|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----|

|                                                                                                | VINMON [2:0] = 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4.0                                     | V  |

|                                                                                                | VINMON [2:0] = 110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8.0                                     | V  |

|                                                                                                | VINMON [2:0] = 111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 9.0                                     | V  |

|                                                                                                | VINMON [2:0] = 000.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2.8                                     | V  |

|                                                                                                | VINMON [2:0] = 001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3.0                                     | V  |

|                                                                                                | VINMON [2:0] = 010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3.2                                     | V  |

| AVIN UV Warning Interrupt Threshold Falling                                                    | VINMON [2:0] = 011                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3.4                                     | V  |

| (tracks rising threshold)                                                                      | VINMON [2:0] = 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3.6                                     | V  |

|                                                                                                | VINMON [2:0] = 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3.8                                     | V  |

|                                                                                                | VINMON [2:0] = 110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 7.0                                     | V  |

|                                                                                                | VINMON [2:0] = 111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8.0                                     | V  |

| AVIN UV Shutdown Threshold                                                                     | AVIN voltage below which regulators are forced to shut down                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2.7                                     | V  |

|                                                                                                | All Regulators Enabled but no load,<br>buck-boost regulator is disabled. Low<br>power mode enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 300 400                                 | μА |

|                                                                                                | All Regulators Enabled but no load, buck-boost regulator is disabled. Low power mode disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2.15                                    | mA |

| AVIN, Operating Supply Current                                                                 | AVIN=5.0V, VCC5 = 5.0V, All Regulators<br>Enabled but no load, buck-boost<br>regulator is disabled.<br>Bypass [] = 1. Low power mode enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 520 680                                 | μА |

|                                                                                                | AVIN=5.0V, VCC5 = 5.0V, All Regulators<br>Enabled but no load, buck-boost<br>regulator is disabled.<br>Bypass [] = 1. Low power mode disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3.2                                     | mA |

| N/IN O I O I O I                                                                               | All Regulators Enabled but no load, buck-boost regulator is enabled with no load. Low power mode enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 800 1200                                | μА |

| AVIN, Operating Supply Current                                                                 | All Regulators Enabled but no load,<br>buck-boost regulator is enabled with no<br>load. Low power mode disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2.25                                    | mA |

| AVIN Operating Supply Correct                                                                  | One HV Regulator turned ON. Buck-<br>Boost regulator is disabled. Low power<br>mode enabled for HV Regulator and<br>VCC5 regulator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 150                                     | μА |

| Aviiv, Operating Supply Current                                                                | One HV Regulator turned ON. Buck-<br>Boost regulator is disabled. Low power<br>mode disabled for HV Regulator and<br>VCC5 regulator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0.85                                    | mA |

| AVIN, Operating Supply Current                                                                 | AVIN=12V, VCC5 = 5.0V. All other regulators disabled. Low power mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 100                                     | μA |

| AVIN, Operating Supply Current  AVIN, Operating Supply Current  AVIN, Operating Supply Current | All Regulators Enabled but no load, buck-boost regulator is disabled. Low power mode enabled.  All Regulators Enabled but no load, buck-boost regulator is disabled. Low power mode disabled.  AVIN=5.0V, VCC5 = 5.0V, All Regulators Enabled but no load, buck-boost regulator is disabled.  Bypass [] = 1. Low power mode enabled.  AVIN=5.0V, VCC5 = 5.0V, All Regulators Enabled but no load, buck-boost regulator is disabled.  Bypass [] = 1. Low power mode disabled.  All Regulators Enabled but no load, buck-boost regulator is enabled with no load. Low power mode enabled.  All Regulators Enabled but no load, buck-boost regulator is enabled with no load. Low power mode disabled.  One HV Regulator turned ON. Buck-Boost regulator is disabled. Low power mode enabled for HV Regulator and VCC5 regulator.  One HV Regulator turned ON. Buck-Boost regulator is disabled. Low power mode disabled for HV Regulator and VCC5 regulator.  AVIN=12V, VCC5 = 5.0V. All other | 2.15 520 680 3.2 800 1200 2.25 150 0.85 | r  |

|                                                                      | enabled.                                                                                                                                                                 |    |                                      |     |    |

|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--------------------------------------|-----|----|

|                                                                      | AVIN=12V, VCC5 = 5.0V. All other regulators disabled. Low power mode disabled.                                                                                           |    | 450                                  |     | μΑ |

|                                                                      | AVIN=5.0V, VCC5 = 5.0V. All other regulators disabled. Bypass [] =1                                                                                                      |    | 100                                  |     | μΑ |

| Thermal Warning Temperature                                          | Temperature rising                                                                                                                                                       |    | 125                                  |     | °C |

| Thermal Warning Hysteresis                                           |                                                                                                                                                                          |    | 25                                   |     | °C |

| Thermal Shutdown Temperature                                         | Temperature rising                                                                                                                                                       |    | 155                                  |     | °C |

| Thermal Shutdown Hysteresis                                          |                                                                                                                                                                          |    | 25                                   |     | °C |

| Thermal Shutdown Deglitch (Note 1)                                   | Enable and disable timing                                                                                                                                                | 75 | 100                                  | 125 | μs |

| Power Up Delay after initial AVIN ramp.                              | Time from AVIN > AVIN UV rising threshold to PG for first regulator (Bucks). (zero delay setting)                                                                        |    | 2000                                 |     | μs |

| Transition time from Deep Sleep (DPSLP) State to Active State        | Time from PWREN pin low to high transition (exit DPSLP State) to time when the first regulator turns ON with minimum turn on delay configuration.                        |    | 600                                  |     | μs |

| Transition time from Sleep State (SLEEP) to Active State             | Time from I <sup>2</sup> C command to clear SLEEP EN register bit (exit SLEEP state) to time when the first regulator turns ON with minimum turn on delay configuration. |    | 600                                  |     | μs |

| Regulator Programmable Startup Delay Timings between turn on events. | ONDLY=000 ONDLY=001 ONDLY=010 ONDLY=011 ONDLY=100 ONDLY=101 ONDLY=111                                                                                                    |    | 0<br>0.25<br>0.5<br>1<br>2<br>4<br>8 |     | ms |

| Regulator Programmable Turn Off Delay                                | Configurable in 1ms steps between 0ms to 15ms                                                                                                                            | 0  |                                      | 15  | ms |

| nRESET, Delay Timings                                                | Configurable to 20, 40, 60 or 100ms.                                                                                                                                     | 20 |                                      | 100 | ms |

| Retry time after entering UVOVFLT state                              | Time when all regulators are forced off before trying ON sequence again                                                                                                  |    | 100                                  |     | ms |

| Watch dog timer                                                      | Monitors I <sup>2</sup> C inactivity and time out function                                                                                                               |    | 8                                    |     | s  |

| Hard reset wait timer                                                | Hard reset turns off the regulators, waits in the reset state for a "hard-reset time delay" and restarts the on sequence.                                                |    | 0.5                                  |     | s  |

Note 1: Guaranteed by design only.

Note 2: When AVIN > AVIN\_OV threshold, the system moves to the RESET operating state to turn-off all regulators. VCC5 regulator (Or LDO if the  $AVIN_OV_SEL=0$ ) continues to function even when AVIN is higher than  $AVIN_OV$  to retain the VCC5 output and keep the PMIC powered on.

#### **BUCK1/2 STEP-DOWN DC/DC ELECTRICAL CHARACTERISTICS**

(VIN = 12V, VCC5 = 5V,  $T_A$  = 25°C, unless otherwise specified.)

| PARAMETER                                                             | CONDITIONS                                                                                                         | MIN   | TYP    | MAX                | UNIT  |

|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------|--------|--------------------|-------|

| VIN1,2, Operating Input Voltage                                       |                                                                                                                    | 2.7   |        | V <sub>IN_OV</sub> | V     |

| VFB1,2, Programmable Output<br>Voltage Range                          | Configurable in 20mV steps, (Note 1)                                                                               | 0.6   |        | 5.26               | V     |

|                                                                       | Configurable in 5mV steps                                                                                          | 0.6   |        | 1.875              | V     |

| Maximum Allowable Continuous<br>Output Current                        | DC current output, 0.47µH, Switching frequency = 1.0MHz, VFB1,2 = 1.2V.                                            |       |        | 6.0                | Α     |

| Standby Supply Current                                                | VFB1,2 >= 103%, Regulator Enabled, VFB1,2 = 1.8V, No Load, Low Power Mode enabled                                  |       | 40     |                    | μΑ    |

| Standby Supply Current                                                | Regulator Enabled, VFB1,2 = 1.8V, No Load.<br>Lower Power Mode Disabled                                            |       | 410    |                    |       |

| Shutdown Current                                                      | Regulator Disabled                                                                                                 |       | 1      |                    | μA    |

| DC Output Voltage Accuracy                                            | 0.6V < VFB1,2 < 1.25V, I <sub>OUT</sub> = 4A<br>(Continuous Conduction, CCM)                                       | -12.5 | VNOM   | 12.5               | mV    |

|                                                                       | VFB1,2 >= 1.25V, I <sub>OUT</sub> = 4A<br>(Continuous Conduction, CCM)                                             | -1    | VNOM   | 1                  | %     |

|                                                                       | 0.6V < VFB1,2 < 1.25V, I <sub>OUT</sub> = 10mA,<br>(Discontinuous Conduction Mode, DCM)<br>Low power mode disabled | -25   | VNOM   | 25                 | mV    |

|                                                                       | VFB1,2 >= 1.25V, I <sub>OUT</sub> = 10mA, Discontinuous Conduction Mode, DCM. Low power mode disabled.             | -2    | VNOM   | 2                  | %     |

|                                                                       | 0.6V < VFB1,2 < 1.25V, No Load,<br>Discontinuous Conduction Mode, DCM. Low<br>power mode enabled.                  |       | VNOM+2 |                    | %     |

|                                                                       | VFB1,2 >= 1.25V, No Load, Discontinuous Conduction Mode, DCM.                                                      | 0     | VNOM+2 | 4                  | %     |

| Line Regulation                                                       | VFB1,2 = 1.8V, VIN1,2 = 5.0V to 13.0V,<br>(Continuous Conduction or CCM mode)                                      |       | 0.15   |                    | %     |

| Load Regulation                                                       | VFB1,2 = 1.8V, 2.0A to 6.0A<br>(Continuous Conduction or CCM mode)                                                 |       | 0.1    |                    | %     |

| Power Good Threshold / POK                                            | VFB1,2 Rising, POK [] = 1                                                                                          | 87    | 90     | 93                 | %VNOM |

| Fower Good Threshold / FOR                                            | VFB1,2 Falling, POK [] = 0                                                                                         | 84    | 87     | 90                 | %VNOM |

| Power Good Hysteresis / POK                                           | VFB1,2 Falling, relative to regulation point                                                                       |       | 3      |                    | %VNOM |

| Overvoltage Fault Threshold                                           | VFB1,2 Rising, relative to regulation point                                                                        | 107   | 113    | 117                | %VNOM |

| Overvoltage Fault Hysteresis                                          | VFB1,2 Falling, relative to regulation point                                                                       |       | 3      |                    | %VNOM |

|                                                                       | Freq = 0000, VIN = 12.0V, VFB1,2 = 1.0V                                                                            |       | 0.4    |                    | MHz   |

|                                                                       | Freq = 0001, VIN = 12.0V, VFB1,2 = 1.0V                                                                            |       | 0.5    |                    | MHz   |

| Frankski Control Control                                              | Freq = 0010, VIN = 12.0V, VFB1,2 = 1.0V                                                                            |       | 0.6    |                    | MHz   |

| Emulated Switching Frequency Range, CCM - Continuous Conduction Mode. | Freq = 0011, VIN = 12.0V, VFB1,2 = 1.2V                                                                            |       | 0.7    |                    | MHz   |

|                                                                       | Freq = 0100, VIN = 12.0V, VFB1,2 = 1.2V                                                                            |       | 8.0    |                    | MHz   |

|                                                                       | Freq = 0101, VIN = 12.0V, VFB1,2 = 1.2V                                                                            |       | 0.9    |                    | MHz   |

|                                                                       | Freq = 0110, VIN = 12.0V, VFB1,2 = 1.8V                                                                            |       | 1.0    |                    | MHz   |

|                                                | Freq = 0111, VIN = 12.0V, VFB1,2 = 1.8V                                                   |     | 1.1  |      | MHz   |

|------------------------------------------------|-------------------------------------------------------------------------------------------|-----|------|------|-------|

|                                                | Freq = 1000, VIN = 12.0V, VFB1,2 = 1.8V                                                   |     | 1.2  |      | MHz   |

|                                                | Freq = 1001, VIN = 12.0V, VFB1,2 = 2.5V                                                   |     | 1.3  |      | MHz   |

|                                                | Freq = 1010, VIN = 12.0V, VFB1,2 = 2.5V                                                   |     | 1.4  |      | MHz   |

|                                                | Freq = 1011, VIN = 12.0V, VFB1,2 = 2.5V                                                   |     | 1.5  |      | MHz   |

|                                                | Freq = 1100, VIN = 12.0V, VFB1,2 = 3.3V                                                   |     | 1.6  |      | MHz   |

|                                                | Freq = 1101, VIN = 12.0V, VFB1,2 = 3.3V                                                   |     | 1.7  |      | MHz   |

|                                                | Freq = 1110, VIN = 12.0V, VFB1,2 = 3.3V                                                   |     | 1.8  |      | MHz   |

|                                                | Freq = 1111, VIN = 12.0V, VFB1,2 = 3.3V                                                   |     | 1.9  |      | MHz   |

| Emulated switching frequency accuracy          | At the default switching frequency setting                                                | -20 |      | 20   | %     |

| T <sub>MIN</sub> , Minimum on Time             |                                                                                           |     | 65   | 85   | ns    |

| Soft-Start Period Tss                          | 5% to 95% VNOM                                                                            |     | 1000 | 1500 | μs    |

| $T_{\text{start}}$ , Time from EN to PG        | Time from enable to PGOOD                                                                 |     | 1200 |      | μs    |

|                                                | ILIM set = 00                                                                             |     | 6    |      | Α     |

| Peak Current Limit Cyale by Cyale              | ILIM set = 01                                                                             |     | 7    |      | Α     |

| Peak Current Limit, Cycle-by-Cycle             | ILIM set = 10 (Note 3)                                                                    |     | 8    |      | Α     |

|                                                | ILIM set = 11 (Note 3)                                                                    |     | 9    |      | Α     |

| Peak Current Limit, Cycle-by-Cycle<br>Accuracy | At default ILIM setting                                                                   | -10 |      | 10   | %     |

|                                                | ILIM set = 00                                                                             |     | 5    |      | Α     |

| Valley Current Limit Cycle by Cycle            | ILIM set = 01                                                                             |     | 6    |      | Α     |

| Valley Current Limit, Cycle-by-Cycle           | ILIM set = 10                                                                             |     | 7    |      | Α     |

|                                                | ILIM set = 11                                                                             |     | 8    |      | Α     |

| Valley Current Limit, Cycle-by-Cycle Accuracy  | At default ILIM setting                                                                   | -10 |      | 10   | %     |

| LS FET reverse conduction current limit        |                                                                                           |     | 3    |      | Α     |

| Current Limit, Shutdown                        | % compared to Peak Current Limit, cycle-by-cycle                                          | 115 | 125  | 135  | %     |

| Current Limit, Warning                         | % compared to Peak Current Limit, cycle-by-cycle                                          | 70  | 80   | 90   | %     |

| HS FET On-Resistance                           | Isw = 1A, V <sub>CC5</sub> = 5.0V                                                         |     | 30   |      | mΩ    |

| LS FET On-Resistance                           | Isw = 1A, V <sub>CC5</sub> = 5.0V                                                         |     | 11   |      | mΩ    |

| SW Leakage Current (Note 2)                    | V <sub>IN</sub> = 12.0V, V <sub>SW</sub> = 0V                                             |     | 5    |      | μΑ    |

| OVV Leakage Guilelit (Note 2)                  | V <sub>IN</sub> = 12.0V, V <sub>SW</sub> = 12.0V                                          |     | 10   |      | μΑ    |

| Dynamic Voltage Scaling Pate                   | Configurable in 5mV steps                                                                 |     | 0.02 |      | mV/us |

| Dynamic Voltage Scaling Rate                   | Configurable in 20mV steps                                                                |     | 0.08 |      | mV/us |

| Output Pull Down Resistance                    | Pull Down resistance is only connected when DISPLDN[] = 0 and the regulator is turned off |     |      | 10   | Ohms  |

|                                                |                                                                                           |     |      |      |       |

Note 1: VFB1,2 settings of 5.25V or higher not recommended. Lifetime reliability guaranteed for output settings less than 5.25V. Note 2: The current leakage from SW is not from Power FETs but from active circuitry associated with the SW node of the regulators

Note 3: Applicable for VIN < 10V. Do not use these settings when VIN > 10V

#### **BUCK3/4 STEP-DOWN DC/DC ELECTRICAL CHARACTERISTICS**

(VIN = 12V, VCC5 = 5V,  $T_A$  = 25°C, unless otherwise specified.)

| PARAMETER                                                       | CONDITIONS                                                                                                        | MIN   | TYP    | MAX                | UNIT  |

|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-------|--------|--------------------|-------|

| VIN3,4 Operating Input Voltage                                  |                                                                                                                   | 2.7   |        | V <sub>IN_OV</sub> | V     |

| VFB3,4 Programmable Output Voltage Range                        | Configurable in 20mV steps, (Note 1)                                                                              | 0.6   |        | 5.26               | V     |

|                                                                 | Configurable in 5mV steps                                                                                         | 0.6   |        | 1.875              | V     |

| Maximum Allowable Continuous<br>Output Current                  | DC current output, 0.47µH, Switching frequency = 1.0MHz, VFB3,4 = 1.2V                                            |       |        | 4.0                | Α     |

| Standby Supply Current                                          | VFB3,4 >= 103%, Regulator Enabled, VFB3,4 = 1.8V, No Load. Low Power Mode Enabled                                 |       | 40     |                    | μA    |

| Standby Supply Current                                          | Regulator Enabled, VFB3,4 = 1.8V, No Load.<br>Low Power Mode Disabled                                             |       | 410    |                    | μA    |

| Shutdown Current                                                | Regulator Disabled                                                                                                |       | 1.0    |                    | μA    |

| Output Voltage Accuracy                                         | 0.6V < VFB3,4 < 1.25V, I <sub>OUT</sub> = 3A<br>(Continuous Conduction, CCM)                                      | -12.5 | VNOM   | 12.5               | mV    |

|                                                                 | VFB3,4 >= 1.25V, I <sub>OUT</sub> = 3A<br>(Continuous Conduction, CCM)                                            | -1    | VNOM   | 1                  | %     |

|                                                                 | 0.6V < VFB3,4 < 1.25V, I <sub>OUT</sub> = 10mA<br>(Discontinuous Conduction Mode, DCM)<br>Low power mode disabled | -25   | VNOM   | 25                 | mV    |

|                                                                 | VFB3,4 >= 1.25V, I <sub>OUT</sub> = 10mA<br>(Discontinuous Conduction Mode, DCM)<br>Low power mode disabled       | -2    | VNOM   | 2                  | %     |

|                                                                 | 0.6V < VFB3,4 < 1.25V, No Load<br>(Discontinuous Conduction Mode, DCM)<br>Low power mode enabled                  |       | VNOM+2 |                    | %     |

|                                                                 | VFB3,4 >= 1.25V, No Load<br>(Discontinuous Conduction Mode, DCM)<br>Low power mode enabled                        | 0     | VNOM+2 | 4                  | %     |

| Line Regulation                                                 | VFB3,4 = 1.8V, VIN3,4 = 5.0V to 13.0V, PWM Regulation                                                             |       | 0.15   |                    | %     |

| Load Regulation                                                 | VFB3,4 = 1.8V, PWM Regulation, 2.0A to 4.0A                                                                       |       | 0.10   |                    | %     |

| Power Good Threshold / POK                                      | VFB3,4 Rising, POK [] = 1                                                                                         | 87    | 90     | 93                 | %VNOM |

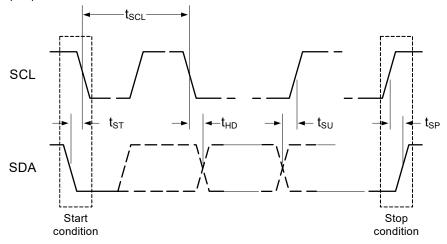

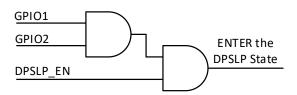

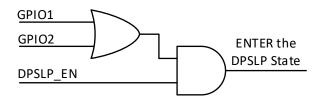

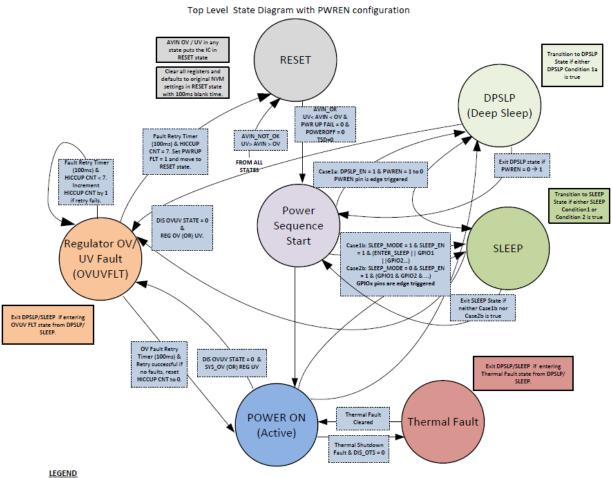

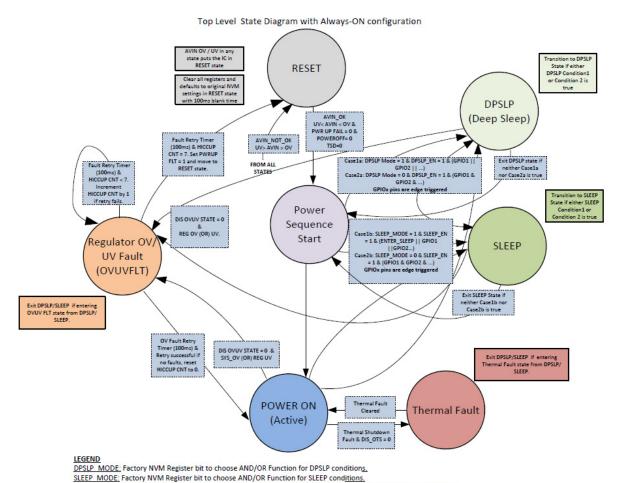

| 1 ower dood Threshold / 1 ork                                   | VFB3,4 Fallng, POK [] = 0                                                                                         | 84    | 87     | 90                 | %VNOM |