## 4.2W Mono Class-K Audio Amplifier

#### Features

- Supply voltage range: 2.8 V to 5.5 V

- Static operation current: 3.5mA

- Shutdown current: <1uA

- Loudspeaker peak power from 5V supply:

- 4.2W @ 4Ω, Po,10% THD+N

- 3.5W @ 4Ω, Po,1% THD+N

- Loudspeaker peak power from 4.2V supply:

- 3W @ 4Ω, Po,10% THD+N

- 2.6W @ 4Ω, Po,1% THD+N

- 2.9W @ 8Ω, Po,10% THD+N

- 2.3W @ 8Ω, Po,1% THD+N

- Gain setting: 27.5dB

- Integrated adaptive charge-pump circuit

- Non-Crack-Noise (NCN) Function

- Pop noise and click noise reduction

- Under-Voltage detection

- Short-Circuit protection with auto recovery

- Over temperature protection with auto recovery

#### **Applications**

- Portable Multimedia Devices

- Mobile Phones

- GPS

- Handsets

#### **Description**

The AD51653 is a mono, class-D audio amplifier with a built-in, adaptive charge pump circuit for better system power efficiency. Due to its design, AD51653 can provide a constant 3W peak output power with 40hm speaker at 4.2V of battery output voltage. When the amplitude of the input audio signal is below a threshold, AD51653 operates in power-saving which disables mode. the charge-pump circuit to save power, and the amplifier is directly powered by the battery. When the amplitude of the audio signal exceeds the threshold level, AD51653 enables the charge-pump circuit to generate a regulated, 2xVDD (input power) power supply up to 6.5V, to drive the amplifier. Since most of time the audio signal is below the threshold level, this feature prolongs the battery life effectively without sacrificing the output quality.

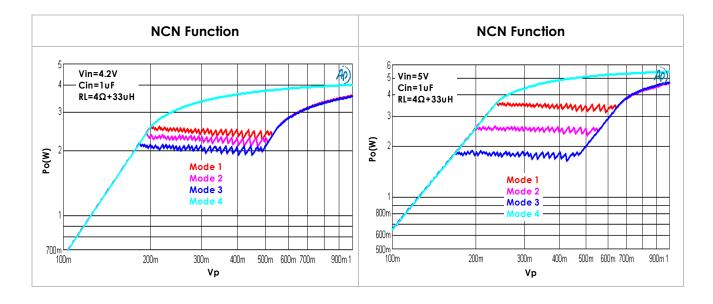

The non-crack-noise (NCN) function is enabled to prevent output signal from distortion when the input signal exceeds a threshold level. All these functions are performed automatically. AD51653 features four control modes, controlled by a one-wire pulse signal, to achieve different NCN mode setting.

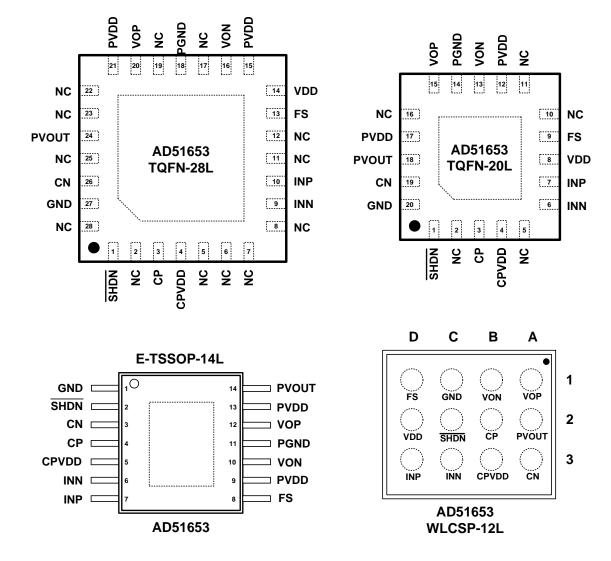

The output short circuit and over temperature protections provide auto-recovery feature. AD51653 is available in TQFN 4x4-28L, TQFN3x3-20L, E-TSSOP-14L and WLCSP-12L packages.

Elite Semiconductor Memory Technology Inc.

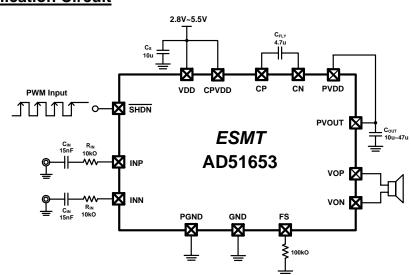

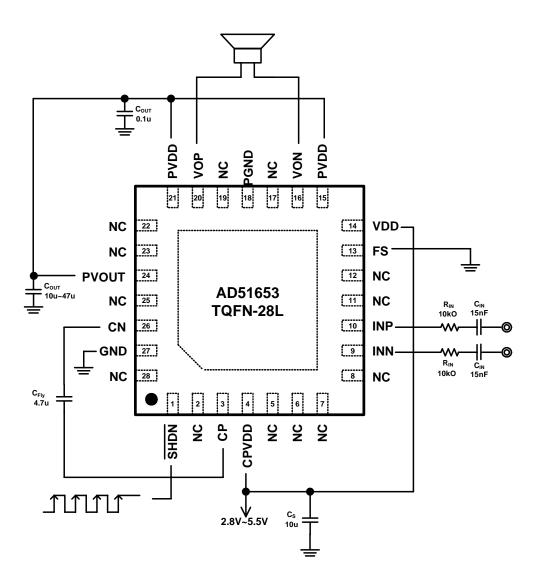

#### Simplified Application Circuit

#### Pin Assignments (Top View)

#### **Pin Description**

| NAME  | TQFN-28    | TQFN-20 | E-TSSOP-14 | WLCSP-12 | TYP | DESCRIPTION                                     |

|-------|------------|---------|------------|----------|-----|-------------------------------------------------|

| SHDN  | 1          | 1       | 2          | C2       | Ι   | Shutdown terminal (active low).                 |

| NC    | 2          | 2       | N/A        | N/A      | N/A | Not connected.                                  |

| СР    | 3          | 3       | 4          | B2       | I/O | Charge-pump flying capacitor positive terminal. |

| CPVDD | 4          | 4       | 5          | B3       | Р   | Charge-pump Supply.                             |

| NC    | 5, 6, 7, 8 | 5       | N/A        | N/A      | N/A | Not connected.                                  |

| INN   | 9          | 6       | 6          | C3       | Ι   | Negative input.                                 |

| INP   | 10         | 7       | 7          | D3       | Ι   | Positive input.                                 |

| NC    | 11, 12     | N/A     | N/A        | N/A      | N/A | Not connected.                                  |

| FS    | 13         | 9       | 8          | D1       | Ι   | Back-up pin, connect to GND or NC.              |

| VDD   | 14         | 8       | 9          | D2       | Р   | Analog Supply.                                  |

Elite Semiconductor Memory Technology Inc.

Publication Date: Aug. 2016 Revision: 0.4 2/21

# **ESMT**

## Preliminary

| PVDD  | 15          | 12    | N/A | N/A | Р                                       | Power Supply, connect to PVOUT.                 |

|-------|-------------|-------|-----|-----|-----------------------------------------|-------------------------------------------------|

| VON   | 16          | 13    | 10  | B1  | 0                                       | Negative amplifier output.                      |

| NC    | 17          | 10,11 | N/A | N/A | N/A                                     | Not connected.                                  |

| PGND  | 18          | 14    | 11  | N/A | Р                                       | Power ground.                                   |

| NC    | 19          | N/A   | N/A | N/A | N/A                                     | Not connected.                                  |

| VOP   | 20          | 15    | 12  | A1  | Р                                       | Positive amplifier output                       |

| PVDD  | 21          | 17    | 13  | N/A | Р                                       | Power Supply, connect to PVOUT.                 |

| NC    | 22, 23      | 16    | N/A | N/A | N/A                                     | Not connected.                                  |

| PVOUT | 24          | 18    | 14  | A2  | 0                                       | Charge-pump output.                             |

| NC    | 25          | N/A   | N/A | N/A | N/A                                     | Not connected.                                  |

| CN    | 26          | 19    | 3   | A3  | I/O                                     | Charge-pump flying capacitor negative terminal. |

| GND   | 27          | 20    | 1   | C1  | Р                                       | Analog ground.                                  |

| NC    | 28          | N/A   | N/A | N/A | N/A                                     | Not connected.                                  |

|       | Thermal pad |       |     | Р   | Must be soldered to PCB's ground plane. |                                                 |

## **Ordering Information**

| Product ID      | Package                      | Packing                      | Comments |

|-----------------|------------------------------|------------------------------|----------|

| AD51653-HI28NRR | TQFN-28L<br>(4mmx4mm)        | Tape/Reel<br>3K Units/Reel   | Green    |

| AD51653-HH20NRR | TQFN-20L<br>(3mmx3mm)        | Tape/Reel<br>5K Units/Reel   | Green    |

| AD51653-QG14NRR | E-TSSOP-14L                  | Tape/Reel<br>2.5K Units/Reel | Green    |

| AD51653-WL12NRR | WLCSP-12L<br>(1.48mmx1.31mm) | Tape/Reel<br>3K Units/Reel   | Green    |

#### Available Package

| Package Type | Device No. | θ <sub>JA</sub> (° C/W) | Exposed Thermal Pad |

|--------------|------------|-------------------------|---------------------|

| TQFN-28L     |            | 37(° C/W)               | Yes (Note 1)        |

| TQFN-20L     | AD51653    | 48(° C/W)               | Yes (Note 1)        |

| E-TSSOP-14L  |            | 38(° C/W)               | Yes (Note 1)        |

| WLCSP-12L    |            | 128(° C/W)              | No                  |

Note1: The thermal pad is at the bottom of package. To optimize the performance of thermal dissipation, solder the thermal pad to PCB's ground plane is suggested.

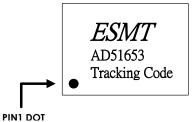

#### **Marking Information**

#### AD51653

TQFN-28L and E-TSSOP-14L Package Marking Information

Line 1 : LOGO

٠

Line 2 : Product No

Line 3 : Tracking Code

TQFN-20L Package Marking Information

Line 1 : LOGO Line 2 : Product No Line 3 : Tracking Code

• WLCSP-12L Package Marking Information

ABX : Product code %% : Tracking Code

Elite Semiconductor Memory Technology Inc.

## Absolute Maximum Ratings

| SYMBOL           | PARAMETER                                          | TEST CONDITIONS   | MIN  | MAX     | UNIT |

|------------------|----------------------------------------------------|-------------------|------|---------|------|

| VDD              | Supply voltage                                     | VDD, CPVDD        | -0.3 | 7       | V    |

| VI               | Interface pin voltage                              | SHDN, INN, INP    | -0.3 | VDD+0.3 | V    |

| T <sub>A</sub>   | Operating free-air temperature                     | erange            | -40  | 85      | °C   |

| TJ               | Operating junction temperature range               |                   | -40  | 150     | °C   |

| T <sub>stg</sub> | Storage temperature range                          |                   |      | 150     | °C   |

| ESD              | HBM protection voltage                             |                   |      |         | kV   |

| Latch-up         | +IT                                                |                   |      |         | mA   |

| Laton up         | -IT                                                |                   | -200 |         | mA   |

| RL               | Minimum Load Resistance (except WLCSP-12L package) |                   |      |         | Ω    |

|                  | Minimum Load Resistance for                        | WLCSP-12L package | 6.4  |         | Ω    |

### **Electrical Characteristics**

• T<sub>A</sub>=25°C (unless otherwise noted)

| SYMBOL                      | PARAMETER                                 | CONDITION                       | MIN | TYP | MAX  | UNIT |

|-----------------------------|-------------------------------------------|---------------------------------|-----|-----|------|------|

| VDD                         | Supply voltage                            |                                 | 2.8 |     | 5.5  | V    |

| Ι <sub>Q</sub>              | Quiescent supply current                  | VDD=3.6V, no input              |     | 3.5 | 10   | mA   |

| I <sub>SD</sub>             | Quiescent supply current in shutdown mode | VDD=3.6V, SHDN=0V               |     | 0.1 | 1    | μA   |

| V <sub>IH</sub>             | High-level Input Voltage                  | SHDN                            | 1.2 |     | VDD  | V    |

| V <sub>IL</sub>             | Low-level Input Voltage                   | SHDN                            | 0   |     | 0.35 | V    |

| I <sub>IH</sub>             | High-level Input Current                  | VDD=5.5V, Vi=5.8V               |     |     | 100  | μA   |

| I <sub>IL</sub>             | Low-level Input Current                   | VDD=5.5V, Vi=-0.3V              |     |     | 5    | μA   |

| Over temperature protection |                                           |                                 |     | 160 |      | °C   |

| Hysteresis t                | emperature                                |                                 |     | 135 |      | °C   |

| Vos                         | Output offset voltage                     | No load                         |     | 5   | 20   | mV   |

| R <sub>IN</sub>             | Input Resistance                          |                                 |     | 5   |      | kΩ   |

| f <sub>PWM</sub>            | Modulation Frequency                      | VDD=2.8V to 5.5V                | 240 | 300 | 360  | kHz  |

| PSRR                        | Power supply rejection                    | VDD=3.6V, Vpp_sin=0.2V, f=217Hz |     | -68 |      | dB   |

| FORR                        | ratio                                     | VDD=3.6V, Vpp_sin=0.2V, f=1kHz  |     | -68 |      | dB   |

## **Electrical Characteristics(continued)**

•  $T_A=25^{\circ}C$  (unless otherwise noted)

| SYMBOL           | PARAMETER                 | CONDITION                                               | MIN  | TYP  | MAX | UNIT |

|------------------|---------------------------|---------------------------------------------------------|------|------|-----|------|

|                  |                           | THD+N=10%, f=1kHz,                                      |      | 3    |     |      |

|                  |                           | $R_L$ =4 $\Omega$ +33 $\mu$ H, VDD=4.2V                 |      | 5    |     |      |

|                  |                           | THD+N=1%, f=1kHz,                                       |      | 2.6  |     |      |

|                  |                           | $R_L$ =4 $\Omega$ +33 $\mu$ H, VDD=4.2V                 |      | 2.0  |     |      |

|                  |                           | THD+N=10%, f=1kHz,<br>R <sub>L</sub> =8Ω+33μH, VDD=4.2V |      | 2.9  |     |      |

| Po               | Output power              |                                                         |      | 2.9  |     | w    |

| 10               |                           | THD+N=1%, f=1kHz,                                       |      | 2.3  |     | vv   |

|                  |                           | R <sub>L</sub> =8Ω+33μH, VDD=4.2V                       |      | 2.0  |     |      |

|                  |                           | THD+N=10%, f=1kHz,                                      |      | 2.7  |     |      |

|                  |                           | $R_L=8\Omega+33\mu H$ , VDD=4V                          |      | 2.1  |     |      |

|                  |                           | THD+N=1%, f=1kHz,                                       |      | 2.3  |     |      |

|                  |                           | $R_L=8\Omega+33\mu H$ , VDD=4V                          |      | 2.0  |     |      |

| THD+N            | Total harmonic distortion | VDD=3.6V, Po=0.3W                                       |      | 0.04 |     | %    |

| THD+N            | plus noise                | VDD=3.6V, Po=1W                                         |      | 0.04 |     | %    |

| Ton              | Wake-up time              | VDD=2.8V to 5.5V                                        |      | 35   | 50  | ms   |

| Vn               | Output integrated noise   | VDD=3.6V, Gain=27.5dB, a-weighted filter                |      | 130  |     | μV   |

| Charge-pu        | Imp                       |                                                         |      |      |     |      |

| PVOUT            | Output voltage            | Power-saving mode                                       |      | VDD  |     | V    |

| FVOOT            |                           | High power mode                                         |      | 6.5V |     | V    |

| I <sub>OUT</sub> | Maximum output current    |                                                         |      |      | 1   | А    |

| fcp              | Operating frequency       | VDD=2.8V to 5.5V                                        | 480  | 600  | 720 | kHz  |

| NCN              |                           |                                                         |      |      |     |      |

| T <sub>AT</sub>  | Attack time               | VDD=3.6V                                                |      | 27   |     | ms   |

| T <sub>RL</sub>  | Release time              | VDD=3.6V                                                |      | 1.8  |     | s    |

| A <sub>MAX</sub> | Maximum attenuation gain  | NCN enable (Mode 1~3)                                   |      | -8.7 |     | dB   |

| One wire p       | oulse control             |                                                         |      |      |     |      |

| T <sub>HI</sub>  | Program high time         |                                                         | 0.24 |      |     | μS   |

| T <sub>LO</sub>  | Program low time          |                                                         |      |      | 240 | μS   |

| T <sub>OFF</sub> | Low time to shutdown      |                                                         | 240  | 300  | 360 | μS   |

ESMT

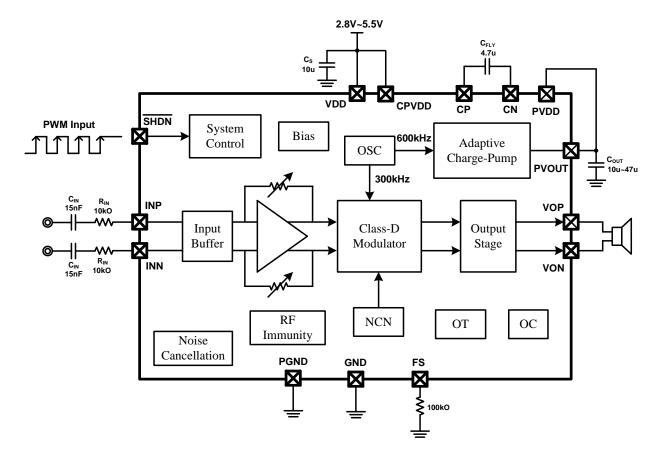

### **Functional Block Diagram**

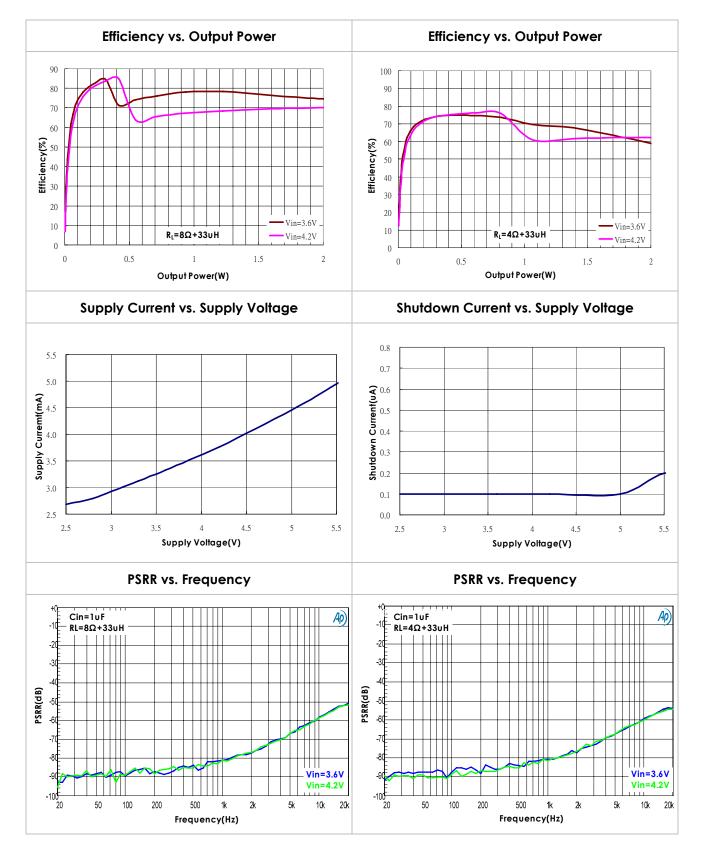

## **Typical Characteristics**

## **Typical Characteristics**

Elite Semiconductor Memory Technology Inc.

Publication Date: Aug. 2016 Revision: 0.4 9/21

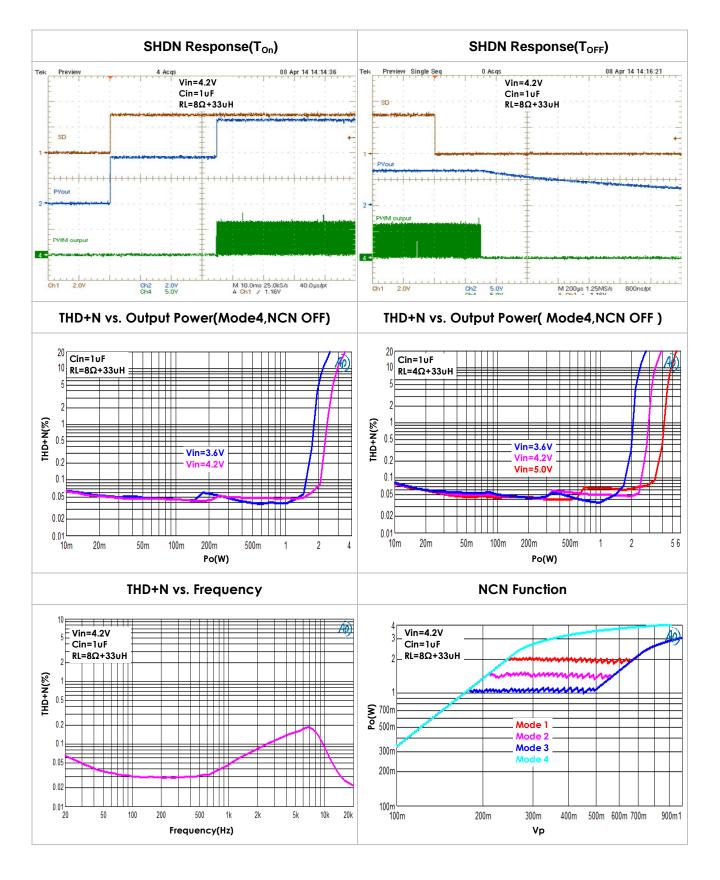

## **Typical Characteristics**

#### **Operation Descriptions**

#### • Amplifier Function with Charge-Pump

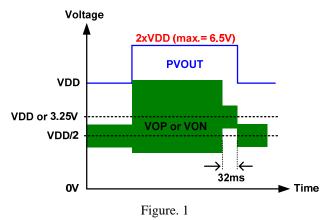

AD51653 is a class-D power amplifier with an adaptive charge-pump boost circuit. With the help of charge-pump, AD51653 can delivery 2.4W output power at 4V supply. As the amplitude of output signal is smaller than a quarter of VDD, AD51653 works in power-saving mode, the class D amplifier is powered at VDD. As the amplitude of output signal is larger than a quarter of VDD, AD51653 works in high-power mode, and charge-pump output is regulated to 2xVDD or maximum 6.5V. Figure 1 shows the function of adaptive charge-pump circuit operation. When working under high-power mode, once the output signal amplitude drops below a quarter of VDD, the charge-pump circuit returns to power-saving mode after 32ms.

The soft-start time of charge-pump, output building from 0V to VDD, is about 0.5ms. Under power-saving mode, charge-pump will not function in switching status to save power, and PVOUT will equal to VDD. As charge-pump switch to high-power mode, the power switches are fully turned on to charge output capacitor. Normally, it takes about 20us for charge-pump to build from VDD to 6.5V.

#### NCN Function

Large input signal or lower supply voltage will easily lead to distortion of output signal. The distortion of crack signal will also cause perpetual damage to the speaker. AD51653 features a non-crack noise (NCN) function to prevent output signal from distortion to provide a better listening experience to user and protect the speaker from overload. NCN function can automatically adjust system gain to let the output signal remain smooth by detecting the distortion level of output signal and keeping the distortion level at NCN limit level with lower THD+N performance.

| VDD=4.2V/8ohm load |           |                     |              |  |  |  |

|--------------------|-----------|---------------------|--------------|--|--|--|

| Mode               | Gain (dB) | NCN Limit Level @Po | NCN Function |  |  |  |

| 1                  | 27.5      | 2W                  | ON           |  |  |  |

| 2                  | 27.5      | 1.5W                | ON           |  |  |  |

| 3                  | 27.5      | 1W                  | ON           |  |  |  |

| 4                  | 27.5      | -                   | OFF          |  |  |  |

## Preliminary

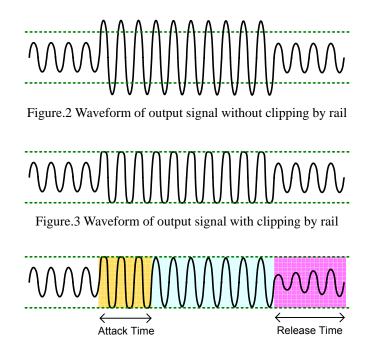

Figure 2 shows the ideal output waveform without clipping by rail. Figure 3 shows the realistic output signal with clipping by rail. Figure 4 shows the output waveform with NCN function enabled. When output signal is distorted, gain immediately decreases by one step. Then, gain will decrease incrementally every 27ms, which is the attack time. The maximum attenuation of gain is -8.7dB at NCN function enable (mode 1~3). Once the output signal is undistorted, the gain level will remain unchanged until the input signal is lowered. As output is lowered, the attenuated gain steps is released incrementally every 1.8s, which is the release time.

Figure.4 Waveform of output signal with NCN ON

#### • Thermal protection

If the internal junction temperature is higher than 160°C, the outputs of loudspeaker drivers is disabled and be kept low. The temperature at which the AD51653 returns to normal operation is about 135°C. The variation of protected temperature is about 10%.

#### • Short-circuit protection

To protect loudspeaker drivers from over-current damage, AD51653 has a built-in short-circuit protection circuit. When the wires connected to loudspeakers are shorted to each other, to GND, or to PVDD, overload detectors may activate. Once one of the positive and negative half bridge overload detectors is activated, the amplifier outputs turns off and the protection latch is engaged. The short circuit protection latch has auto-recovery function every 220ms.

#### • Under-voltage detection

When the VDD voltage is lower than 2.4V, amplifiers is disabled and the output kept low. Otherwise, AD51653 returns to normal operation.

#### • Operating Mode Selection

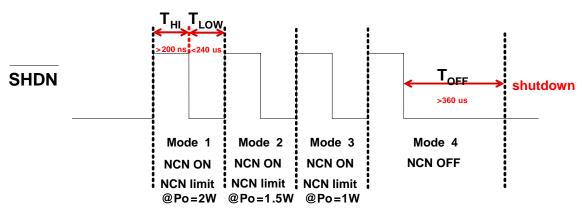

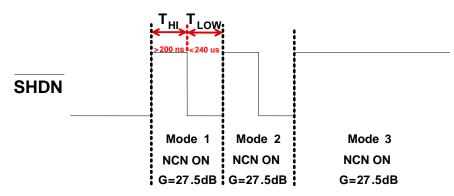

AD51653 has four operation modes which can be selected by one-wire control pulse. The chip enters Mode 1 when SHDN/ pin pulled to high. The NCN function to ON and NCN limit level at Po=2W. By continuing to supply low  $\rightarrow$  high at SHDN/ pin, the NCN will be set to ON still and NCN limit level at Po=1.5W. Be mindful of T<sub>HI</sub> and T<sub>LOW</sub>, as T<sub>HI</sub> should not be shorter than 200ns and T<sub>LOW</sub> should not be longer than 240µs. As a result, given an appropriate pulse at SHDN/ pin, the user can easily choose the operating mode. Note that these four modes will repeat as the pulse at SHDN/ pin continues to give (Mode1  $\rightarrow$  Mode2  $\rightarrow$  Mode3  $\rightarrow$  Mode4  $\rightarrow$  Mode1 ...). Figure 5 shows the one-wire pulse control function.

Figure.5 One-Wire Pulse Control

Figure 6 shows an example of entering mode 3. If shutdown is desired, SHDN/ should be pulled to low for more than  $300\mu$ s, and the chip will enter shutdown mode, resetting mode selection.

Figure.6 One-Wire Pulse Control Entering Mode 3

#### Gain Setting

The total gain of the audio amplifier is set by Rin, according to the following equation (a).

$$Gain = \frac{360k\Omega}{5k + R_{in}} \left( \frac{V}{V} \right) \dots \dots (a)$$

#### **Application information**

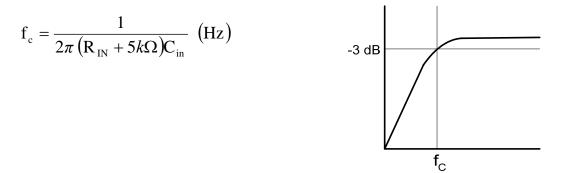

#### • Input capacitors (C<sub>IN</sub>) and input resistors

Performance at low frequency (bass) is affected by the corner frequency ( $f_c$ ) of the high-pass filter, which consists of an input resistor and an input capacitor ( $C_{IN}$ ). The resistance of input resistors is different at different gain setting. The respective gain and input resistance are listed in Table 1. For fully differential amplifiers, component matching is important for PSRR, CMRR, and even-order distortion cancellation. It is recommended to use 1% tolerance value of  $R_{IN}$  and  $C_{IN}$  to get better performance.

#### Charge-pump capacitors (C<sub>OUT</sub> and C<sub>FLY</sub>)

The capacitance and ESR of  $C_{OUT}$  directly affect the charge-pump output voltage ripple, thus affect amplifier's performance. X5R or X7R ceramic type capacitor with capacitance of 10µF and low ESR is recommended for  $C_{OUT}$ .

Flying capacitor directly affects charge-pump's load regulation and output capability. X5R or X7R ceramic type capacitor with capacitance of  $4.7\mu$ F and low ESR is recommended for C<sub>FLY</sub>.

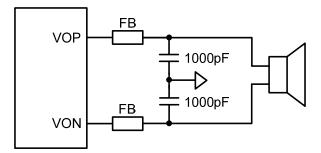

#### • Ferrite Bead Selection

If the traces between AD51653 and speaker are short, the ferrite bead filters can reduce the high frequency emissions to meet FCC requirements. A ferrite bead that has very low impedance at low frequency and high impedance at high frequency (above 1MHz) is recommended. The impedance of the ferrite bead can be used along with a small capacitor with a value around 1000pF to reduce the frequency spectrum of the signal to an acceptable level.

Figure 8. Typical Ferrite Bead Filter

**ESMT**

### **Application Circuit Example**

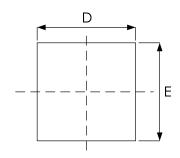

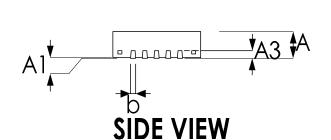

Package Outline Drawing TQFN-28L (4x4 mm)

**TOP VIEW**

**BOTTOM VIEW**

| Symbol | Dimension in mm |      |  |  |

|--------|-----------------|------|--|--|

| Symbol | Min             | Max  |  |  |

| А      | 0.70            | 0.80 |  |  |

| A1     | 0.00            | 0.05 |  |  |

| A 3    | 0.20 REF.       |      |  |  |

| b      | 0.15            | 0.25 |  |  |

| D      | 4.00            | BSC  |  |  |

| E      | 4.00 BSC        |      |  |  |

| е      | 0.40 BSC        |      |  |  |

| L      | 0.30            | 0.50 |  |  |

| Exposed pad |                 |      |  |  |  |

|-------------|-----------------|------|--|--|--|

|             | Dimension in mm |      |  |  |  |

|             | Min             | Max  |  |  |  |

| D2          | 2.5             | 2.65 |  |  |  |

| E2          | 2.5             | 2.65 |  |  |  |

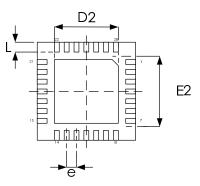

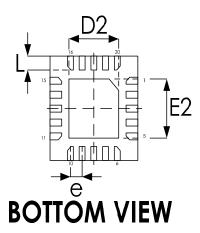

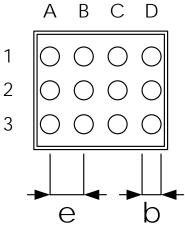

Package Outline Drawing TQFN-20L (3x3 mm)

**TOP VIEW**

| Symph ol | Dimension in mm |       |  |  |

|----------|-----------------|-------|--|--|

| Symbol   | Min             | Max   |  |  |

| А        | 0.70            | 0.85  |  |  |

| A1       | 0.00            | 0.05  |  |  |

| A3       | 0.20 REF.       |       |  |  |

| b        | 0.15            | 0.25  |  |  |

| D        | 2.924           | 3.076 |  |  |

| Е        | 2.924           | 3.076 |  |  |

| е        | 0.40            | BSC   |  |  |

| L        | 0.324           | 0.476 |  |  |

| Exposed pad     |      |      |  |  |  |

|-----------------|------|------|--|--|--|

| Dimension in mm |      |      |  |  |  |

| Min Max         |      |      |  |  |  |

| D2              | 1.40 | 1.60 |  |  |  |

| E2              | 1.40 | 1.60 |  |  |  |

Preliminary

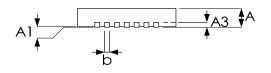

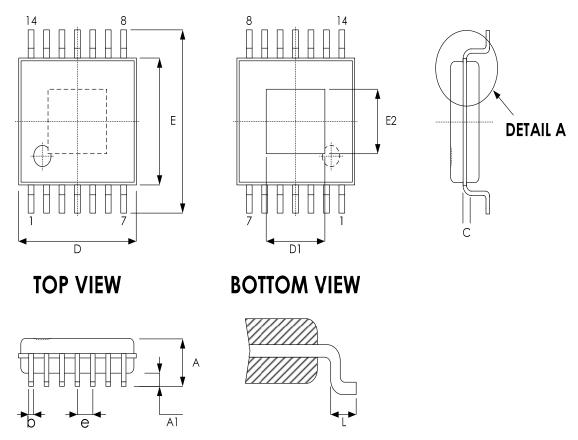

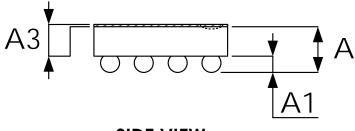

Package Outline Drawing E-TSSOP-14L

**SIDE VIEW**

DETAIL A

| Symbol | Dimension in mm |      |  |

|--------|-----------------|------|--|

|        | Min             | Max  |  |

| А      |                 | 1.20 |  |

| A1     | 0.05            | 0.15 |  |

| b      | 0.19            | 0.30 |  |

| D      | 4.90            | 5.10 |  |

| E      | 4.30            | 4.50 |  |

| E1     | 6.40 BSC        |      |  |

| е      | 0.65 BSC        |      |  |

| L      | 0.5 0.75        |      |  |

| Exposed | pad |

|---------|-----|

|         |     |

|    | Dimension in mm |      |

|----|-----------------|------|

|    | Min             | Max  |

| D1 | 1.92            | 2.54 |

| E2 | 1.67            | 2.29 |

Elite Semiconductor Memory Technology Inc.

Preliminary

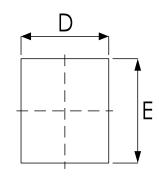

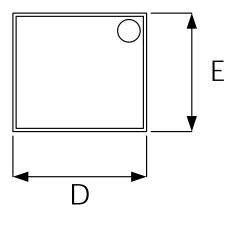

## Package Outline Drawing WLCSP-12L (1.48mm x 1.31mm)

**TOP VIEW**

**BOTTOM VIEW**

**SIDE VIEW**

| Symbol | Dimension in mm |  |

|--------|-----------------|--|

|        | Typical         |  |

| А      | 0.536           |  |

| A1     | 0.16            |  |

| A3     | 0.025           |  |

| b      | 0.175           |  |

| D      | 1.48            |  |

| Е      | 1.31            |  |

| е      | 0.35            |  |

#### Elite Semiconductor Memory Technology Inc.

## **Revision History**

| Revision | Date       | Description                     |

|----------|------------|---------------------------------|

| 0.1      | 2015.04.02 | Preliminary version.            |

| 0.2      | 2015.05.07 | Update gain setting in page 13. |

| 0.3      | 2015.12.24 | Update One-Wire Pulse timing    |

| 0.4      | 2016.08.02 | Update Application Circuit      |

## **Important Notice**

All rights reserved.

No part of this document may be reproduced or duplicated in any form or by any means without the prior permission of ESMT.

The contents contained in this document are believed to be accurate at the time of publication. ESMT assumes no responsibility for any error in this document, and reserves the right to change the products or specification in this document without notice.

The information contained herein is presented only as a guide or examples for the application of our products. No responsibility is assumed by ESMT for any infringement of patents, copyrights, or other intellectual property rights of third parties which may result from its use. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of ESMT or others.

Any semiconductor devices may have inherently a certain rate of failure. To minimize risks associated with customer's application, adequate design and operating safeguards against injury, damage, or loss from such failure, should be provided by the customer when making application designs.

ESMT's products are not authorized for use in critical applications such as, but not limited to, life support devices or system, where failure or abnormal operation may directly affect human lives or cause physical injury or property damage. If products described here are to be used for such kinds of application, purchaser must do its own quality assurance testing appropriate to such applications.