# 18W Stereo Class-D Audio Amplifier with Power Limit

#### **Features**

- Single supply voltage

10 ~ 26V for loudspeaker driver

Built-in LDO output 3.3V for others

- Loudspeaker power from 24V supply

SE Mode: 8 W/ch into 8Ω @ 1% THD+N for stereo

SE Mode: 10 W/ch into  $8\Omega$  @10% THD+N for stereo

Loudspeaker power from 24V supply SE Mode:14 W/ch into 4Ω @ 1% THD+N for stereo

SE Mode:18 W/ch into 4 $\Omega$  @ 10% THD+N for stereo

BTL mode: 38W into  $8\Omega$  @ 10% THD+N for Mono

- Single-ended analog inputs

- Single-ended outputs

- Four selectable, fixed gain settings

- Internal oscillator

- Short-circuit protection with auto recovery

- Thermal protection with auto recovery

- Under-voltage detection

- Pop noise and click noise reduction

- Adjustable power limit function for speaker protection

MONO mode selection for BTL operation

### **Applications**

- TV audio

- Boom-Box

- Powered speaker

### **Description**

The AD52583 is a high efficiency stereo class-D audio amplifier with adjustable power limit function. The loudspeaker driver operates from 10~26V supply voltage and analog circuit operates at 3.3V supply voltage. It can deliver 18W/ch output power into  $4\Omega$  loudspeaker without external heat sink during play music. AD52583 provides mono mode application, it can deliver 38W into  $8\Omega$  loudspeaker. The adjustable power limit function allows user to set a voltage rail lower than half of 3.3V to limit the amount of current through the speaker.

The gain of the amplifier is controlled by two gain select pins. The gain selections are 20, 26, 32, 36 dR

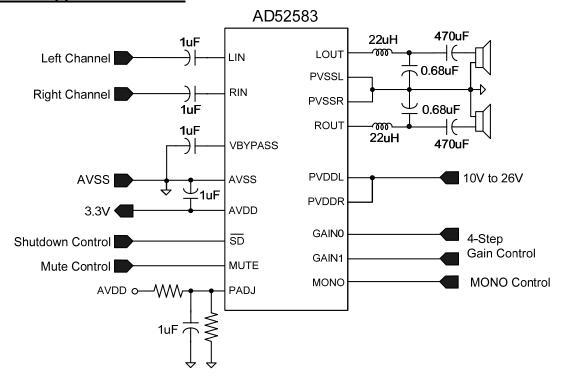

# **Simplified Application Circuit**

Elite Semiconductor Memory Technology Inc./Elite MicroPower Inc.

Publication Date: Jul. 2012 Revision: 1.0 1/19

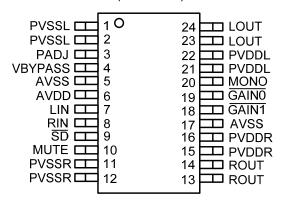

### **Pin Assignments**

# TSSOP PACKAGE (TOP VIEW)

# **Pin Description**

| PIN         | NAME    | TYP | DESCRIPTION                                    | CHARACTERISTIC                                          |

|-------------|---------|-----|------------------------------------------------|---------------------------------------------------------|

| 1,2         | PVSSL   | Р   | High-voltage ground for left channel           |                                                         |

| 3           | PADJ    | I   | Power limit level input, connect to AVSS for   | Give V(PADJ) < VCAP to                                  |

|             |         |     | no power limit                                 | set power limit level.                                  |

| 4           | VBYPASS | 0   | Reference for amplifier inputs                 | Biased at PVDD/14.6                                     |

| 5           | AVSS    | Р   | Low-voltage analog ground                      |                                                         |

| 6           | AVDD    | 0   | 3.3V Regulated output                          |                                                         |

| 7           | LIN     | I   | Audio input for left channel                   |                                                         |

| 8           | RIN     | I   | Audio input for right channel                  |                                                         |

| 9           | SD      | I   | Shutdown signal. Active low                    | Schmitt trigger TTL input buffer, internally pull low.  |

| 10          | MUTE    | I   | Mute signal.                                   | Schmitt trigger TTL input buffer, internally pull low.  |

| 11,12       | PVSSR   | Р   | High-voltage ground for right channel          |                                                         |

| 13,14       | ROUT    | 0   | Right channel output                           |                                                         |

| 15,16       | PVDDR   | Р   | High-voltage power supply for right channel    |                                                         |

| 17          | AVSS    | Р   | Low-voltage analog ground                      |                                                         |

| 18          | GAIN1   | I   | Gain select most-significant bit. Active low.  | Schmitt trigger TTL input buffer, internally pull high. |

| 19          | GAIN0   | ı   | Gain select least-significant bit. Active low. | Schmitt trigger TTL input buffer, internally pull high. |

| 20          | MONO    | I   | Mana mada quitab Activa bigh                   | Schmitt trigger TTL input                               |

|             |         |     | Mono mode switch. Active high.                 | buffer, internally pull low.                            |

| 21,22       | PVDDL   | Р   | High-voltage power supply for left channel     |                                                         |

| 23,24       | LOUT    | 0   | Left channel output                            |                                                         |

| Thermal Pad |         | Р   | Must be soldered to PCB's ground plane         |                                                         |

Elite Semiconductor Memory Technology Inc./Elite MicroPower Inc.

Publication Date: Jul. 2012 Revision: 1.0 **2/19**

## **Ordering Information**

| Product ID      | Package     | Packing                                | Comments |

|-----------------|-------------|----------------------------------------|----------|

| AD52583-QG24NAT | E-TSSOP 24L | 62 Units/ Tube<br>100 Tubes/ Small Box | Green    |

## **Available Package**

| Package Type | Device No. | θ <sub>JA</sub> (° C/W) | Exposed Thermal Pad |

|--------------|------------|-------------------------|---------------------|

| E-TSSOP 24L  | AD52583    | 32.8                    | Yes (Note 1)        |

Note1: The thermal pad is at the bottom of package. To optimize the performance of thermal dissipation, solder the thermal pad to PCB's ground plane is suggested.

# **Marking Information**

### AD52583

Marking Information

Line 1: LOGO

Line 2: Product No

Line 3: Tracking Code

Publication Date: Jul. 2012 Revision: 1.0 3/19