# 800 MHz, 50 mW Current Feedback Amplifier

AD8001

#### **FEATURES**

Excellent Video Specifications ( $R_L$  = 150  $\Omega$ , G = +2) Gain Flatness 0.1 dB to 100 MHz 0.01% Differential Gain Error 0.025° Differential Phase Error Low Power

5.5 mA Max Power Supply Current (55 mW)

High Speed and Fast Settling

880 MHz, -3 dB Bandwidth (G = +1)

440 MHz, -3 dB Bandwidth (G = +2)

1200 V/ $\mu s$  Slew Rate

10 ns Settling Time to 0.1%

**Low Distortion**

$-65 \text{ dBc THD, } f_C = 5 \text{ MHz}$

33 dBm Third Order Intercept,  $F_1 = 10 \text{ MHz}$

-66 dB SFDR, f = 5 MHz

**High Output Drive**

70 mA Output Current

Drives Up to 4 Back-Terminated Loads (75  $\Omega$  Each) While Maintaining Good Differential Gain/Phase Performance (0.05%/0.25°)

#### **APPLICATIONS**

A-to-D Drivers

Video Line Drivers

Professional Cameras

Video Switchers

Special Effects

RF Receivers

#### **GENERAL DESCRIPTION**

The AD8001 is a low power, high speed amplifier designed to operate on  $\pm 5$  V supplies. The AD8001 features unique

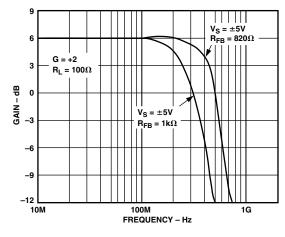

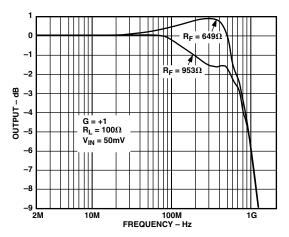

Figure 1. Frequency Response of AD8001

## REV. D

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective companies.

#### FUNCTIONAL BLOCK DIAGRAMS

8-Lead PDIP (N-8), 5-Lead SOT-23-5 CERDIP (Q-8) and SOIC (R-8) (RT-5)

NC = NO CONNECT

transimpedance linearization circuitry. This allows it to drive video loads with excellent differential gain and phase performance on only 50 mW of power. The AD8001 is a current feedback amplifier and features gain flatness of 0.1 dB to 100 MHz while offering differential gain and phase error of 0.01% and 0.025°. This makes the AD8001 ideal for professional video electronics such as cameras and video switchers. Additionally, the AD8001's low distortion and fast settling make it ideal for buffer high speed A-to-D converters.

The AD8001 offers low power of 5.5 mA max ( $V_S = \pm 5~V$ ) and can run on a single +12 V power supply, while being capable of delivering over 70 mA of load current. These features make this amplifier ideal for portable and battery-powered applications where size and power are critical.

The outstanding bandwidth of 800 MHz along with 1200 V/ $\mu$ s of slew rate make the AD8001 useful in many general-purpose high speed applications where dual power supplies of up to  $\pm 6$  V and single supplies from 6 V to 12 V are needed. The AD8001 is available in the industrial temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C.

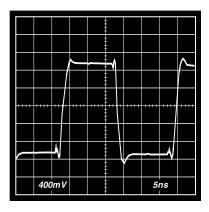

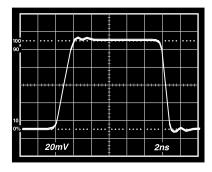

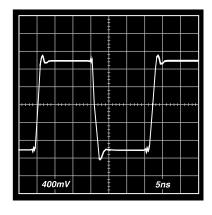

Figure 2. Transient Response of AD8001; 2 V Step, G = +2

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © 2003 Analog Devices, Inc. All rights reserved.

## **AD8001\* Product Page Quick Links**

Last Content Update: 11/01/2016

## Comparable Parts

View a parametric search of comparable parts

## Evaluation Kits <a> □</a>

Universal Evaluation Board for Single High Speed Operational Amplifiers

## Documentation <a>□</a>

## **Application Notes**

- AN-253: Find Op Amp Noise with Spreadsheet

- AN-257: Careful Design Tames High Speed Op Amps

- AN-356: User's Guide to Applying and Measuring Operational Amplifier Specifications

- AN-358: Noise and Operational Amplifier Circuits

- AN-417: Fast Rail-to-Rail Operational Amplifiers Ease Design Constraints in Low Voltage High Speed Systems

- AN-649: Using the Analog Devices Active Filter Design Tool

- AN-692: Universal Precision Op Amp Evaluation Board

#### **Data Sheet**

- AD8001: 800 MHz, 50mW Current Feedback Amplifier Data Sheet

- · AD8001: Military Data Sheet

## **User Guides**

- UG-755: 8-Lead SOIC Amplifier Evaluation Board User Guide

- UG-838: Evaluation Board for Single, High Speed Op Amps Offered in 5-Lead SOT-23 and 6-Lead SOT-23 Packages

## Tools and Simulations

- · Analog Filter Wizard

- · Analog Photodiode Wizard

- AD8001 SPICE Macro Model

## Reference Materials -

## **Product Selection Guide**

• High Speed Amplifiers Selection Table

## **Tutorials**

- MT-034: Current Feedback (CFB) Op Amps

- MT-051: Current Feedback Op Amp Noise Considerations

- MT-057: High Speed Current Feedback Op Amps

- MT-059: Compensating for the Effects of Input Capacitance on VFB and CFB Op Amps Used in Current-to-Voltage Converters

## Design Resources <a>□</a>

- · AD8001 Material Declaration

- · PCN-PDN Information

- · Quality And Reliability

- · Symbols and Footprints

## Discussions 🖳

View all AD8001 EngineerZone Discussions

## Sample and Buy -

Visit the product page to see pricing options

## Technical Support -

Submit a technical question or find your regional support number

<sup>\*</sup> This page was dynamically generated by Analog Devices, Inc. and inserted into this data sheet. Note: Dynamic changes to the content on this page does not constitute a change to the revision number of the product data sheet. This content may be frequently modified.

# $\label{eq:continuous} \textbf{AD8001-SPECIFICATIONS} \ \ (@\ \textbf{T}_A = +\ 25^{\circ}\textbf{C},\ \textbf{V}_S = \pm\ 5\ \textbf{V},\ \textbf{R}_L = 100\ \Omega,\ \text{unless otherwise noted.})$

| Model                                                                                             |                                      | Conditions                                                                                                                                                                                                                                                                                                 | Min                                    | AD8001A<br>Typ                         | Max             | Unit                                          |

|---------------------------------------------------------------------------------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|----------------------------------------|-----------------|-----------------------------------------------|

| DYNAMIC PERFORMANCE  -3 dB Small Signal Bandwidth,                                                | N Package<br>R Package<br>RT Package | $G = +2$ , < 0.1 dB Peaking, $R_F = 750 \Omega$<br>$G = +1$ , < 1 dB Peaking, $R_F = 1 k\Omega$<br>$G = +2$ , < 0.1 dB Peaking, $R_F = 681 \Omega$<br>$G = +1$ , < 0.1 dB Peaking, $R_F = 845 \Omega$<br>$G = +2$ , < 0.1 dB Peaking, $R_F = 768 \Omega$<br>$G = +1$ , < 0.1 dB Peaking, $R_F = 1 k\Omega$ | 350<br>650<br>350<br>575<br>300<br>575 | 440<br>880<br>440<br>715<br>380<br>795 |                 | MHz<br>MHz<br>MHz<br>MHz<br>MHz<br>MHz<br>MHz |

| Bandwidth for 0.1 dB Flatness                                                                     | N Package<br>R Package<br>RT Package | $G = +2$ , $R_F = 750 \Omega$<br>$G = +2$ , $R_F = 681 \Omega$<br>$G = +2$ , $R_F = 768 \Omega$                                                                                                                                                                                                            | 85<br>100<br>120                       | 110<br>125<br>145                      |                 | MHz<br>MHz<br>MHz                             |

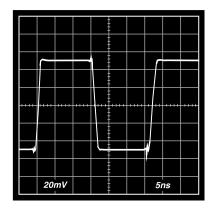

| Slew Rate                                                                                         | KI I ackage                          | $G = +2, V_0 = 2 \text{ V Step}$<br>$G = -1, V_0 = 2 \text{ V Step}$                                                                                                                                                                                                                                       | 800<br>960                             | 1000<br>1200                           |                 | V/μs<br>V/μs                                  |

| Settling Time to 0.1%<br>Rise and Fall Time                                                       |                                      | $G = -1$ , $V_O = 2$ V Step<br>$G = +2$ , $V_O = 2$ V Step, $R_F = 649 \Omega$                                                                                                                                                                                                                             |                                        | 10<br>1.4                              |                 | ns<br>ns                                      |

| NOISE/HARMONIC PERFORM<br>Total Harmonic Distortion                                               | IANCE                                | $f_C = 5 \text{ MHz}, V_O = 2 \text{ V p-p}$<br>$G = +2, R_I = 100 \Omega$                                                                                                                                                                                                                                 |                                        | -65                                    |                 | dBc                                           |

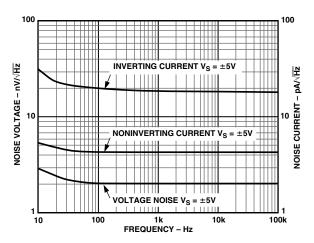

| Input Voltage Noise Input Current Noise                                                           |                                      | f = 10 kHz<br>f = 10 kHz, +In<br>-In                                                                                                                                                                                                                                                                       |                                        | 2.0<br>2.0<br>18                       |                 | $nV/\sqrt{Hz}$ $pA/\sqrt{Hz}$ $pA/\sqrt{Hz}$  |

| Differential Gain Error Differential Phase Error Third Order Intercept 1 dB Gain Compression SFDR |                                      | NTSC, $G = +2$ , $R_L = 150 \Omega$<br>NTSC, $G = +2$ , $R_L = 150 \Omega$<br>f = 10  MHz<br>f = 10  MHz<br>f = 5  MHz                                                                                                                                                                                     |                                        | 0.01<br>0.025<br>33<br>14<br>-66       | 0.025<br>0.04   | % Degree dBm dBm dB                           |

| DC PERFORMANCE<br>Input Offset Voltage                                                            |                                      | $T_{MIN}$ - $T_{MAX}$                                                                                                                                                                                                                                                                                      |                                        | 2.0                                    | 5.5<br>9.0      | mV<br>mV                                      |

| Offset Drift  -Input Bias Current  +Input Bias Current                                            |                                      | $T_{MIN}$ - $T_{MAX}$                                                                                                                                                                                                                                                                                      |                                        | 10<br>5.0<br>3.0                       | 25<br>35<br>6.0 | μV/°C<br>±μΑ<br>±μΑ                           |

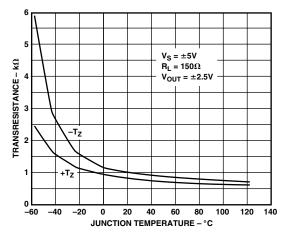

| Open-Loop Transresistance                                                                         |                                      | $T_{MIN}-T_{MAX}$ $V_{O} = \pm 2.5 \text{ V}$ $T_{MIN}-T_{MAX}$                                                                                                                                                                                                                                            | 250<br>175                             | 900                                    | 10              | ±μΑ<br>±μΑ<br>kΩ<br>kΩ                        |

| INPUT CHARACTERISTICS Input Resistance                                                            |                                      | +Input<br>-Input                                                                                                                                                                                                                                                                                           |                                        | 10<br>50                               |                 | $M\Omega$                                     |

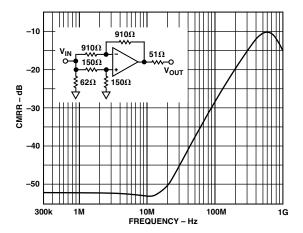

| Input Capacitance<br>Input Common-Mode Voltage I<br>Common-Mode Rejection Ratio                   |                                      | +Input                                                                                                                                                                                                                                                                                                     |                                        | 1.5<br>3.2                             |                 | pF<br>±V                                      |

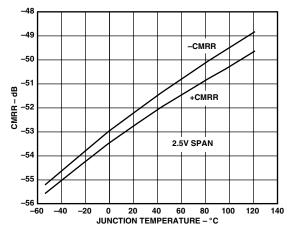

| Offset Voltage -Input Current +Input Current                                                      |                                      | $V_{CM} = \pm 2.5 \text{ V}$<br>$V_{CM} = \pm 2.5 \text{ V}, T_{MIN} - T_{MAX}$<br>$V_{CM} = \pm 2.5 \text{ V}, T_{MIN} - T_{MAX}$                                                                                                                                                                         | 50                                     | 54<br>0.3<br>0.2                       | 1.0<br>0.7      | dB<br>μΑ/V<br>μΑ/V                            |

| OUTPUT CHARACTERISTICS Output Voltage Swing Output Current Short Circuit Current                  |                                      | $R_{L} = 150 \Omega$ $R_{L} = 37.5 \Omega$                                                                                                                                                                                                                                                                 | 2.7<br>50<br>85                        | 3.1<br>70<br>110                       |                 | ±V<br>mA<br>mA                                |

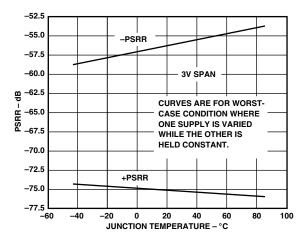

| POWER SUPPLY Operating Range Quiescent Current Power Supply Rejection Ratio  -Input Current       |                                      | $T_{MIN}$ - $T_{MAX}$<br>+ $V_S$ = +4 V to +6 V, - $V_S$ = -5 V<br>- $V_S$ = -4 V to -6 V, + $V_S$ = +5 V<br>$T_{MIN}$ - $T_{MAX}$                                                                                                                                                                         | ±3.0<br>60<br>50                       | 5.0<br>75<br>56<br>0.5                 | ±6.0<br>5.5     | V<br>mA<br>dB<br>dB<br>μA/V                   |

| +Input Current                                                                                    |                                      | $T_{MIN}$ $T_{MAX}$ $T_{MIN}$                                                                                                                                                                                                                                                                              |                                        | 0.5                                    | 0.5             | μΑ/V<br>μΑ/V                                  |

Specifications subject to change without notice.

-2- REV. D

#### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| Supply Voltage                                     |

|----------------------------------------------------|

| Internal Power Dissipation @ 25°C <sup>2</sup>     |

| PDIP Package (N)                                   |

| SOIC (R)                                           |

| 8-Lead CERDIP1.1 W                                 |

| SOT-23-5 Package (RT)                              |

| Input Voltage (Common Mode) $\dots \pm V_S$        |

| Differential Input Voltage ±1.2 V                  |

| Output Short Circuit Duration                      |

| Observe Power Derating Curves                      |

| Storage Temperature Range N, R65°C to +125°C       |

| Operating Temperature Range (A Grade)40°C to +85°C |

| Lead Temperature Range (Soldering 10 sec) 300°C    |

|                                                    |

#### NOTES

Commiss Vales as

<sup>1</sup>Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

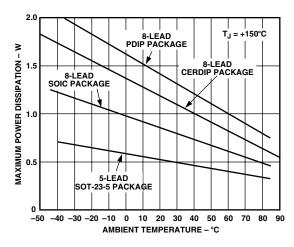

<sup>2</sup>Specification is for device in free air: 8-Lead PDIP Package: θ<sub>JA</sub> = 90°C/W 8-Lead SOIC Package: θ<sub>JA</sub> = 155°C/W 8-Lead CERDIP Package: θ<sub>JA</sub> = 110°C/W 5-Lead SOT-23-5 Package: θ<sub>JA</sub> = 260°C/W

#### MAXIMUM POWER DISSIPATION

The maximum power that can be safely dissipated by the AD8001 is limited by the associated rise in junction temperature. The maximum safe junction temperature for plastic encapsulated devices is determined by the glass transition temperature of the plastic, approximately 150°C. Exceeding this limit temporarily may cause a shift in parametric performance due to a change in the stresses exerted on the die by the package. Exceeding a junction temperature of 175°C for an extended period can result in device failure.

While the AD8001 is internally short circuit protected, this may not be sufficient to guarantee that the maximum junction temperature (150°C) is not exceeded under all conditions. To ensure proper operation, it is necessary to observe the maximum power derating curves.

Figure 3. Plot of Maximum Power Dissipation vs. Temperature

#### **ORDERING GUIDE**

10 6 17

| Model            | Temperature<br>Range | Package<br>Description | Package<br>Option | Branding |  |

|------------------|----------------------|------------------------|-------------------|----------|--|

| AD8001AN         | −40°C to +85°C       | 8-Lead PDIP            | N-8               |          |  |

| AD8001AQ         | −55°C to +125°C      | 8-Lead CERDIP          | Q-8               |          |  |

| AD8001AR         | −40°C to +85°C       | 8-Lead SOIC            | R-8               |          |  |

| AD8001AR-REEL    | −40°C to +85°C       | 13" Tape and REEL      | R-8               |          |  |

| AD8001AR-REEL7   | −40°C to +85°C       | 7" Tape and REEL       | R-8               |          |  |

| AD8001ART-REEL   | −40°C to +85°C       | 13" Tape and REEL      | RT-5              | HEA      |  |

| AD8001ART-REEL7  | −40°C to +85°C       | 7" Tape and REEL       | RT-5              | HEA      |  |

| AD8001ACHIPS     | −40°C to +85°C       | Die Form               |                   |          |  |

| 5962-9459301MPA* | −55°C to +125°C      | 8-Lead CERDIP          | Q-8               |          |  |

<sup>\*</sup>Standard Military Drawing Device.

#### CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD8001 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

REV. D \_3\_

# **AD8001—Typical Performance Characteristics**

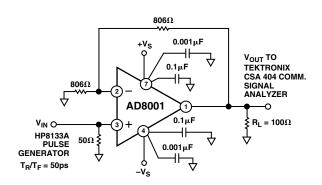

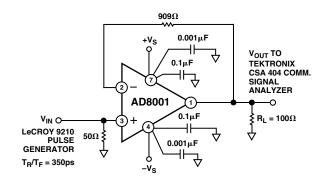

TPC 1. Test Circuit, Gain = +2

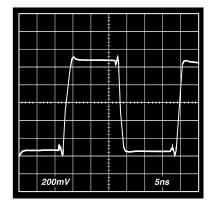

TPC 2. 1 V Step Response, G = +2

TPC 3. 2 V Step Response, G = +1

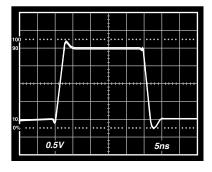

TPC 4. 2 V Step Response, G = +2

TPC 5. Test Circuit, Gain = +1

TPC 6. 100 mV Step Response, G = +1

-4- REV. D

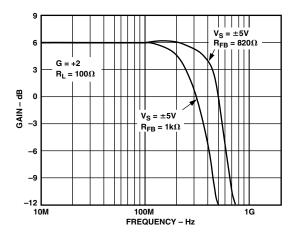

TPC 7. Frequency Response, G = +2

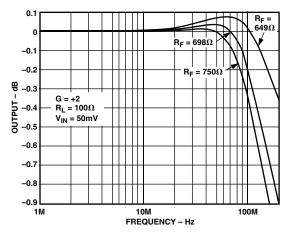

TPC 8. 0.1 dB Flatness, R Package (for N Package Add 50  $\Omega$  to R<sub>F</sub>)

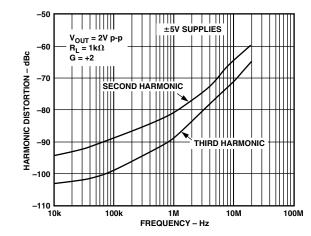

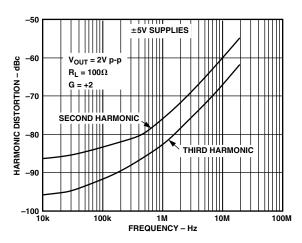

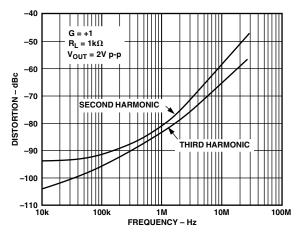

TPC 9. Distortion vs. Frequency,  $R_L = 1 \text{ k}\Omega$

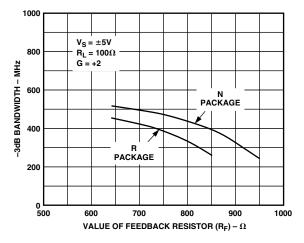

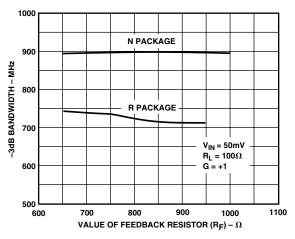

TPC 10. -3 dB Bandwidth vs. R<sub>F</sub>

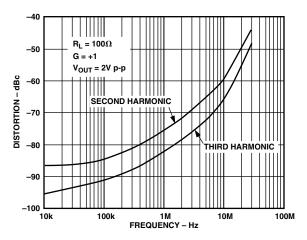

TPC 11. Distortion vs. Frequency,  $R_L = 100 \Omega$

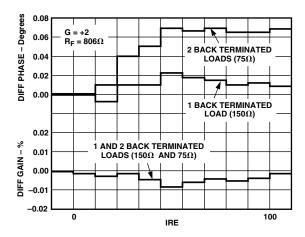

TPC 12. Differential Gain and Differential Phase

REV. D \_5\_

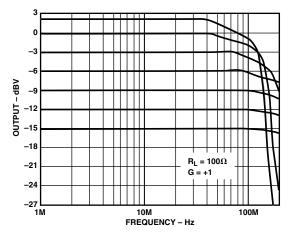

TPC 13. Frequency Response, G = +1

TPC 14. Flatness, R Package, G = +1 (for N Package Add 100  $\Omega$  to  $R_{\rm F}$ )

TPC 15. Distortion vs. Frequency,  $R_L = 1 \text{ k}\Omega$

TPC 16. -3 dB Bandwidth vs.  $R_F$ , G = +1

TPC 17. Distortion vs. Frequency,  $R_L = 100 \Omega$

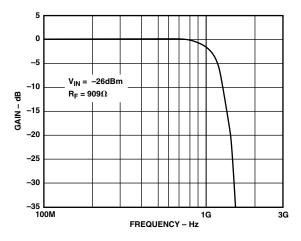

TPC 18. Large Signal Frequency Response, G = +1

-6- REV. D

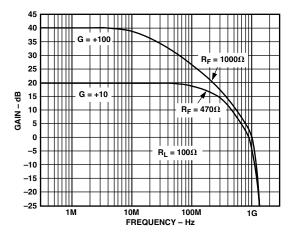

TPC 19. Frequency Response, G = +10, G = +100

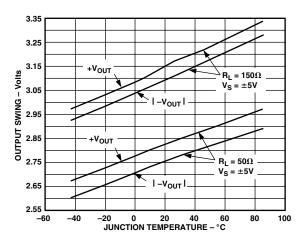

TPC 20. Output Swing vs. Temperature

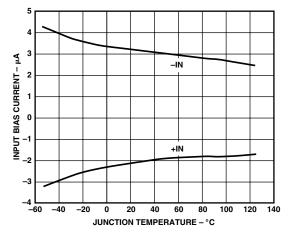

TPC 21. Input Bias Current vs. Temperature

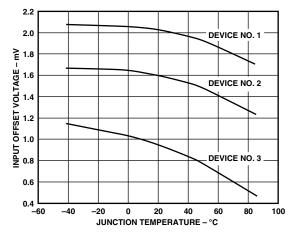

TPC 22. Input Offset vs. Temperature

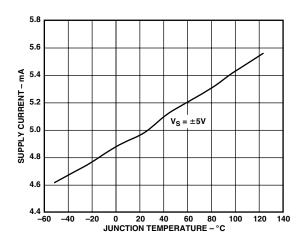

TPC 23. Supply Current vs. Temperature

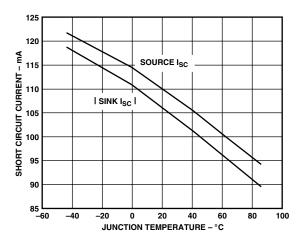

TPC 24. Short Circuit Current vs. Temperature

REV. D -7-

TPC 25. Transresistance vs. Temperature

TPC 26. Noise vs. Frequency

TPC 27. CMRR vs. Temperature

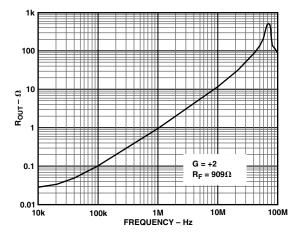

TPC 28. Output Resistance vs. Frequency

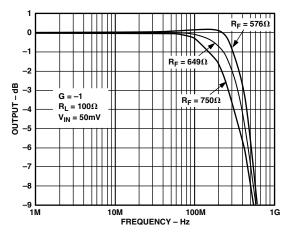

TPC 29. -3 dB Bandwidth vs. Frequency, G = -1

TPC 30. PSRR vs. Temperature

-8- REV. D

TPC 31. CMRR vs. Frequency

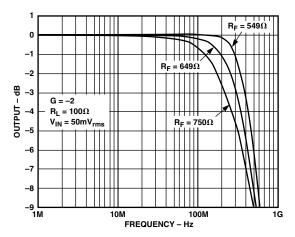

TPC 32. -3 dB Bandwidth vs. Frequency, G = -2

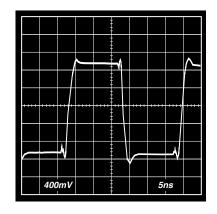

TPC 33. 100 mV Step Response, G = -1

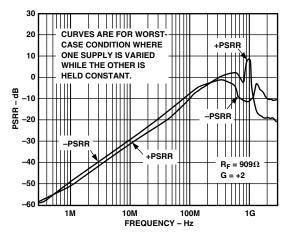

TPC 34. PSRR vs. Frequency

TPC 35. 2 V Step Response, G = -1

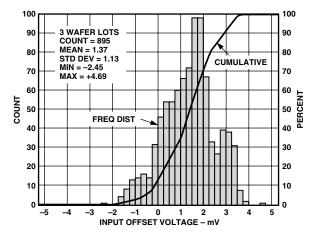

TPC 36. Input Offset Voltage Distribution

REV. D –9–

#### THEORY OF OPERATION

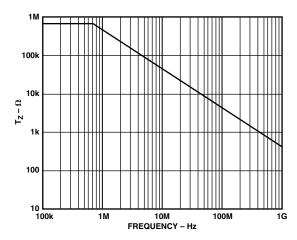

A very simple analysis can put the operation of the AD8001, a current feedback amplifier, in familiar terms. Being a current feedback amplifier, the AD8001's open-loop behavior is expressed as transimpedance,  $\Delta V_O/\Delta L_{IN}$ , or  $T_Z$ . The open-loop transimpedance behaves just as the open-loop voltage gain of a voltage feedback amplifier, that is, it has a large dc value and decreases at roughly 6 dB/octave in frequency.

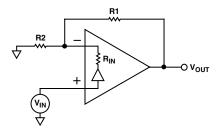

Since the  $R_{IN}$  is proportional to  $1/g_M$ , the equivalent voltage gain is just  $T_Z \times g_M$ , where the  $g_M$  in question is the transconductance of the input stage. This results in a low open-loop input impedance at the inverting input, a now familiar result. Using this amplifier as a follower with gain, Figure 4, basic analysis yields the following result.

$$\frac{V_O}{V_{IN}} = G \times \frac{T_Z(S)}{T_Z(S) + G \times R_{IN} + R1}$$

$$G = 1 + \frac{R1}{R2} \quad R_{IN} = 1/g_M \approx 50 \ \Omega$$

Figure 4. Follower with Gain

Recognizing that  $G \times R_{IN} \le R1$  for low gains, it can be seen to the first order that bandwidth for this amplifier is independent of gain (G). This simple analysis in conjunction with Figure 5 can, in fact, predict the behavior of the AD8001 over a wide range of conditions.

Figure 5. Transimpedance vs. Frequency

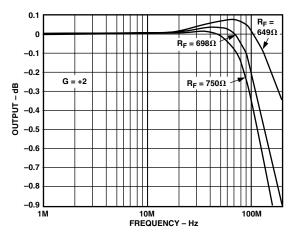

Considering that additional poles contribute excess phase at high frequencies, there is a minimum feedback resistance below which peaking or oscillation may result. This fact is used to determine the optimum feedback resistance,  $R_{\rm F}$ . In practice, parasitic capacitance at Pin 2 will also add phase in the feedback loop, so picking an optimum value for  $R_{\rm F}$  can be difficult. Figure 6 illustrates this problem. Here the fine scale (0.1 dB/div) flatness is plotted versus feedback resistance. These plots were taken using an evaluation card which is available to customers so that these results may readily be duplicated.

Achieving and maintaining gain flatness of better than 0.1 dB at frequencies above 10 MHz requires careful consideration of several issues.

Figure 6. 0.1 dB Flatness vs. Frequency

#### Choice of Feedback and Gain Resistors

Because of the above-mentioned relationship between the bandwidth and feedback resistor, the fine scale gain flatness will, to some extent, vary with feedback resistance. It, therefore, is recommended that once optimum resistor values have been determined, 1% tolerance values should be used if it is desired to maintain flatness over a wide range of production lots. In addition, resistors of different construction have different associated parasitic capacitance and inductance. Surface-mount resistors were used for the bulk of the characterization for this data sheet. It is not recommended that leaded components be used with the AD8001.

–10– REV. D

### **Printed Circuit Board Layout Considerations**

As to be expected for a wideband amplifier, PC board parasitics can affect the overall closed-loop performance. Of concern are stray capacitances at the output and the inverting input nodes. If a ground plane is to be used on the same side of the board as the signal traces, a space (5 mm min) should be left around the signal lines to minimize coupling. Additionally, signal lines connecting the feedback and gain resistors should be short enough so that their associated inductance does not cause high frequency gain errors. Line lengths on the order of less than 5 mm are recommended. If long runs of coaxial cable are being driven, dispersion and loss must be considered.

## **Power Supply Bypassing**

Adequate power supply bypassing can be critical when optimizing the performance of a high frequency circuit. Inductance in the power supply leads can form resonant circuits that produce peaking in the amplifier's response. In addition, if large current transients must be delivered to the load, then bypass capacitors (typically greater than 1  $\mu F)$  will be required to provide the best settling time and lowest distortion. A parallel combination of 4.7  $\mu F$  and 0.1  $\mu F$  is recommended. Some brands of electrolytic capacitors will require a small series damping resistor  $\approx\!4.7~\Omega$  for optimum results.

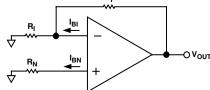

#### DC Errors and Noise

There are three major noise and offset terms to consider in a current feedback amplifier. For offset errors, refer to the equation below. For noise error the terms are root-sum-squared to give a net output error. In the circuit in Figure 7 they are input offset (V<sub>IO</sub>), which appears at the output multiplied by the noise gain of the circuit  $(1 + R_F/R_I)$ , noninverting input current  $(I_{BN} \times R_N)$ also multiplied by the noise gain, and the inverting input current, which when divided between R<sub>F</sub> and R<sub>I</sub> and subsequently multiplied by the noise gain always appears at the output as  $I_{BN} \times R_F$ . The input voltage noise of the AD8001 is a low 2 nV/  $\sqrt{\text{Hz}}$ . At low gains though the inverting input current noise times R<sub>F</sub> is the dominant noise source. Careful layout and device matching contribute to better offset and drift specifications for the AD8001 compared to many other current feedback amplifiers. The typical performance curves in conjunction with the following equations can be used to predict the performance of the AD8001 in any application.

$$V_{OUT} = V_{IO} \times \left(1 + \frac{R_F}{R_I}\right) \pm I_{BN} \times R_N \times \left(1 + \frac{R_F}{R_I}\right) \pm I_{BI} \times R_F$$

Figure 7. Output Offset Voltage

### **Driving Capacitive Loads**

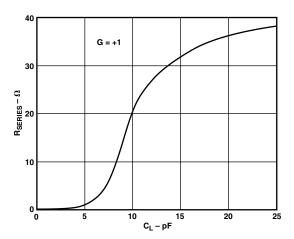

The AD8001 was designed primarily to drive nonreactive loads. If driving loads with a capacitive component is desired, best frequency response is obtained by the addition of a small series resistance, as shown in Figure 8. The accompanying graph shows the optimum value for  $R_{\text{SERIES}}$  versus capacitive load. It is worth noting that the frequency response of the circuit when driving large capacitive loads will be dominated by the passive roll-off of  $R_{\text{SERIES}}$  and  $C_{\rm L}$ .

Figure 8. Driving Capacitive Loads

Figure 9. Recommended  $R_{SERIES}$  vs. Capacitive Load

REV. D –11–

#### Communications

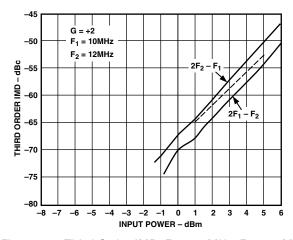

Distortion is a key specification in communications applications. Intermodulation distortion (IMD) is a measure of the ability of an amplifier to pass complex signals without the generation of spurious harmonics. The third order products are usually the most problematic since several of them fall near the fundamentals and do not lend themselves to filtering. Theory predicts that the third order harmonic distortion components increase in power at three times the rate of the fundamental tones. The specification of third order intercept as the virtual point where fundamental and harmonic power are equal is one standard measure of distortion performance. Op amps used in closed-loop applications do not always obey this simple theory. At a gain of +2, the AD8001 has performance summarized in Figure 10. Here the worst third order products are plotted versus input power. The third order intercept of the AD8001 is +33 dBm at 10 MHz.

Figure 10. Third Order IMD;  $F_1 = 10$  MHz,  $F_2 = 12$  MHz

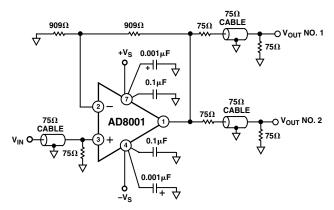

#### Operation as a Video Line Driver

The AD8001 has been designed to offer outstanding performance as a video line driver. The important specifications of differential gain (0.01%) and differential phase (0.025°) meet the most exacting HDTV demands for driving one video load. The AD8001 also drives up to two back terminated loads as shown in Figure 11, with equally impressive performance (0.01%, 0.07°). Another important consideration is isolation between loads in a multiple load application. The AD8001 has more than 40 dB of isolation at 5 MHz when driving two 75  $\Omega$  back terminated loads.

Figure 11. Video Line Driver

–12– REV. D

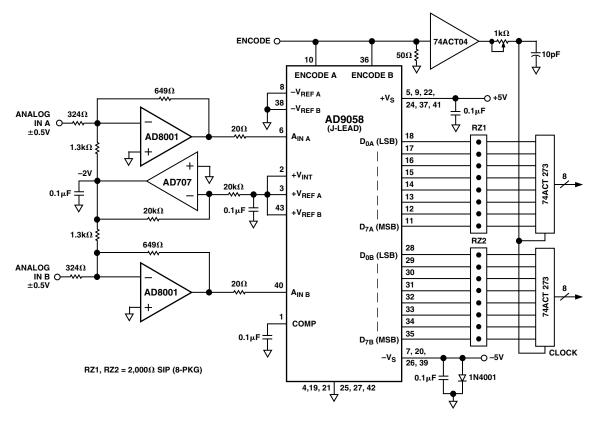

### **Driving A-to-D Converters**

The AD8001 is well suited for driving high speed analog-to-digital converters such as the AD9058. The AD9058 is a dual 8-bit 50 MSPS ADC. In the circuit below, the AD8001 is shown driving the inputs of the AD9058, which are configured for 0 V to 2 V ranges. Bipolar input signals are buffered, amplified  $(-2\times)$ , and offset (by +1.0 V) into the proper input range of the

ADC. Using the AD9058's internal +2 V reference connected to both ADCs as shown in Figure 12 reduces the number of external components required to create a complete data acquisition system. The 20  $\Omega$  resistors in series with ADC inputs are used to help the AD8001s drive the 10 pF ADC input capacitance. The AD8001 only adds 100 mW to the power consumption while not limiting the performance of the circuit.

Figure 12. AD8001 Driving a Dual A-to-D Converter

REV. D -13-

## **Layout Considerations**

The specified high speed performance of the AD8001 requires careful attention to board layout and component selection. Proper  $R_{\rm F}$  design techniques and low parasitic component selection are mandatory.

The PCB should have a ground plane covering all unused portions of the component side of the board to provide a low impedance ground path. The ground plane should be removed from the area near the input pins to reduce stray capacitance.

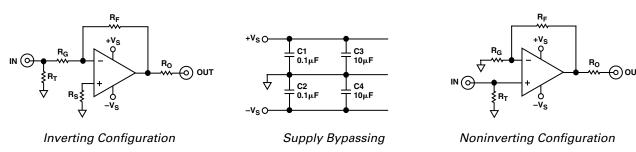

Chip capacitors should be used for supply bypassing (see Figure 13). One end should be connected to the ground plane and the other within 1/8 inch of each power pin. An additional large

(4.7  $\mu$ F–10  $\mu$ F) tantalum electrolytic capacitor should be connected in parallel, but not necessarily so close, to supply current for fast, large-signal changes at the output.

The feedback resistor should be located close to the inverting input pin in order to keep the stray capacitance at this node to a minimum. Capacitance variations of less than 1 pF at the inverting input will significantly affect high speed performance.

Stripline design techniques should be used for long signal traces (greater than about 1 inch). These should be designed with a characteristic impedance of 50  $\Omega$  or 75  $\Omega$  and be properly terminated at each end.

Figure 13. Inverting and Noninverting Configurations for Evaluation Boards

Table I. Recommended Component Values

|                              | AD8001AN (PDIP)<br>Gain |      |      |      | AD8001AR (SOIC)<br>Gain |      |      |      |      | AD8001ART (SOT-23-5)<br>Gain |      |      |      |      |      |

|------------------------------|-------------------------|------|------|------|-------------------------|------|------|------|------|------------------------------|------|------|------|------|------|

| Component                    | -1                      | +1   | +2   | +10  | +100                    | -1   | +1   | +2   | +10  | +100                         | -1   | +1   | +2   | +10  | +100 |

| $R_{F}(\Omega)$              | 649                     | 1050 | 750  | 470  | 1000                    | 604  | 953  | 681  | 470  | 1000                         | 845  | 1000 | 768  | 470  | 1000 |

| $R_{G}(\Omega)$              | 649                     |      | 750  | 51   | 10                      | 604  |      | 681  | 51   | 10                           | 845  |      | 768  | 51   | 10   |

| $R_O$ (Nominal) ( $\Omega$ ) | 49.9                    | 49.9 | 49.9 | 49.9 | 49.9                    | 49.9 | 49.9 | 49.9 | 49.9 | 49.9                         | 49.9 | 49.9 | 49.9 | 49.9 | 49.9 |

| $R_{S}(\Omega)$              | 0                       |      |      |      |                         | 0    |      |      |      |                              | 0    |      |      |      |      |

| $R_T$ (Nominal) ( $\Omega$ ) | 54.9                    | 49.9 | 49.9 | 49.9 | 49.9                    | 54.9 | 49.9 | 49.9 | 49.9 | 49.9                         | 54.9 | 49.9 | 49.9 | 49.9 | 49.9 |

| Small Signal<br>BW (MHz)     | 340                     | 880  | 460  | 260  | 20                      | 370  | 710  | 440  | 260  | 20                           | 240  | 795  | 380  | 260  | 20   |

| 0.1 dB Flatness<br>(MHz)     | 105                     | 70   | 105  |      |                         | 130  | 100  | 120  |      |                              | 110  | 300  | 145  |      |      |

–14– REV. D

#### **OUTLINE DIMENSIONS**

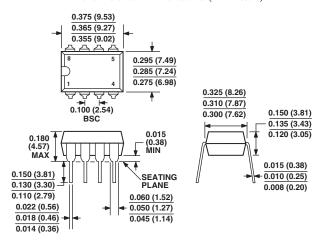

## 8-Lead Plastic Dual In-Line Package [PDIP]

(N-8)

Dimensions shown in inches and (millimeters)

#### **COMPLIANT TO JEDEC STANDARDS MO-095AA**

CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETER DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN

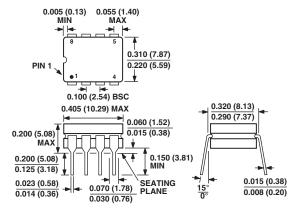

# 8-Lead Ceramic Dual In-Line Package [CERDIP] (Q-8)

Dimensions shown in inches and (millimeters)

CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETERS DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN

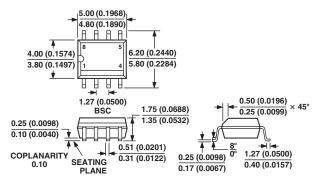

## 8-Lead Standard Small Outline Package [SOIC]

(R-8)

Dimensions shown in millimeters and (inches)

COMPLIANT TO JEDEC STANDARDS MS-012AA

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN

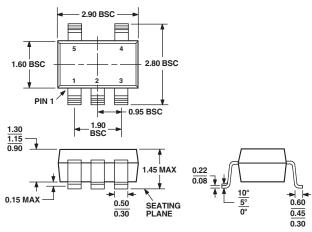

## 5-Lead Small Outline Transistor Package [SOT-23] (RT-5)

Dimensions shown in millimeters

**COMPLIANT TO JEDEC STANDARDS MO-178AA**

REV. D -15-

# C01043-0-7/03(D)

# AD8001

# **Revision History**

| Location                                      | Page      |

|-----------------------------------------------|-----------|

| 7/03—Data Sheet changed from REV. C to REV. D |           |

| Renumbered figures and TPCs                   | Universal |

| Changes to ORDERING GUIDE                     |           |

| Updated OUTLINE DIMENSIONS                    | 15        |