# LF to 2.7 GHz Dual 60 dB TruPwr™ Detector

### **Data Sheet**

#### FEATURES

RMS measurement of high crest-factor signals Dual-channel and channel difference outputs ports Integrated accurately scaled temperature sensor Wide dynamic range ±1 dB over 60 dB ±0.5 dB temperature-stable linear-in-dB response Low log conformance ripple +5 V operation at 70 mA, -40°C to +85°C Small footprint, 5 mm × 5 mm, LFCSP

#### **APPLICATIONS**

Wireless infrastructure power amplifier linearization/control Antenna VSWR monitor Gain and power control and measurement Transmitter signal strength indication (TSSI) Dual-channel wireless infrastructure radios

#### **GENERAL DESCRIPTION**

The AD8364 is a true rms, responding, dual-channel RF power measurement subsystem for the precise measurement and control of signal power. The flexibility of the AD8364 allows communications systems, such as RF power amplifiers and radio transceiver AGC circuits, to be monitored and controlled with ease. Operating on a single 5 V supply, each channel is fully specified for operation up to 2.7 GHz over a dynamic range of 60 dB. The AD8364 provides accurately scaled, independent, rms outputs of both RF measurement channels. Difference output ports, which measure the difference between the two channels, are also available. The on-chip channel matching makes the rms channel difference outputs extremely stable with temperature and process variations. The device also includes a useful temperature sensor with an accurately scaled voltage proportional to temperature, specified over the device operating temperature range. The AD8364 can be used with input signals having rms values from -55 dBm to +5 dBm referred to 50  $\Omega$  and large crest factors with no accuracy degradation.

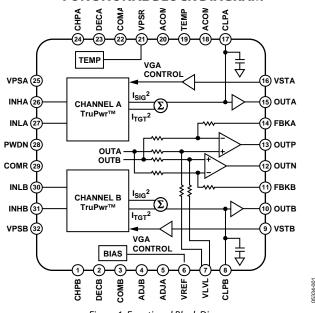

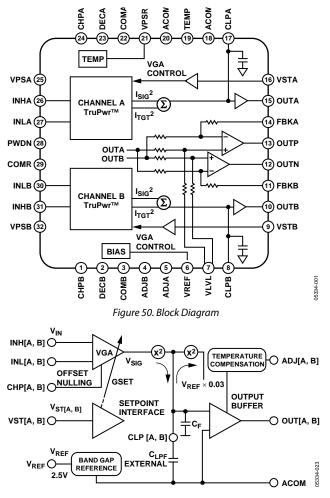

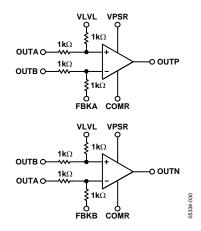

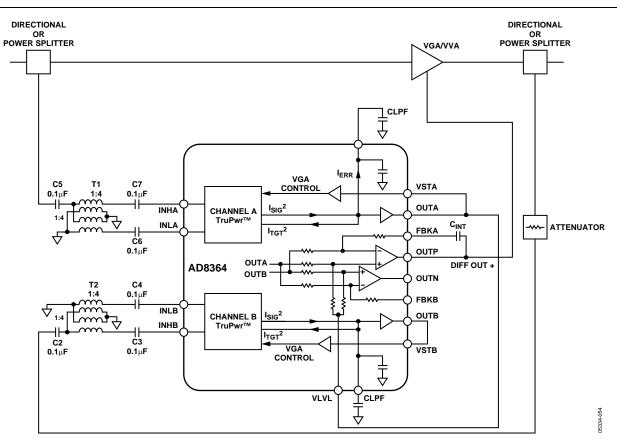

### FUNCTIONAL BLOCK DIAGRAM

AD8364

Figure 1. Functional Block Diagram

Integrated in the AD8364 are two matched AD8362 channels (see the AD8362 data sheet for more information) with improved temperature performance and reduced log conformance ripple. Enhancements include improved temperature performance and reduced log-conformance ripple compared to the AD8362. Onchip wide bandwidth output operational amplifiers are connected to accom-modate flexible configurations that support many system solutions.

The device can easily be configured to provide four rms measurements simultaneously. Linear-in-dB rms measurements are supplied at OUTA and OUTB, with conveniently scaled slopes of 50 mV/dB. The rms difference between OUTA and OUTB is available as differential or single-ended signals at OUTP and OUTN. An optional voltage applied to VLVL provides a common mode reference level to offset OUTP and OUTP and OUTN above ground.

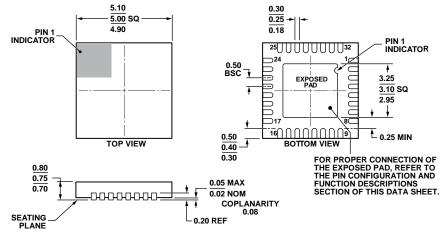

The AD8364 is supplied in a 32-lead, 5 mm  $\times$  5 mm LFCSP, for the operating temperature of  $-40^{\circ}$ C to  $+85^{\circ}$ C.

#### Rev. C

#### Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

## AD8364\* Product Page Quick Links

Last Content Update: 11/01/2016

### Comparable Parts

View a parametric search of comparable parts

### Evaluation Kits

AD8364 Evaluation Board

### Documentation 🖵

#### **Application Notes**

• AN-1040: RF Power Calibration Improves Performance of Wireless Transmitters

#### **Data Sheet**

• AD8364: LF to 2.7 GHz Dual 60dB TruPwr<sup>™</sup> Detector Data Sheet

### Tools and Simulations $\square$

- ADIsimPLL<sup>™</sup>

- ADIsimRF

### Reference Materials

#### **Product Selection Guide**

RF Source Booklet

#### **Technical Articles**

- Log Amps and Directional Couplers Enable VSWR Detection

- Measuring the RF Power in CDMA2000 and W-CDMA High Power Amplifiers (HPAs)

- · Measuring VSWR and Gain in Wireless Systems

### Design Resources 🖵

- AD8364 Material Declaration

- PCN-PDN Information

- Quality And Reliability

- · Symbols and Footprints

### Discussions 🖵

View all AD8364 EngineerZone Discussions

### Sample and Buy

Visit the product page to see pricing options

### Technical Support

Submit a technical question or find your regional support number

<sup>\*</sup> This page was dynamically generated by Analog Devices, Inc. and inserted into this data sheet. Note: Dynamic changes to the content on this page does not constitute a change to the revision number of the product data sheet. This content may be frequently modified.

## TABLE OF CONTENTS

| Features 1                                            |

|-------------------------------------------------------|

| Applications1                                         |

| Functional Block Diagram1                             |

| General Description1                                  |

| Revision History 2                                    |

| Specifications                                        |

| Absolute Maximum Ratings7                             |

| ESD Caution7                                          |

| Pin Configuration and Function Descriptions           |

| Typical Performance Characteristics                   |

| Theory of Operation                                   |

| Square Law Detector and Amplitude Target              |

| RF Input Interface19                                  |

| Offset Compensation                                   |

| Temperature Sensor Interface                          |

| VREF Interface                                        |

| Power-Down Interface                                  |

| VST[A, B] Interface20                                 |

| OUT[A, B, P, N] Outputs                               |

| Measurement Channel Difference Output Using OUT[P, N] |

|                                                       |

#### **REVISION HISTORY**

| 8/2016—Rev. B to Rev. C      |   |

|------------------------------|---|

| Updated Outline Dimensions 4 | 1 |

| Changes to Ordering Guide    | 1 |

#### 1/2012—Rev. A to Rev. B

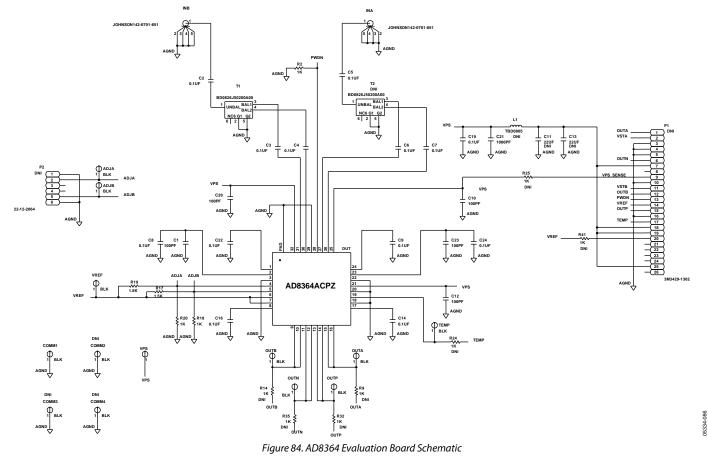

| Change to Figure 84 40 |

|------------------------|

|------------------------|

#### 11/2011-Rev. 0 to Rev. A

| Changes to Figure 2                                    | 8  |

|--------------------------------------------------------|----|

| Changes to Automatic Power Control Section             | 24 |

| Replaced Evaluation and Characterization Circuit Board |    |

| Layouts Section with Evaluation Board Section          | 40 |

| Changes to Figure 84                                   | 40 |

| Controller Mode                                                       | 22 |

|-----------------------------------------------------------------------|----|

| RF Measurement Mode Basic Connections                                 | 23 |

| Controller Mode Basic Connections                                     | 24 |

| Constant Output Power Operation                                       | 27 |

| Gain-Stable Transmitter/Receiver                                      | 29 |

| Temperature Compensation Adjustment                                   | 31 |

| Device Calibration and Error Calculation                              | 31 |

| Selecting Calibration Points to Improve Accuracy over a Reduced Range | 32 |

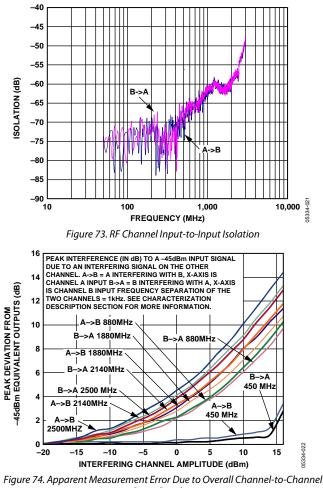

| Channel Isolation                                                     | 34 |

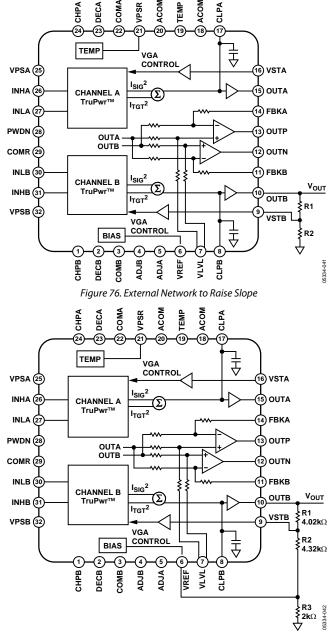

| Altering the Slope                                                    | 35 |

| Choosing the Right Value for CHP[A, B] and CLP[A, B]                  | 36 |

| RF Burst Response Time                                                | 36 |

| Single-Ended Input Operation                                          | 36 |

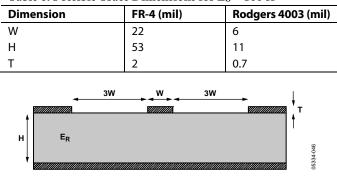

| Printed Circuit Board Considerations                                  | 37 |

| Package Considerations                                                | 37 |

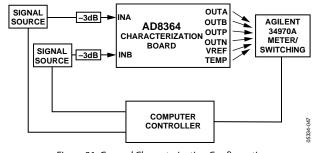

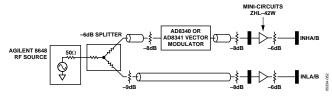

| Description of Characterization                                       | 38 |

| Basis for Error Calculations                                          | 38 |

| Evaluation Board                                                      | 40 |

| Outline Dimensions                                                    | 41 |

| Ordering Guide                                                        | 41 |

| Deleted Figure 85 and Figure 86; Renumbered Sequentially | 41 |

|----------------------------------------------------------|----|

| Updated Outline Dimensions                               | 41 |

| Changes to Ordering Guide                                | 41 |

| Deleted Table 7, AD8364-EVAL-500 Evaluation Board        |    |

| Configuration Options and AD8364-EVAL-2140 Evaluation    |    |

| Board Configuration Options; Renumbered Sequentially     | 42 |

| Deleted Evaluation Boards Section and Figure 87          | 44 |

| Deleted Figure 88                                        | 45 |

| Deleted Assembly Drawings Section, Figure 89, and        |    |

| Figure 90                                                | 46 |

|                                                          |    |

4/2005—Revision 0: Initial Version

### **SPECIFICATIONS**

$V_S = VPSA = VPSB = VPSR = 5 V, T_A = 25^{\circ}C$ , Channel A frequency = Channel B frequency, VLVL = VREF, VST[A, B] = OUT[A, B], OUT[P, N] = FBK[A, B], differential input via Balun, CW input  $f \le 2.7$  GHz, unless otherwise noted.

| Table 1 | • |

|---------|---|

|---------|---|

| Parameter                              | Test Conditions/Comments                                                         | Min | Тур        | Max | Unit   |

|----------------------------------------|----------------------------------------------------------------------------------|-----|------------|-----|--------|

| OVERALL FUNCTION                       | Channel A and Channel B, CW sine wave input                                      |     |            |     |        |

| Signal Input Interface                 | INH[A, B] (Pins 26, 31) INL[A, B] (Pins 27, 30)                                  |     |            |     |        |

| Specified Frequency Range              |                                                                                  | LF  |            | 2.7 | GHz    |

| DC Common-Mode Voltage                 |                                                                                  |     | 2.5        |     | V      |

| Signal Output Interface                | OUT[A, B] (Pins 15, 10)                                                          |     |            |     |        |

| Wideband Noise                         | $CLP[A, B] = 0.1 \mu F$ , $f_{SPOT} = 100 \text{ kHz}$ ,                         |     | 40         |     | nV/√Hz |

|                                        | RF input = 2140 MHz, ≥-40 dBm                                                    |     |            |     |        |

| MEASUREMENT MODE,                      | ADJA = ADJB = 0 V, error referred to best fit line using                         |     |            |     |        |

| 450 MHz OPERATION                      | linear regression @ $P_{INH[A, B]} = -40 \text{ dBm}$ and $-20 \text{ dBm}$ ,    |     |            |     |        |

|                                        | T <sub>A</sub> = 25°C, balun = M/A-Com ETK4-2T                                   |     |            |     |        |

| ±1 dB Dynamic Range <sup>1</sup>       | Pins OUT[A, B]                                                                   |     | 69         |     | dB     |

|                                        | $-40^{\circ}C < T_{A} < +85^{\circ}C$                                            |     | 65         |     | dB     |

| ±0.5 dB Dynamic Range <sup>1</sup>     | Pins OUT[A, B], (Channel A/Channel B)                                            |     | 62/59      |     | dB     |

|                                        | $-40^{\circ}$ C < T <sub>A</sub> < +85°C, (Channel A/Channel B)                  |     | 50/52      |     | dB     |

| Maximum Input Level                    | ±1 dB error                                                                      |     | 12         |     | dBm    |

| Minimum Input Level                    | ±1 dB error                                                                      |     | -58        |     | dBm    |

| Slope                                  |                                                                                  |     | 51.6       |     | mV/dB  |

| Intercept                              |                                                                                  |     | -59        |     | dBm    |

| Output Voltage—High Power In           | Pins OUT[A, B] @ $P_{INH[A, B]} = -10 \text{ dBm}$                               |     | 2.53       |     | V      |

| Output Voltage—Low Power In            | Pins OUT[A, B] @ $P_{INH[A, B]} = -40 \text{ dBm}$                               |     | 0.99       |     | V      |

| Temperature Sensitivity                | Deviation from OUT[A, B] @ 25°C                                                  |     |            |     |        |

|                                        | $-40^{\circ}C < T_A < 85^{\circ}C; P_{INH[A, B]} = -10 \text{ dBm}$              |     | -0.1, +0.2 |     | dB     |

|                                        | -40°C < T <sub>A</sub> < 85°C; P <sub>INH[A, B]</sub> = -25 dBm                  |     | -0.2, +0.3 |     | dB     |

|                                        | $-40^{\circ}C < T_A < 85^{\circ}C; P_{INH[A, B]} = -40 \text{ dBm}$              |     | -0.3, +0.4 |     | dB     |

|                                        | Deviation from OUTP to OUTN @ 25°C                                               |     |            |     |        |

|                                        | -40°C < T <sub>A</sub> < 85°C; P <sub>INH[A, B]</sub> = -10 dBm, -25 dBm         |     | ±0.25      |     | dB     |

|                                        | -40°C < T <sub>A</sub> < 85°C; P <sub>INH[A, B]</sub> = -25 dBm, -25 dBm         |     | ±0.2       |     | dB     |

|                                        | -40°C < T <sub>A</sub> < 85°C; P <sub>INH[A, B]</sub> = -40 dBm, -25 dBm         |     | ±0.2       |     | dB     |

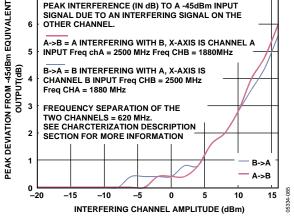

| Input A to Input B Isolation           | Baluns = Macom ETC1.6-4-2-3 (both channels)                                      |     | 71         |     | dB     |

| Input A to OUTB Isolation              | Freq separation = $1 \text{ kHz}$                                                |     |            |     |        |

| Input B to OUTA Isolation <sup>2</sup> | $P_{INHB} = -50 \text{ dBm}, \text{OUTB} = \text{OUTB}_{PINHB} \pm 1 \text{ dB}$ |     | 54         |     | dB     |

|                                        | $P_{INHA} = -50 \text{ dBm}, \text{OUTA} = \text{OUTA}_{PINHA} \pm 1 \text{ dB}$ |     | 54         |     | dB     |

|                                        |                                                                                  |     |            |     |        |

| Input Impedance                        | INHA/INLA, INHB/INLB differential drive                                          |     | 210  0.1   |     | Ω∥pF   |

| Input Return Loss                      | With recommended balun                                                           |     | -12        |     | dB     |

| MEASUREMENT MODE,                      | ADJA = ADJB = 0 V, error referred to best fit line using                         |     |            |     |        |

| 880 MHz OPERATION                      | linear regression @ $P_{INH[A, B]} = -40$ dBm and $-20$ dBm,                     |     |            |     |        |

|                                        | T <sub>A</sub> = 25°C, balun = Mini-Circuits® JTX-4-10T                          |     |            |     |        |

| ±1 dB Dynamic Range <sup>1</sup>       | Pins OUT[A, B], (Channel A/Channel B)                                            |     | 66/57      |     | dB     |

|                                        | -40°C < T <sub>A</sub> < +85°C                                                   |     | 58/40      |     | dB     |

| ±0.5 dB Dynamic Range <sup>1</sup>     | Pins OUT[A, B], (Channel A/Channel B)                                            |     | 62/54      |     | dB     |

|                                        | $-40^{\circ}C < T_{A} < +85^{\circ}C$                                            |     | 20/20      |     | dB     |

| Maximum Input Level                    | ±1 dB error, (Channel A/Channel B)                                               |     | 8/0        |     | dBm    |

| Minimum Input Level                    | ±1 dB error, (Channel A/Channel B)                                               |     | -58/-57    |     | dBm    |

| Slope                                  |                                                                                  |     | 51.6       |     | mV/dB  |

| Intercept                              |                                                                                  |     | -59.2      |     | dBm    |

| Output Voltage—High Power In           | Pins OUT[A, B] @ $P_{INH[A, B]} = -10 \text{ dBm}$                               |     | 2.54       |     | V      |

| Output Voltage—Low Power In            | Pins OUT[A, B] @ $P_{INH[A, B]} = -40 \text{ dBm}$                               |     | 0.99       |     | v      |

| Parameter                               | Test Conditions/Comments                                                                                                                                                             | Min Typ I   | Max Unit |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------|

| Temperature Sensitivity                 | Deviation from OUT[A, B] @ 25°C                                                                                                                                                      |             | Ī        |

|                                         | $-40^{\circ}C < T_A < 85^{\circ}C; P_{INH[A, B]} = -10 \text{ dBm}$                                                                                                                  | +0.5        | dB       |

|                                         | -40°C < T <sub>A</sub> < 85°C; P <sub>INH[A, B]</sub> = -25 dBm                                                                                                                      | +0.5        | dB       |

|                                         | $-40^{\circ}C < T_A < 85^{\circ}C; P_{INH[A, B]} = -40 \text{ dBm}$                                                                                                                  | +0.5        | dB       |

|                                         | Deviation from OUTP to OUTN @ 25°C                                                                                                                                                   |             |          |

|                                         | $-40^{\circ}C < T_A < 85^{\circ}C; P_{INH[A, B]} = -10 \text{ dBm}, -25 \text{ dBm}$                                                                                                 | +0.1, -0.2  | dB       |

|                                         | -40°C < T <sub>A</sub> < 85°C; P <sub>INH[A, B]</sub> = -25 dBm, -25 dBm                                                                                                             | +0.1, -0.2  | dB       |

|                                         | -40°C < T <sub>A</sub> < 85°C; P <sub>INH[A, B]</sub> = -40 dBm, -25 dBm                                                                                                             | +0.1, -0.2  | dB       |

| Input A to Input B Isolation            | Baluns = Macom ETC1.6-4-2-3 (both channels)                                                                                                                                          | 64          | dB       |

| Input A to OUTB Isolation               | $P_{INHB} = -50 \text{ dBm}, \text{OUTB} = \text{OUTB}_{PINHB} \pm 1 \text{ dB}$                                                                                                     | 35          | dB       |

| Input B to OUTA Isolation <sup>2</sup>  | $P_{INHA} = -50 \text{ dBm}, \text{OUTA} = \text{OUTA}_{PINHA} \pm 1 \text{ dB}$                                                                                                     | 35          | dB       |

| Input Impedance                         | INHA/INLA, INHB/INLB differential drive                                                                                                                                              | 200  0.3    | Ω  pF    |

| Input Return Loss                       | With recommended balun                                                                                                                                                               | -9          | dB       |

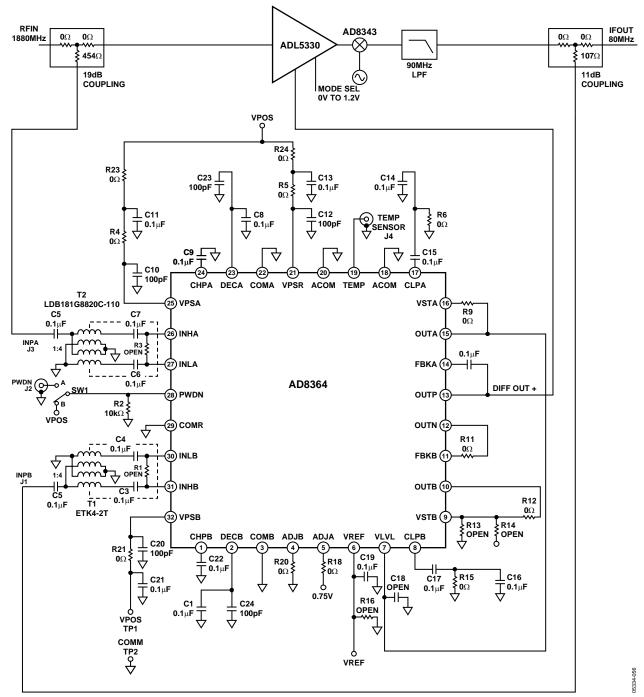

| MEASUREMENT MODE,<br>1880 MHz OPERATION | ADJA = ADJB = 0.75 V, error referred to best fit line using<br>linear regression @ $P_{INH[A, B]} = -40$ dBm and $-20$ dBm,<br>$T_A = 25^{\circ}$ C, balun = Murata LDB181G8820C-110 |             |          |

| ±1 dB Dynamic Range <sup>1</sup>        | Pins OUT[A, B], (Channel A/Channel B)                                                                                                                                                | 69/61       | dB       |

|                                         | $-40^{\circ}C < T_{A} < +85^{\circ}C$                                                                                                                                                | 60/50       | dB       |

| ±0.5 dB Dynamic Range <sup>1</sup>      | Pins OUT[A, B], (Channel A/Channel B)                                                                                                                                                | 62/51       | dB       |

|                                         | $-40^{\circ}C < T_{A} < +85^{\circ}C$                                                                                                                                                | 58/51       | dB       |

| Maximum Input Level                     | ±1 dB error, (Channel A/Channel B)                                                                                                                                                   | 11/3        | dBm      |

| Minimum Input Level                     | ±1 dB error                                                                                                                                                                          | -58         | dBm      |

| Slope                                   |                                                                                                                                                                                      | 50          | mV/dB    |

| Intercept                               |                                                                                                                                                                                      | -62         | dBm      |

| Output Voltage—High Power In            | Pins OUT[A, B] @ $P_{INH[A,B]} = -10 \text{ dBm}$                                                                                                                                    | 2.49        | V        |

| Output Voltage—Low Power In             | Pins OUT[A, B] @ $P_{INH[A,B]} = -40 \text{ dBm}$                                                                                                                                    | 0.98        | V        |

| Temperature Sensitivity                 | Deviation from OUT[A, B] @ 25°C                                                                                                                                                      |             |          |

|                                         | -40°C < T <sub>A</sub> < 85°C; P <sub>INH[A, B]</sub> = -10 dBm                                                                                                                      | +0.5, -0.2  | dB       |

|                                         | $-40^{\circ}C < T_A < 85^{\circ}C; P_{INH[A, B]} = -25 \text{ dBm}$                                                                                                                  | +0.5, -0.2  | dB       |

|                                         | $-40^{\circ}C < T_A < 85^{\circ}C; P_{INH[A, B]} = -40 \text{ dBm}$                                                                                                                  | +0.5, -0.2  | dB       |

|                                         | Deviation from OUTP to OUTN @ 25°C                                                                                                                                                   |             |          |

|                                         | -40°C < T <sub>A</sub> < 85°C; P <sub>INH[A, B]</sub> = -10 dBm, -25 dBm                                                                                                             | ±0.3        | dB       |

|                                         | -40°C < T <sub>A</sub> < 85°C; P <sub>INH[A, B]</sub> = -25 dBm, -25 dBm                                                                                                             | ±0.3        | dB       |

|                                         | $-40^{\circ}\text{C} < \text{T}_{\text{A}} < 85^{\circ}\text{C}; P_{\text{INH}[\text{A}, \text{B}]} = -40 \text{ dBm}, -25 \text{ dBm}$                                              | ±0.3        | dB       |

| Input A to Input B Isolation            | Baluns = Macom ETC1.6-4-2-3 (both channels)                                                                                                                                          | 61          | dB       |

| Input A to OUTB Isolation               | $P_{INHB} = -50 \text{ dBm}, \text{OUTB} = \text{OUTB}_{PINHB} \pm 1 \text{ dB}$                                                                                                     | 33          | dB       |

| Input B to OUTA Isolation <sup>2</sup>  | $P_{INHA} = -50 \text{ dBm}, \text{OUTA} = \text{OUTA}_{PINHA} \pm 1 \text{ dB}$                                                                                                     | 33          | dB       |

| Input Impedance                         | INHA/INLA, INHB/INLB differential drive                                                                                                                                              | 167  0.14   | Ω∥pF     |

| Input Return Loss                       | With recommended balun                                                                                                                                                               | -8          | dB       |

| MEASUREMENT MODE,<br>2.14 GHz OPERATION | ADJA = ADJB = 1.02 V, error referred to best fit line using<br>linear regression @ $P_{INH[A, B]} = -40$ dBm and $-20$ dBm,<br>$T_A = 25^{\circ}$ C, balun = Murata LDB212G1020C-001 |             |          |

| ±1 dB Dynamic Range <sup>1</sup>        | Pins OUT[A, B], (Channel A/Channel B)                                                                                                                                                | 66/57       | dB       |

|                                         | $-40^{\circ}C < T_{A} < +85^{\circ}C$                                                                                                                                                | 58/40       | dB       |

| ±0.5 dB Dynamic Range <sup>1</sup>      | Pins OUT[A, B], (Channel A/Channel B)                                                                                                                                                | 62/54       | dB       |

| ,                                       | $-40^{\circ}C < T_{A} < +85^{\circ}C$                                                                                                                                                | 30/30       | dB       |

| Maximum Input Level                     | ±1 dB Error, (Channel A/Channel B)                                                                                                                                                   | -2/-4       | dBm      |

| Minimum Input Level                     | ±1 dB Error, (Channel A/Channel B)                                                                                                                                                   | -57-51      | dBm      |

| Slope                                   | Channel A/Channel B                                                                                                                                                                  | 49.5/52.1   | mV/dB    |

| Intercept                               | Channel A/Channel B                                                                                                                                                                  | -58.3/-57.1 | dBm      |

| Output Voltage—High Power In            | Pins OUT[A, B] @ $P_{INH[A, B]} = -10 \text{ dBm}$                                                                                                                                   | 2.42        | V        |

|                                         |                                                                                                                                                                                      |             |          |

## **Data Sheet**

| Parameter                                                        | Test Conditions/Comments                                                                                                                                                       | Min Typ    | Мах | Unit  |

|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----|-------|

| Temperature Sensitivity                                          | Deviation from OUT[A, B] @ 25°C                                                                                                                                                |            |     |       |

|                                                                  | $-40^{\circ}C < T_{A} < 85^{\circ}C; P_{INH[A, B]} = -10 \text{ dBm}$                                                                                                          | +0.1, -0.4 | 4   | dB    |

|                                                                  | $-40^{\circ}C < T_A < 85^{\circ}C; P_{INH[A, B]} = -25 \text{ dBm}$                                                                                                            | +0.1, -0.4 | 4   | dB    |

|                                                                  | $-40^{\circ}C < T_A < 85^{\circ}C$ ; $P_{INH[A, B]} = -40 \text{ dBm}$                                                                                                         | +0.1, -0.4 | 4   | dB    |

|                                                                  | Deviation from OUTP to OUTN @ 25°C                                                                                                                                             |            |     |       |

|                                                                  | −40°C < T <sub>A</sub> < 85°C; P <sub>INH[A, B]</sub> = −10 dBm, −25 dBm                                                                                                       | +0.1, -0.4 | 4   | dB    |

|                                                                  | −40°C < T <sub>A</sub> < 85°C; P <sub>INH[A, B]</sub> = −25 dBm, −25 dBm                                                                                                       | +0.2, -0.2 | 2   | dB    |

|                                                                  | -40°C < T <sub>A</sub> < 85°C; P <sub>INH[A, B]</sub> = -40 dBm, -25 dBm                                                                                                       | +0.1, -0.2 | 2   | dB    |

| Deviation from CW Response                                       | 5.5 dB peak-to-rms ratio (WCDMA one channel)                                                                                                                                   | 0.2        |     | dB    |

|                                                                  | 12 dB peak-to-rms ratio (WCDMA three channels)                                                                                                                                 | 0.3        |     | dB    |

|                                                                  | 18 dB peak-to-rms ratio (WCDMA four channels)                                                                                                                                  | 0.3        |     | dB    |

| Input A to Input B Isolation                                     | Baluns = Macom ETC1.6-4-2-3 (both channels)                                                                                                                                    | 58         |     | dB    |

| Input A to OUTB Isolation                                        | $P_{INHB} = -50 \text{ dBm}, \text{OUTB} = \text{OUTB}_{PINHB} \pm 1 \text{ dB}$                                                                                               | 33         |     | dB    |

| Input B to OUTA Isolation <sup>2</sup>                           | $P_{INHA} = -50 \text{ dBm}, \text{OUTA} = \text{OUTA}_{PINHA} \pm 1 \text{ dB}$                                                                                               | 33         |     | dB    |

| Input Impedance                                                  | INHA/INLA, INHB/INLB differential drive                                                                                                                                        | 150  1.9   |     | Ω  pF |

| Input Return Loss                                                | With recommended balun                                                                                                                                                         | -10        |     | dB    |

| MEASUREMENT MODE,<br>2.5 GHz OPERATION                           | ADJA = ADJB = 1.14 V, error referred to best fit line using linear regression @ $P_{INH[A, B]} = -40$ dBm and $-20$ dBm, $T_A = 25^{\circ}$ C, balun = Murata LDB182G4520C-110 |            |     |       |

| ± 1 dB Dynamic Range <sup>1</sup>                                | Pins OUT[A, B], (Channel A/Channel B)                                                                                                                                          | 69/63      |     | dB    |

|                                                                  | $-40^{\circ}C < T_A < +85^{\circ}C$                                                                                                                                            | 58         |     | dB    |

| ±0.5 dB Dynamic Range <sup>1</sup>                               | Pins OUT[A, B], (Channel A/Channel B)                                                                                                                                          | 55/50      |     | dB    |

|                                                                  | $-40^{\circ}C < T_{A} < +85^{\circ}C$                                                                                                                                          | 25         |     | dB    |

| Maximum Input Level                                              | ±1 dB error, (Channel A/Channel B)                                                                                                                                             | 17/11      |     | dBm   |

| Minimum Input Level                                              | ±1 dB error                                                                                                                                                                    | -52        |     | dBm   |

| Slope                                                            |                                                                                                                                                                                | 50         |     | mV/dB |

| Intercept                                                        |                                                                                                                                                                                | -52.7      |     | dBm   |

| Output Voltage—High Power In                                     | Pins OUT[A, B] @ $P_{INH[A, B]} = -10 \text{ dBm}$                                                                                                                             | 2.14       |     | v     |

| Output Voltage—Low Power In                                      | Pins OUT[A, B] @ $P_{INH[A, B]} = -40 \text{ dBm}$                                                                                                                             | 0.65       |     | v     |

| Temperature Sensitivity                                          | Deviation from OUT[A, B] @ 25°C                                                                                                                                                |            |     |       |

|                                                                  | $-40^{\circ}\text{C} < \text{T}_{\text{A}} < 85^{\circ}\text{C}; \text{P}_{\text{INH}[\text{A, B}]} = -10 \text{ dBm}$                                                         | ±0.5       |     | dB    |

|                                                                  | -40°C < T <sub>A</sub> < 85°C; P <sub>INH[A, B]</sub> = -25 dBm                                                                                                                | ±0.5       |     | dB    |

|                                                                  | -40°C < T <sub>A</sub> < 85°C; P <sub>INH[A, B]</sub> = -40 dBm                                                                                                                | ±0.5       |     | dB    |

|                                                                  | Deviation from OUTP to OUTN @ 25°C                                                                                                                                             |            |     |       |

|                                                                  | $-40^{\circ}\text{C} < \text{T}_{\text{A}} < 85^{\circ}\text{C}; \text{P}_{\text{INH}[\text{A, B}]} = -10 \text{ dBm}, -25 \text{ dBm}$                                        | ±0.3       |     | dB    |

|                                                                  | $-40^{\circ}\text{C} < \text{T}_{\text{A}} < 85^{\circ}\text{C}; \text{P}_{\text{INH}[\text{A}, B]} = -25 \text{ dBm}, -25 \text{ dBm}$                                        | ±0.3       |     | dB    |

|                                                                  | $-40^{\circ}\text{C} < \text{T}_{\text{A}} < 85^{\circ}\text{C}; P_{\text{INH}[\text{A}, \text{B}]} = -40 \text{ dBm}, -25 \text{ dBm}$                                        | ±0.3       |     | dB    |

| Input A to Input B Isolation                                     | Baluns = Macom ETC1.6-4-2-3 (both channels)                                                                                                                                    | 54         |     | dB    |

| Input A to OUTB Isolation                                        | $P_{INHB} = -50 \text{ dBm}, \text{OUTB} = \text{OUTB}_{PINHB} \pm 1 \text{ dB}$                                                                                               | 31         |     | dB    |

| Input B to OUTA Isolation <sup>2</sup>                           | $P_{INHA} = -50 \text{ dBm}, \text{OUTA} = \text{OUTA}_{PINHA} \pm 1 \text{ dB}$                                                                                               | 31         |     |       |

| Input Impedance                                                  | INHA/INLA, INHB/INLB differential drive                                                                                                                                        | 150  1.7   |     | Ω∥pF  |

| Input Return Loss                                                | With recommended balun                                                                                                                                                         | -11.5      |     | dB    |

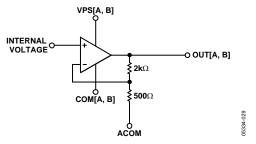

| OUTPUT INTERFACE                                                 | Pin OUTA and OUTB                                                                                                                                                              |            |     | -     |

| Voltage Range Min                                                | $R_L \ge 200 \Omega$ to ground                                                                                                                                                 | 0.09       |     | v     |

| Voltage Range Max                                                | $R_L \ge 200 \Omega$ to ground                                                                                                                                                 | Vs – 0.15  |     | v     |

| Source/Sink Current OUTA and OUTB held at $V_s/2$ , to 1% change |                                                                                                                                                                                | 70         |     | mA    |

| Parameter                  | Test Conditions/Comments                                                                                      | Min | Тур       | Max  | Unit  |

|----------------------------|---------------------------------------------------------------------------------------------------------------|-----|-----------|------|-------|

| SETPOINT INPUT             | Pin VSTA and VSTB                                                                                             |     |           |      |       |

| Voltage Range              | Law conformance error ≤1 dB                                                                                   | 0.5 |           | 3.75 | v     |

| Input Resistance           |                                                                                                               |     | 68        |      | kΩ    |

| Logarithmic Scale Factor   | $f = 450 \text{ MHz}, -40^{\circ}\text{C} \le T_{\text{A}} \le +85^{\circ}\text{C}$                           |     | 50        |      | mV/dE |

| Logarithmic Intercept      | $f = 450 \text{ MHz}, -40^{\circ}\text{C} \le T_{\text{A}} \le +85^{\circ}\text{C}$ , referred to 50 $\Omega$ |     | -55       |      | dBm   |

| CHANNEL DIFFERENCE OUTPUT  | Pin OUTP and OUTN                                                                                             |     |           |      |       |

| Voltage Range Min          | $R_L \ge 200 \Omega$ to ground                                                                                |     | 0.1       |      | V     |

| Voltage Range Max          | $R_{L} \ge 200 \Omega$ to ground                                                                              |     | Vs - 0.15 |      | V     |

| Source/Sink Current        | OUTP and OUTN held at $V_s/2$ , to 1% change                                                                  |     | 70        |      | mA    |

| DIFFERENCE LEVEL ADJUST    | Pin VLVL                                                                                                      |     |           |      |       |

| Voltage Range <sup>3</sup> | OUT[P, N] = FBK[A, B]                                                                                         | 0   |           | 5    | V     |

| OUT[P,N] Voltage Range     | OUT[P, N] = FBK[A, B]                                                                                         | 0   |           | Vs – | V     |

|                            |                                                                                                               |     |           | 0.15 |       |

| Input Resistance           |                                                                                                               |     | 1         |      | kΩ    |

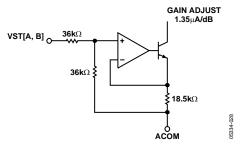

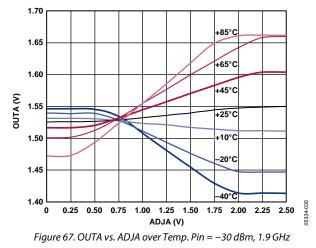

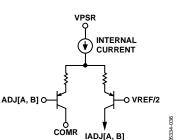

| TEMPERATURE COMPENSATION   | Pin ADJA and ADJB                                                                                             |     |           |      |       |

| Input Voltage Range        |                                                                                                               | 0   |           | 2.5  | V     |

| Input Resistance           |                                                                                                               |     | >1        |      | MΩ    |

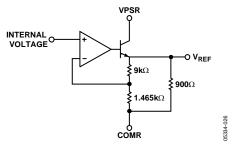

| VOLTAGE REFERENCE          | Pin VREF                                                                                                      |     |           |      |       |

| Output Voltage             | RF in = $-55 \text{ dBm}$                                                                                     |     | 2.5       |      | V     |

| Temperature Sensitivity    | $-40^{\circ}C \le T_A \le +85^{\circ}C$                                                                       |     | 0.4       |      | mV/°C |

| Current Limit Source/Sink  | 1% change                                                                                                     |     | 10/3      |      | mA    |

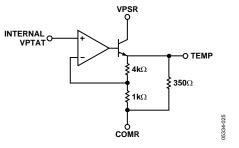

| TEMPERATURE REFERENCE      | Pin TEMP                                                                                                      |     |           |      |       |

| Output Voltage             | $T_A = 25^{\circ}C, R_L \ge 10 \text{ k}\Omega$                                                               |     | 0.62      |      | V     |

| Temperature Coefficient    | $-40^{\circ}C \le T_A \le +85^{\circ}C$ , $R_L \ge 10 \text{ k}\Omega$                                        |     | 2         |      | mV/°C |

| Current Source/Sink        | $T_A = 25^{\circ}C$ to 1% change                                                                              |     | 1.6/2     |      | mA    |

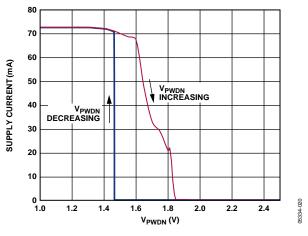

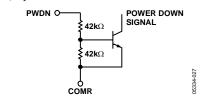

| POWER-DOWN INTERFACE       | Pin PWDN                                                                                                      |     |           |      |       |

| Logic Level to Enable      | Logic LO enables                                                                                              |     |           | 1    | V     |

| Logic Level to Disable     | Logic HI disables                                                                                             | 3   |           |      | V     |

| Input Current              | Logic HI PWDN = $5 V$                                                                                         |     | 95        |      | μA    |

| -                          | Logic LO PWDN = 0 V                                                                                           |     | <100      |      | μA    |

| Enable Time                | PWDN LO to OUTA/OUTB at 100% final value,                                                                     |     | 2         |      | μs    |

|                            | $C_{LPA/B} = Open, C_{HPA/B} = 10 \text{ nF}, \text{RF in} = 0 \text{ dBm}$                                   |     |           |      |       |

| Disable Time               | PWDN HI to OUTA/OUTB at 10% final value,                                                                      |     | 1.6       |      | μs    |

|                            | $C_{LPA/B} = Open, C_{HPA/B} = 10nF, RF in = 0 dBm$                                                           |     |           |      |       |

| POWER INTERFACE            | Pin VPS[A, B], VPSR                                                                                           |     |           |      |       |

| Supply Voltage             |                                                                                                               | 4.5 |           | 5.5  | V     |

| Quiescent Current          | $RF in = -55 dBm, V_s = 5 V$                                                                                  |     | 70        |      | mA    |

|                            | $-40^{\circ}C \le T_A \le +85^{\circ}C$                                                                       |     |           | 90   | mA    |

| Supply Current             | PWDN enabled, $V_s = 5 V$                                                                                     |     | 500       |      | μΑ    |

|                            | $-40^{\circ}C \le T_A \le +85^{\circ}C$                                                                       |     |           | 900  | μA    |

<sup>1</sup> Best fit line, linear regression.

<sup>2</sup> See Figure 73 for a plot of isolation vs. frequency for a ±1 dB error.

<sup>3</sup> VLVL + OUTA/2 should not exceed VPSA – 1.31 V. Likewise, VLVL + OUTB/2 should not exceed VPSB – 1.31 V.

### **ABSOLUTE MAXIMUM RATINGS**

#### Table 2.

| Parameter                                   | Rating                   |

|---------------------------------------------|--------------------------|

| Supply Voltage VPSA, VPSB, VPSR             | 5.5 V                    |

| PWDN, VSTA, VSTB, ADJA, ADJB,<br>FBKA, FBKB | 0 V, 5.5 V               |

| Input Power (Referred to 50 $\Omega$ )      | 23 dBm                   |

| Internal Power Dissipation                  | 600 mW                   |

| θ <sub>JA</sub>                             | 39.8°C/W <sup>1, 2</sup> |

| θ」                                          | 3.9°C/W <sup>2</sup>     |

| θ <sub>JB</sub>                             | 22.8°C/W <sup>2</sup>    |

| $\Psi_{JT}$                                 | 0.4°C/W <sup>1, 2</sup>  |

| Maximum Junction Temperature                | 125°C                    |

| Operating Temperature Range                 | -40°C to +85°C           |

| Storage Temperature Range                   | –65°C to +150°C          |

<sup>1</sup> Still air.

<sup>2</sup> All values are modeled using a standard 4-layer JEDEC test board with the pad soldered to the board and thermal vias in the board.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

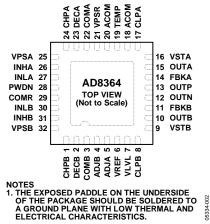

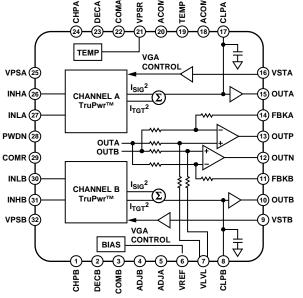

## **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

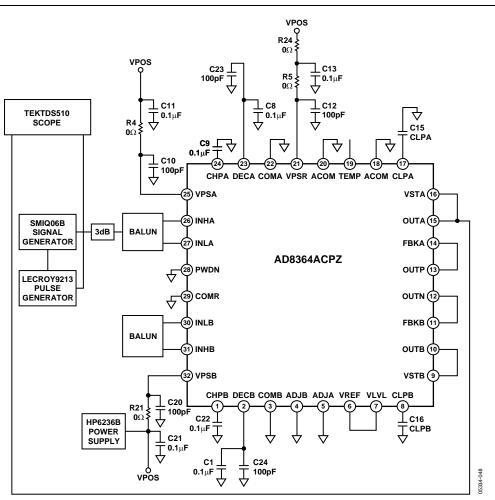

Figure 2. Pin Configuration

#### **Table 3. Pin Function Descriptions**

| Pin No.          | Mnemonic         | Description                                                                                                                                                                                                                                                                                                                               | Equiv. Circuit |

|------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 1                | СНРВ             | Connect to common via a capacitor to determine 3 dB point of Channel B input signal high-pass filter.                                                                                                                                                                                                                                     |                |

| 2, 23            | DECB, DECA       | Decoupling Terminals for INHA/INLA and INHB/INLB. Connect to common via a large capacitance to complete input circuit.                                                                                                                                                                                                                    |                |

| 3, 22, 29        | COMB, COMA, COMR | Input System Common Connection. Connect via low impedance to system common.                                                                                                                                                                                                                                                               |                |

| 4, 5             | ADJB, ADJA       | Temperature Compensation for Channel B and Channel A. An external voltage is connected to these pins to improve temperature drift. This voltage can be derived from VREF, that is, connect a resistor from VREF to ADJ[A, B] and another resistor from ADJ[A, B] to ground. The value of these resistors change as the frequency changes. |                |

| 6                | VREF             | General-Purpose Reference Voltage Output of 2.5 V.                                                                                                                                                                                                                                                                                        | Figure 54      |

| 7                | VLVL             | Reference Level Input for OUTP and OUTN. (Usually connected to VREF through a voltage divider or left open).                                                                                                                                                                                                                              |                |

| 8, 17            | CLPB, CLPA       | Channel B and Channel A Connection for Loop Filter Integration (Averaging) Capacitor. Connect a ground-referenced capacitor to this pin. A resistor can be connected in series with this capacitor to improve loop stability and response time.                                                                                           |                |

| 9                | VSTB             | The voltage applied to this pin sets the decibel value of the required RF input voltage to Channel B, which results in zero current flow in the loop integrating capacitor pin, CLPB.                                                                                                                                                     |                |

| 10               | OUTB             | Channel B Output of Error Amplifier. In measurement mode, normally connected directly to VSTB.                                                                                                                                                                                                                                            | Figure 57      |

| 11               | FBKB             | Feedback Through 1 k $\Omega$ to the Negative Terminal of the Integrated Op Amp Driving OUTN.                                                                                                                                                                                                                                             |                |

| 12               | OUTN             | Channel Differencing Op Amp Output. In measurement mode, normally connected directly to FBKB and follows the equation OUTN = OUTA – OUTB + VLVL.                                                                                                                                                                                          |                |

| 13               | OUTP             | Channel Differencing Op Amp Output. In measurement mode, normally connected directly to FBKA and follows the equation OUTP = OUTA – OUTB + VLVL.                                                                                                                                                                                          |                |

| 14               | FBKA             | Feedback Through 1k $\Omega$ to the Negative Terminal of the Integrated Op Amp Driving OUTP.                                                                                                                                                                                                                                              |                |

| 15               | OUTA             | Channel A Output of Error Amplifier. In measurement mode, normally connected directly to VSTA.                                                                                                                                                                                                                                            | Figure 57      |

| 16               | VSTA             | The voltage applied to this pin sets the decibel value of the required RF input voltage to Channel A that results in zero current flow in the loop integrating capacitor pin, CLPA.                                                                                                                                                       |                |

| 18, 20           | ACOM             | Analog Common for Channels A and B. Connect via low impedance to common.                                                                                                                                                                                                                                                                  |                |

| 21, 25, 32       | VPSR, VPSA, VPSB | Supply for the Input System of Channels A and B. Supply for the internal references. Connect to +5 V power supply.                                                                                                                                                                                                                        |                |

| 19               | TEMP             | Temperature Sensor Output.                                                                                                                                                                                                                                                                                                                | Figure 53      |

| 24               | СНРА             | Connect to common via a capacitor to determine 3 dB point of Channel A input signal high-pass filter.                                                                                                                                                                                                                                     |                |

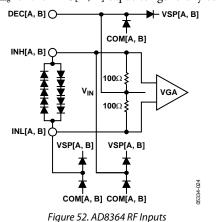

| 26, 27           | INHA, INLA       | Channel A High and Low RF Signal Input Terminal.                                                                                                                                                                                                                                                                                          | Figure 52      |

| 28               | PWDN             | Disable/Enable Control Input. Apply logic high voltage to shut down the AD8364.                                                                                                                                                                                                                                                           | Figure 55      |

| 30, 31           | INLB, INHB       | Channel B Low and High RF Signal Input Terminal.                                                                                                                                                                                                                                                                                          | Figure 52      |

| Under<br>Package | Exposed Paddle   | The exposed paddle on the underside of the package must be soldered to a ground plane with low thermal and electrical characteristics.                                                                                                                                                                                                    |                |

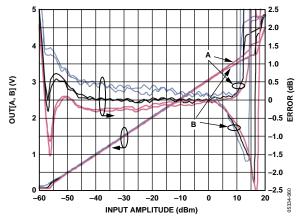

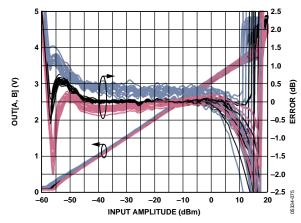

## **TYPICAL PERFORMANCE CHARACTERISTICS**

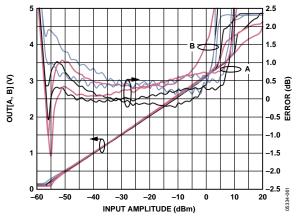

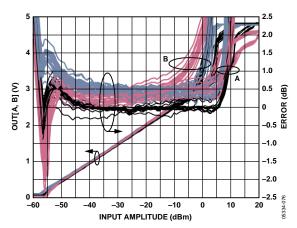

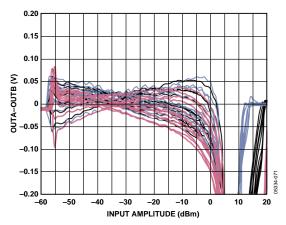

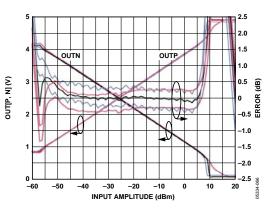

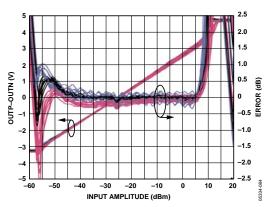

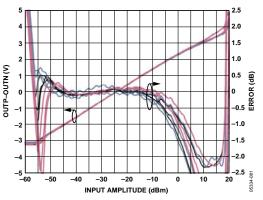

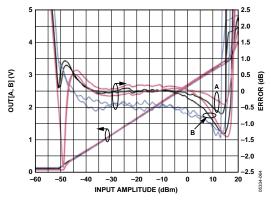

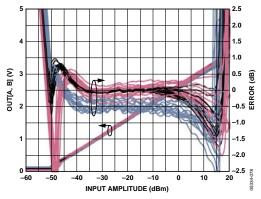

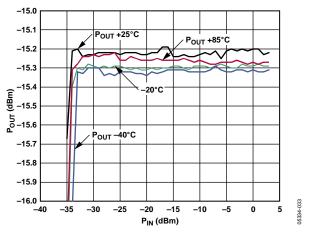

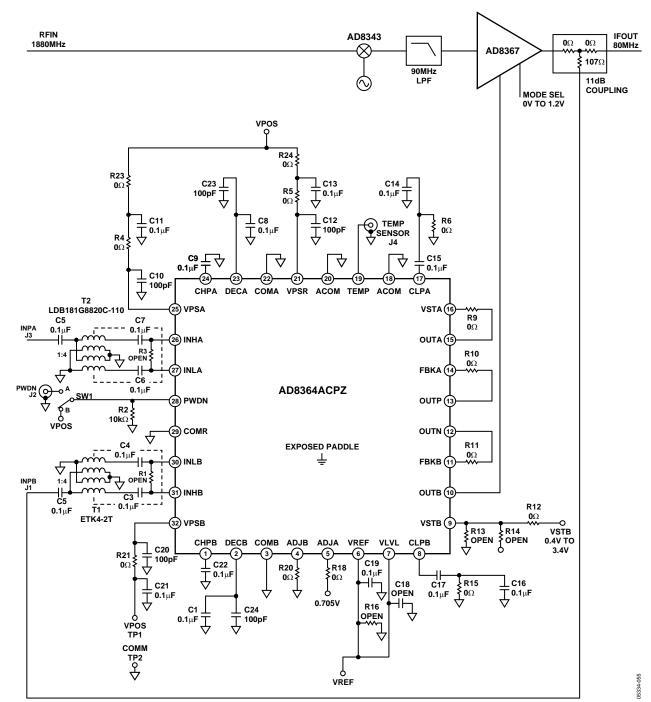

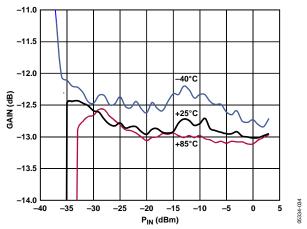

$V_P = 5 V$ ;  $T_A = +25^{\circ}C$ ,  $-40^{\circ}C$ ,  $+85^{\circ}C$ ; CLPA/B = OPEN. Colors:  $+25^{\circ}C$  black,  $-40^{\circ}C$  blue,  $+85^{\circ}C$  red.

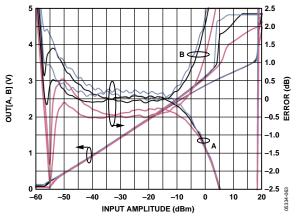

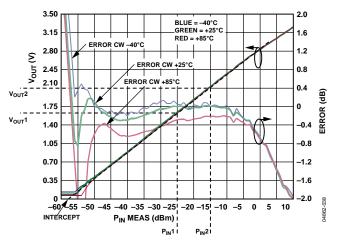

Figure 3. OUT[A, B] Voltage and Log Conformance vs. Input Amplitude at 450 MHz, Typical Device, ADJ[A, B] = 0 V, Sine Wave, Differential Drive, Balun = Macom ETK4-2T

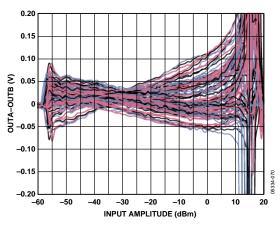

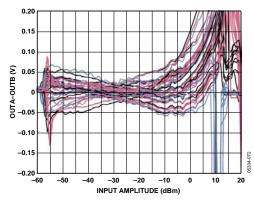

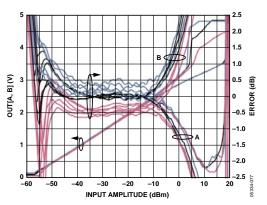

Figure 4. Distribution of OUT[A, B] Voltage and Error over Temperature After Ambient Normalization vs. Input Amplitude for at Least 30 Devices from Multiple Lots, Frequency = 450 MHz, ADJ[A, B] = 0 V, Sine Wave, Differential Drive, Balun = Macom ETK4-2T

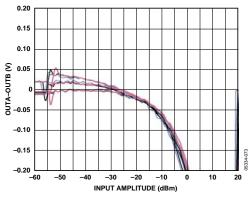

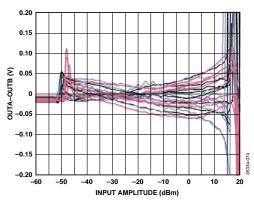

Figure 5. Distribution of [OUTA – OUTB] Voltage vs. Input Amplitude over Temperature for at Least 30 Devices from Multiple Lots, Frequency = 450 MHz, ADJ[A, B] = 0 V, Sine Wave, Differential Drive, Balun = Macom ETK4-2T

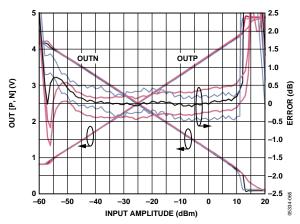

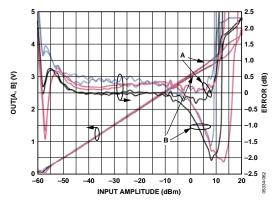

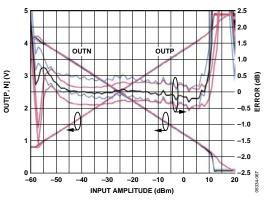

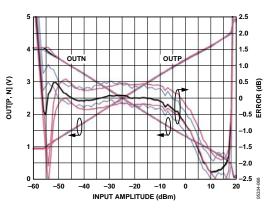

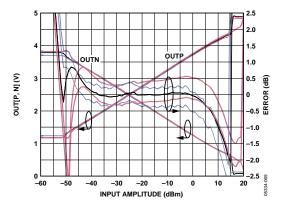

Figure 6. OUT[P, N] Voltage and Log Conformance vs. Input Amplitude at 450 MHz, with B Input Held at –25 dBm and A Input Swept, Typical Device, ADJ[A, B] = 0 V, Sine Wave, Differential Drive, Balun = Macom ETK4-2T (Note that the OUTP and OUTN Error Curves Overlap)

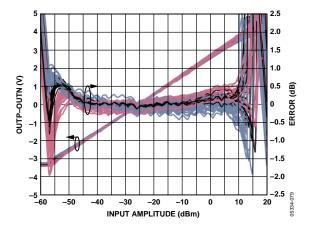

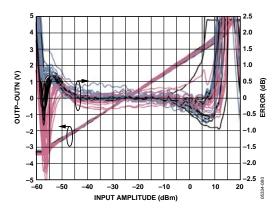

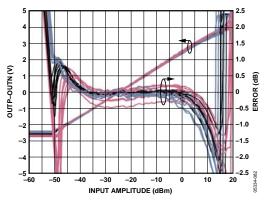

Figure 7. Distribution of [OUTP – OUTN] Voltage and Error over Temperature After Ambient Normalization vs. Input Amplitude for at Least 30 Devices from Multiple Lots, Frequency = 450 MHz, ADJ[A, B] = 0 V, Sine Wave, Differential Drive,  $P_{\rm IN}$  Ch. B = –25 dBm, Channel A Swept

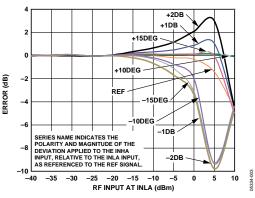

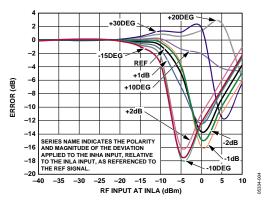

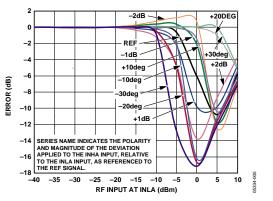

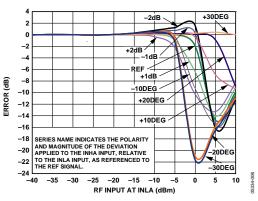

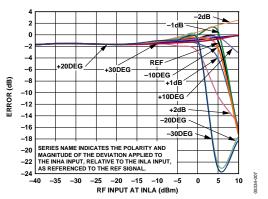

Figure 8. Log Conformance vs. Input Amplitude at various Amplitude and Phase Balance points, 450 MHz, Typical Device, ADJ[A, B] = 0 V, Sine Wave, Differential Drive

Figure 9. OUT[A, B] Voltage and Log Conformance vs. Input Amplitude at 880 MHz, Typical Device, ADJ[A, B] = 0.5 V, Sine Wave, Differential Drive, Balun = Mini-Circuits JTX-4-10T

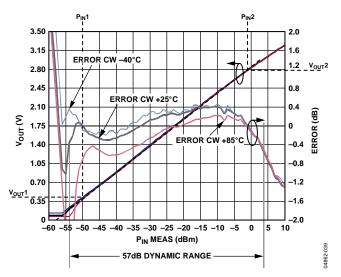

Figure 10. Distribution of OUT[A, B] Voltage and Error over Temperature After Ambient Normalization vs. Input Amplitude for at Least 15 Devices from Multiple Lots, Frequency = 880 MHz, ADJ[A, B] = 0.5 V, Sine Wave, Differential Drive, Balun =JTX-4-10T

Figure 11. Distribution of [OUTA – OUTB] Voltage vs. Input Amplitude over Temperature for at Least 15 Devices from Multiple Lots, Frequency = 880 MHz, ADJ[A, B] = 0.5 V, Sine Wave, Differential Drive, Balun =JTX-4-10T

Figure 12. OUT[P, N] Voltage and Log Conformance vs. Input Amplitude at 880 MHz, with B Input Held at –25 dBm and A Input Swept, Typical Device, ADJ[A, B] = 0.5 V, Sine Wave, Differential Drive, Balun = JTX-4-10T (Note that the OUTP and OUTN Error Curves Overlap)

Figure 13. Distribution of [OUTP – OUTN] Voltage and Error over Temperature After Ambient Normalization vs. Input Amplitude for at Least 15 Devices from Multiple Lots, Frequency = 880 MHz, ADJ[A, B] =0.5 V, Sine Wave, Differential Drive, P<sub>IN</sub> Ch. B = −25 dBm, Channel A Swept

Figure 14. Log Conformance vs. Input Amplitude at Various Amplitude and Phase Balance points, 880 MHz, Typical Device, ADJ[A, B] = 0.5 V, Sine Wave, Differential Drive

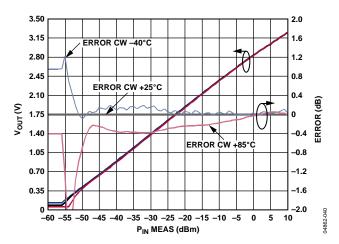

Figure 15. OUT[A, B] Voltage and Log Conformance vs. Input Amplitude at 1.88 GHz, Typical Device, TADJ[A, B]= 0.65 V, Sine Wave, Differential Drive, Balun = Murata LDB181G8820C-110

Figure 16. Distribution of OUT[A, B] Voltage and Error over Temperature After Ambient Normalization vs. Input Amplitude for at Least 20 Devices from Multiple Lots, Frequency = 1.88 GHz, ADJ[A, B] = 0.65 V, Sine Wave, Differential Drive, Balun = Murata LDB181G8820C-110

Figure 17. Distribution of [OUTA – OUTB] Voltage vs. Input Amplitude over Temperature for at Least 20 Devices from Multiple Lots, Frequency = 1.88 GHz, ADJ[A, B] = 0.65 V, Sine Wave, Differential Drive, Balun = Murata LDB181G8820C-110

Figure 18. OUT[P, N] Voltage and Log Conformance vs. Input Amplitude at 1.88 GHz, with B Input Held at –25 dBm and A Input Swept, Typical Device, ADJ[A, B] = 0.65 V, Sine Wave, Differential Drive, Balun = Murata LDB181G8820C-110 (Note that the OUTP and OUTN Error Curves Overlap)

Figure 19. Distribution of [OUTP – OUTN] Voltage and Error over Temperature After Ambient Normalization vs. Input Amplitude for at Least 20 Devices from Multiple Lots, Frequency = 1.88 GHz, ADJ[A, B] =0.65 V, Sine Wave, Differential Drive,  $P_{IN}$  Ch. B = -25 dBm, Channel A Swept

Figure 20. Log Conformance vs. Input Amplitude at Various Amplitude and Phase Balance Points, 1.880 GHz, Typical Device, ADJ[A, B] = 0.65 V, Sine Wave, Differential Drive

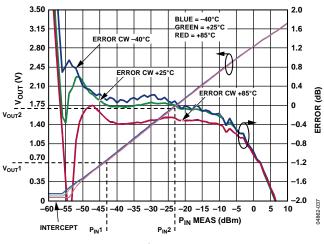

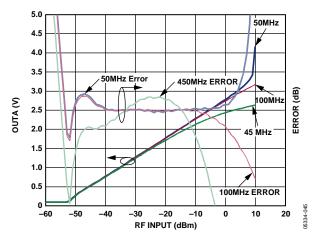

Figure 21. OUT[A, B] Voltage and Log Conformance vs. Input Amplitude at 2.14 GHz, Typical Device, ADJ[A, B] = 0.85 V, Sine Wave, Differential Drive, Balun = Murata LDB212G1020C-001

Figure 22. Distribution of OUT[A, B] Voltage and Error over Temperature After Ambient Normalization vs. Input Amplitude for at Least 3 Devices from Multiple Lots, Frequency = 2.14 GHz, ADJ[A, B] = 0.85 V, Sine Wave, Differential Drive, Balun = Murata LDB212G1020C-001

Figure 23. Distribution of [OUTA – OUTB] Voltage vs. Input Amplitude over Temperature for 3 Devices from Multiple Lots, Frequency = 2.14 GHz, ADJ[A, B] = 0.85 V, Sine Wave, Differential Drive, Balun = Murata LDB212G1020C-001

Figure 24. OUT[P, N] Voltage and Log Conformance vs. Input Amplitude at 2.14 GHz, with B Input Held at –25 dBm and A Input Swept, Typical Device, ADJ[A, B] = 0.85 V, Sine Wave, Differential Drive, Balun = Murata LDB212G1020C-001 (Note that the OUTP and OUTN Error Curves Overlap)

Figure 25. Distribution of [OUTP – OUTN] Voltage and Error over Temperature After Ambient Normalization vs. Input Amplitude for at Least 3 Devices from Multiple Lots, Frequency = 2.14 GHz, ADJ[A, B] = 0.85 V, Sine Wave, Differential Drive,  $P_{IN}$  Ch. B = -25 dBm, Channel A Swept

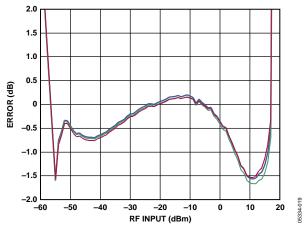

Figure 26. Log Conformance vs. Input Amplitude at Various Amplitude and Phase Balance Points, 2.140 GHz, Typical Device, ADJ[A, B] = 0.85 V, Sine Wave, Differential Drive

Figure 27. OUT[A, B] Voltage and Log Conformance vs. Input Amplitude at 2.5 GHz, Typical Device, ADJ[A, B] = 1.1 V, Sine Wave, Differential Drive, Balun = Murata LDB182G4520C-110

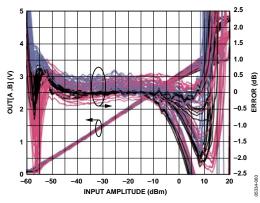

Figure 28. Distribution of OUT[A, B] Voltage and Error over Temperature After Ambient Normalization vs. Input Amplitude for at Least 15 Devices from Multiple Lots, Frequency = 2.5 GHz, ADJ[A, B] = 1.1 V, Sine Wave, Differential Drive, Balun = Murata LDB182G4520C-110

Figure 29. Distribution of [OUTA – OUTB] Voltage vs. Input Amplitude over Temperature for at Least 15 Devices from Multiple Lots, Frequency = 2.5 GHz, ADJ[A, B] = 1.1 V, Sine Wave, Differential Drive, Balun = Murata LDB182G4520C-110

Figure 30. OUT[P, N] Voltage and Log Conformance vs. Input Amplitude at 2.5 GHz, with B Input Held at –25 dBm and A Input Swept, Typical Device, ADJ[A, B] = 1.1 V, Sine Wave, Differential Drive, Balun = Murata LDB182G4520C-110 (Note that the OUTP and OUTN Error Curves Overlap)

Figure 31. Distribution of [OUTP – OUTN] Voltage and Error over Temperature After Ambient Normalization vs. Input Amplitude for at Least 15 Devices from Multiple Lots, Frequency = 2.5 GHz, ADJ[A, B] =1.1 V, Sine Wave, Differential Drive, PIN Ch. B = –25 dBm, Channel A Swept

Figure 32. Log Conformance vs. Input Amplitude at Various Amplitude and Phase Balance Points, 2.500 GHz, Typical Device, ADJ[A, B] = 1.1 V, Sine Wave, Differential Drive

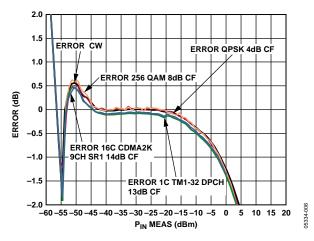

Figure 33. Output Error from CW Linear Reference vs. Input Amplitude with Different Waveforms, CW, QPSK, 256QAM, WCDMA 1-Carrier Test Model 1 with 32 DPCH, CDMA2000, 16-Carrier, 9-Channel SR1 Frequency 2.140 GHz, CLP[A, B] = 1 μF, Balun = Murata LDB212G1020C-001

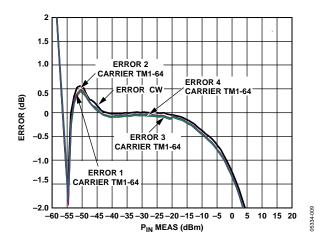

Figure 34. Error from CW Linear Reference vs. Input Amplitude with Different Waveforms, CW, WCDMA1, 2-, 3-, and 4-Carrier, Test Model 1 with 64 DPCH, Frequency 2.14 GHz, Balun = Murata LDB212G1020C-001

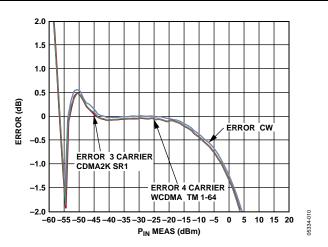

Figure 35. Output Voltage and Error from CW Linear Reference vs. Input Amplitude with Different Waveforms, CW, 3-Carrier CDMA2000 SR1, 4-Carrier WCDMA, Test Model 1 with 64 DPCH, Frequency 2.140 GHz, Balun = Murata LDB212G1020C-001

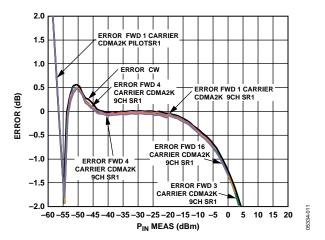

Figure 36. Error from CW Linear Reference vs. Input Amplitude with Different Waveforms, CW, 1-Carrier CDMA2000 Pilot CH SR1, 1-Carrier CDMA2000 9CH SR1, 3-Carrier CDMA2000 9CH SR1, 4-Carrier CDMA2000 9CH SR1 Frequency 16-Carrier CDMA2000 9CH SR1, Frequency 2.140 GHz, Balun = Murata LDB212G1020C-001

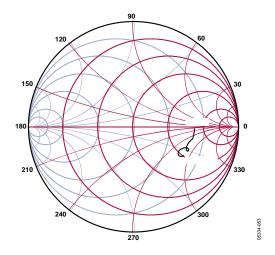

Figure 37. Differential Input Impedance (S11) vs. Frequency;  $Z_0 = 50 \Omega$

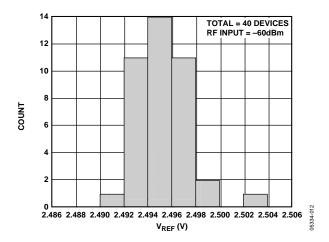

Figure 38. Distribution of VREF for 40 Devices

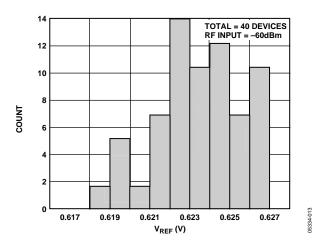

Figure 39. Distribution of TEMP Voltage for 40 Devices

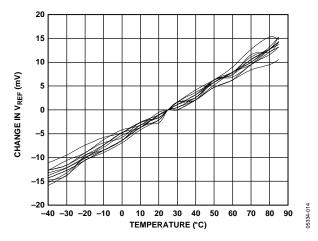

Figure 40. Change in VREF vs. Temperature for 11 Devices

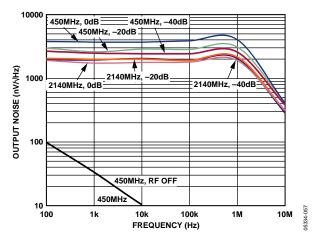

Figure 41. Noise Spectral Density of OUT[A, B]; CLP[A, B] = Open

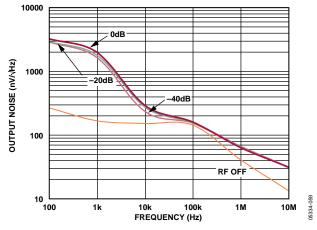

Figure 42. Noise Spectral Density of OUT[P, N]; CLP[A, B] = 0.1  $\mu$ F, Frequency = 2140 MHz

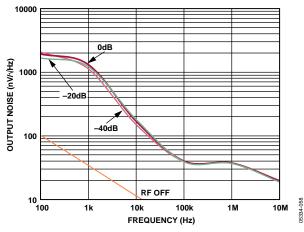

Figure 43. Noise Spectral Density of OUT[A, B]; CLP[A, B] = 0.1  $\mu$ F, Frequency = 2140 MHz

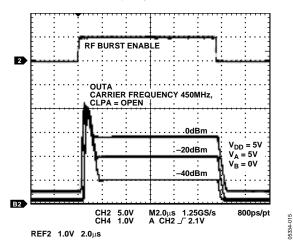

Figure 44. Output Response to RF Burst Input for Various RF Input Levels, Carrier Frequency 450 MHz, CLPA = Open

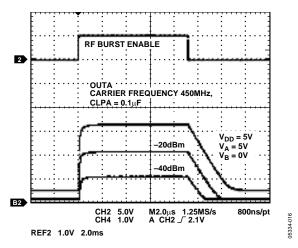

Figure 45. Output Response to RF Burst Input for Various RF Input Levels, Carrier Frequency 450 MHz, CLPA = 0.1 µF

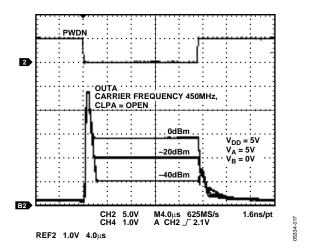

Figure 46. Output Response Using Power-Down Mode for Various RF Input Levels, Carrier Frequency 450 MHz, CLPA = Open

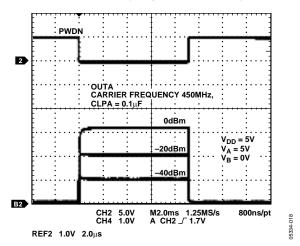

Figure 47. Output Response Using Power-Down Mode for Various RF Input Levels, Carrier Frequency 450 MHz, CLPA = 0.1  $\mu$ F, CHPA = 10 nF

Figure 48. Output Voltage Stability vs. VP (Supply Voltage) at 2.14 GHz, When VP Varies by 10%,ADJ[A, B] =0.85 V, Sine Wave, Differential Drive, Murata LDB212G1020C-001

Figure 49. Supply Current vs. VPWDN

### **Data Sheet**

### THEORY OF OPERATION

The AD8364 is a dual-channel, 2.7 GHz, true rms responding detector with 60 dB measurement range. It incorporates two AD8362 channels with shared reference circuitry (See the AD8362 datasheet for more information). Multiple enhancements have been made to the AD8362 cores to improve measurement accuracy. Log-conformance peak-to-peak ripple has been reduced to  $<\pm 0.2$  dB over the entire dynamic range. Temperature stability of the rms output measurements provides  $<\pm 0.5$  dB error over the specified temperature range of  $-40^{\circ}$ C to 85°C through proprietary techniques. The use of well-matched channels offers extremely temperature-stable difference outputs, OUTP and OUTN. Given well-matched channels through IC integration, the rms measurement outputs, OUTA and OUTB, drift in the same manner. With OUTP shorted to FBKA, the function at OUTP is

$OUTP = OUTA - OUTB + VLVL \tag{1}$

When OUTN is shorted to FBKB, the function at OUTN is

OUTN = OUTB - OUTA + VLVL(2)

OUTP and OUTN are insensitive to the common drift due to the difference cancellation of OUTA and OUTB.

The AD8364 is a fully calibrated rms-to-dc converter capable of operating on signals of a few hertz to 2.7 GHz or more. Unlike logarithmic amplifiers, the AD8364 response is waveform independent. The device accurately measures waveforms that have a high peak-to-rms ratio (crest factor). Figure 50 shows a block diagram.

A single channel of the AD8364 consists of a high performance AGC loop. As shown in Figure 51, the AGC loop comprises a wide bandwidth variable gain amplifier (VGA), square law detectors, an amplitude target circuit, and an output driver. For a more detailed description of the functional blocks, see the AD8362 data sheet.

Figure 51. Single-Channel Details

# SQUARE LAW DETECTOR AND AMPLITUDE TARGET

The output of the VGA, called  $V_{SIG}$ , is applied to a wideband square law detector. The detector provides the true rms response of the RF input signal, independent of waveform, up to a crest factor of 6. The detector output, called  $I_{SQU}$ , is a fluctuating current with positive mean value. The difference between  $I_{SQU}$  and an internally generated current,  $I_{TGT[A, B]}$ , is integrated by  $C_F$  and a capacitor attached to CLP[A, B]. CF is the on-chip 25 pF filter capacitor. CLP[A, B] can be used to arbitrarily increase the averaging time while trading off response time. When the AGC loop is at equilibrium,

$$MEAN(I_{SQU}) = I_{TGT[A, B]}$$

(3)

This equilibrium occurs only when

$MEAN(V_{SIG}^2) = V_{TGT[A, B]}^2$ (4)

where  $V_{\text{TGT}}$  is an attenuated version of the VREF voltage.

Because the square law detectors are electrically identical and well matched, process and temperature dependent variations are effectively cancelled.

By forcing the above identity through varying the VGA setpoint, it is apparent that

$$RMS(V_{SIG}) = \sqrt{(MEAN(V_{SIG}^2))} = \sqrt{(V_{TGT}^2)} = V_{TGT}$$

(5)

Substituting the value of  $V_{\mbox{\tiny SIG}}$  , we have

$$RMS(G0 \times RF_{IN} \exp(-VST[A, B]/V_{GNS})) = V_{TGT}$$

(6)

When connected as a measurement device VST[A, B] = OUT[A, B]. Solving for OUT[A, B] as a function of  $RF_{IN}$ ,

$$OUT[A, B] = V_{SLOPE} \times \text{Log10}(RMS(RF_{IN})/V_Z)$$

(7)

where  $V_{\text{SLOPE}}$  is laser trimmed to 1 V/decade (or 50 mV/dB) at 100 MHz.  $V_Z$  is the intercept voltage, since Log 10(1) = 0 when  $RMS(RF_{\text{IN}}) = V_Z$ . If desired, the effective value of  $V_{\text{SLOPE}}$  may be altered by using a resistor divider from OUT[A, B] to drive VST[A, B]. The intercept,  $V_Z$ , is also laser trimmed to 180  $\mu$ V (-62 dBm, referred to 50  $\Omega$ ) with a CW signal at 100 MHz. This value is extrapolated, because OUT[A, B] do not respond to input of less than approximately -55 dBm with differential drive.

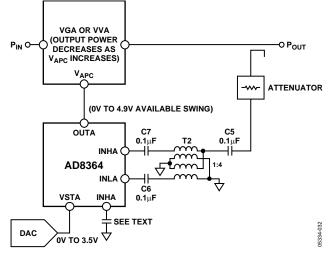

In most applications, the AGC loop is closed through the setpoint interface, VST[A, B]. In measurement mode, OUT[A, B] are tied to VST[A, B], respectively. In controller mode, a control voltage is applied to VST[A, B]. Pins OUT[A, B] drive the control input of a system. The RF feedback signal to the input pins is forced to have an rms value determined by VSTA or VSTB.

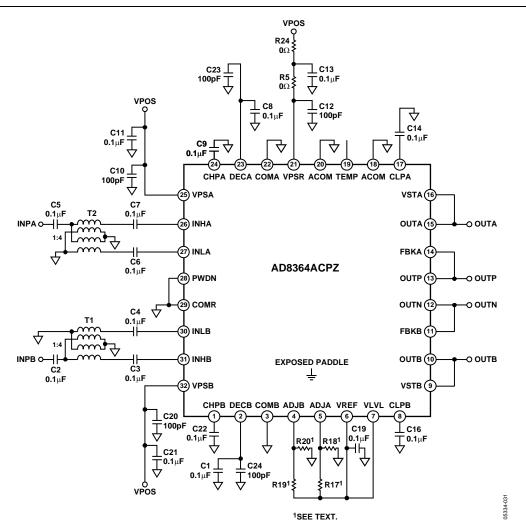

#### **RF INPUT INTERFACE**

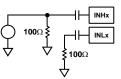

The AD8364 RF inputs are connected as shown in Figure 52. There are 100  $\Omega$  resistors connected between DEC[A, B] and INH[A, B] and also between DEC[A, B] and INL[A, B]. The DEC[A, B] pins have a dc level established as (7 × VPS[A, B] + 55 × V\_{BE})/30. With a 5 V supply, DEC[A, B] is approximately 2.5 V.

Signal-coupling capacitors must be connected from the input signal to the INH[A, B] and INL[A, B] pins. The high-pass corner is

$$f_{high-pass} = 1/(2 \times \pi \times 100 \times C) \tag{8}$$

A decoupling capacitor must be connected from DEC[A, B] to ground to attenuate any signal at the midpoint. A 100 pF and 0.1  $\mu$ F cap from DEC[A, B] to ground are recommended, with a 1 nF coupling capacitor such that signals greater than 1.6 MHz can be measured. For coupling signals less than 1.6 MHz, 100 × C<sub>coupling</sub> for the DEC[A, B] capacitor generally can be used.

#### **OFFSET COMPENSATION**

An offset-nulling loop is used to address small dc offsets in the VGA. The high-pass corner frequency of this loop is internally preset to about 1 MHz using an on-chip capacitor of 25 pF  $(1/(2 \times 5K \times 25 \text{ pF}))$ , which is sufficiently low for most HF applications. The high-pass corner can be reduced by a capacitor from CHP[A, B] to ground. The input offset voltage varies depending on the actual gain at which the VGA is operating and, thus, on the input signal amplitude. When an excessively large value of CHP[A, B] is used, the offset correction process may lag the more rapid changes in the VGA gain, which may increase the time required for the loop to fully settle for a given steady input amplitude.