# 8-Bit, 100 MSPS 3V A/D Converter

**AD9283S**

#### 1.0 Scope

This specification documents the detail requirements for space qualified product manufactured on Analog Devices, Inc.'s QML certified line per MIL-PRF-38535 Level V except as modified herein.

The manufacturing flow described in the STANDARD SPACE LEVEL PRODUCTS PROGRAM brochure is to be considered a part of this specification. <a href="http://www.analog.com/aerospace">http://www.analog.com/aerospace</a>

This data sheet specifically details the space grade version of this product. A more detailed operational description and a complete data sheet for commercial product grades can be found at <a href="https://www.analog.com/AD9283">www.analog.com/AD9283</a>

#### **2.0 PART NUMBER.** The complete part number(s) of this specification follow:

<u>Part Number</u> <u>Description</u>

**AD9283-703RC** 8-Bit, 100 MSPS 3V ADC

3.0 Case Outline

<u>Letter</u> <u>Descriptive designator</u> <u>Case Outline</u>

RC CQCC1-N20 20 – Terminal leadless chip carrier (LCC)

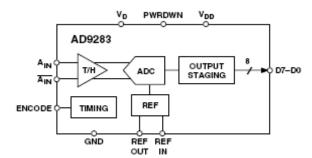

Figure 1 – Functional Block Diagram

Tel: 781.329.4700 www.analog.com Fax: 781.326.8703 © 2010 Analog Devices, Inc. All rights reserved.

# AD9283S

|            | Package: RC         |             |                                                                                                                                                                                                         |  |  |  |

|------------|---------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin Number | <u>Name</u>         | <u>Type</u> | <u>Description</u>                                                                                                                                                                                      |  |  |  |

| 1          | PWRDWN              | DI          | Power-Down Function Select; Logic HIGH for Power-Down Mode (Digital Outputs go to high impedance state)                                                                                                 |  |  |  |

| 2          | VREF OUT            | AO          | Internal Reference Output (1.25 V typ); Bypass with 0.1 µF to Ground                                                                                                                                    |  |  |  |

| 3          | VREF IN             | Al          | Reference Input for ADC (1.25 V typ)                                                                                                                                                                    |  |  |  |

| 4          | GND                 | Р           | Ground                                                                                                                                                                                                  |  |  |  |

| 5          | V <sub>D</sub>      | Р           | Analog 3 V Power Supply                                                                                                                                                                                 |  |  |  |

| 6          | A <sub>IN</sub> BAR | AI          | Analog Input for ADC (Can be left open if operating in single-ended mode, but recommend connection to a 0.1 $\mu$ F capacitor and a 25 $\Omega$ resistor in series to Ground for better input matching) |  |  |  |

| 7          | A <sub>IN</sub>     | Al          | Analog Input for ADC                                                                                                                                                                                    |  |  |  |

| 8          | V <sub>D</sub>      | Р           | Analog 3 V Power Supply                                                                                                                                                                                 |  |  |  |

| 9          | GND                 | Р           | Ground                                                                                                                                                                                                  |  |  |  |

| 10         | ENCODE              | DI          | Encode Clock for ADC (ADC Samples on Rising Edge of ENCODE)                                                                                                                                             |  |  |  |

| 11         | D7                  | DO          | Data Output MSB. ADC DB7                                                                                                                                                                                |  |  |  |

| 12         | D6                  | DO          | Data Output. ADC DB6                                                                                                                                                                                    |  |  |  |

| 13         | D5                  | DO          | Data Output. ADC DB5                                                                                                                                                                                    |  |  |  |

| 14         | D4                  | DO          | Data Output. ADC DB4                                                                                                                                                                                    |  |  |  |

| 15         | $V_{DD}$            | Р           | Digital output power supply. Nominally 2.5 V to 3.6 V                                                                                                                                                   |  |  |  |

| 16         | GND                 | Р           | Ground                                                                                                                                                                                                  |  |  |  |

| 17         | D3                  | DO          | Data Output. ADC DB3                                                                                                                                                                                    |  |  |  |

| 18         | D2                  | DO          | Data Output. ADC DB2                                                                                                                                                                                    |  |  |  |

| 19         | D1                  | DO          | Data Output. ADC DB1                                                                                                                                                                                    |  |  |  |

| 20         | D0                  | DO          | Data Output LSB. ADC DB0                                                                                                                                                                                |  |  |  |

|            |                     | •           | •                                                                                                                                                                                                       |  |  |  |

Type: AI = Analog Input, AO = Analog Output, DI = Digital Input, DO = Digital Output, P = Power.

$Figure\ 2-\underline{Terminal\ Connections\ and\ Pin\ Function\ Descriptions}$

# 4.0 ABSOLUTE MAXIMUM RATINGS. (T<sub>A</sub> = 25°C, unless otherwise noted)

| V <sub>D</sub> , V <sub>DD</sub> | 4V                             |

|----------------------------------|--------------------------------|

| Analog Input                     | 0.5V to V <sub>D</sub> + 0.5V  |

| Digital Inputs                   | 0.5V to V <sub>DD</sub> + 0.5V |

| VREF IN                          | 0.5V to V <sub>D</sub> + 0.5V  |

| Digital Output Current           | 20mA                           |

| Operating Temperature Range      | 55 °C to +125 °C               |

| Storage Temperature Range        | 65 °C to +150 °C               |

| Maximum Junction Temperature     | +150 °C                        |

#### **NOTES**

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions outside of those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

## 5.0 THERMAL CHARACTERISTICS:

|                  | Junction-to-Case    | Junction-to-Ambient |          |

|------------------|---------------------|---------------------|----------|

| Package Type     | $(\Theta_{\sf JC})$ | $(\Theta_{JA})$     | Units    |

| RC (LCC Package) | 35                  | 110                 | °C/W Max |

# AD9283S

# 6.0 Table I. Electrical Table:

|                                     |                 | Table I                                  |                   |                            |                            |              |

|-------------------------------------|-----------------|------------------------------------------|-------------------|----------------------------|----------------------------|--------------|

| Parameter See notes at end of table | Symbol          | Conditions 1/ Unless otherwise specified | Subgroup          | <u>Limit</u><br><u>Min</u> | <u>Limit</u><br><u>Max</u> | <u>Units</u> |

| DC ACCURACY                         |                 |                                          |                   |                            |                            |              |

| Differential Nonlinearity           | DNL             |                                          | 1                 | -1                         | +1.25                      | - LSB        |

|                                     | DINL            |                                          | 2, 3              | -1                         | +1.50                      |              |

| Integral Manlinearity               | INII            |                                          | 1                 | -1.25                      | +1.25                      | - LSB        |

| Integral Nonlinearity               | INL             |                                          | 2, 3              | -3.5                       | +3.5                       |              |

| No Missing Codes                    |                 |                                          | 1, 2, 3           | Guaranteed                 |                            |              |

| O-i F 0/                            |                 |                                          | 1                 | -6                         | +6                         | %FS          |

| Gain Error <u>2</u> /               | A <sub>E</sub>  |                                          | 2, 3              | -8                         | +8                         |              |

| ANALOG INPUT                        | 1               |                                          |                   |                            | l                          |              |

|                                     |                 |                                          | 1                 | -40                        | +40                        |              |

| Input Offset Voltage                | Vos             |                                          | 2, 3              | -45                        | +45                        | mV           |

| Reference Voltage                   |                 | With 100uA load                          | /ith 100uA load 1 | 1.2                        | 1.3                        |              |

|                                     | $V_{REF}$       | 2, 3 1.                                  | 1.17              | 1.33                       | V                          |              |

| Input Resistance                    | R <sub>IN</sub> |                                          | 1                 | 7                          | 13                         | k0           |

|                                     |                 |                                          | 2, 3              | 5                          | 16                         |              |

| SWITCHING PERFORMANCE               |                 |                                          | ,                 |                            |                            | 1            |

| Maximum Conversion Rate             | ENC<br>_freq    |                                          | 9,10,11           | 100                        |                            | MSPS         |

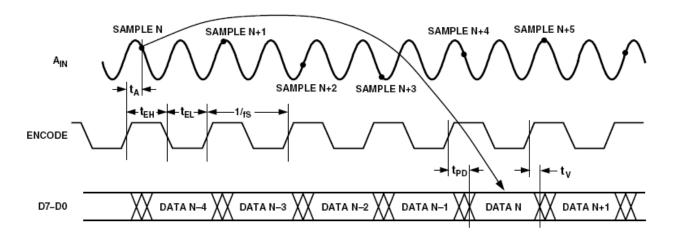

| Output Propagation Delay 3/         | t <sub>PD</sub> |                                          | 9                 |                            | 7.0                        | ns           |

| DIGITAL INPUTS, ENC, PWRDW          |                 |                                          |                   |                            |                            | <u> </u>     |

| Logic "1" Voltage                   | V <sub>IH</sub> |                                          | 1, 2, 3           | 2.0                        |                            | V            |

| Logic "0" Voltage                   | V <sub>IL</sub> |                                          | 1, 2, 3           |                            | 0.8                        | V            |

| Logic "1" Current                   | I <sub>IH</sub> |                                          | 1, 2, 3           | -1.0                       | 1.0                        | μA           |

| Logic "0" Current                   | I <sub>IL</sub> |                                          | 1, 2, 3           | -1.0                       | 1.0                        | μΑ           |

| DIGITAL OUTPUTS                     | 1               |                                          |                   |                            |                            | •            |

| Logic "1" Voltage                   | V <sub>OH</sub> |                                          | 1, 2, 3           | 2.95                       |                            | V            |

| Logic "0" Voltage                   | V <sub>OL</sub> |                                          | 1, 2, 3           |                            | 0.05                       | V            |

| POWER SUPPLY                        | 1               | 1                                        | ı                 |                            | 1                          | 1            |

| Power Dissipation 4/                | Pd              |                                          | 1, 2, 3           |                            | 120                        | mW           |

| Power-Down Dissipation              | Pd_pwrd<br>wn   |                                          | 1, 2, 3           |                            | 7                          | mW           |

| Power Supply Rejection<br>Ratio     | PSRR            | VD= 2.85 to 3.15V                        | 1                 | -18                        | 18                         | mV/V         |

| Table I, continued                           |                        |                         |          |                            |                            |              |

|----------------------------------------------|------------------------|-------------------------|----------|----------------------------|----------------------------|--------------|

| Parameter See notes at end of table          | Symbol                 | Conditions 1/           | Subgroup | <u>Limit</u><br><u>Min</u> | <u>Limit</u><br><u>Max</u> | <u>Units</u> |

| DYNAMIC PERFORMANCE 5/                       | DYNAMIC PERFORMANCE 5/ |                         |          |                            |                            |              |

| Signal-to-Noise Ratio<br>(Without Harmonics) | SNR                    | f <sub>IN</sub> = 41MHz | 4        | 43.5                       |                            | dB           |

| Signal-to-Noise Ratio<br>(With Harmonics)    | SINAD                  | f <sub>IN</sub> = 41MHz | 4        | 42.5                       |                            | dB           |

| 2 <sup>nd</sup> Harmonic Distortion          | 2 <sup>nd</sup> HD     | f <sub>IN</sub> = 41MHz | 4        | 49                         |                            | dBc          |

| 3 <sup>rd</sup> Harmonic Distortion          | 3 <sup>rd</sup> HD     | f <sub>IN</sub> = 41MHz | 4        | 47                         |                            | dBc          |

#### TABLE I NOTES:

- T<sub>A</sub> = +25 °C, T<sub>A</sub> Max = +125 °C, T<sub>A</sub> Min = -55 °C. V<sub>DD</sub> = 3.0V, V<sub>D</sub> = 3.0V; single-ended input; external reference, unless otherwise noted.

- Gain error and gain temperature coefficient are based on the ADC only (with a fixed 1.25V external reference).

- 2/ 3/ t<sub>PD</sub> is measured from the 1.5V level of the ENCODE input to the 50%/50% levels of the digital outputs swing. The digital output load during test is not to exceed an ac load of 10 pF or a dc current of  $\pm$  40  $\mu$ A.

- Power dissipation measured with encode at rated speed and a dc analog input.

- SNR/harmonics based on an analog input voltage of -0.7 dBFS referenced to a 1.024 V full-scale input range.

Figure 3 – <u>Timing Diagram</u>

## 7.0 Table II. Electrical Test Requirements:

| Table II                                |                                                         |  |  |  |

|-----------------------------------------|---------------------------------------------------------|--|--|--|

| Test Requirements                       | Subgroups (in accordance with MIL-PRF-38535, Table III) |  |  |  |

| Interim Electrical Parameters           | 1                                                       |  |  |  |

| Final Electrical Parameters             | 1, 2, 3, 4, 9, 10, 11 <u>1</u> / <u>2</u> /             |  |  |  |

| Group A Test Requirements               | 1, 2, 3, 4, 9, 10, 11                                   |  |  |  |

| Group C end-point electrical parameters | 1 <u>2</u> /                                            |  |  |  |

| Group D end-point electrical parameters | 1                                                       |  |  |  |

#### Notes:

- 1/ PDA apply to Subgroup 1 only. Delta's excluded from PDA.

- 2/ See Table III for Delta parameters. See Table I for test conditions.

## 8.0 Table III. Life Test / Burn-in Delta limits:

| Table III      |                    |              |  |  |

|----------------|--------------------|--------------|--|--|

| Test Symbol    | <u>Delta Limit</u> | <u>Units</u> |  |  |

| Pd             | ±5                 | mW           |  |  |

| Vos            | ±5                 | mV           |  |  |

| A <sub>E</sub> | ±1                 | %FS          |  |  |

#### 9.0 Life Test / Burn-In Circuit:

- 9.1 HTRB is not applicable for this drawing.

- 9.2 Burn-in is per MIL-STD-883 Method 1015 test condition D.

- 9.3 Steady state life test is per MIL-STD-883 Method 1005, test condition D.

# 10.0 MIL-STD-38535 QMLV exceptions:

- 10.1 Full WLA per MIL-STD-883 TM 5007 is not available for this product. SEM inspection only is available per MIL-STD-883, TM2018.

- 10.2 This product is manufactured in a MIL-PRF-38535 QMLQ certified wafer fab facility.

| Description of Change                                                                                                                                                                                                                               | Date                                                                                                                                                                                                                                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Initiate                                                                                                                                                                                                                                            | 5/12/2008                                                                                                                                                                                                                                                                                                                   |

| Correct Section 1.0 Scope description. Update deltas for product release. Minor format improvements and clarifications for product release.                                                                                                         | 11/4/2008                                                                                                                                                                                                                                                                                                                   |

| Remove post Group C specification limits in Table III such that only Delta limits are listed. Remove QMLV exception for testing in QMLQ facility. Add Figure 1 block diagram and update pin connections with descriptions. Formatting improvements. | 3/24/2010                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                             |

| _                                                                                                                                                                                                                                                   | Initiate  Correct Section 1.0 Scope description. Update deltas for product release. Minor format improvements and clarifications for product release.  Remove post Group C specification limits in Table III such that only Delta limits are listed. Remove QMLV exception for testing in QMLQ facility. Add Figure 1 block |