# WiMAX/BWA/WiBRO/LTE RF MxFE $2 \times 2$ MIMO Transceiver

AD9356

### **FEATURES**

RF transceiver with integrated 12-bit ADCs and DACs

Band: 2.3 GHz to 2.7 GHz

3.5 MHz < BW < 10 MHz

Superior receiver sensitivity with NF < 3.2 dB

Highly linear and spectrally pure transmitter

Tx EVM: -40 dB

SNR: >130 dB/Hz at frequency offset >8 MHz Transmit (Tx) power control range of 58 dB, resolution of 0.25 dB

Receive (Rx) gain control

Real-time monitor and control signals for manual gain Autonomous automatic gain control (AGC)

Automatic frequency correction: <0.012 ppm

Integrated fractional-N synthesizer Integrated phase noise: <0.4°rms

Multichip synchronization

Industry-standard JESD207 and ADI/Q digital interface

#### **APPLICATIONS**

WiMAX/BWA/WiBRO/LTE

Femtocell/picocell/microcell base stations

Fixed CPEs

## **GENERAL DESCRIPTION**

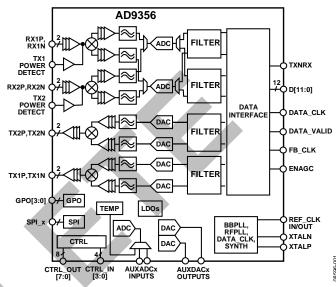

The AD9356 is a radio frequency (RF) transceiver with high performance dual receivers and transmitters, ideally suited for WiMAX, WiBRO, BWA, and LTE base stations and fixed CPEs. The RF MxFE\* combines an RF front end with a mixed-signal baseband, enabling an easy-to-use JESD207 or ADI/Q\* digital interface to the baseband processor (BBP), ASIC, or FPGA. The AD9356 operates in the 2.3 GHz to 2.7 GHz range, covering most licensed and unlicensed bands, and supports channel bandwidths of 3.5 MHz, 4.375 MHz, 5 MHz, 7 MHz, 8.75 MHz, and 10 MHz.

The direct-conversion receivers have state-of-the-art noise figure and linearity and require no external components with the exception of baluns. The complete RF subsystem integrates autonomous AGC loops, dc offset corrections, and quadrature calibrations, eliminating the need for high speed interaction with the BBP.

Two high dynamic range ADCs, followed by decimation and channel filters, digitize the received signals and produce 12-bit output signals at a sample rate determined by the bandwidth mode. The transmit path takes 12-bit input data and interpolates before converting to the analog domain and upconverting to the carrier frequency.

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

The highly linear transmit path has excellent spectral purity with sideband noise less than  $-130~\mathrm{dBc/Hz}$  at 8 MHz frequency offset and offers an error vector magnitude (EVM) of  $-40~\mathrm{dB}$ . An accurate power detector with a range of more than 50 dB in 0.25 dB steps measures the output power of each transmitter independently.

The reference frequency can be provided by an external reference clock or by an internal digitally controlled crystal oscillator (DCXO). The DCXO resolution is 0.012 ppm.

Using the built-in state machine to control the device, the AD9356 can be easily controlled in time division duplexing (TDD), half-duplex frequency division duplexing (HFDD), or, if two devices are used, frequency division duplexing (FDD) mode.

One three-input internal auxiliary ADC and two auxiliary DACs are available for system monitoring and control. A user-defined state machine can automatically sequence four GPOs. A single 3.3 V supply powers the device with on-chip low dropout linear voltage regulators (LDOs) providing all other required supplies. The AD9356 package is a 10 mm  $\times$  10 mm, 144-ball BGA.

# **NOTES**