# 16-Bit, 400 MSPS Digital-to-Analog Converter

AD9726

#### **FEATURES**

**Dynamic performance**

$SFDR \geq 78 \; dBc \; at \; f_{OUT} = 20 \; MHz$

IMD  $\geq$  82 dBc at f<sub>OUT</sub> = 70 MHz ACLR  $\geq$  76 dBc at f<sub>OUT</sub> = 70 MHz

$NSD \le -160 \text{ dB/Hz at } f_{\text{OUT}} = 70 \text{ MHz}$

**Precision calibrated linearity**

DNL  $\leq \pm 0.5$  LSB at +25°C

INL  $\leq \pm 1.0$  LSB at +25°C

THD  $\leq$  -95 dB at  $f_{OUT} = 1$  MHz

LVDS inputs with internal 100  $\boldsymbol{\Omega}$  terminations

Automatic data/clock timing synchronization

Single data rate or double data rate capable

**Differential current outputs**

Internal precision reference

Operates on 2.5 V and 3.3 V supplies

**Extended industrial temperature range**

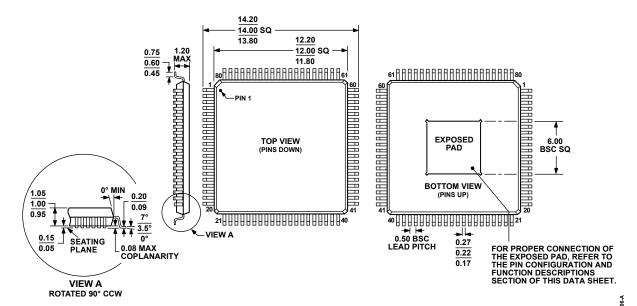

Thermally enhanced, 80-lead, RoHS-compliant

TQFP\_EP package

#### **APPLICATIONS**

Instrumentation

Test equipment

**Waveform synthesis**

**Communications systems**

### **GENERAL DESCRIPTION**

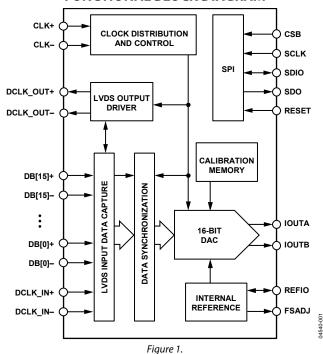

The AD9726 is a 16-bit digital-to-analog converter (DAC) that offers leading edge performance at conversion rates of up to 400 MSPS. The device uses low voltage differential signaling (LVDS) inputs and includes internal 100  $\Omega$  terminations. The analog output can be single-ended or differential current. An internal precision reference is included.

The AD9726 also features synchronization logic to monitor and optimize the timing between incoming data and the sample clock. This reduces system complexity and simplifies timing requirements. An LVDS clock output is also available to drive an external data pump in either single data rate (SDR) or double data rate (DDR) mode.

All device operation is fully programmable using the flexible serial port interface (SPI). The AD9726 is also fully functional in its default state for applications without a controller.

#### **FUNCTIONAL BLOCK DIAGRAM**

### **PRODUCT HIGHLIGHTS**

- A unique combination of precision and performance makes the AD9726 equally suited to applications with demanding frequency domain or demanding time domain requirements.

- Nonvolatile factory calibration assures a highly linear transfer function. Internal logic offers on demand selfcalibration for linearity even at extended operating temperatures.

- Proprietary architecture minimizes data dependent, discrete mixing spurs and offers enhanced dynamic performance over a wide range of output frequencies. High input data rates create a very high frequency synthesis bandwidth.

- 4. The fully automatic, transparent synchronizer maintains optimized timing between clock and data in real time and offers programmable control options for added flexibility.

- 5. Full-scale output current is external resistor programmable.

# **AD9726\* Product Page Quick Links**

Last Content Update: 11/01/2016

# Comparable Parts

View a parametric search of comparable parts

### Evaluation Kits <a> □</a>

· AD9726 Evaluation Board

### Documentation <a>□</a>

### **Application Notes**

- AN-320A: CMOS Multiplying DACs and Op Amps Combine to Build Programmable Gain Amplifier, Part 1

- AN-808: Multicarrier CDMA2000 Feasibility

- AN-834: AD9786/AD9726 Calibration Engine

- AN-912: Driving a Center-Tapped Transformer with a Balanced Current-Output DAC

#### **Data Sheet**

AD9726: 16-Bit, 400 MSPS Digital-to-Analog Converter Data Sheet

### Reference Materials

### **Solutions Bulletins & Brochures**

- Digital to Analog Converters ICs Solutions Bulletin

- Digital-to-Analog Converter ICs Solutions Bulletin, Volume 10, Issue 1

- Test & Instrumentation Solutions Bulletin, Volume 10, Issue 3

# Design Resources <a>□</a>

- · AD9726 Material Declaration

- PCN-PDN Information

- · Quality And Reliability

- · Symbols and Footprints

# Discussions <a>□</a>

View all AD9726 EngineerZone Discussions

# Sample and Buy -

Visit the product page to see pricing options

# Technical Support -

Submit a technical question or find your regional support number

<sup>\*</sup> This page was dynamically generated by Analog Devices, Inc. and inserted into this data sheet. Note: Dynamic changes to the content on this page does not constitute a change to the revision number of the product data sheet. This content may be frequently modified.

| TABLE OF CONTENTS                                      |                                                           |    |

|--------------------------------------------------------|-----------------------------------------------------------|----|

| Features1                                              | Typical Performance Characteristics                       | .2 |

| Applications                                           | Serial Port Interface                                     | .5 |

| Functional Block Diagram                               | Theory of Operation                                       | .7 |

| General Description                                    | DAC Clock and Data Clock Output1                          | .7 |

| Product Highlights                                     | Data Clock Input 1                                        | .7 |

| Revision History                                       | Data Synchronization Circuitry1                           | .8 |

| Specifications                                         | Analog Output1                                            | .8 |

| DC Specifications                                      | Internal Reference and Full-Scale Output                  | .9 |

| AC Specifications4                                     | Reset                                                     | 9  |

| Digital Signal Specifications5                         | Serial Port Interface 1                                   | .9 |

| Timing Specifications5                                 | SPI Pin Description2                                      | 0  |

| Timing Diagrams6                                       | Calibration2                                              | 0  |

| Absolute Maximum Ratings 8                             | Sync Logic Operation and Programming2                     | 22 |

| Thermal Resistance                                     | Outline Dimensions                                        | :4 |

| ESD Caution8                                           | Ordering Guide2                                           | :4 |

| Pin Configuration and Function Descriptions9           |                                                           |    |

| Terminology                                            |                                                           |    |

| REVISION HISTORY                                       |                                                           |    |

| 2/10—Rev. A to Rev. B                                  | 11/05—Rev. 0 to Rev. A                                    |    |

| Changes to Table 45                                    | Changes to Features                                       |    |

| Added Figure 4 and Figure 5, Renumbered Sequentially 6 | Changes to Table 3 and Table 4                            |    |

| Changes to Figure 5 and Table 79                       | Changes to the Terminology Section 1                      |    |

| Changes to Table 916                                   | Changes to the Driving the DAC Clock Inputs Section 1     |    |

| Added Data Synchronization Circuitry Bypass Section 18 | Changes to the Reset and Serial Port Interface Sections 1 |    |

| Changes to Ordering Guide                              | Updated Outline Dimensions                                |    |

|                                                        | Changes to the Ordering Guide                             | .2 |

7/05—Revision 0: Initial Version

# **SPECIFICATIONS**

### **DC SPECIFICATIONS**

$DBVDD = AVDD1 = AVDD2 = 3.3 \text{ V}, DVDD = CLKVDD = ADVDD = ACVDD = 2.5 \text{ V}, I_{OUT\text{-FS}} = 20 \text{ mA}, internal reference, the substitution of the property of the propert$  $T_{\mbox{\scriptsize MIN}}$  to  $T_{\mbox{\scriptsize MAX}},$  unless otherwise specified.

Table 1.

| Parameter                                                 | Min  | Тур   | Max  | Unit         |

|-----------------------------------------------------------|------|-------|------|--------------|

| ACCURACY <sup>1</sup>                                     |      |       |      |              |

| DNL                                                       |      | ±0.5  | ±1.0 | LSB          |

| INL                                                       |      | ±1.0  | ±2.5 | LSB          |

| Offset Error                                              |      | 0.003 |      | % FS         |

| Gain Error                                                |      | 0.003 |      | % FS         |

| ANALOG OUTPUT                                             |      |       |      |              |

| Full-Scale Current                                        |      | 20    |      | mA           |

| Compliance Voltage                                        |      | ±1    |      | V            |

| Output Impedance                                          |      | 10    |      | ΜΩ           |

| INTERNAL REFERENCE                                        |      |       |      |              |

| Output Voltage                                            | 1.18 | 1.22  | 1.27 | V            |

| Output Current <sup>2</sup>                               |      | 1     |      | μΑ           |

| EXTERNAL REFERENCE                                        |      |       |      |              |

| Input Voltage                                             |      | 1.2   |      | V            |

| Input Resistance                                          |      | 10    |      | ΜΩ           |

| Small Signal Bandwidth                                    |      | 200   |      | kHz          |

| TEMPERATURE COEFFICIENTS                                  |      |       |      |              |

| Gain Drift                                                |      | ±10   |      | ppm of FS/°C |

| Offset Drift                                              |      | ±10   |      | ppm of FS/°C |

| Reference Drift                                           |      | ±30   |      | ppm/°C       |

| POWER SUPPLIES <sup>3</sup>                               |      |       |      |              |

| AVDD1, AVDD2                                              |      |       |      |              |

| Voltage Range                                             | 3.13 |       | 3.47 | V            |

| Supply Current (I <sub>AVDD1</sub> + I <sub>AVDD2</sub> ) |      | 52    | 60   | mA           |

| ADVDD, ACVDD                                              |      |       |      |              |

| Voltage Range                                             | 2.37 |       | 2.63 | V            |

| Supply Current $(I_{ACVDD} + I_{ADVDD})$                  |      | 16    | 18   | mA           |

| CLKVDD                                                    |      |       |      |              |

| Voltage Range                                             | 2.37 |       | 2.63 | V            |

| Supply Current (Iclkvdd)                                  |      | 45    | 50   | mA           |

| DVDD                                                      |      |       |      |              |

| Voltage Range                                             | 2.37 |       | 2.63 | V            |

| Supply Current (I <sub>DVDD</sub> )                       |      | 80    | 90   | mA           |

| DBVDD                                                     |      |       |      |              |

| Voltage Range                                             | 3.13 |       | 3.47 | V            |

| Supply Current (IDBVDD)                                   |      | 16    | 18   | mA           |

| POWER DISSIPATION (P <sub>DISS</sub> )                    |      | 575   |      | mW           |

| Sleep Mode                                                |      | 465   |      | mW           |

| Power-Down Mode                                           |      | ≤10   |      | mW           |

| OPERATING TEMPERATURE RANGE                               | -40  |       | +85  | °C           |

$<sup>^{1}</sup>$  T<sub>AMB</sub> = 25°C.  $^{2}$  Use buffer amplifier to drive external load.

$<sup>^3</sup>$  Supply currents and power dissipation measured in SDR with  $f_{DAC}$  = 400 MHz and  $f_{OUT}$  = 1 MHz.

### **AC SPECIFICATIONS**

$DBVDD = AVDD1 = AVDD2 = 3.3 \text{ V}, DVDD = CLKVDD = ADVDD = ACVDD = 2.5 \text{ V}, I_{OUT\text{-}FS} = 20 \text{ mA}, internal reference}, T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise specified}.$

Table 2.

| Parameter                                                                             | Min Typ Max | Unit   |

|---------------------------------------------------------------------------------------|-------------|--------|

| DYNAMIC PERFORMANCE                                                                   |             |        |

| Output Settling Time (tst) to 0.1%                                                    | 10.5        | ns     |

| Output Rise Time (10% to 90%)                                                         | 500         | ns     |

| Output Fall Time (90% to 10%)                                                         | 500         | ns     |

| Output Noise (I <sub>OUTFS</sub> = 20 mA)                                             | 45          | pA/√Hz |

| TOTAL HARMONIC DISTORTION (THD)                                                       |             |        |

| $f_{DAC} = 400 \text{ MHz}$ , $f_{OUT} = 1 \text{ MHz}$ , 0 dBFS                      | <b>-95</b>  | dB     |

| SPURIOUS-FREE DYNAMIC RANGE (SFDR)                                                    |             |        |

| $f_{DAC} = 400 \text{ MHz}, 0 \text{ dBFS}$                                           |             |        |

| $f_{OUT} = 20 \text{ MHz}$                                                            | 78          | dBc    |

| $f_{OUT} = 70 \text{ MHz}$                                                            | 68          | dBc    |

| $f_{OUT} = 140 \text{ MHz}$                                                           | 62          | dBc    |

| $f_{DAC} = 400 \text{ MHz}, -3 \text{ dBFS}$                                          |             |        |

| $f_{OUT} = 20 \text{ MHz}$                                                            | 80          | dBc    |

| $f_{OUT} = 70 \text{ MHz}$                                                            | 70          | dBc    |

| $f_{OUT} = 140 \text{ MHz}$                                                           | 62          | dBc    |

| $f_{DAC} = 200 \text{ MHz}, 0 \text{ dBFS}$                                           |             |        |

| $f_{OUT} = 20 \text{ MHz}$                                                            | 84          | dBc    |

| $f_{OUT} = 70 \text{ MHz}$                                                            | 62          | dBc    |

| $f_{DAC} = 200 \text{ MHz}$ , $-3 \text{ dBFS}$                                       |             |        |

| $f_{OUT} = 20 \text{ MHz}$                                                            | 82          | dBc    |

| $f_{OUT} = 70 \text{ MHz}$                                                            | 68          | dBc    |

| TWO-TONE INTERMODULATION DISTORTION (IMD)                                             |             |        |

| $f_{DAC} = 400 \text{ MHz}, 0 \text{ dBFS}$                                           |             |        |

| $f_{OUT1} = 20 \text{ MHz}, f_{OUT2} = 21 \text{ MHz}$                                | 86          | dBc    |

| $f_{OUT1} = 70 \text{ MHz}, f_{OUT2} = 71 \text{ MHz}$                                | 82          | dBc    |

| $f_{OUT1} = 140 \text{ MHz}, f_{OUT2} = 141 \text{ MHz}$                              | 74          | dBc    |

| ADJACENT CHANNEL LEAKAGE RATIO (ACLR)                                                 |             |        |

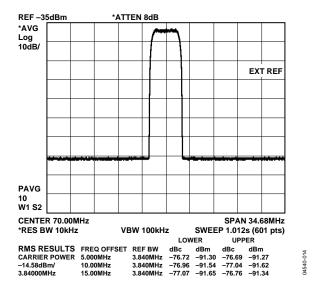

| f <sub>DATA</sub> = 245.76 MSPS, f <sub>CARRIER</sub> = 70 MHz, One-Carrier WCDMA     | 76          | dBc    |

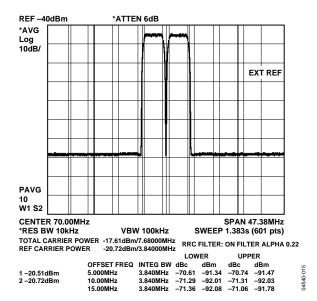

| f <sub>DATA</sub> = 245.76 MSPS, f <sub>CARRIER</sub> = 70 MHz, Two-Carrier WCDMA     | 70          | dBc    |

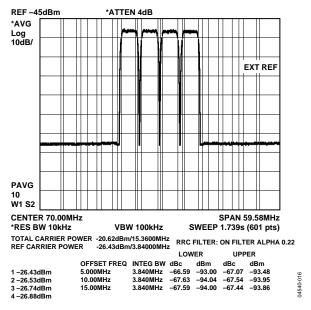

| f <sub>DATA</sub> = 245.76 MSPS, f <sub>CARRIER1</sub> = 70 MHz, Four-Carrier WCDMA   | 66          | dBc    |

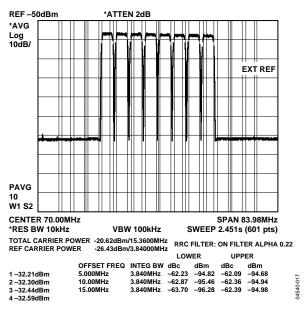

| $f_{DATA} = 245.76 \text{ MSPS}, f_{CARRIER1} = 70 \text{ MHz}, Eight-Carrier WCDMA}$ | 62          | dBc    |

| NOISE SPECTRAL DENSITY (NSD)                                                          |             |        |

| $f_{DAC} = 400 \text{ MHz}$ , $f_{OUT} = 70 \text{ MHz}$ , 0 dBFS                     | -160        | dBm/Hz |

| $f_{DAC} = 400 \text{ MHz}$ , $f_{OUT} = 70 \text{ MHz}$ , $-3 \text{ dBFS}$          | -163        | dBm/Hz |

| $f_{DAC} = 400 \text{ MHz}$ , $f_{OUT} = 70 \text{ MHz}$ , $-6 \text{ dBFS}$          | -165        | dBm/Hz |

| UPDATE RATE                                                                           | 0 400       | MSPS   |

### **DIGITAL SIGNAL SPECIFICATIONS**

$DBVDD = AVDD1 = AVDD2 = 3.3 \text{ V}, DVDD = CLKVDD = ADVDD = ACVDD = 2.5 \text{ V}, I_{OUT\text{-}FS} = 20 \text{ mA}, internal reference}, T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise specified}.$

Table 3.

| Parameter                                | Min | Тур  | Max  | Unit |

|------------------------------------------|-----|------|------|------|

| DAC CLOCK INPUTS (CLK±)                  |     |      |      |      |

| Differential Voltage                     | 0.5 | 1.0  |      | V    |

| Common-Mode Voltage                      | 1.0 | 1.25 |      | V    |

| LVDS INPUTS (DB[15:0]±, DCLK_IN±)        |     |      |      |      |

| Input Voltage Range                      | 825 |      | 1575 | mV   |

| Differential Threshold Voltage           |     |      | 100  | mV   |

| Differential Input Impedance             |     | 100  |      | Ω    |

| LVDS OUTPUT (DCLK_OUT±)                  |     |      |      |      |

| Differential Output Voltage <sup>1</sup> | 250 | 400  |      | mV   |

| Offset Voltage                           | 1.0 | 1.2  |      | V    |

| Short-Circuit Output Current             |     | 20   |      | mA   |

| CMOS INPUTS (CSB, SCLK, SDIO, RESET)     |     |      |      |      |

| Logic 0 Voltage                          |     |      | 0.5  | V    |

| Logic 1 Voltage                          | 2.5 |      |      | V    |

| Input Current                            |     | 1    |      | nA   |

| CMOS OUTPUTS (SDO, SDIO)                 |     |      |      |      |

| Logic 0 Voltage                          |     |      | 0.5  | V    |

| Logic 1 Voltage                          | 3.0 |      |      | V    |

| Short-Circuit Output Current             |     | 10   |      | mA   |

| CONTROL INPUTS (SPI_DIS, SDR_EN)         |     |      |      |      |

| Logic 0 Voltage                          |     |      | 0.5  | V    |

| Logic 1 Voltage                          | 2.0 |      |      | V    |

| Input Current                            |     | 1    |      | nA   |

$<sup>^{\</sup>text{1}}$  With 100  $\Omega$  external load.

### **TIMING SPECIFICATIONS**

$DBVDD = AVDD1 = AVDD2 = 3.3 \text{ V}, DVDD = CLKVDD = ADVDD = ACVDD = 2.5 \text{ V}, I_{OUT\text{-}FS} = 20 \text{ mA}, internal reference}, T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise specified}.$

Table 4.

| Parameter                                                | Min  | Тур  | Max  | Unit             |

|----------------------------------------------------------|------|------|------|------------------|

| LVDS DATA BUS                                            |      |      |      |                  |

| Data Synchronization Enabled (Default)                   |      |      |      |                  |

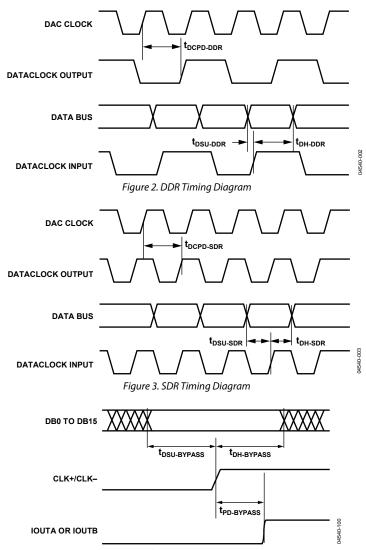

| DDR DCLK_OUT± Propagation Delay (tdcpd-ddr)              |      |      | 2000 | ps               |

| DDR DB[15:0]± Setup Time (t <sub>DSU-DDR</sub> )         | -100 |      |      | ps               |

| DDR DB[15:0]± Hold Time (t <sub>DH-DDR</sub> )           | 500  |      |      | ps               |

| SDR DCLK_OUT± Propagation Delay (t <sub>DCPD-SDR</sub> ) |      |      | 300  | ps               |

| SDR DB[15:0]± Setup Time (t <sub>DSU-SDR</sub> )         | -100 |      |      | ps               |

| SDR DB[15:0] $\pm$ Hold Time (t <sub>DH-SDR</sub> )      | 500  |      |      | ps               |

| Data Synchronization Bypassed                            |      |      |      |                  |

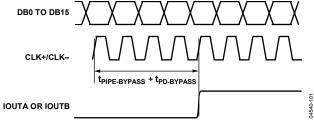

| DB[15:0]± Setup Time (t <sub>DSU-BYPASS</sub> )          | 800  |      |      | ps               |

| DB[15:0]± Hold Time (t <sub>DH-BYPASS</sub> )            | 50   |      |      | ps               |

| CLK± to IOUT Propagation Delay (tpd-BYPASS)              |      | 0.85 |      | ns               |

| DB[15:0]± to IOUT Pipeline Delay (tpipe-BYPASS)          |      | 4    |      | DAC clock cycles |

| Parameter                              | Min | Тур | Max | Unit |

|----------------------------------------|-----|-----|-----|------|

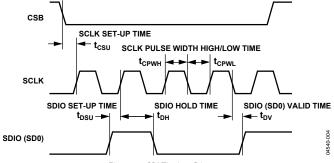

| SERIAL PORT INTERFACE                  |     |     |     |      |

| SCLK Frequency (f <sub>SCLK</sub> )    |     |     | 15  | MHz  |

| SCLK Rise/Fall Time                    |     |     | 1   | ms   |

| SCLK Pulse Width High (tcpwh)          | 30  |     |     | ns   |

| SCLK Pulse Width Low (tcpwl)           | 30  |     |     | ns   |

| SCLK Setup Time (t <sub>CSU</sub> )    | 30  |     |     | ns   |

| SDIO Setup Time (t <sub>DSU</sub> )    | 30  |     |     | ns   |

| SDIO Hold Time (t <sub>DH</sub> )      | 0   |     |     | ns   |

| SDIO/SDO Valid Time (t <sub>DV</sub> ) |     |     | 30  | ns   |

| RESET PULSE WIDTH                      | 1.5 |     |     | ns   |

### **TIMING DIAGRAMS**

Figure 4. Data Synchronization Bypass Timing Diagram

Figure 5. Data Synchronization Bypass Pipeline Delay

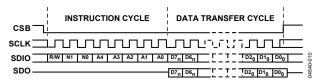

Figure 6. SPI Timing Diagram

### **ABSOLUTE MAXIMUM RATINGS**

Table 5.

| Table 3.         |                 |                  |

|------------------|-----------------|------------------|

| Parameter        | With Respect to | Rating           |

| DBVDD, AVDD1,    | DBGND, AGND1,   | –0.3 V to 3.6 V  |

| AVDD2            | AGND2           |                  |

| DVDD, CLKVDD,    | DGND, CLKGND,   | –0.3 V to 2.8 V  |

| ACVDD, ADVDD     | ACGND, ADGND    |                  |

| DBGND, AGND1,    | DBGND, AGND1,   | −0.3 V to +0.3 V |

| AGND2            | AGND2           |                  |

| DGND, CLKGND,    | DGND, CLKGND,   | −0.3 V to +0.3 V |

| ACGND, ADGND     | ACGND, ADGND    |                  |

| REFIO, FSDAJ     | AGND1           | -0.3 V to AVDD1  |

|                  |                 | + 0.3 V          |

| IOUTA, IOUTB     | AGND1           | -1.0 V to AVDD1  |

|                  |                 | + 0.3 V          |

| CLK±             | CLKGND          | −0.3 V to CLKVDD |

|                  |                 | + 0.3 V          |

| DB[15:0]±,       | DBGND           | −0.3 V to DBVDD  |

| DCLK_IN±,        |                 | + 0.3 V          |

| DCLK_OUT±        |                 |                  |

| CSB, SCLK, SDIO, | DBGND           | -0.3 V to DBVDD  |

| SDO, RESET, REXT |                 | + 0.3 V          |

| SDR_EN, SPI_DIS  | ADGND           | −0.3 V to ADVDD  |

|                  |                 | + 0.3 V          |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### THERMAL RESISTANCE

Thermal impedance can be lowered to 23°C/W by soldering the exposed package pad to an external heat sink (for example, the internal PCB copper ground plane). However, this is not necessary for the power dissipation and operating temperature range of the AD9726.

**Table 6. Thermal Resistance**

| Package Type                                | θја | Unit |

|---------------------------------------------|-----|------|

| 80-Lead TQFP_EP Package, Thermally Enhanced | 32  | °C/W |

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

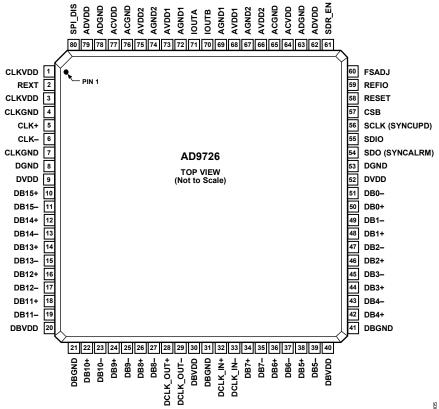

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

NOTES 1. THE EXPOSED PAD SHOULD BE CONNECTED TO GROUND FOR ELECTRICAL AND THERMAL PURPOSES.  $\frac{50}{9}$

Figure 7. Pin Configuration

**Table 7. Pin Function Descriptions**

| Pin |          |                               | Pin |           |                              |

|-----|----------|-------------------------------|-----|-----------|------------------------------|

| No. | Mnemonic | Description                   | No. | Mnemonic  | Description                  |

| 1   | CLKVDD   | Clock Supply Voltage          | 22  | DB10+     | Data Bit 10 True             |

| 2   | REXT     | Sets Data Clock Output Drive1 | 23  | DB10-     | Data Bit 10 Complement       |

| 3   | CLKVDD   | Clock Supply Voltage          | 24  | DB9+      | Data Bit 9 True              |

| 4   | CLKGND   | Clock Supply Common           | 25  | DB9-      | Data Bit 9 Complement        |

| 5   | CLK+     | DAC Clock Input True          | 26  | DB8+      | Data Bit 8 True              |

| 6   | CLK-     | DAC Clock Input Complement    | 27  | DB8-      | Data Bit 8 Complement        |

| 7   | CLKGND   | Clock Supply Common           | 28  | DCLK_OUT+ | Data Clock Output True       |

| 8   | DGND     | Digital Supply Common         | 29  | DCLK_OUT- | Data Clock Output Complement |

| 9   | DVDD     | Digital Supply Voltage        | 30  | DBVDD     | Data Bus Supply Voltage      |

| 10  | DB15+    | Data Bit 15 True              | 31  | DBGND     | Data Bus Supply Common       |

| 11  | DB15-    | Data Bit 15 Complement        | 32  | DCLK_IN+  | Data Clock Input True        |

| 12  | DB14+    | Data Bit 14 True              | 33  | DCLK_IN-  | Data Clock Input Complement  |

| 13  | DB14-    | Data Bit 14 Complement        | 34  | DB7+      | Data Bit 7 True              |

| 14  | DB13+    | Data Bit 13 True              | 35  | DB7-      | Data Bit 7 Complement        |

| 15  | DB13-    | Data Bit 13 Complement        | 36  | DB6+      | Data Bit 6 True              |

| 16  | DB12+    | Data Bit 12 True              | 37  | DB6-      | Data Bit 6 Complement        |

| 17  | DB12-    | Data Bit 12 Complement        | 38  | DB5+      | Data Bit 5 True              |

| 18  | DB11+    | Data Bit 11 True              | 39  | DB5-      | Data Bit 5 Complement        |

| 19  | DB11-    | Data Bit 11 Complement        | 40  | DBVDD     | Data Bus Supply Voltage      |

| 20  | DBVDD    | Data Bus Supply Voltage       | 41  | DBGND     | Data Bus Supply Common       |

| 21  | DBGND    | Data Bus Supply Common        | 42  | DB4+      | Data Bit 4 True              |

| Pin |                |                                               |

|-----|----------------|-----------------------------------------------|

| No. | Mnemonic       | Description                                   |

| 43  | DB4-           | Data Bit 4 Complement                         |

| 44  | DB3+           | Data Bit 3 True                               |

| 45  | DB3-           | Data Bit 3 Complement                         |

| 46  | DB2+           | Data Bit 2 True                               |

| 47  | DB2-           | Data Bit 2 Complement                         |

| 48  | DB1+           | Data Bit 1 True                               |

| 49  | DB1-           | Data Bit 1 Complement                         |

| 50  | DB0+           | Data Bit 0 True                               |

| 51  | DB0-           | Data Bit 0 Complement                         |

| 52  | DVDD           | Digital Supply Voltage                        |

| 53  | DGND           | Digital Supply Common                         |

| 54  | SDO (SYNCALRM) | SPI Data Output (SYNCALRM) <sup>2</sup>       |

| 55  | SDIO           | SPI Data Input/Output <sup>3</sup>            |

| 56  | SCLK (SYNCUPD) | SPI Clock Input (SYNCUPD)4                    |

| 57  | CSB            | SPI Chip Select Bar (Active Low)              |

| 58  | RESET          | Hardware Reset (Active High)                  |

| 59  | REFIO          | Internal Reference Input/Output⁵              |

| 60  | FSADJ          | Output Current Full-Scale Adjust <sup>6</sup> |

| 61  | SDR_EN         | Single Data Rate Mode Enable <sup>7</sup>     |

| 62  | ADVDD          | Analog Supply Voltage                         |

| 63  | ADGND          | Analog Supply Common                          |

| 64  | ACVDD          | Analog Supply Voltage                         |

| 65  | ACGND          | Analog Supply Common                          |

| 66  | AVDD2          | Analog Supply Voltage                         |

| 67  | AGND2          | Analog Supply Common                          |

| 68  | AVDD1          | Analog Supply Voltage                         |

| Pin<br>No. | Mnemonic | Description                                                                                                                                          |

|------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 69         | AGND1    | Analog Supply Common                                                                                                                                 |

| 70         | IOUTB    | Analog Current Output Complement                                                                                                                     |

| 71         | IOUTA    | Analog Current Output True                                                                                                                           |

| 72         | AGND1    | Analog Supply Common                                                                                                                                 |

| 73         | AVDD1    | Analog Supply Voltage                                                                                                                                |

| 74         | AGND2    | Analog Supply Common                                                                                                                                 |

| 75         | AVDD2    | Analog Supply Voltage                                                                                                                                |

| 76         | ACGND    | Analog Supply Common                                                                                                                                 |

| 77         | ACVDD    | Analog Supply Voltage                                                                                                                                |

| 78         | ADGND    | Analog Supply Common                                                                                                                                 |

| 79         | ADVDD    | Analog Supply Voltage                                                                                                                                |

| 80         | SPI_DIS  | Serial Port Interface Disable <sup>8</sup>                                                                                                           |

|            | EPAD     | Analog Ground. Serves as an electrical connection to the substrate of the die and should be connected to ground for electrical and thermal purposes. |

$<sup>^{1}</sup>$  Nominally 1  $k\Omega$  to DBGND (may be omitted if data clock output is unused).

<sup>&</sup>lt;sup>2</sup> SDO is output in 4-wire SPI mode and three-state in 3-wire SPI mode. If SPI is disabled (SPI\_DIS = ADVDD), the alternate pin function is SYNCALRM output.

<sup>&</sup>lt;sup>3</sup> SDIO is input only in 4-wire SPI mode and bidirectional in 3-wire SPI mode. <sup>4</sup> If SPI is disabled (SPI\_DIS = ADVDD), the alternate pin function is SYNCUPD.

$<sup>^5</sup>$  Bypass with 0.1  $\mu F$  to AGND1. Use the buffer amp to drive external circuitry. Limit the output current to 1  $\mu A$ . Apply an external reference to this pin.

$<sup>^6</sup>$  Nominally 2 k $\Omega$  to AGND1 for 20 mA full-scale output (internal reference). <sup>7</sup> If SPI is disabled, tie the pin to ADVDD to enable SDR. Otherwise, tie to

$<sup>^{\</sup>rm 8}$  Tie the pin to ADVDD to disable SPI; otherwise, tie to ADGND.

### **TERMINOLOGY**

### Integral Nonlinearity (INL)

The maximum deviation of the actual analog output from the ideal output, as determined by a straight line drawn from zero scale to full scale.

### Differential Nonlinearity (DNL)

A measure of the maximum deviation in analog output associated with any single value change in the digital input code relative to an ideal LSB.

#### **Offset Error**

The deviation of the output current from the ideal zero-scale current. For differential outputs, 0 mA is expected at  $I_{\rm OUTA}$  when all inputs are low, and 0 mA is expected at  $I_{\rm OUTB}$  when all inputs are high.

### Monotonicity

A DAC is monotonic if the analog output increases or remains constant in response to an increase in the digital input.

#### **Gain Error**

The deviation of the output current from the ideal full-scale current. Actual full-scale output current is determined by subtracting the output when all inputs are low from the output when all inputs are high.

### **Output Compliance Range**

The range of allowable voltage seen by the analog output of a current output DAC. Operation beyond the compliance limits may cause output stage saturation and/or breakdown resulting in nonlinear performance.

### **Temperature Drift**

Temperature drift is specified as the maximum change in a parameter from ambient temperature (25°C) to either  $T_{\text{MIN}}$  or  $T_{\text{MAX}}$  and is typically reported as ppm/°C.

#### **Power Supply Rejection**

The maximum change in the full-scale output as all power supplies are varied over their respective operating voltage range.

### Spurious-Free Dynamic Range (SFDR)

The difference in decibels between the peak amplitude of a test tone and the peak amplitude of the largest spurious signal over the specified bandwidth.

### **Intermodulation Distortion (IMD)**

The difference in decibels between the maximum peak amplitude of two test tones and the maximum peak amplitude of the distortion products created from the sum or difference of integer multiples of the test tones.

### Adjacent Channel Leakage Ratio (ACLR)

The ratio between the measured power of a wideband signal within a channel relative to the measured power in an empty adjacent channel.

### **Noise Spectral Density (NSD)**

The measured noise power over a 1 Hz bandwidth seen at the analog output.

### **Total Harmonic Distortion (THD)**

The ratio in decibels of the rms power sum of the first six harmonic components to the rms power of the output signal.

## TYPICAL PERFORMANCE CHARACTERISTICS

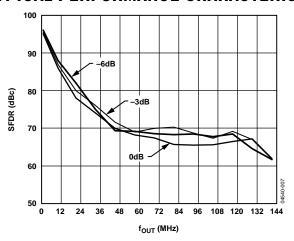

Figure 8. SFDR vs. fout at 400 MSPS

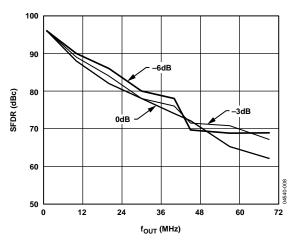

Figure 9. SFDR vs. f<sub>OUT</sub> at 200 MSPS

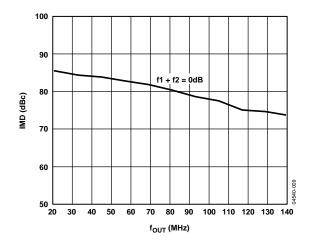

Figure 10. Two-Tone IMD vs. f<sub>OUT</sub> at 400 MSPS

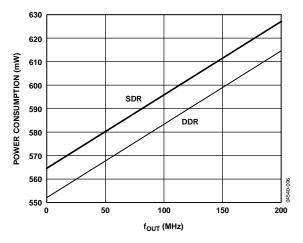

Figure 11. Power Consumption vs.  $f_{OUT}$  at 400 MSPS

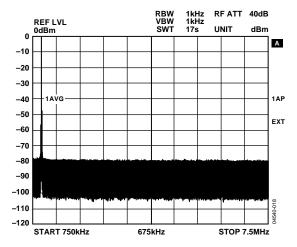

Figure 12. THD at 400 MSPS and  $f_{OUT} = 1$  MHz (Diplexer Low-Pass Output Showing 0 dBm Fundamental (See the Performance Effects of Calibration Section))

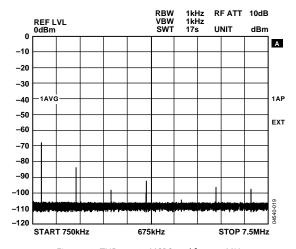

Figure 13. THD at 400 MSPS and f<sub>OUT</sub> = 1 MHz (Diplexer High-Pass Output Showing Harmonics Before Calibration; (See the Performance Effects of Calibration Section))

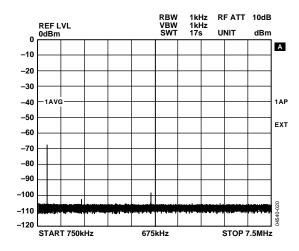

Figure 14. THD at 400 MSPS and f<sub>OUT</sub> = 1 MHz (Diplexer High-Pass Output Showing Harmonics After Calibration,

See the Performance Effects of Calibration Section)

Figure 15. One-Carrier WCDMA at 400 MSPS  $f_{OUT} = 70 \text{ MHz}$

Figure 16. Two-Carrier WCDMA at 400 MSPS  $f_{OUT} = 70 \text{ MHz}$

Figure 17. Four-Carrier WCDMA at 400 MSPS f<sub>OUT</sub> = 70 MHz

Figure 18. Eight-Carrier WCDMA at 400 MSPS  $f_{OUT} = 70 \text{ MHz}$

# **SERIAL PORT INTERFACE**

Table 8. SPI Register Map

| Addr | Bit 7     | Bit 6     | Bit 5     | Bit 4     | Bit 3     | Bit 2     | Bit 1      | Bit 0      |

|------|-----------|-----------|-----------|-----------|-----------|-----------|------------|------------|

| 0x00 | SDIODIR   | DATADIR   | SWRESET   | SLEEP     | PWRDWN    |           |            | EXTREF     |

| 0x02 | DATAFMT   | DATARATE  | INVDCLKI  | INVDCLKO  | DISDCLKO  | SYNCMAN   | SYNCUPD    | SYNCALRM   |

| 0x0E |           |           | CALMEM[1] | CALMEM[0] |           | CALCLK[2] | CALCLK[1]  | CALCLK[0]  |

| 0x0F | SCALSTAT  | SELFCAL   | XFERSTAT  | MEMXFER   | SMEMWR    | SMEMRD    | FMEMRD     | UNCAL      |

| 0x10 | MEMADR[7] | MEMADR[6] | MEMADR[5] | MEMADR[4] | MEMADR[3] | MEMADR[2] | MEMADR[1]  | MEMADR[0]  |

| 0x11 |           |           | MEMDAT[5] | MEMDAT[4] | MEMDAT[3] | MEMDAT[2] | MEMDAT[1]  | MEMDAT[0]  |

| 0x15 |           |           |           |           |           |           | SYNCOUT[1] | SYNCOUT[0] |

| 0x16 |           | BYPASS    | SYNCEXT   | SYNCIN[1] | SYNCIN[0] |           |            |            |

Table 9. SPI Register Bit Default and Descriptions Values

| Addr | Name                | Bits   | I/O | Default | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------|---------------------|--------|-----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x00 | SDIODIR             | 7      | 1   | 0       | 0: SDIO is input only (4-wire SPI mode), and SDO is used for output. 1: SDIO is input/output (3-wire SPI mode), and SDO is unused.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | DATADIR             | 6      | 1   | 0       | 0: SPI serial data byte is MSB first format. 1: SPI serial data byte is LSB first format.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      | SWRESET             | 5      | 1   | 0       | 1: software reset: SPI registers (except 0x00) to default values. <sup>1</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      | SLEEP               | 4      | 1   | 0       | 1: analog outputs temporarily disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | PWRDWN              | 3      | 1   | 0       | 1: full device power-down; all circuits disabled except SPI.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | EXTREF              | 0      | 1   | 0       | 1: power-down internal reference; use external reference source. <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0x02 | DATAFMT             | 7      | 1   | 0       | 0: input data-word is twos complement binary format. 1: input data-word is unsigned binary format.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | DATARATE            | 6      | 1   | 0       | 0: DDR mode.<br>1: SDR mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | INVDCLKI            | 5      | 1   | 0       | 1: inverts the polarity of the data clock input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | INVDCLKO            | 4      | 1   | 0       | 1: inverts the polarity of the data clock output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      | DISDCLKO            | 3      | 1   | 0       | 1: disables the data clock output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | SYNCMAN             | 2      | 1   | 0       | 1: enables sync manual mode; disables automatic update.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | SYNCUPD             | 1      | 1   | 0       | 1: forces manual sync update.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | SYNCALRM            | 0      | 0   | 0       | 1: indicates that sync logic requires update.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0x0E | CALMEM              | [2:0]  | Ι   | 000     | 2-bit SMEM contents and calibration status indicator. 00: uncalibrated; SMEM contains default values (63). 01: self-calibrated; SMEM contains values from self-calibration. 10: factory-calibrated; SMEM values are transferred from FMEM. 11: user-calibrated; SMEM contains user-entered values. 3-bit self-calibration clock divider ratio. Affects time available for algorithm settling. Each value increase reduces time by 50%.³ 000: self-calibration clock is DAC clock/4096 (maximum self-calibration settling time for highest linearity accuracy). 001,010,011: self-calibration clock is DAC clock/2048,1024,512. 100,101,110: self-calibration clock is DAC clock/256,128,64. 111: self-calibration clock is DAC clock/32 (minimum self-calibration settling time for |

| 0.05 | CCALCTAT            | -      |     |         | fastest algorithm completion).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 0x0F | SCALSTAT            | 7      | 0   | 0       | 1: indicates completion of self-calibration cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | SELFCAL             | 6      | 0   | 0       | 1: initiates self-calibration cycle. <sup>4</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      | XFERSTAT<br>MEMXFER | 5<br>4 | l   | 0       | 1: indicates completion of memory transfer cycle.  1: initiates FMEM to SMEM transfer. <sup>5</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      | SMEMWR              | 3      |     | 0       | 1: initiates FMEM to SMEM transfer.  1: enables static memory (SMEM) write operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | SMEMRD              | 2      |     | 0       | 1: enables static memory (SMEM) write operation.  1: enable sstatic memory (SMEM) read operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      |                     |        |     | -       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      | FMEMRD<br>UNCAL     | 0      |     | 0       | 1: enables factory memory (FMEM) read operation. 1: enables uncalibrated operation; all SMEM to default values. <sup>6</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | UNCAL               | U      | I   | U       | i. enables uncalibrated operation; all swicivi to default values."                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Addr | Name    | Bits  | I/O | Default  | Description                                                                            |  |

|------|---------|-------|-----|----------|----------------------------------------------------------------------------------------|--|

| 0x10 | MEMADR  | [7:0] | I   | 00000000 | bit memory address value for read/write operations.                                    |  |

| 0x11 | MEMDAT  | [5:0] | I/O | 000000   | -bit memory data value for read/write operations.                                      |  |

| 0x15 | SYNCOUT | [1:0] | 0   | 00       | bit output value indicates current sync quadrant.                                      |  |

| 0x16 | BYPASS  | 6     | I   | 0        | 1: bypasses data synchronization circuitry. Data is sampled using the DAC clock (CLK±) |  |

|      | SYNCEXT | 5     | 1   | 0        | 1: enables sync external mode; disable auto quadrant select.                           |  |

|      | SYNCIN  | [4:3] | I   | 00       | 2-bit input value is used to specify the sync quadrant.                                |  |

<sup>&</sup>lt;sup>1</sup> SWRESET also resets itself. SMEM contents are unaffected by SWRESET; however, CALMEM reports an uncalibrated state.

<sup>&</sup>lt;sup>2</sup> EXTREF is optional because the internal reference circuit is designed to be overdriven by an external source.

<sup>3</sup> The self-calibration clock is also used for the memory transfer cycle; therefore, the CALCLK value affects the MEMXFER process time.

<sup>4</sup> Register Bits 3:0 must all be 0 to assert SELFCAL. The time required for the self-calibration cycle is ~100 ms at 100 MHz with CALCLK = 0.

<sup>5</sup> Register Bits 3:0 must all be 0 to assert MEMXFER. The time required for the memory transfer cycle is ~15 ms at 100 MHz with CALCLK = 0.

<sup>6</sup> The UNCAL bit remains asserted after the cycle completes (SMEM contents held at default values) until the bit is cleared by the user.

### THEORY OF OPERATION

The AD9726 uses LVDS for input data to enable high sample rates and high performance. LVDS technology uses differential signals for noise rejection and small signal amplitude for fast speed with lower power. Each LVDS input on the AD9726 has an internal 100  $\Omega$  active load for proper termination.

### DAC CLOCK AND DATA CLOCK OUTPUT

The AD9726 uses two clock inputs and offers one clock output. All are differential signals.

The AD9726 is driven by a master input clock that initiates conversion and controls all on-chip activity. This signal is referred to as the DAC clock. It is not LVDS, and the CLK+ and CLK-pins are high impedance inputs.

The DAC clock is then used to generate the data clock output. The DCLK\_OUT+ and DCLK\_OUT- pins form an LVDS signal that can be used to drive an external FPGA or another data pump. In SDR mode, the data clock output always runs at the same frequency as the DAC clock. In DDR mode, the data clock output always runs at ½ the DAC clock frequency.

Use of the data clock output is optional. It is meant to serve as a convenient means of regulating the incoming data stream. The driver can be loaded by a 100  $\Omega$  differential termination. An external 1  $k\Omega$  resistor from the REXT pin to DBGND is also required to set the drive strength. If unused, the data clock output pins can be left unconnected, and the 1  $k\Omega$  resistor at REXT can be omitted.

The data clock output can also be inverted by asserting the INVDCLKO bit in SPI Register 0x02, or the driver can be disabled by asserting the DISDCLKO bit in the same register.

### **DATA CLOCK INPUT**

The remaining clock signal associated with the AD9726 is the data clock input. This LVDS signal is not optional and must accompany the 16-bit data bus. The data clock input is used to latch incoming data into the synchronization (sync) logic.

The data clock input always runs at the same frequency as the data clock output in both SDR and DDR modes. A logical inversion can be accomplished by asserting the INVDCLKI bit.

### **Driving the DAC Clock Inputs**

The DAC clock must be precise and spectrally pure to ensure the highest ac performance. A symmetrical 50% duty cycle should be maintained at all times.

The CLK+ and CLK- input pins should be driven by a signal with a common-mode voltage near ½ of CLKVDD. From this point, peak-to-peak signal amplitude should swing over a range of at least several hundred millivolts.

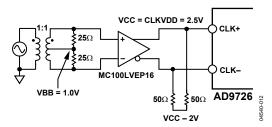

Figure 19. Active DAC Clock Drive Circuit

The circuit option shown in Figure 19 uses a receiver/driver IC from the 2.5 V LVPECL logic family to provide complementary outputs that fall within these guidelines. A transformer helps ensure a 50% duty cycle and provides a single-ended to differential conversion at the input.

The LVPECL device can be conveniently powered from the same power supply as CLKVDD. The center tap of the transformer secondary must be held at 1 V, the switching threshold of the receiver/driver inputs (use a resistive divider to generate this voltage or use the internal VBB source with a buffer amplifier). Based on a 1:1 impedance ratio, 25  $\Omega$  resistors across the secondary provide a matched load to a 50  $\Omega$  source.

The driver outputs are terminated as close as possible to the AD9726 with 50  $\Omega$  to VCC – 2 V (or use a Thevenin equivalent circuit). Controlled impedance PCB traces should be used to minimize reflections. Signal levels at the CLK+ and CLK– pins transition between a high near 1500 mV to a low near 750 mV.

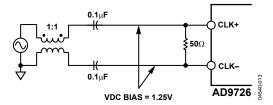

Figure 20. Passive DAC Clock Drive Circuit

An alternative circuit option for driving the DAC clock inputs employs a transmission line transformer (balun) to accomplish the single-ended to differential conversion. This all-passive circuit is considerably simpler and less costly, and it provides acceptable performance over a limited range of frequencies.

In this implementation, a sine wave (or other single-ended source) is coupled directly to the differential DAC clock inputs through a 50  $\Omega$  transformer. Capacitors are used for isolation, and each DAC clock pin must be dc-biased to a level of 1.25 V (a pair of simple resistive dividers can be used).

The 50  $\Omega$  termination resistor should be placed as close as possible to the input pins, and controlled impedance PCB traces should be used.

Good ac performance can be expected from either the active or passive DAC clock drive circuit. However, in a passive circuit, the output slew rate is dependent on the frequency of the input; whereas an active circuit provides consistently high output slew rates over a wide range of input frequencies.

#### **DATA SYNCHRONIZATION CIRCUITRY**

The high performance of the AD9726 requires maintaining synchronization between the incoming bits and the DAC clock used to sample and convert the data. Despite the inherent difficulty in specifying the phase relationship of the DAC clock and the LVDS data clock input and the challenge presented by the high operating speed of the interface, the AD9726 contains real-time logic to automatically monitor and align the data bus with the DAC clock.

Whether in SDR or DDR mode, input data is always provided at the same rate. Furthermore, the rate of incoming data always equals the frequency period of the DAC clock. The data rate and the DAC clock must also be frequency locked. To accomplish this, the primary purpose of the data clock output is to provide a time base for data that is derived directly from the DAC clock.

The function of the data clock input is to latch incoming data into the sync block. From there, it is the function of the synchronization logic to position the data with respect to the DAC clock for optimal ac performance.

Individual data bits must maintain close alignment with one another so that PCB traces have matched delays across the width of the 16-bit bus. In addition, a fixed setup and hold timing relationship between the data clock input and the data bus is required.

However, because of the sync logic, the phase relationship between the data bus and the DAC clock is internally optimized. Furthermore, if the phase between the data bus and the DAC clock drifts over time or temperature, the sync logic automatically updates and adjusts for it. After synchronization is reached, the phase between the data bus and the DAC clock can vary by a full cycle without loss or corruption of data.

More detailed explanations of sync operation and optional programmable modes are presented in the Sync Logic Operation and Programming section, which also includes an explanation of how to use the sync logic without the SPI.

### **Data Synchronization Circuitry Bypass**

Due to internal design limitations, the data synchronization circuitry does not assure a fixed or predictable pipeline delay between the data input and the analog output after power-up. For designs where multichip synchronization or fixed pipeline delay is important, the AD9726 can be configured to bypass the resynchronization circuitry and assure a fixed pipeline delay of four DAC clock cycles. In this mode, the data is sampled into

the DAC using the DAC clock (CLK±) and following the timing presented in Figure 4, Figure 5, and Table 4.

The data synchronization circuitry bypass is enabled by writing 0x40 to Address 0x16. The AD9726 should also be configured in single data rate mode by writing 0x80 to Address 0x02. In this mode, the sync logic is bypassed, making its configurations and status reporting irrelevant.

### **ANALOG OUTPUT**

The AD9726 is based around a high dynamic range CMOS core. The analog output consists of differential current sources, each capable of up to 20 mA full scale. Discrete output devices are PMOS and capable of sourcing current into an output termination within a compliance voltage range of  $\pm 1$  V.

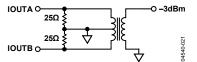

In a typical application, both outputs drive discrete resistors-toanalog ground. From there, especially for higher frequency outputs, they feed the center-tap secondary of a 1:1 RF transformer. A differential-to-single-ended conversion is accomplished that provides added gain and cancellation of even ordered harmonics.

Figure 21. Transformer Output Circuit

For maximum output power, resistor values can be increased to 50  $\Omega$  to provide up to 0 dBm into a 50  $\Omega$  load without loss of performance for most transformers.

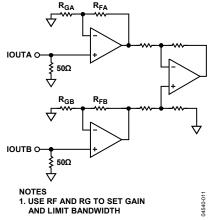

Figure 22. Op Amp Output Circuit

As an alternative, an active output stage can be used in the classic instrumentation amplifier configuration. Here, each DAC output feeds the noninverting input of one of the Analog Devices, Inc., high speed transimpedance op amps.

### INTERNAL REFERENCE AND FULL-SCALE OUTPUT

The AD9726 contains an internal 1.2 V precision reference source; this reference voltage appears at the REFIO pin. It can be used to drive external circuitry if properly buffered.

Apply an external reference voltage source to the REFIO pin if desired. The internal source is designed to be easily overdriven by an external source; however, the internal reference can also be powered down using the EXTREF bit in SPI Register 0x00.

The reference voltage (either internal or external) is applied to an external precision resistor at the FSADJ pin. The resulting current is internally amplified to provide the full-scale current at the DAC output according to the following equation:

$$I_{\rm OUTFS} = VREF/R_{\rm FSADJ} \times 32$$

Taking into account the binary value appearing at the data bus inputs, the output currents I<sub>OUTA</sub> and I<sub>OUTB</sub> can be determined according to the following equations:

```

IOUTA = I_{OUTFS} \times DB[15:0]/65536

IOUTB = I_{OUTFS} \times (1 - DB[15:0])/65536

```

Note that the AD9726 features nonvolatile, factory-calibrated gain using the internal reference source and a precision 2 k $\Omega$  load. Gain accuracy in any application is, therefore, dependent upon the accuracy of  $R_{\text{FSADJ}}$ .

### **RESET**

Following initial power-up and application of a valid DAC clock signal, the AD9726 should always be initialized with an active high pulse on the RESET pin. This defaults the programmable registers, initializes volatile calibration memory, and prepares the synchronization logic for data. The data bus should be static prior to the reset pulse. After reset, LVDS data can flow.

The default state of the AD9726 is DDR and twos complement binary input data. To use the AD9726 in this mode, it is not necessary to program any device registers. However, the SPI is enabled by default unless the SPI\_DIS pin is connected high. If not disabled, SPI input pins should not be left floating.

### **SERIAL PORT INTERFACE**

The serial port interface is a flexible and synchronous serial communications port allowing easy interface to many industry standard microcontroller and microprocessor protocols (including both Motorola SPI\* and Intel\* SSR). The interface provides read/write access to registers that configure the operation of the AD9726.

The AD9726 SPI supports single-byte and multibyte transfers as well as MSB- or LSB-justified data formats. The interface can be configured in 3-wire mode (in which SDIO is bidirectional) or the default 4-wire mode (in which SDIO and SDO function as unidirectional data input and data output, respectively).

### **Communication Cycle**

All communication cycles have two phases. The first phase is concerned with writing an instruction byte into the SPI controller and always coincides with the first eight rising edges of SCLK. The instruction byte provides the controller with information regarding the second phase of the cycle, namely the data transfer phase. The instruction byte contains the number of data bytes to be transferred (one to four), a register address, and a bit initiating a read or write operation.

Figure 23. SPI Communication Cycle

Any communication cycle begins with CSB going low, which also resets the SPI control logic. Similarly, any communication cycle ends with CSB going high, which aborts any incomplete data transfer. After a communication cycle begins, the next eight SCLK rising edges interpret data on the SDIO pin as the instruction byte.

### **Instruction Byte**

The instruction byte bits are shown in the following bit map.

| B7  | В6 | B5 | B4 | В3 | B2 | B1 | B0 |

|-----|----|----|----|----|----|----|----|

| R/W | N1 | N0 | A4 | А3 | A2 | A1 | A0 |

### $R/\overline{W}$

Bit 7 of the instruction byte selects a read or write transfer. If the bit is set high, a read operation is indicated. If the bit is low, a write operation is indicated.

### N1, N0

Bit 6 and Bit 5 of the instruction byte determine the number of data bytes to be transferred, as shown in Table 10.

Table 10.

| N1 | N0 | Description               |  |

|----|----|---------------------------|--|

| 0  | 0  | Transfer one data byte    |  |

| 0  | 1  | Transfer two data bytes   |  |

| 1  | 0  | Transfer three data bytes |  |

| 1  | 1  | Transfer four data bytes  |  |

### A4, A3, A2, A1, A0

Bit 4 through Bit 0 of the instruction byte specify a 5-bit binary value corresponding to a valid register address. In the case of multibyte transfers, the location specified is either an initial or a concluding register address. The SPI controller increments or decrements this value to generate successive address values depending on whether LSB or MSB justification is active.

#### MSB/LSB Transfers

The SPI can support both MSB- and LSB-justified serial data byte formats. This functionality is determined by Bit 6 in SPI Register 0x00. This bit defaults low, which is MSB justification. In this mode, serial data bits are written to and/or read from registers sequentially from Bit 7 to Bit 0.

If Bit 6 of SPI Register 0x00 is set high, the controller switches to LSB justification. In this mode, data bits are written to or read from registers sequentially from Bit 0 to Bit 7. Writing to the instruction bytes is also affected by the active justification.

For multibyte transfers with MSB justification, the address in the instruction byte is interpreted as a final address, and its value is decremented automatically by the controller. For multibyte transfers with LSB justification, the address in the instruction byte is interpreted as an initial address, and its value is incremented automatically by the controller.

Care must be exercised when switching from MSB to LSB justification. The controller switches modes immediately once all eight bits of SPI Register 0x00 are written (even if in the process of a multibyte transfer). For this reason, a single byte command is recommended when changing justification.

### 3-Wire and 4-Wire Operation

Bit 7 of SPI Register 0x00 defaults low, enabling 4-wire SPI operation. In this mode, serial data is input from the SDIO pin, and serial data is output on the SDO pin. Setting Bit 7 of SPI Register 0x00 high enables 3-wire operation. In this mode, SDIO becomes bidirectional and switches automatically from input to output when necessary. The SDO pin in this mode is unused and assumes a high impedance state.

As with MSB or LSB justification, care must be exercised when switching operational modes. The change occurs immediately once all eight bits of SPI Register 0x00 are written.

### **Writing and Reading Register Data**

Bringing CSB low initiates a new communication cycle. The next eight rising edges of SCLK latch data from SDIO into the instruction byte. If Bit 7 of the instruction byte is low, a write operation is enabled. If Bit 7 is high, a read operation is enabled.

For a write operation, a data byte is latched from the SDIO pin into a register on the next eight rising edges of SCLK. If the instruction byte Bit 6 and Bit 5 are not both 0, a multibyte transfer latches data bytes into adjacent registers after each successive set of eight rising SCLK edges. Depending upon MSB or LSB justification, the controller decrements or increments the address value in the instruction byte during the cycle as necessary.