## **IF Digitizing Subsystem**

AD9870

#### **FEATURES**

10 MHz-300 MHz Input Frequency

Baseband (I/Q) Digital Output

10 kHz-150 kHz Output Signal Bandwidth

12 dB SSB NF

> -1 dBm IIP3 (High IIP3 Mode)

25 dB Continuous AGC Range + 16 dB Gain Step

Support for LO and Sampling Clock Synthesis

Programmable Decimation Rate, Output Format, AAF

Cutoff, AGC and Synthesizer Settings

360 Ω Input Impedance

2.7 V-3.6 V Supply Voltage

Low Current: 42 mA Typ (High IIP3 Mode),

30 mA Typ (Low IIP3, Fixed Gain Mode)

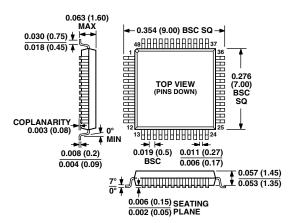

48-Lead LQFP Package (1.4 mm Thick)

APPLICATIONS

Portable and Mobile Radio Products

Digital UHF/VHF FDMA Products

TETRA

### PRODUCT DESCRIPTION

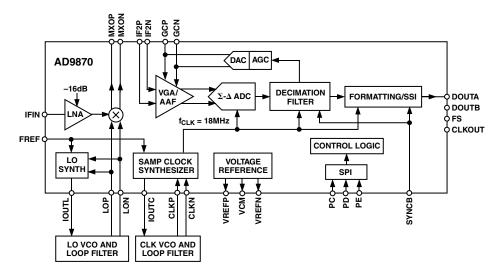

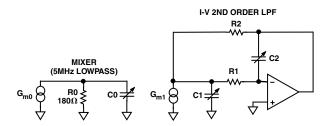

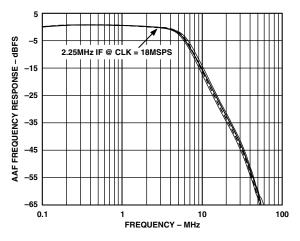

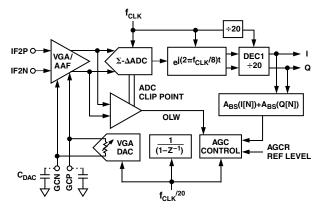

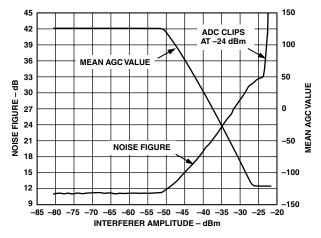

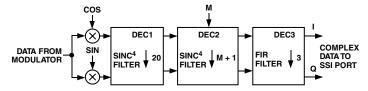

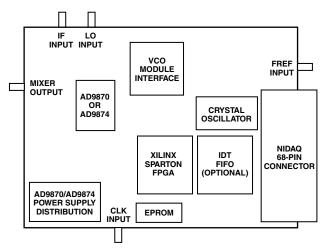

The AD9870 is a general-purpose IF subsystem that digitizes a low-level 10 MHz–300 MHz IF input with a bandwidth of up to 150 kHz. The signal chain of the AD9870 consists of a low-noise amplifier, a mixer, a variable gain amplifier with integral antialias filter, a bandpass sigma-delta analog-to-digital converter, and a decimation filter with programmable decimation factor. An automatic gain control (AGC) circuit provides the AD9870 with 25 dB of continuous gain adjustment. The high dynamic range of the bandpass sigma-delta converter allows the AD9870 to cope with blocking signals that are as much as 70 dB stronger than the desired signal. Auxiliary blocks include clock and LO synthesizers as well as a serial peripheral interface (SPI) port.

The SPI port programs numerous parameters of the AD9870, including the synthesizer divide ratios, the AGC attack and decay times, the AGC target signal level, the decimation factor, the output data format, the 16 dB attenuator, and the bias currents of several blocks. Reducing bias currents allows the user to reduce power consumption at the expense of reduced performance.

### **FUNCTIONAL BLOCK DIAGRAM**

# $\textbf{AD9870-SPECIFICATIONS} \begin{subarray}{l} (VDDI = VDDF = VDDA = 3.3 \ V, \ VDDC = VDDL = 3.3 \ V, \ VDDD = VDDH = 3.3 \ V, \ VDDQ = VDDH = 3.3 \ V, \ VDDQ = VDDH = 3.3 \ V, \ VDDQ = VDDP = 5.0 \ V, \ CLK = 18 \ MSPS, \ F_{IF} = 73.35 \ MHz, \ F_{L0} = 71.1 \ MHz, \ unless \ otherwise \ noted.) \\ \end{subarray}$

| Parameter                                                                                                                                                                                                                                            | Conditions <sup>1</sup>                                                                                                                                      | Min                       | Тур                                       | Max                                  | Unit                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-------------------------------------------|--------------------------------------|------------------------------------------------------|

| OVERALL                                                                                                                                                                                                                                              |                                                                                                                                                              |                           |                                           |                                      |                                                      |

| Analog Supply Voltage<br>(VDDA, VDDF, VDDI)                                                                                                                                                                                                          |                                                                                                                                                              | 2.7                       | 3.0                                       | 3.6                                  | V                                                    |

| Digital Supply Voltage (VDDD, VDDC, VDDL)                                                                                                                                                                                                            |                                                                                                                                                              | 2.7                       | 3.0                                       | 3.6                                  | V                                                    |

| Interface Supply Voltage (VDDH)                                                                                                                                                                                                                      |                                                                                                                                                              | 1.8                       |                                           | 3.6                                  | V                                                    |

| Charge Pump Supply Voltage<br>(VDDP, VDDQ)                                                                                                                                                                                                           |                                                                                                                                                              | 2.7                       | 3.0                                       | 5.5                                  | V                                                    |

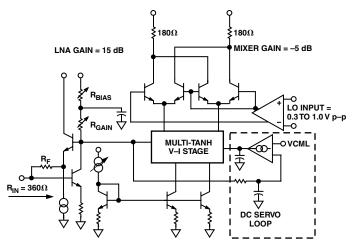

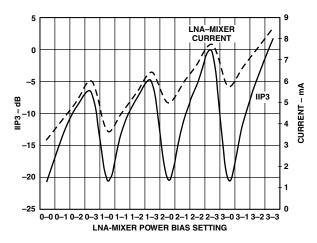

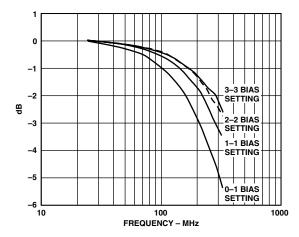

| Total Current SSB Noise Figure @ Max VGA Gain Input Third-Order Intercept (IIP3) Input Impedance Gain Variation Over Temperature                                                                                                                     | High IIP3 Setting High IIP3 Setting Low IIP3 Setting High IIP3 Setting Low IIP3 Setting Low IIP3 Setting                                                     | -5                        | 42<br>12<br>12<br>-1<br>-10<br>360<br>0.6 | 50.6                                 | mA<br>dB<br>dB<br>dBm<br>dBm<br>dBm<br>Ω<br>dB       |

| PREAMP + MIXER Maximum Input and LO Frequencies                                                                                                                                                                                                      |                                                                                                                                                              |                           | 300                                       |                                      | MHz                                                  |

| LO SYNTHESIZER LO Input Frequency LO Input Amplitude FREF (Reference) Frequency FREF Input Amplitude Minimum Charge Pump Output Current Maximum Charge Pump Output Current Charge Pump Output Compliance Voltage <sup>2</sup> Synthesizer Resolution | Programmable in 0.625 mA Steps<br>Programmable in 0.625 mA Steps                                                                                             | 7.75<br>0.3<br>0.1<br>0.3 | 0.625<br>5.000                            | 300<br>1.0<br>25<br>3<br>VDDP - 0.25 | MHz<br>V p-p<br>MHz<br>V p-p<br>mA<br>mA<br>V<br>kHz |

| CLOCK SYNTHESIZER CLK Input Frequency CLK Input Amplitude Minimum Charge Pump Output Current Maximum Charge Pump Output Current Charge Pump Output Compliance Voltage <sup>2</sup> Synthesizer Resolution                                            | Clock VCO Off<br>Programmable in 0.625 mA Steps<br>Programmable in 0.625 mA Steps                                                                            | 13<br>0.3<br>0.25<br>2.2  | 0.625<br>5.000                            | 18<br>VDDQ – 0.25                    | MHz<br>V p-p<br>mA<br>mA<br>V<br>kHz                 |

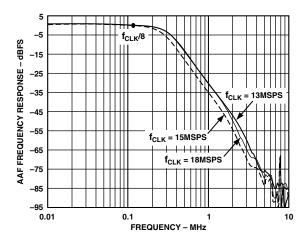

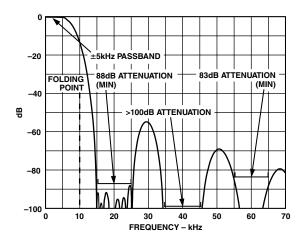

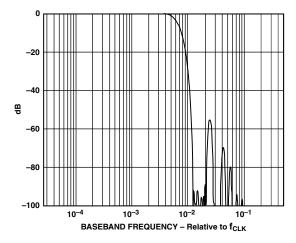

| SIGMA-DELTA ADC Resolution Clock Frequency (f <sub>CLK</sub> ) Center Frequency Dynamic Range Passband Gain Variation                                                                                                                                | BW = 10 kHz                                                                                                                                                  | 13                        | 16<br>f <sub>CLK</sub> /8<br>88           | 18                                   | Bits<br>MHz<br>MHz<br>dB<br>dB                       |

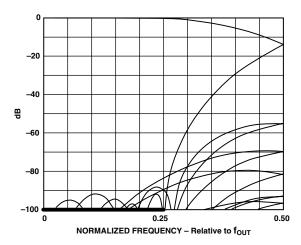

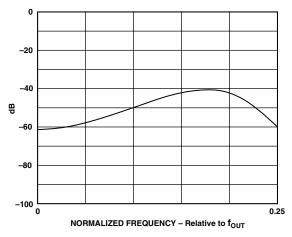

| DECIMATOR Decimation Factor Passband Width Passband Gain Variation Alias Attenuation                                                                                                                                                                 | Programmable in Steps of 60                                                                                                                                  | 60<br>85                  | 50                                        | 960<br>1                             | %<br>dB<br>dB                                        |

| GAIN CONTROL Programmable Gain Step AGC Gain Range (Continuous) AGC Attack Time                                                                                                                                                                      | Programmable                                                                                                                                                 | 18<br>40                  | 16<br>25                                  | 60<br>7000                           | dB<br>dB<br>μs                                       |

| SPI PC Clock Frequency PD Hold Time                                                                                                                                                                                                                  |                                                                                                                                                              | 10                        |                                           | 10                                   | MHz<br>ns                                            |

| SSI CLKOUT Frequency Output Rise/Fall Time                                                                                                                                                                                                           | CMOS Output Mode, Drive Strength = 0<br>CMOS Output Mode, Drive Strength = 1<br>CMOS Output Mode, Drive Strength = 2<br>CMOS Output Mode, Drive Strength = 3 | 1                         |                                           | 18<br>120<br>45<br>16<br>10          | MHz<br>ns<br>ns<br>ns                                |

| OPERATING TEMPERATURE RANGE Basic Functions Meets All Specifications                                                                                                                                                                                 |                                                                                                                                                              | -40<br>-40                |                                           | +95<br>+85                           | °C<br>°C                                             |

$<sup>^{1}</sup>$ Standard operating mode: high IIP3 setting, synthesizers in normal (not fast acquire) mode,  $f_{CLK}$  = 18 MHz, 25 pF load on SSI output pins: VDDx = 3.0 V.  $^{2}$ Voltage span in which LO (or CLK) charge pump output current is maintained within 5% of nominal value of VDDP/2 (or VDDQ/2).

Specifications subject to change without notice.

### **ABSOLUTE MAXIMUM RATINGS\***

| Parameter                                                    | With Respect to                                              | Min  | Max        | Unit |

|--------------------------------------------------------------|--------------------------------------------------------------|------|------------|------|

| VDDF, VDDA, VDDC, VDDD, VDDH, VDDL, VDDI                     | GNDF, GNDA, GNDC, GNDD, GNDH<br>GNDL, GNDI, GNDS             | -0.3 | +4.0       | V    |

| VDDF, VDDA, VDDC, VDDD, VDDH, VDDL, VDDI                     | VDDR, VDDA, VDDC, VDDD, VDDH, VDDL, VDDI                     | -4.0 | +4.0       | V    |

| VDDP, VDDQ                                                   | GNDP, GNDQ                                                   | -0.3 | +6.0       | V    |

| GNDF, GNDA, GNDC, GNDD, GNDH<br>GNDL, GNDI, GNDQ, GNDP, GNDS | GNDF, GNDA, GNDC, GNDD, GNDH<br>GNDL, GNDI, GNDQ, GNDP, GNDS | -0.3 | +0.3       | V    |

| MXOP, MXON, LOP, LON, IFIN, CXIF, CXVL, CXVM                 | GNDI                                                         | -0.3 | VDDI + 0.3 | V    |

| PC, PD, PE, CLKOUT, DOUTA, DOUTB, FS, SYNCB                  | GNDH                                                         | -0.3 | VDDH + 0.3 | V    |

| IF2N, IF2P, GCP, GCN                                         | GNDF                                                         | -0.3 | VDDF + 0.3 | V    |

| VREFP, VREFN, VCM                                            | GNDA                                                         | -0.3 | VDDA + 0.3 | V    |

| IOUTC                                                        | GNDQ                                                         | -0.3 | VDDQ + 0.3 | V    |

| IOUTL                                                        | GNDP                                                         | -0.3 | VDDP + 0.3 | V    |

| CLKP, CLKN                                                   | GNDC                                                         | -0.3 | VDDC + 0.3 | V    |

| FREF                                                         | GNDL                                                         | -0.3 | VDDL + 0.3 | V    |

| Junction Temperature                                         |                                                              |      | 150        | °C   |

| Storage Temperature                                          |                                                              | -65  | +150       | °C   |

| Lead Temperature (10 sec)                                    |                                                              |      | 300        | °C   |

<sup>\*</sup>Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

### THERMAL CHARACTERISTICS

#### Thermal Resistance

48-Lead LQFP

$\theta_{JA} = 91^{\circ}C/W$

$\theta_{\rm IC} = 28^{\circ} \text{C/W}$

### **ORDERING GUIDE**

| Model              | Temperature Range | Package Description                                           | Package Option |

|--------------------|-------------------|---------------------------------------------------------------|----------------|

| AD9870<br>AD9870EB | −40°C to +85°C    | 48-Lead Thin Plastic Quad Flatpack (LQFP)<br>Evaluation Board | ST-48          |

### CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD9870 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

REV. 0 -3-

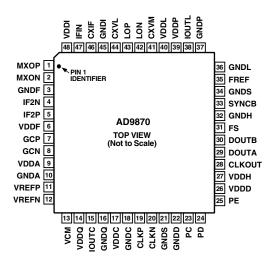

### PIN CONFIGURATION

### PIN FUNCTION DESCRIPTIONS

| Pin | Mnemonic | Description                                     | Pin | Mnemonic | Description                                          |

|-----|----------|-------------------------------------------------|-----|----------|------------------------------------------------------|

| 1   | MXOP     | Mixer Output, Positive                          | 25  | PE       | Enable Input for SPI Port                            |

| 2   | MXON     | Mixer Output, Negative                          | 26  | VDDD     | Positive Power Supply for Internal Digital Functions |

| 3   | GNDF     | Ground for VGA                                  | 27  | VDDH     | Positive Power Supply for Digital Interface          |

| 4   | IF2N     | Second IF Input (to VGA), Negative              | 28  | CLKOUT   | Clock Output for SSI Port                            |

| 5   | IF2P     | Second IF Input (to VGA), Positive              | 29  | DOUTA    | Data Output for SSI Port                             |

| 6   | VDDF     | Positive Power Supply for Antialias Filter/VGA  | 30  | DOUTB    | Data Output for SSI Port, Unused                     |

| 7   | GCP      | Filter Capacitor for VGA Gain Control, Positive | 31  | FS       | Frame Sync for SSI Port                              |

| 8   | GCN      | Filter Capacitor for VGA Gain Control, Negative | 32  | GNDH     | Ground for Digital Interface                         |

| 9   | VDDA     | Positive Power Supply for ADC                   | 33  | SYNCB    | Resets the SSI and Decimator Counters                |

| 10  | GNDA     | Ground for ADC                                  | 34  | GNDS     | Substrate Ground                                     |

| 11  | VREFP    | Voltage Reference, Positive                     | 35  | FREF     | Reference Frequency Input for Both Synthesizers      |

| 12  | VREFN    | Voltage Reference, Negative                     | 36  | GNDL     | Ground for LO Synthesizer                            |

| 13  | VCM      | Common-Mode Voltage (Requires 20 kΩ to GNDA)    | 37  | GNDP     | Ground for LO Synthesizer Charge Pump                |

| 14  | VDDQ     | Pos. Power Supply for Clock Synth. Charge Pump  | 38  | IOUTL    | LO Synthesizer Charge Pump Output Current            |

| 15  | IOUTC    | Clock Synthesizer Charge Pump Output Current    | 39  | VDDP     | Positive Power Supply for LO Synth. Charge Pump      |

| 16  | GNDQ     | Ground for Clock Synthesizer Charge Pump        | 40  | VDDL     | Positive Power Supply for LO Synthesizer             |

| 17  | VDDC     | Positive Power Supply for Clock Synthesizer     | 41  | CXVM     | External Capacitor for Mixer Bias                    |

| 18  | GNDC     | Ground for Clock Synthesizer                    | 42  | LON      | LO Input to Mixer and LO Synthesizer, Negative       |

| 19  | CLKP     | Sampling Clock Input/Clock VCO Tank, Positive   | 43  | LOP      | LO Input to Mixer and LO Synthesizer, Positive       |

| 20  | CLKN     | Sampling Clock Input/Clock VCO Tank, Negative   | 44  | CXVL     | External Capacitor for Preamp Power Supply           |

| 21  | GNDS     | Substrate Ground                                | 45  | GNDI     | Ground for Mixer and Preamp                          |

| 22  | GNDD     | Ground for Digital Functions                    | 46  | CXIF     | External Capacitor for Preamp Bias                   |

| 23  | PC       | Clock Input for SPI Port                        | 47  | IFIN     | First IF Input (to Preamp)                           |

| 24  | PD       | Data I/O for SPI Port                           | 48  | VDDI     | Positive Power Supply for Mixer and Preamp           |

-4- REV. 0

### **SERIAL PERIPHERAL INTERFACE (SPI)**

The Serial Peripheral Interface (SPI) is a bidirectional serial port. It is used to load configuration information into the registers listed below as well as to read back their contents. Table I provides a list of the registers that may be programmed through the SPI port. Addresses and default values are given in hexadecimal form.

Table I. SPI Address Map

| STBY   Standby Control Bits (REF, LO, CKO, CK, GC, LNAMX, VGA, ADC).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Address<br>(Hex) |                | Width | Default Value | Name         | Description                                                                                                                              |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------|-------|---------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0x01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | POWER            | CONTROL REGIS  | STERS |               |              |                                                                                                                                          |  |

| (5.4)   2   0   MIXB   Mixer Bias Current (0 = 1 m.A.) = 2 m.A. 2 = 3 m.A. 3 = 4 m.A.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0x00             | (7:0)          | 8     | 0xFF          | STBY         | Standby Control Bits (REF, LO, CKO, CK, GC, LNAMX, VGA, ADC).                                                                            |  |

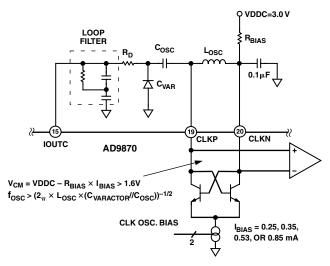

| AGC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0x01             | (5:4)<br>(3:2) | 2 2   | 0 0           | MIXB<br>CKOB | Mixer Bias Current (0 = 1 mA, 1 = 2 mA, 2 = 3 mA, 3 = 4 mA).<br>CK Oscillator Bias (0 = 0.25 mA, 1 = 0.35 mA, 2 = 0.53 mA, 3 = 0.85 mA). |  |

| No.   No.  | 0x02             | (7:0)          | 8     | 0x00          | TEST         | Factory Test Mode.                                                                                                                       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | AGC              |                |       |               |              |                                                                                                                                          |  |

| Default corresponds to maximum gain.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0x03             | ' '            |       |               |              |                                                                                                                                          |  |

| Company   Comp | 0x04             | (7:0)          | 8     | 0xFF          | AGCG(7:0)    | ,                                                                                                                                        |  |

| Circle   C | 0x05             | · ′            |       |               |              |                                                                                                                                          |  |

| Description    | 0x06             | (3:0)          | 4     | 0             | AGCD         |                                                                                                                                          |  |

| LO SYNTHESIZER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | DECIMA           | ATION FACTOR   | •     |               | •            |                                                                                                                                          |  |

| 0x08         (5:0)         6         0x00         LOR(13:8)         Reference Frequency Divisor (6 MSBs of a 14-Bit Word).           0x09         (7:0)         8         0x38         LOR(7:0)         Reference Frequency Divisor (8 LSBs of a 14-Bit Word).           0x0A         (7:5)         3         0x5         LOA         "A" Counter (Prescaler Control Counter).           (4:0)         5         0x00         LOB(12:8)         "B" Counter MSBs (5 MSBs of a 13-Bit Word).           0x0B         (7:0)         8         0x1D         LOB(7:0)         "B" Counter LSBs (8 LSBs of a 13-Bit Word).           0x0C         (6)         1         0         LOF         Enable Fast Acquire.           (5)         1         0         LOINV         Invert Charge Pump (0 = Pump_Up ⇒ IOUTL Sources Current).           (4:2)         3         0         LOI         Charge Pump Current in Normal Operation. Invume = (LOI + 1) × 0.625 mA.           (1:0)         2         0         LOTM         Manual Control of LO Charge Pump (3 = Off, 2 = Down, 1 = Up, 0 = Normal)           0x0D         (3:0)         4         0x0         LOFA(7:0)         LO Fast Acquire Time Unit (4 MSBs of a 14-Bit Word).           0x0E         (7:0)         8         0x04         LOFA(7:0)         LO Fast Acquire Time Unit (8 LSBs of a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0x07             | (3:0)          | 4     | 4             | M            | Decimation Factor = $60 \times (M + 1)$ . Default is decimate-by-300.                                                                    |  |

| 0x09         (7:0)         8         0x38         LOR(7:0)         Reference Frequency Divisor (8 LSBs of a 14-Bit Word). Default (56) Yields 300 kHz from f <sub>REF</sub> = 16.8 MHz.           0x0A         (7:5)         3         0x5         LOA         "A" Counter (Prescaler Control Counter). (4:0)         5         0x00         LOB(12:8)         "B" Counter MSBs (5 MSBs of a 13-Bit Word). (5 mod kHz from 73.35 MHz-2.25 MHz.           0x0B         (7:0)         8         0x1D         LOB(7:0)         "B" Counter LSBs (8 LSBs of a 13-Bit Word).           0x0C         (6)         1         0         LOF         Enable Fast Acquire. (5)           (5)         1         0         LOINV         Invert Charge Pump (0 = Pump_Up ⇒ IOUTL Sources Current). (64:2)           (4:2)         3         0         LOI         Charge Pump Current in Normal Operation. IpUMP = (LOI + 1) × 0.625 mA. (1:0)           (1:0)         2         0         LOTM         Manual Control of LO Charge Pump (3 = Off, 2 = Down, 1 = Up, 0 = Normal)           0x0D         (3:0)         4         0x0         LOFA(13:8)         LO Fast Acquire Time Unit (4 MSBs of a 14-Bit Word).           0x1D         (5:0)         6         00         CKR(7:0)         Reference Frequency Divisor (6 MSBs of a 14-Bit Word).           0x11         (7:0)         8         0x38 <td< td=""><td>LO SYN</td><td>THESIZER</td><td></td><td></td><td></td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | LO SYN           | THESIZER       |       |               |              |                                                                                                                                          |  |

| Default (56) Yields 300 kHz from f <sub>REF</sub> = 16.8 MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0x08             | (5:0)          | 6     | 0x00          | LOR(13:8)    | Reference Frequency Divisor (6 MSBs of a 14-Bit Word).                                                                                   |  |

| (4:0)         5         0x00         LOB(12:8)         "B" Counter MSBs (5 MSBs of a 13-Bit Word). Default LOA and LOB Values Yield 300 kHz from 73.35 MHz-2.25 MHz.           0x0B         (7:0)         8         0x1D         LOB(7:0)         "B" Counter LSBs (8 LSBs of a 13-Bit Word).           0x0C         (6)         1         0         LOF         Enable Fast Acquire.           (5)         1         0         LOINV         Invert Charge Pump (0 = Pump_Up ⇒ IOUTL Sources Current).           (4:2)         3         0         LOI         Charge Pump Current in Normal Operation. I <sub>PUMP</sub> = (LOI + 1) × 0.625 mA.           (1:0)         2         0         LOTM         Manual Control of LO Charge Pump (3 = Off, 2 = Down, 1 = Up, 0 = Normal)           0x0D         (3:0)         4         0x0         LOFA(13:8)         LO Fast Acquire Time Unit (4 MSBs of a 14-Bit Word).           0x0E         (7:0)         8         0x04         LOFA(7:0)         LO Fast Acquire Time Unit (8 LSBs of a 14-Bit Word).           0x10         (5:0)         6         00         CKR(13:8)         Reference Frequency Divisor (6 MSBs of a 14-Bit Word).           0x11         (7:0)         8         0x38         CKR(7:0)         Reference Frequency Divisor (8 LSBs of a 14-Bit Word).           0x11         (7:0)         8         0x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0x09             | (7:0)          | 8     | 0x38          | LOR(7:0)     |                                                                                                                                          |  |

| $0x0C \qquad (6) \qquad 1 \qquad 0 \qquad LOF \qquad Enable Fast Acquire. \\ (5) \qquad 1 \qquad 0 \qquad LOINV \qquad Invert Charge Pump (0 = Pump\_Up \Rightarrow IOUTL Sources Current). \\ (4:2) \qquad 3 \qquad 0 \qquad LOI \qquad Charge Pump Current in Normal Operation. I_{PUMP} = (LOI + 1) × 0.625 mA. \\ (1:0) \qquad 2 \qquad 0 \qquad LOTM \qquad Manual Control of LO Charge Pump (3 = Off, 2 = Down, 1 = Up, 0 = Normal) \\ 0x0D \qquad (3:0) \qquad 4 \qquad 0x0 \qquad LOFA(13:8) \qquad LO Fast Acquire Time Unit (4 MSBs of a 14-Bit Word). \\ 0x0E \qquad (7:0) \qquad 8 \qquad 0x04 \qquad LOFA(7:0) \qquad LO Fast Acquire Time Unit (8 LSBs of a 14-Bit Word). \\ CLOCK SYNTHESIZER \\ 0x10 \qquad (5:0) \qquad 6 \qquad 00 \qquad CKR(13:8) \qquad Reference Frequency Divisor (6 MSBs of a 14-Bit Word). \\ 0x11 \qquad (7:0) \qquad 8 \qquad 0x38 \qquad CKR(7:0) \qquad Reference Frequency Divisor (8 LSBs of a 14-Bit Word). \\ Default Yields 300 kHz from f_{REF} = 16.8 MHz. \\ Min = 3, Max = 16383. \\ \\$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0x0A             | ` ′            |       |               |              | "B" Counter MSBs (5 MSBs of a 13-Bit Word).                                                                                              |  |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0x0B             | (7:0)          | 8     | 0x1D          | LOB(7:0)     | "B" Counter LSBs (8 LSBs of a 13-Bit Word).                                                                                              |  |

| 0x0E         (7:0)         8         0x04         LOFA(7:0)         LO Fast Acquire Time Unit (8 LSBs of a 14-Bit Word).           CLOCK SYNTHESIZER         0x10         (5:0)         6         00         CKR(13:8)         Reference Frequency Divisor (6 MSBs of a 14-Bit Word).           0x11         (7:0)         8         0x38         CKR(7:0)         Reference Frequency Divisor (8 LSBs of a 14-Bit Word).           Default Yields 300 kHz from f <sub>REF</sub> = 16.8 MHz.         Min = 3, Max = 16383.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0x0C             | (5)<br>(4:2)   | 1 3   | 0 0           | LOINV<br>LOI |                                                                                                                                          |  |

| CLOCK SYNTHESIZER           0x10         (5:0)         6         00         CKR(13:8)         Reference Frequency Divisor (6 MSBs of a 14-Bit Word).           0x11         (7:0)         8         0x38         CKR(7:0)         Reference Frequency Divisor (8 LSBs of a 14-Bit Word).           Default Yields 300 kHz from f <sub>REF</sub> = 16.8 MHz.         Min = 3, Max = 16383.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0x0D             | (3:0)          | 4     | 0x0           | LOFA(13:8)   | LO Fast Acquire Time Unit (4 MSBs of a 14-Bit Word).                                                                                     |  |

| 0x10         (5:0)         6         00         CKR(13:8)         Reference Frequency Divisor (6 MSBs of a 14-Bit Word).           0x11         (7:0)         8         0x38         CKR(7:0)         Reference Frequency Divisor (8 LSBs of a 14-Bit Word).           Default Yields 300 kHz from f <sub>REF</sub> = 16.8 MHz.         Min = 3, Max = 16383.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0x0E             | (7:0)          | 8     | 0x04          | LOFA(7:0)    | LO Fast Acquire Time Unit (8 LSBs of a 14-Bit Word).                                                                                     |  |

| 0x11 (7:0) 8 0x38 CKR(7:0) Reference Frequency Divisor (8 LSBs of a 14-Bit Word). Default Yields 300 kHz from f <sub>REF</sub> =16.8 MHz. Min = 3, Max = 16383.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | CLOCK            | SYNTHESIZER    |       |               |              |                                                                                                                                          |  |

| Default Yields 300 kHz from $f_{REF}$ =16.8 MHz.<br>Min = 3, Max = 16383.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0x10             | (5:0)          | 6     | 00            | CKR(13:8)    | Reference Frequency Divisor (6 MSBs of a 14-Bit Word).                                                                                   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0x11             | (7:0)          | 8     | 0x38          | CKR(7:0)     | Default Yields 300 kHz from f <sub>REF</sub> =16.8 MHz.                                                                                  |  |

| 0x12 (4:0) 5 0x00 CKN(12:8) Synthesized Frequency Divisor (5 MSBs of a 13-Bit Word).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0x12             | (4:0)          | 5     | 0x00          | CKN(12:8)    | Synthesized Frequency Divisor (5 MSBs of a 13-Bit Word).                                                                                 |  |

REV. 0 -5-

| Address<br>(Hex) | Bit<br>Breakdown             | Width            | Default Value    | Name                        | Description                                                                                                                                                                                                                                              |  |

|------------------|------------------------------|------------------|------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CLOCK            | SYNTHESIZEI                  | R (Continued)    | 1                |                             |                                                                                                                                                                                                                                                          |  |

| 0x13             | (7:0)                        | 8                | 0x3C             | CKN(7:0)                    | Synthesized Frequency Divisor (8 LSBs of a 13-Bit Word). Default Yields 300 kHz from $f_{\rm CLK}$ = 18 MHz. Min = 3, Max = 8191.                                                                                                                        |  |

| 0x14             | (6)<br>(5)<br>(4:2)<br>(1:0) | 1<br>1<br>3<br>2 | 0<br>0<br>0<br>0 | CKF<br>CKINV<br>CKI<br>CKTM | Enable Fast Acquire. Invert Charge Pump (0 = Pump_Up $\Rightarrow$ IOUTC Sources Current). Charge Pump Current in Normal Operation. I <sub>PUMP</sub> = (CKI + 1) × 0.625 mA. Manual Control of CLK Charge Pump (0 = Off, 1 = Down, 2 = Up, 3 = Normal). |  |

| 0x15             | (3:0)                        | 4                | 0x0              | CKFA(13:8)                  | CK Fast Acquire Time Unit (4 MSBs of a 14-Bit Word).                                                                                                                                                                                                     |  |

| 0x16             | (7:0)                        | 8                | 0x04             | CKFA(7:0)                   | CK Fast Acquire Time Unit (8 LSBs of a 14-Bit Word).                                                                                                                                                                                                     |  |

| SSI CON          | TROL                         |                  |                  |                             |                                                                                                                                                                                                                                                          |  |

| 0x18             | (7:0)                        | 8                | 0x12             | SSICRA                      | SSI Control Register A. See Table III. (Default is FS and CLKOUT Three-Stated.)                                                                                                                                                                          |  |

| 0x19             | (1:0)                        | 2                | 0x0              | SSICRB                      | SSI Control Register B. See Table III.                                                                                                                                                                                                                   |  |

| 0x1A             | (3:0)                        | 4                | 1                | SSIORD                      | Output Rate Divisor. $f_{CLKOUT} = f_{CLK}/SSIORD$ .                                                                                                                                                                                                     |  |

| AAF CA           | PACITOR SET                  | TING/CALIB       | RATION           |                             |                                                                                                                                                                                                                                                          |  |

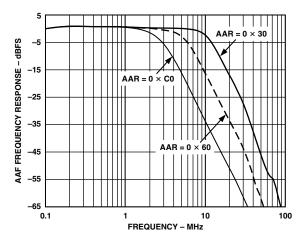

| 0x1C             | (7:0)                        | 8                | 0x00             | AAR                         | Antialias Response Selector. 0x60 Is Recommended.                                                                                                                                                                                                        |  |

| 0x1D             | 5<br>(4:0)                   | 1<br>5           | 0<br>0x0         | ERRN<br>CAPN                | Error Flag. AAF N-Well Capacitor Setting.                                                                                                                                                                                                                |  |

| 0x1E             | 5<br>(4:0)                   | 1<br>15          | 0<br>0x0         | ERRP<br>CAPP                | Error Flag. AAF Poly-Poly Capacitor Setting.                                                                                                                                                                                                             |  |

| TEST RI          | EGISTERS ANI                 | D SPI PORT I     | READ ENABLE      |                             |                                                                                                                                                                                                                                                          |  |

| 0x38             | (7:0)                        | 8                | 0x00             | TEST                        | Factory Test Mode.                                                                                                                                                                                                                                       |  |

| 0x39             | 0                            | 1                | 0                | TEST                        | Factory Test Mode.                                                                                                                                                                                                                                       |  |

| 0x3A             | (7:4, 2:0)<br>(3)            | 7<br>1           | 0x0<br>0         | TEST<br>SPIREN              | Factory Test Mode.<br>Enable Read from SPI Port.                                                                                                                                                                                                         |  |

| 0x3B-<br>0x3F    | (7:0)                        | 1                | 0x00             | TEST                        | Factory Test Mode.                                                                                                                                                                                                                                       |  |

-6- REV. 0

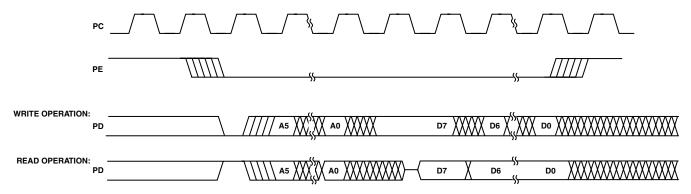

Figure 1. SPI Timing

Figure 1 illustrates the timing for the SPI port. After the peripheral enable (PE) signal goes low, data (PD) is read on the rising edges of the clock (PC). The first bit is a read/not-write indicator; the next six bits are address bits; the eighth bit is ignored; the last eight bits are data. Address and data are given MSB first. If the read/not-write indicator is a zero, a write operation occurs and the data bits are shifted in. If the read/not-write indicator is a one and if the read-back enable bit (Reg. 3A, Bit 3) has been set, a read operation occurs and data is shifted out the data pin on the falling edges of the clock. PE stays low during the operation and goes high at the end of the transfer. If PE rises before an additional eight clock cycles have passed, the operation is aborted.

If PE stays low for an additional eight clock cycles, the destination address is incremented and another eight bits of data are shifted in. Again, should PE rise early, the current byte is ignored. By using this implicit addressing mode, the entire chip can be configured with a single write operation. Registers identified as being subject to frequent updates, namely those associated with power control and AGC operation, have been assigned adjacent addresses to minimize the time required to update them. The autoincrement mode is not supported for read operations.

Multibyte registers are "big-endian" (the most significant byte has the lower address) and are updated when a write to the least significant byte occurs.

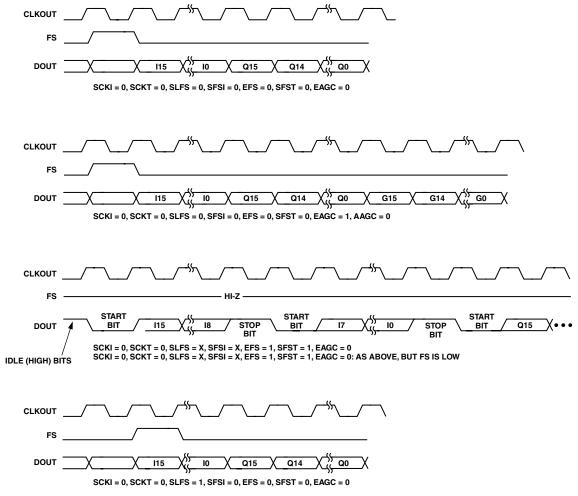

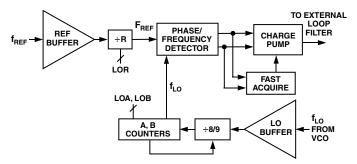

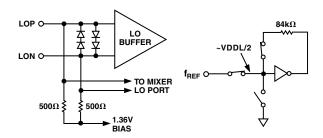

### SYNCHRONOUS SERIAL INTERFACE (SSI)

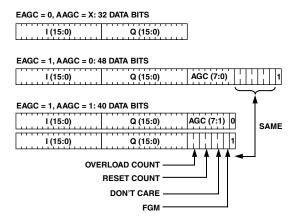

The primary output of the AD9870 is the converted signal, which is available from the SSI port as a serial bit stream. The bit stream consists of a 16-bit I word followed by a 16-bit Q word, where each word is given MSB first and is in two's-complement form. AGC, signal strength, and synchronization information may also be embedded in the data stream. The output bit rate ( $f_{CLKOUT}$ ) is equal to the modulator clock frequency ( $f_{CLK}$ ) divided by the contents of the SSIORD register. Users must verify that the output bit rate is sufficient to accommodate the required number of bits per frame (see Table II) and that the chosen output rate does not introduce harmful spurs. Idle (high) bits are used to fill out each frame; the frame lengths listed in Table II assume that with embedded frame sync (EFS = 1), at least 10 idle bits are desired.

Table II. Max Legal SSIORD Values for 16-Bit I/O Data and Decimation by 60 n

| Bits per Sampl         | e      |

|------------------------|--------|

| (Min No. of Bits per l | Frame) |