# ADC121C021/ADC121C027 I<sup>2</sup>C-Compatible, 12-Bit Analog-to-Digital Converter (ADC) with Alert Function

# **General Description**

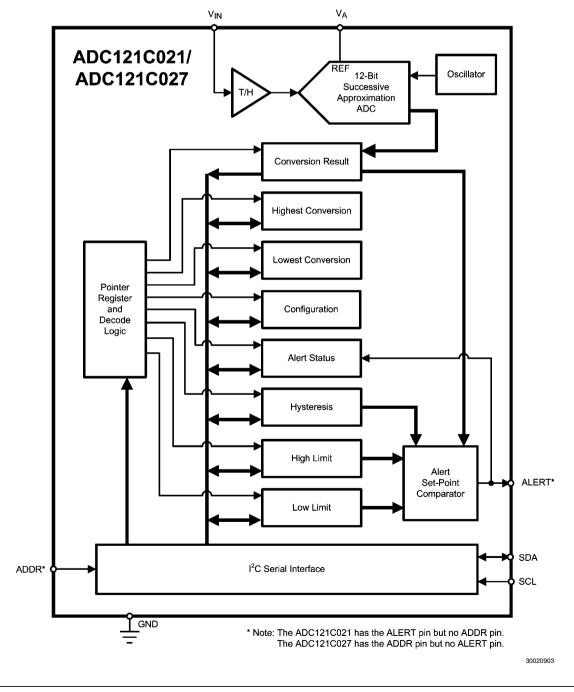

The ADC121C021 is a low-power, monolithic, 12-bit, analog-to-digital converter(ADC) that operates from a +2.7 to 5.5V supply. The converter is based on a successive approximation register architecture with an internal track-and-hold circuit that can handle input frequencies up to 11MHz. The ADC121C021 operates from a single supply which also serves as the reference. The device features an I<sup>2</sup>C-compatible serial interface that operates in all three speed modes, including high speed mode (3.4MHz).

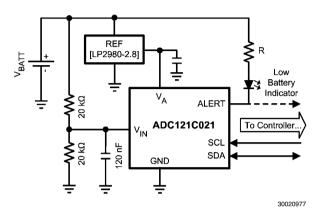

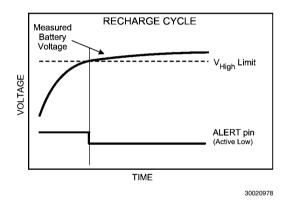

The ADC's Alert feature provides an interrupt that is activated when the analog input violates a programmable upper or lower limit value. The device features an automatic conversion mode, which frees up the controller and I<sup>2</sup>C interface. In this mode, the ADC continuously monitors the analog input for an "out-of-range" condition and provides an interrupt if the measured voltage goes out-of-range.

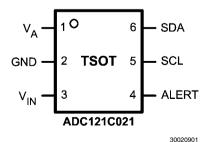

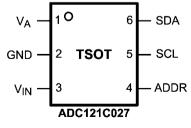

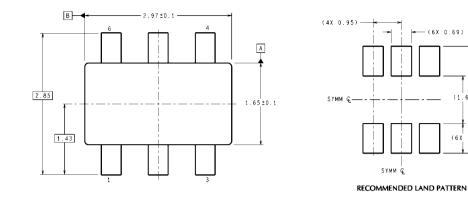

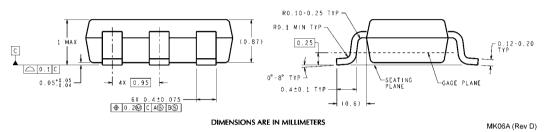

The ADC121C021 comes in a small TSOT-6 package with an alert output. The ADC121C027 comes in a small TSOT-6 package with an address selection input. The ADC121C027 provides three pin-selectable addresses. Pin-compatible alternatives are available with additional address options.

Normal power consumption using a +3V or +5V supply is 0.26mW or 0.78mW, respectively. The automatic power-down feature reduces the power consumption to less than  $1\mu W$  while not converting. Operation over the industrial temperature range of -40°C to +105°C is guaranteed. Their low power consumption and small packages make this family of ADCs an excellent choice for use in battery operated equipment

The ADC121C021 and ADC121C027 are part of a family of pin-compatible ADCs that also provide 8 and 10 bit resolution. For 8-bit ADCs see the ADC081C021 and ADC081C027. For 10-bit ADCs see the ADC101C021 and ADC101C027.

#### **Features**

- I<sup>2</sup>C-Compatible 2-wire Interface which supports standard (100kHz), fast (400kHz), and high speed (3.4MHz) modes

- Extended power supply range (+2.7V to +5.5V)

- Up to four pin-selectable chip addresses

- Out-of-range Alert Function

- Automatic Power-down mode while not converting

- Very small 6-pin TSOT packages

- ±8kV HBM ESD protection (SDA, SCL)

# **Key Specifications**

■ Resolution 12 bits; no missing codes

■ Conversion Time 12 bits; no missing codes

■ INL & DNL ±1 LSB (max) (up to 22kSPS)

■ Throughput Rate 188.9kSPS (max)

■ Power Consumption (at 22kSPS)

# **Applications**

- System Monitoring

- Peak Detection

- Portable Instruments

- Medical Instruments

- Test Equipment

# **Pin-Compatible Alternatives**

All devices are fully pin and function compatible.

| Resolution | ALERT Output               | ADDR Input |

|------------|----------------------------|------------|

| 12-bit     | 12-bit <b>ADC121C021 A</b> |            |

| 10-bit     | ADC101C021                 | ADC101C027 |

| 8-bit      | ADC081C021                 | ADC081C027 |

# **Connection Diagrams**

30020902

I2C® is a registered trademark of Phillips Corporation.

# **Ordering Information**

| Order Code                                                                                                                   | Option      | Package              | Top Mark |

|------------------------------------------------------------------------------------------------------------------------------|-------------|----------------------|----------|

| ADC121C021CIMK                                                                                                               | Alert pin   | TSOT-6               | X30C     |

| ADC121C021CIMKX                                                                                                              | Alert pin   | TSOT-6 Tape-and-Reel | X30C     |

| ADC121C027CIMK                                                                                                               | Address pin | TSOT-6               | X31C     |

| ADC121C027CIMKX                                                                                                              | Address pin | TSOT-6 Tape-and-Reel | X31C     |

| ADC121C027CINIX Address pin  Shipped with the ADC121C021  Also compatible with the ADC121C027 option.  Please order samples. |             | Evaluation Board     |          |

# **Block Diagram**

# **Pin Descriptions**

| Symbol          | Туре                           | Equivalent Circuit            | Description                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------|--------------------------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>A</sub>  | Supply                         | 1                             | Power and unbufferred reference voltage. V <sub>A</sub> must be free of noise and decoupled to GND.                                                                                                                                                                                                                                                                               |

| GND             | Ground                         |                               | Ground for all on-chip circuitry.                                                                                                                                                                                                                                                                                                                                                 |

| V <sub>IN</sub> | Analog Input                   | See Figure 4                  | Analog input. This signal can range from GND to V <sub>A</sub> .                                                                                                                                                                                                                                                                                                                  |

| ALERT           | Digital Output                 |                               | Alert output. Can be configured as active high or active low. This is an open drain data line that must be pulled to the supply $(V_A)$ with an external pull-up resistor.                                                                                                                                                                                                        |

| SCL             | Digital Input                  | PIN D1 Back                   | Serial Clock Input. SCL is used together with SDA to control the transfer of data in and out of the device. This is an open drain data line that must be pulled to the supply (V <sub>A</sub> ) with an external pull-up resistor. This pin's extended ESD tolerance( 8kV HBM) allows extension of the I <sup>2</sup> C bus across multiple boards without extra ESD protection.  |

| SDA             | Digital<br>Input/Output        | ☐ GND                         | Serial Data bi-directional connection. Data is clocked into or out of the internal 16-bit register with SCL. This is an open drain data line that must be pulled to the supply (V <sub>A</sub> ) with an external pull-up resistor. This pin's extended ESD tolerance( 8kV HBM) allows extension of the I <sup>2</sup> C bus across multiple boards without extra ESD protection. |

| ADDR            | Digital Input,<br>three levels | PIN D1 2.1k 41.5k 41.5k 41.5k | Tri-level Address Selection Input. Sets Bits A0 & A1 of the 7-bit slave address. (see <i>Table 1</i> )                                                                                                                                                                                                                                                                            |

# **Package Pinouts**

|                             | V <sub>A</sub> | GND | V <sub>IN</sub> | ALERT | SCL | SDA | ADDR |

|-----------------------------|----------------|-----|-----------------|-------|-----|-----|------|

| ADC121C021<br>TSOT-6        | 1              | 2   | 3               | 4     | 5   | 6   | N/A  |

| <b>ADC121C027</b><br>TSOT-6 | 1              | 2   | 3               | N/A   | 5   | 6   | 4    |

# **Absolute Maximum Ratings**

(Notes 1, 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Supply Voltage, V<sub>△</sub> -0.3V to +6.5V

Voltage on any Analog Input Pin to

**GND** -0.3V to  $(V_A + 0.3V)$

Voltage on any Digital Input Pin to

**GND**

-0.3V to 6.5V Input Current at Any Pin (Note 3) ±15 mA Package Input Current (Note 3) ±20 mA Power Dissipation at  $T_A = 25^{\circ}C$

ESD Susceptibility (Note 5)

VA, GND, VIN, ALERT,

ADDR pins:

Human Body Model 2500V Machine Model 250V Charged Device Model (CDM) 1250V

SDA, SCL pins:

Human Body Model 8000V Machine Model 400V

Junction Temperature +150°C Storage Temperature -65°C to +150°C

# Operating Ratings (Notes 1, 2)

Operating Temperature Range  $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +105^{\circ}\text{C}$ Supply Voltage, VA +2.7V to 5.5V Analog Input Voltage, VIN OV to VA Digital Input Voltage (Note 7) 0V to 5.5V Sample Rate up to 188.9 kSPS

**Package Thermal Resistances**

| Package     | $\theta_{JA}$ |  |

|-------------|---------------|--|

| 6-Lead TSOT | 250°C/W       |  |

Soldering process must comply with National Semiconductor's Reflow Temperature Profile specifications. Refer to www.national.com/packaging. (Note 6)

# **Electrical Characteristics**

The following specifications apply for  $V_A = +2.7V$  to +5.5V, GND = 0V,  $f_{SCL}$  up to 3.4MHz,  $f_{IN} = 1kHz$  for  $f_{SCL}$  up to 400kHz,  $f_{IN} = 10$ kHz for  $f_{SCL} = 3.4$ MHz unless otherwise noted. **Boldface limits apply for T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>**: all other limits T<sub>A</sub> = 25°C unless otherwise noted.

See (Note 4)

| Symbol           | Parameter                             | Conditions                                                          | Typical<br>(Note 9) | Limits<br>(Note 9) | Units (Limits |

|------------------|---------------------------------------|---------------------------------------------------------------------|---------------------|--------------------|---------------|

| STATIC CO        | ONVERTER CHARACTERISTICS              |                                                                     |                     |                    | •             |

|                  | Resolution with No Missing Codes      |                                                                     |                     | 12                 | Bits          |

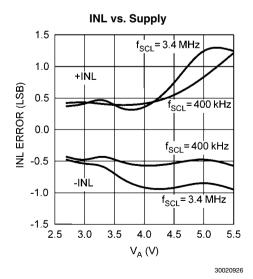

| INL              | Integral Non-Linearity (End Point     | $V_A = +2.7V$ to $+3.6V$<br>$f_{SCL}$ up to 400kHz (Note 13)        | ±0.5                | ±1                 | LSB (max)     |

| IINL             | Method)                               | V = 12.7V to 15.5V f up to 2.4MHz                                   | +1.2                |                    | LSB           |

|                  |                                       | $V_A = +2.7V \text{ to } +5.5V. f_{SCL} \text{ up to } 3.4MHz$      | -0.9                |                    | LSB           |

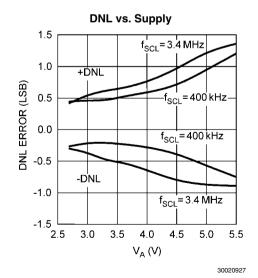

|                  |                                       | $V_A = +2.7V \text{ to } +3.6V$                                     | +0.5                | +1                 | LSB (max)     |

| DNI              | Differential New Linearity            | f <sub>SCL</sub> up to 400kHz (Note 13)                             | -0.5                | -0.9               | LSB (min)     |

| DNL              | Differential Non-Linearity            | $V_A = +2.7V \text{ to } +5.5V. f_{SCL} \text{ up to } 3.4MHz$      | +1.3                |                    | LSB           |

|                  |                                       |                                                                     | -0.9                |                    | LSB           |

| V <sub>OFF</sub> | Offset Error                          | $V_A = +2.7V \text{ to } +3.6V$<br>$f_{SCL}$ up to 400kHz (Note 13) | +0.1                | ±1.6               | LSB (max)     |

|                  |                                       | $V_A = +2.7V \text{ to } +5.5V. f_{SCL} \text{ up to } 3.4MHz$      | +1.4                |                    | LSB           |

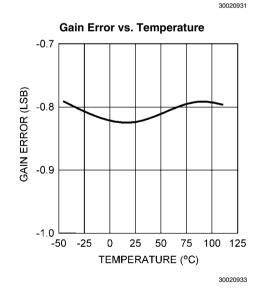

| GE               | Gain Error                            |                                                                     | -0.8                | ±6                 | LSB (max)     |

| DYNAMIC          | CONVERTER CHARACTERISTICS             |                                                                     |                     |                    |               |

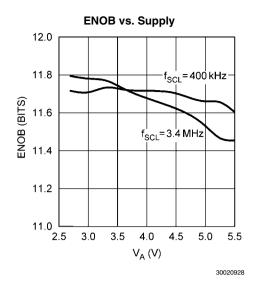

| ENOD             | Effective Nember of Dite              | $V_A = +2.7V \text{ to } +3.6V$                                     | 11.7                | 11.3               | Bits (min)    |

| ENOB             | Effective Number of Bits              | $V_A = +3.6V \text{ to } +5.5V$                                     | 11.5                |                    | Bits (min)    |

| 2                |                                       | $V_A = +2.7V \text{ to } +3.6V$                                     | 72.5                | 70.4               | dB (min)      |

| SNR              | Signal-to-Noise Ratio                 | $V_A = +3.6V \text{ to } +5.5V$                                     | 71                  |                    | dB (min)      |

|                  |                                       | $V_A = +2.7V \text{ to } +3.6V$                                     | -92                 | -78                | dB (max)      |

| THD              | Total Harmonic Distortion             | V <sub>A</sub> = +3.6V to +5.5V                                     | -87                 |                    | dB (max)      |

|                  |                                       | $V_A = +2.7V \text{ to } +3.6V$                                     | 72.6                | 70                 | dB (min)      |

| SINAD            | Signal-to-Noise Plus Distortion Ratio | $V_{\Delta} = +3.6V \text{ to } +5.5V$                              | 71                  |                    | dB (min)      |

| Symbol            | Parameter                                          | Conditions                                                               | Typical (Note 9)    | Limits<br>(Note 9)    | Units (Limits) |  |  |  |

|-------------------|----------------------------------------------------|--------------------------------------------------------------------------|---------------------|-----------------------|----------------|--|--|--|

| 0500              | Ozoniana Franco Domania Barras                     | $V_A = +2.7V \text{ to } +3.6V$                                          | 90                  | 76                    | dB (min)       |  |  |  |

| SFDR              | Spurious-Free Dynamic Range                        | V <sub>A</sub> = +3.6V to +5.5V                                          | 87                  |                       | dB (min)       |  |  |  |

| Int               | Intermodulation Distortion, Second                 | $V_A = +3.0V$ ,<br>$f_a = 1.035 \text{ kHz}$ , $f_b = 1.135 \text{ kHz}$ | -89                 |                       | dB             |  |  |  |

| IMD               | Order Terms (IMD <sub>2</sub> )                    | $V_A = +5.0V$ ,<br>$f_a = 1.035 \text{ kHz}$ , $f_b = 1.135 \text{ kHz}$ | -91                 |                       | dB             |  |  |  |

| IIVID             | Intermodulation Distortion, Third                  | $V_A = +3.0V$ ,<br>$f_a = 1.035 \text{ kHz}$ , $f_b = 1.135 \text{ kHz}$ | -88                 |                       | dB             |  |  |  |

|                   | Order Terms (IMD <sub>3</sub> )                    | $V_A = +5.0V$ ,<br>$f_a = 1.035 \text{ kHz}$ , $f_b = 1.135 \text{ kHz}$ | -88                 |                       | dB             |  |  |  |

| FPBW              | <br> Full Power Bandwidth (-3dB)                   | $V_A = +3.0V$                                                            | 8                   |                       | MHz            |  |  |  |

|                   | Full Fower Baridwidth (-3dB)                       | $V_A = +5.0V$                                                            | 11                  |                       | MHz            |  |  |  |

| ANALOG I          | ANALOG INPUT CHARACTERISTICS                       |                                                                          |                     |                       |                |  |  |  |

| $V_{IN}$          | Input Range                                        |                                                                          | 0 to V <sub>A</sub> |                       | V              |  |  |  |

| I <sub>DCL</sub>  | DC Leakage Current (Note 10)                       |                                                                          |                     | ±1                    | μA (max)       |  |  |  |

|                   | Input Capacitance                                  | Track Mode                                                               | 30                  |                       | pF             |  |  |  |

| C <sub>INA</sub>  | Imput Capacitance                                  | Hold Mode                                                                | 3                   |                       | pF             |  |  |  |

| SERIAL IN         | TERFACE INPUT CHARACTERISTIC                       | CS (SCL, SDA)                                                            |                     |                       |                |  |  |  |

| $V_{IH}$          | Input High Voltage                                 |                                                                          |                     | 0.7 x V <sub>A</sub>  | V (min)        |  |  |  |

| $V_{IL}$          | Input Low Voltage                                  |                                                                          |                     | 0.3 x V <sub>A</sub>  | V (max)        |  |  |  |

| I <sub>IN</sub>   | Input Current (Note 10)                            |                                                                          |                     | ±1                    | μA (max)       |  |  |  |

| C <sub>IN</sub>   | Input Pin Capacitance                              |                                                                          | 3                   |                       | pF             |  |  |  |

| V <sub>HYST</sub> | Input Hysteresis                                   |                                                                          |                     | 0.1 x V <sub>A</sub>  | V (min)        |  |  |  |

|                   | SELECTION INPUT CHARACTERIS                        | STICS (ADDR)                                                             | •                   |                       | •              |  |  |  |

| V <sub>IH</sub>   | Input High Voltage                                 |                                                                          |                     | V <sub>A</sub> - 0.5V | V (min)        |  |  |  |

| V <sub>IL</sub>   | Input Low Voltage                                  |                                                                          |                     | 0.5                   | V (max)        |  |  |  |

| I <sub>IN</sub>   | Input Current (Note 10)                            |                                                                          |                     | ±1                    | μA (max)       |  |  |  |

| LOGIC OU          | TPUT CHARACTERISTICS, OPEN-                        | PRAIN (SDA, ALERT)                                                       | •                   |                       |                |  |  |  |

|                   | 0                                                  | I <sub>SINK</sub> = 3 mA                                                 |                     | 0.4                   | V (max)        |  |  |  |

| $V_{OL}$          | Output Low Voltage                                 | I <sub>SINK</sub> = 6 mA                                                 |                     | 0.6                   | V (max)        |  |  |  |

| l <sub>oz</sub>   | High-Impedence Output<br>Leakage Current (Note 10) |                                                                          |                     | ±1                    | μA (max)       |  |  |  |

|                   | Output Coding                                      |                                                                          | Sti                 | aight (Natural        | ) Binary       |  |  |  |

| Symbol               | Parameter                                         | Conditions               |                                              | Typical<br>(Note 9)     | Limits<br>(Note 9) | Units (Limits) |

|----------------------|---------------------------------------------------|--------------------------|----------------------------------------------|-------------------------|--------------------|----------------|

| POWER R              | EQUIREMENTS                                       | •                        |                                              |                         |                    |                |

|                      | Supply Voltage Minimum                            |                          |                                              |                         | 2.7                | V (min)        |

| V <sub>A</sub>       | Supply Voltage Maximum                            |                          |                                              |                         | 5.5                | V (max)        |

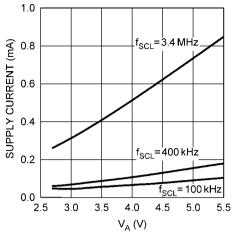

| Continuous           | Operation Mode 2-wire interface a                 | ctive.                   |                                              |                         |                    |                |

|                      |                                                   | f <sub>SCL</sub> =400kHz | $V_A = 2.7V \text{ to } 3.6V$                | 0.08                    | 0.14               | mA (max)       |

| ı                    | Supply Current                                    | ISCL - TOOKI IZ          | $V_A = 4.5V \text{ to } 5.5V$                | 0.16                    | 0.30               | mA (max)       |

| I <sub>N</sub>       | Зарру Сапен                                       | f <sub>SCI</sub> =3.4MHz | $V_A = 2.7V \text{ to } 3.6V$                | 0.37                    | 0.55               | mA (max)       |

|                      |                                                   | ISCL=3.4WI12             | $V_A = 4.5V \text{ to } 5.5V$                | 0.74                    | 0.99               | mA (max)       |

|                      |                                                   | f <sub>SCL</sub> =400kHz | V <sub>A</sub> = 3.0V                        | 0.26                    |                    | mW             |

| P. Dower Consumption | ISCL-400KHZ                                       | V <sub>A</sub> = 5.0V    | 0.78                                         |                         | mW                 |                |

| $P_N$                | Power Consumption                                 | f <sub>SCL</sub> =3.4MHz | V <sub>A</sub> = 3.0V                        | 1.22                    |                    | mW             |

|                      |                                                   |                          | V <sub>A</sub> = 5.0V                        | 3.67                    |                    | mW             |

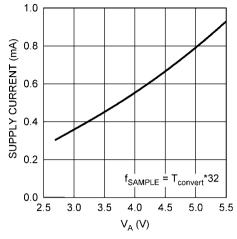

| Automatic            | Conversion Mode 2-wire interface st               | opped and quiet (SCL     | = SDA = V <sub>A</sub> ). f <sub>SAMPL</sub> | E = T <sub>CONVER</sub> | <sub>RT</sub> * 32 | •              |

|                      | Supply Current                                    |                          | $V_A = 2.7V \text{ to } 3.6V$                | 0.41                    | 0.59               | mA (max)       |

| I <sub>A</sub>       | Supply Current                                    |                          | $V_A = 4.5V \text{ to } 5.5V$                | 0.78                    | 1.2                | mA (max)       |

|                      | Barrar Cara arrantian                             |                          | V <sub>A</sub> = 3.0V                        | 1.35                    |                    | mW             |

| $P_A$                | Power Consumption                                 |                          | V <sub>A</sub> = 5.0V                        | 3.91                    |                    | mW             |

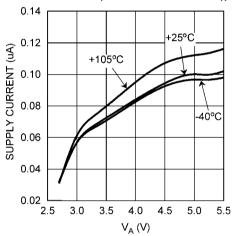

| Power Dov            | vn Mode (PD <sub>1</sub> ) 2-wire interface stop  | oed and quiet. (SCL = S  | $SDA = V_A$ ).(Note 10)                      | )                       |                    |                |

| I <sub>PD1</sub>     | Supply Current                                    |                          |                                              | 0.1                     | 0.2                | μA (max)       |

| P <sub>PD1</sub>     | Power Consumption                                 |                          |                                              | 0.5                     | 0.9                | μW (max)       |

| Power Dov            | vn Mode (PD <sub>2</sub> ) 2-wire interface activ | e. Master communicatii   | ng with a different d                        | evice on the            | bus.               | •              |

|                      |                                                   | f 4001-11-               | $V_A = 2.7V \text{ to } 3.6V$                | 13                      | 45                 | μA (max)       |

|                      |                                                   | f <sub>SCL</sub> =400kHz | $V_A = 4.5V \text{ to } 5.5V$                | 27                      | 80                 | μA (max)       |

| I <sub>PD2</sub>     | Supply Current                                    |                          | $V_A = 2.7V \text{ to } 3.6V$                | 89                      | 150                | μA (max)       |

|                      |                                                   | f <sub>SCL</sub> =3.4MHz | $V_A = 4.5V \text{ to } 5.5V$                | 168                     | 250                | μA (max)       |

|                      |                                                   | f 4001-11                | V <sub>A</sub> = 3.0V                        | 0.04                    |                    | mW             |

| Б                    |                                                   | f <sub>SCL</sub> =400kHz | V <sub>A</sub> = 5.0V                        | 0.14                    |                    | mW             |

| $P_{PD2}$            | Power Consumption                                 | ( 0 4NV)                 | V <sub>A</sub> = 3.0V                        | 0.29                    |                    | mW             |

|                      |                                                   | f <sub>SCL</sub> =3.4MHz | $V_A = 5.0V$                                 | 0.84                    |                    | mW             |

# A.C. and Timing Characteristics

The following specifications apply for  $V_A = +2.7V$  to +5.5V. **Boldface limits apply for T\_{MIN} \le T\_A \le T\_{MAX}** and all other limits are at  $T_A = 25^{\circ}\text{C}$ , unless otherwise specified.

| Symbol              | Parameter                                            | Conditions (Note 12)                                                                           | Typical<br>(Note 9) | Limits<br>(Notes 9,<br>12) | Units<br>(Limits)                                |

|---------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------|---------------------|----------------------------|--------------------------------------------------|

| CONVER              | SION RATE                                            |                                                                                                |                     | ,                          |                                                  |

|                     | Conversion Time                                      |                                                                                                | 1                   |                            | μs                                               |

|                     |                                                      | f <sub>SCL</sub> = 100kHz                                                                      | 5.56                |                            | kSPS                                             |

|                     |                                                      | f <sub>SCL</sub> = 400kHz                                                                      | 22.2                |                            | kSPS                                             |

| f <sub>CONV</sub>   | Conversion Rate                                      | f <sub>SCL</sub> = 1.7MHz                                                                      | 94.4                |                            | kSPS                                             |

|                     |                                                      | $f_{SCL} = 3.4MHz$                                                                             | 188.9               |                            | kSPS                                             |

| DIGITAL             | TIMING SPECS (SCL, SDA)                              | - 002                                                                                          | · ·                 |                            |                                                  |

| f <sub>SCL</sub>    | Serial Clock Frequency                               | Standard Mode<br>Fast Mode<br>High Speed Mode, $C_b = 100pF$<br>High Speed Mode, $C_b = 400pF$ |                     | 100<br>400<br>3.4<br>1.7   | kHz (max)<br>kHz (max)<br>MHz (max)<br>MHz (max) |

| t <sub>LOW</sub>    | SCL Low Time                                         | Standard Mode Fast Mode High Speed Mode, $C_b = 100pF$ High Speed Mode, $C_b = 400pF$          |                     | 4.7<br>1.3<br>160<br>320   | us (min) us (min) ns (min) ns (min)              |

| t <sub>HIGH</sub>   | SCL High Time                                        | Standard Mode<br>Fast Mode<br>High Speed Mode, $C_b = 100pF$<br>High Speed Mode, $C_b = 400pF$ |                     | 4.0<br>0.6<br>60<br>120    | us (min) us (min) ns (min) ns (min)              |

| t <sub>SU;DAT</sub> | Data Setup Time                                      | Standard Mode<br>Fast Mode<br>High Speed Mode                                                  |                     | 250<br>100<br>10           | ns (min)<br>ns (min)<br>ns (min)                 |

|                     |                                                      | Standard Mode (Note 14)                                                                        |                     | 0<br>3.45                  | us (min)<br>us (max)                             |

|                     | Data Hold Time                                       | Fast Mode (Note 14)                                                                            |                     | 0<br>0.9                   | us (min)<br>us (max)                             |

| t <sub>HD;DAT</sub> | Data Hold Time                                       | High Speed Mode, C <sub>b</sub> = 100pF                                                        |                     | 0<br>70                    | ns (min)<br>ns (max)                             |

|                     |                                                      | High Speed Mode, C <sub>b</sub> = 400pF                                                        |                     | 0<br>150                   | ns (min)<br>ns (max)                             |

| t <sub>SU;STA</sub> | Setup time for a start or a repeated start condition | Standard Mode<br>Fast Mode<br>High Speed Mode                                                  |                     | 4.7<br>0.6<br>160          | us (min)<br>us (min)<br>ns (min)                 |

| t <sub>HD;STA</sub> | Hold time for a start or a repeated start condition  | Standard Mode<br>Fast Mode<br>High Speed Mode                                                  |                     | 4.0<br>0.6<br>160          | us (min)<br>us (min)<br>ns (min)                 |

| t <sub>BUF</sub>    | Bus free time between a stop and start condition     | Standard Mode<br>Fast Mode                                                                     |                     | 4.7<br>1.3                 | us (min)<br>us (min)                             |

| t <sub>SU;STO</sub> | Setup time for a stop condition                      | Standard Mode<br>Fast Mode<br>High Speed Mode                                                  |                     | 4.0<br>0.6<br>160          | us (min)<br>us (min)<br>ns (min)                 |

| Symbol | Parameter                                       | Conditions (Note 12)                      | Typical<br>(Note 9) | Limits<br>(Notes 9,<br>12) | Units<br>(Limits) |

|--------|-------------------------------------------------|-------------------------------------------|---------------------|----------------------------|-------------------|

|        |                                                 | Standard Mode                             |                     | 1000                       | ns (max)          |

|        |                                                 | Foot Mode                                 |                     | 20+0.1C <sub>b</sub>       | ns (min)          |

|        |                                                 | Fast Mode                                 |                     | 300                        | ns (max)          |

| rDA    | Rise time of SDA signal                         | High Speed Mode, C <sub>b</sub> = 100pF   |                     | 10                         | ns (min)          |

|        |                                                 | Trigit opeca wode, o <sub>b</sub> = Toopi |                     | 80                         | ns (max)          |

|        |                                                 | High Speed Mode, C <sub>b</sub> = 400pF   |                     | 20                         | ns (min)          |

|        |                                                 | 3                                         |                     | 160                        | ns (max)          |

|        |                                                 | Standard Mode                             |                     | 250                        | ns (max)          |

|        |                                                 | Fast Mode                                 |                     | 20+0.1C <sub>b</sub>       | ns (min)          |

|        |                                                 | T dot Wood                                |                     | 250                        | ns (max)          |

| DA     | Fall time of SDA signal                         | High Speed Mode, C <sub>b</sub> = 100pF   |                     | 10                         | ns (min)          |

|        |                                                 | riigii opeda iiidas, o <sub>b</sub>       |                     | 80                         | ns (max)          |

|        |                                                 | High Speed Mode, C <sub>b</sub> = 400pF   |                     | 20                         | ns (min)          |

|        |                                                 | ·                                         |                     | 160                        | ns (max)          |

|        |                                                 | Standard Mode                             |                     | 1000                       | ns (max)          |

|        |                                                 | Fast Mode                                 |                     | 20+0.1C <sub>b</sub>       | ns (min)          |

|        |                                                 |                                           |                     | 300                        | ns (max)          |

| CL     | Rise time of SCL signal                         | High Speed Mode, C <sub>b</sub> = 100pF   |                     | 10                         | ns (min)          |

|        |                                                 |                                           |                     | 40                         | ns (max)          |

|        |                                                 | High Speed Mode, C <sub>b</sub> = 400pF   |                     | 20                         | ns (min)          |

|        |                                                 |                                           |                     | 80                         | ns (max)          |

|        |                                                 | Standard Mode                             |                     | 1000                       | ns (max)          |

|        |                                                 | Fast Mode                                 |                     | 20+0.1C <sub>b</sub>       | ns (min)          |

|        | Rise time of SCL signal after a                 |                                           |                     | 300                        | ns (max)          |

| rCL1   | repeated start condition and after an           | High Speed Mode, C <sub>b</sub> = 100pF   |                     | 10                         | ns (min)          |

|        | acknowledge bit.                                | 3                                         |                     | 80                         | ns (max)          |

|        |                                                 | High Speed Mode, C <sub>b</sub> = 400pF   |                     | 20                         | ns (min)          |

|        |                                                 | ·                                         |                     | 160                        | ns (max)          |

|        |                                                 | Standard Mode                             |                     | 300                        | ns (max)          |

|        |                                                 | Fast Mode                                 |                     | 20+0.1C <sub>b</sub>       | ns (min)          |

|        |                                                 |                                           |                     | 300                        | ns (max)          |

| CL     | Fall time of a SCL signal                       | High Speed Mode, C <sub>b</sub> = 100pF   |                     | 10                         | ns (min)          |

|        |                                                 | , , ,                                     |                     | 40                         | ns (max)          |

|        |                                                 | High Speed Mode, C <sub>b</sub> = 400pF   |                     | 20                         | ns (min)          |

|        |                                                 | , , , ,                                   |                     | 80                         | ns (max)          |

| 'b     | Capacitive load for each bus line (SCL and SDA) |                                           |                     | 400                        | pF (max)          |

| _      | Pulse Width of spike suppressed                 | Fast Mode                                 |                     | 50                         | ns (max)          |

| SP     | (Note 11)                                       | High Speed Mode                           |                     | 10                         | ns (max)          |

**Note 1:** Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions. Operation of the device beyond the maximum Operating Ratings is not recommended.

Note 2: All voltages are measured with respect to GND = 0V, unless otherwise specified.

**Note 3:** When the input voltage at any pin exceeds 5.5V or is less than GND, the current at that pin should be limited per the Absolute Maximum Ratings. The mximum package input current rating limits the number of pins that can safely exceed the power supplies.

Note 4: The absolute maximum junction temperature  $(T_J max)$  for this device is 150°C. The maximum allowable power dissipation is dictated by  $T_J max$ , the junction-to-ambient thermal resistance  $(\theta_{JA})$ , and the ambient temperature  $(T_A)$ , and can be calculated using the formula  $P_D MAX = (T_J max - T_A) / \theta_{JA}$ . The values for maximum power dissipation will be reached only when the device is operated in a severe fault condition (e.g., when input or output pins are driven beyond the operating ratings, or the power supply polarity is reversed).

Note 5: Human body model is a 100 pF capacitor discharged through a 1.5 k $\Omega$  resistor. Machine model is a 220 pF capacitor discharged through 0  $\Omega$ . Charged device model simulates a pin slowly acquiring charge (such as from a device sliding down the feeder in an automated assembler) then rapidly being discharged.

Note 6: Reflow temperature profiles are different for lead-free packages.

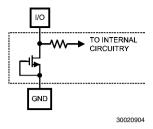

Note 7: The inputs are protected as shown below. Input voltage magnitudes up to 5.5V, regardless of V<sub>A</sub>, will not cause errors in the conversion result. For example, if V<sub>A</sub> is 3V, the digital input pins can be driven with a 5V logic device.

Note 8: To guarantee accuracy, it is required that V<sub>A</sub> be well bypassed and free of noise.

Note 9: Typical figures are at T<sub>J</sub> = 25°C, and represent most likely parametric norms. Test limits are guaranteed to National's AOQL (Average Outgoing Quality Level).

Note 10: This parameter is guaranteed by design and/or characterization and is not tested in production.

Note 11: Spike suppression filtering on SCL and SDA will supress spikes that are less than 50ns for standard and fast modes, and less than 10ns for hs-mode.

Note 12:  $C_b$  refers to the capacitance of one bus line.  $C_b$  is expressed in pF units.

Note 13: The ADC will meet Minimum/Maximum specifications for f<sub>SCL</sub> up to 3.4MHz and V<sub>A</sub> = 2.7V to 3.6V when operating in the Quiet Interface Mode (Section 1.11).

Note 14: The ADC121C021 will provide a minimum data hold time of 300ns to comply with the I2C Specification.

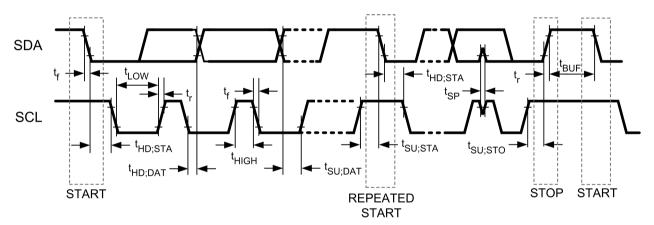

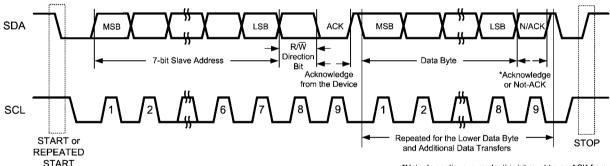

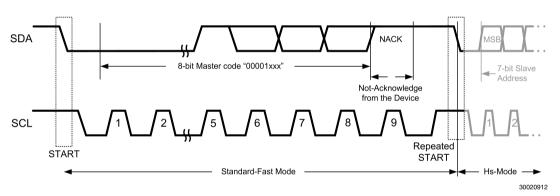

# **Timing Diagrams**

30020960

FIGURE 1. Serial Timing Diagram

9

# **Specification Definitions**

**ACQUISITION TIME** is the time required for the ADC to acquire the input voltage. During this time, the hold capacitor is charged by the input voltage.

**APERTURE DELAY** is the time between the start of a conversion and the time when the input signal is internally acquired or held for conversion.

**CONVERSION TIME** is the time required, after the input voltage is acquired, for the ADC to convert the input voltage to a digital word.

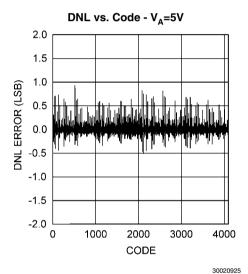

**DIFFERENTIAL NON-LINEARITY (DNL)** is the measure of the maximum deviation from the ideal step size of 1 LSB.

**EFFECTIVE NUMBER OF BITS (ENOB, or EFFECTIVE BITS)** is another method of specifying Signal-to-Noise and Distortion or SINAD. ENOB is defined as (SINAD - 1.76) / 6.02 and says that the converter is equivalent to a perfect ADC of this (ENOB) number of bits.

**FULL POWER BANDWIDTH** is a measure of the frequency at which the reconstructed output fundamental drops 3 dB below its low frequency value for a full scale input.

**GAIN ERROR** is the deviation of the last code transition (111...110) to (111...111) from the ideal  $(V_{REF} - 1.5 LSB)$ , after adjusting for offset error.

INTEGRAL NON-LINEARITY (INL) is a measure of the deviation of each individual code from a line drawn from negative full scale (½ LSB below the first code transition) through positive full scale (½ LSB above the last code transition). The deviation of any given code from this straight line is measured from the center of that code value.

**INTERMODULATION DISTORTION (IMD)** is the creation of additional spectral components as a result of two sinusoidal frequencies being applied to an individual ADC input at the same time. It is defined as the ratio of the power in either the second or the third order intermodulation products to the sum of the power in both of the original frequencies. Second order products are  $f_a \pm f_b$ , where  $f_a$  and  $f_b$  are the two sine wave input frequencies. Third order products are  $(2f_a \pm f_b)$  and  $(f_a \pm 2f_b)$ . IMD is usually expressed in dB.

**MISSING CODES** are those output codes that will never appear at the ADC output. The ADC121C021 is guaranteed not to have any missing codes.

**OFFSET ERROR** is the deviation of the first code transition (000...000) to (000...001) from the ideal (i.e. GND + 0.5 LSB).

**SIGNAL TO NOISE RATIO (SNR)** is the ratio, expressed in dB, of the rms value of the input signal to the rms value of the sum of all other spectral components below one-half the sampling frequency, not including harmonics or d.c.

SIGNAL TO NOISE PLUS DISTORTION (S/N+D or SINAD) Is the ratio, expressed in dB, of the rms value of the input signal to the rms value of all of the other spectral components below half the clock frequency, including harmonics but excluding d.c.

SPURIOUS FREE DYNAMIC RANGE (SFDR) is the difference, expressed in dB, between the desired signal amplitude to the amplitude of the peak spurious spectral component, where a spurious spectral component is any signal present in the output spectrum that is not present at the input and may or may not be a harmonic.

**TOTAL HARMONIC DISTORTION (THD)** is the ratio, expressed in dBc, of the rms total of the first n harmonic components at the output to the rms level of the input signal frequency as seen at the output. THD is calculated as

THD = 20 x

$$\log_{10} \sqrt{\frac{A_{f2}^2 + \dots + A_{Fn}^2}{A_{f1}^2}}$$

where  $A_{f1}$  is the RMS power of the input frequency at the output and  $A_{f2}$  through  $A_{fn}$  are the RMS power in the first n harmonic frequencies.

**THROUGHPUT TIME** is the minimum time required between the start of two successive conversions. It is the acquisition time plus the conversion time.

**LEAST SIGNIFICANT BIT (LSB)** is the bit that has the smallest value or weight of all bits in a word. This value is

$$LSB = V_{\Delta} / 2^{n}$$

where  $V_A$  is the supply voltage for this product, and "n" is the resolution in bits, which is 12 for the ADC121C021.

MOST SIGNIFICANT BIT (MSB) is the bit that has the largest value or weight of all bits in a word. Its value is 1/2 of  $\rm V_A$ .

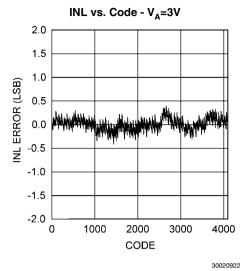

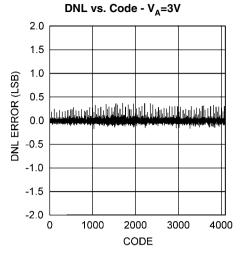

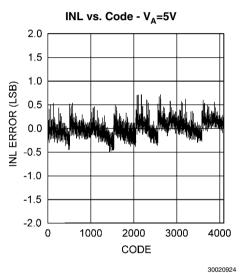

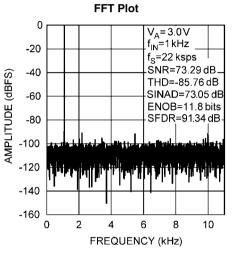

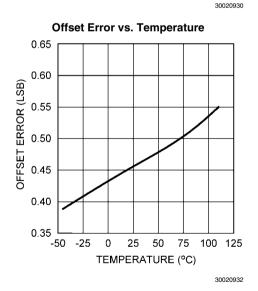

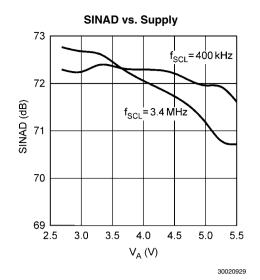

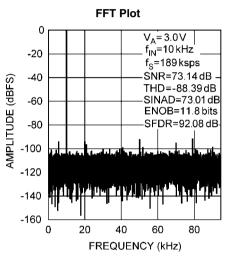

# **Typical Performance Characteristics** $f_{SCL} = 400 \, \text{kHz}, \, f_{SAMPLE} = 22 \, \text{kSPS}, \, f_{IN} = 1 \, \text{kHz}, \, V_A = 5.0 \, \text{V}, \, T_A = +25 \, ^{\circ}\text{C}, \, \text{unless otherwise stated}.$

30020923

## Continuous Operation Supply Current vs. V<sub>A</sub>

30020934

## Power Down (PD<sub>1</sub>) Supply Current vs. V<sub>A</sub>

30020936

## Automatic Conversion Supply Current vs. $V_{\rm A}$

30020935

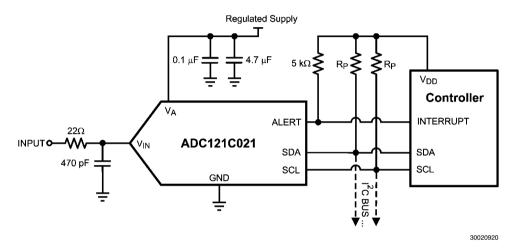

# 1.0 Functional Description

The ADC121C021 is a successive-approximation analog-to-digital converter designed around a charge-redistribution digital-to-analog converter. Unless otherwise stated, references to the ADC121C021 in this section will apply to both the ADC121C021 and the ADC121C027.

#### 1.1 CONVERTER OPERATION

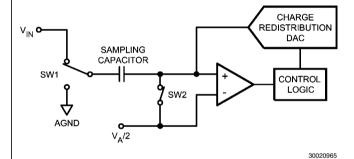

Simplified schematics of the ADC121C021 in both track and hold operation are shown in *Figure 2* and *Figure 3* respectively. In *Figure 2*, the ADC121C021 is in track mode; switch SW1 connects the sampling capacitor to the analog input channel, and SW2 equalizes the comparator inputs. The ADC is in this state for approximately 0.4µs at the beginning of every conversion cycle. Conversions occur when the conversion result register is read by the I<sup>2</sup>C controller and when the ADC is in automatic conversion mode. (see Section 1.9)

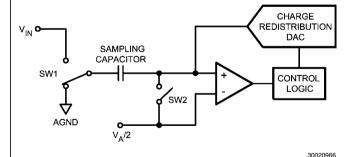

Figure 3 shows the ADC121C021 in hold mode: switch SW1 connects the sampling capacitor to ground and switch SW2 unbalances the comparator. The control logic then instructs the charge-redistribution DAC to add or subtract fixed amounts of charge to or from the sampling capacitor until the comparator is balanced. When the comparator is balanced, the digital word supplied to the DAC is also the digital representation of the analog input voltage. This digital word is stored in the conversion result register and read via the 2-wire interface.

FIGURE 2. ADC121C021 in Track Mode

FIGURE 3. ADC121C021 in Hold Mode

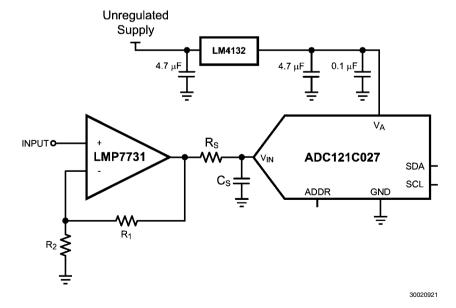

#### 1.2 ANALOG INPUT

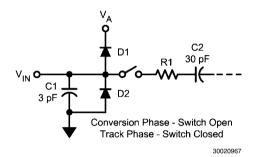

An equivalent circuit for the input of the ADC121C021 is shown in *Figure 4*. Diodes D1 and D2 provide ESD protection for the analog input. The operating range for the analog input is 0 V to  $V_A$ . Going beyond this range will cause the ESD diodes to conduct and result in erratic operation.

The capacitor C1 in Figure 4 has a typical value of 3 pF and is mainly the package pin capacitance. Resistor R1 is the on resistance ( $R_{ON}$ ) of the multiplexer and track / hold switch and is typically  $500\Omega$ . Capacitor C2 is the ADC121C021 sampling capacitor, and is typically 30 pF. The ADC121C021 will deliver best performance when driven by a low-impedance source (less than  $100\Omega$ ). This is especially important when using the ADC121C021 to sample dynamic signals. The dynamic performance of the ADC will be affected significantly by large source impedances. An input buffer amplifier may be necessary to limit source impedance. A high-accuracy opamp is recommended to maximize circuit performance. Also important when sampling dynamic signals is an anti-aliasing band-pass or low-pass filter which reduces harmonics and noise at the input.

FIGURE 4. Equivalent Input Circuit

#### 1.3 ADC TRANSFER FUNCTION

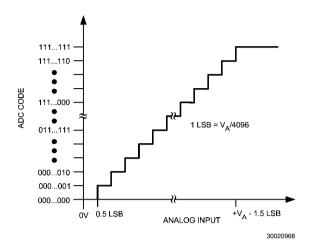

The output format of the ADC121C021 is straight binary. Code transitions occur midway between successive integer LSB values. The LSB width for the ADC121C021 is  $\rm V_A/4096$ . The ideal transfer characteristic is shown in Figure 5. The transition from an output code of 0000 0000 0000 to a code of 0000 0000 0000 0001 is at 1/2 LSB, or a voltage of  $\rm V_A/8192$ . Other code transitions occur at intervals of 1 LSB.

FIGURE 5. Ideal Transfer Characteristic

#### 1.4 REFERENCE VOLTAGE

The ADC121C021 uses the supply  $(V_A)$  as the reference. With that said,  $V_A$  must be treated as a reference. The analog-to-digital conversion will only be as precise as the reference  $(V_A)$ . Therefore, the reference  $(V_A)$  should be free of noise. It is also recommended that the reference be driven by a voltage source with low output impedance.

The Applications section provides recommended ways to drive the reference  $(V_A)$  appropriately. Refer to Section 2.1 for details.

#### 1.5 POWER-ON RESET

The power-on reset (POR) state is the point at which the supply voltage rises above the power-on reset threshold, generating an internal reset. Each of the registers contains a defined value upon POR and this data remains there until any of the following occurs:

- The first conversion is completed, causing the Conversion Result Register and various status registers to be updated internally.

- The master writes a different data word to any of the writeable registers.

- The ADC is powered down.

When resetting the device, it is crutial that the  $V_A$  supply be lowered to a maximum of 200mV before the supply is raised again to power-up the device. Dropping the supply to within 200mV of GND during a reset will ensure the ADC performs as specified.

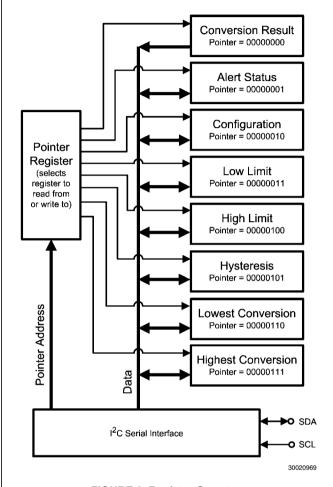

#### 1.6 INTERNAL REGISTERS

The ADC121C021 is equipped with 8 internal data registers and one address pointer register. The registers provide additional ADC functions such as storing minimum and maximum conversion results, setting alert threshold levels, and storing data to configure the operation of the device. *Figure 6* shows all of the registers and their corresponding address pointer values. All of the registers are read/write capable except the conversion result register which is read-only.

## 1.6.1 Address Pointer Register

The address pointer register controls which of the data registers is accessed by the I<sup>2</sup>C interface. The first data byte of every write operation is stored in the address pointer register. This value selects the register that the following data bytes will be written to or read from. Only the three LSBs of this register are relevant. The other bits must always be written as zeros. After a power-on reset, the pointer register defaults to all zeros (conversion result register).

Default Value: 00h

| P7 | P6 | P5 | P4 | P3 | P2              | P1 | P0    |

|----|----|----|----|----|-----------------|----|-------|

| 0  | 0  | 0  | 0  | 0  | Register Select |    | elect |

| P2 | P1 | P0 | REGISTER                        |

|----|----|----|---------------------------------|

| 0  | 0  | 0  | Conversion Result (read only)   |

| 0  | 0  | 1  | Alert Status (read/write)       |

| 0  | 1  | 0  | Configuration (read/write)      |

| 0  | 1  | 1  | Low Limit (read/write)          |

| 1  | 0  | 0  | High Limit (read/write)         |

| 1  | 0  | 1  | Hysteresis (read/write)         |

| 1  | 1  | 0  | Lowest Conversion (read/write)  |

| 1  | 1  | 1  | Highest Conversion (read/write) |

FIGURE 6. Register Structure

#### 1.6.2 Conversion Result Register

Pointer Address 00h (Read Only)

Default Value: 0000h

| D15        | D14      | D13 | D12 | D11                     | D10 | D9 | D8 |  |

|------------|----------|-----|-----|-------------------------|-----|----|----|--|

| Alert Flag | Reserved |     |     | Conversion Result[11:8] |     |    |    |  |

|            |          |     |     |                         |     |    |    |  |

| D7                     | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|------------------------|----|----|----|----|----|----|----|

| Conversion Result[7:0] |    |    |    |    |    |    |    |

| Bits  | Name              | Description                                                                                                                                                                                                                                                                                                                                                                         |

|-------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15    | Alert Flag        | When the Alert Bit Enable is set in the Configuration Register, this bit will be high if either alert flag is set in the Alert Status Register. Otherwise, this bit is a zero. This bit indicates that an alert condition has occured. The I <sup>2</sup> C controller will typically read the Alert Status register and other data registers to determine the source of the alert. |

| 14:12 | Reserved          | Always reads zeros.                                                                                                                                                                                                                                                                                                                                                                 |

| 11:0  | Conversion Result | The Analog-to-Digital conversion result. The Conversion result data is a 12-bit data word in straight binary format. The MSB is D11.                                                                                                                                                                                                                                                |

## 1.6.3 Alert Status Register

Pointer Address 01h (Read/Write)

Default Value: 00h

| D7 | D6       | D5    | D4    | D3 | D2 | D1 | D0 |

|----|----------|-------|-------|----|----|----|----|

|    | Reserved |       |       |    |    |    |    |

|    |          | Alert | Alert |    |    |    |    |

| Bits | Name                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2  | Reserved                  | Always reads zeros. Zeros must be written to these bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

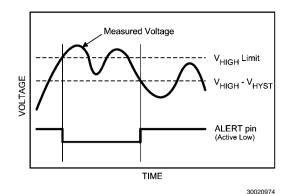

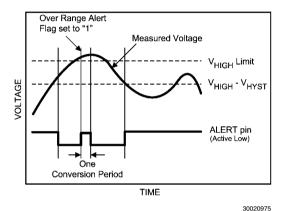

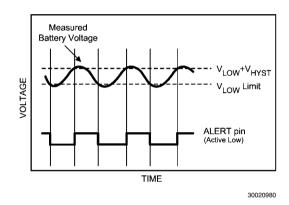

| 1    | Over Range<br>Alert Flag  | Bit is set to 1 when the measured voltage exceeds the V <sub>HIGH</sub> limit stored in the programmable V <sub>HIGH</sub> limit register. Flag is reset to 0 when one of the following two conditions is met: (1) The controller writes a one to this bit. (2) The measured voltage decreases below the programmed V <sub>HIGH</sub> limit minus the programmed V <sub>HYST</sub> value (See <i>Figure 9</i> ). The alert will only self-clear if the Alert Hold bit is cleared in the Configuration register. If the Alert Hold bit is set, the only way to clear an over range alert is to write a one to this bit. |

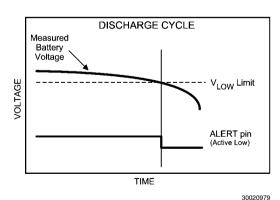

| 0    | Under Range<br>Alert Flag | Bit is set to 1 when the measured voltage falls below the $V_{LOW}$ limit stored in the programmable $V_{LOW}$ limit register. Flag is reset to 0 when one of the following two conditions is met: (1) The controller writes a one to this bit. (2) The measured voltage increases above the programmed $V_{LOW}$ limit plus the programmed $V_{HYST}$ value. The alert will only self-clear if the Alert Hold bit is cleared in the Configuration register. If the Alert Hold bit is set, the only way to clear an under range alert is to write a one to this bit.                                                   |

## 1.6.4 Configuration Register

Pointer Address 02h (Read/Write)

Default Value: 00h

| D7               | D6 | D5    | D4    | D3     | D2     | D1       | D0 |

|------------------|----|-------|-------|--------|--------|----------|----|

| Cycle Time [2:0] |    | Alert | Alert | Alert  | 0      | Polarity |    |

|                  |    | Hold  | Flag  | Pin    |        |          |    |

|                  |    |       |       | Enable | Enable |          |    |

| Сус | le Time | [2:0] | Conversion                  | Typical                        |

|-----|---------|-------|-----------------------------|--------------------------------|

| D7  | D6      | D5    | Interval                    | f <sub>convert</sub><br>(kSPS) |

| 0   | 0       | 0     | Mode Disabled               | 0                              |

| 0   | 0       | 1     | T <sub>convert</sub> x 32   | 27                             |

| 0   | 1       | 0     | T <sub>convert</sub> x 64   | 13.5                           |

| 0   | 1       | 1     | T <sub>convert</sub> x 128  | 6.7                            |

| 1   | 0       | 0     | T <sub>convert</sub> x 256  | 3.4                            |

| 1   | 0       | 1     | T <sub>convert</sub> x 512  | 1.7                            |

| 1   | 1       | 0     | T <sub>convert</sub> x 1024 | 0.9                            |

| 1   | 1       | 1     | T <sub>convert</sub> x 2048 | 0.4                            |

| Bits | Name              | Description                                                                                                                                                                                                                                         |

|------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:5  | Cycle Time        | Configures Automatic Conversion mode. When these bits are set to zeros, the automatic conversion mode is disabled. This is the case at power-up.  When these bits are set to a non-zero value, the ADC will begin operating in automatic conversion |

|      |                   | mode. (See Section 1.9). The Cycle Time table shows how different values provide various conversion intervals.                                                                                                                                      |

| 4    | Alert Hold        | O: Alerts will self-clear when the measured voltage moves within the limits by more than the hysteresis register value.  1: Alerts will not self-clear and are only cleared when a one is written to the alert high flag or the                     |

|      |                   | alert low flag in the Alert Status register.                                                                                                                                                                                                        |

| 3    | Alert Flag Enable | O: Disables alert status bit [D15] in the Conversion Result register.     1: Enables alert status bit [D15] in the Conversion Result register.                                                                                                      |

| 2    | Alert Pin Enable  | 0: Disables the ALERT output pin. The ALERT output will TRI-STATE when the pin is disabled.  1: Enables the ALERT output pin.  *This bit does not apply to the ADC121C027.                                                                          |

| 1    | Reserved          | Always reads zeros. Zeros must be written to these bits.                                                                                                                                                                                            |

| 0    | Polarity          | This bit configures the active level polarity of the ALERT output pin.  0: Sets the ALERT pin to active low.  1: Sets the ALERT pin to active high.  *This bit does not apply to the ADC121C027.                                                    |

# 1.6.5 V<sub>LOW</sub> -- Alert Limit Register - Under Range

Pointer Address 03h (Read/Write)

Default Value: 0000h

| D15         D14         D13         D12         D11         D10         D9         D8 |      |       |    |                              | D8 |    |    |  |

|---------------------------------------------------------------------------------------|------|-------|----|------------------------------|----|----|----|--|

|                                                                                       | Rese | erved |    | V <sub>LOW</sub> Limit[11:8] |    |    |    |  |

|                                                                                       |      |       |    |                              |    |    |    |  |

| D7                                                                                    | D6   | D5    | D4 | D3                           | D2 | D1 | D0 |  |

| V <sub>LOW</sub> Limit[7:0]                                                           |      |       |    |                              |    |    |    |  |

| Bits  | Name     | Description                                                                                                                                          |

|-------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:12 | Reserved | Always reads zeros. Zeros must be written to these bits.                                                                                             |

| 11:0  | LOW      | Sets the lower limit threshold used to determine the alert condition. If the conversion moves lower than this limit, a $V_{LOW}$ alert is generated. |

# 1.6.6 V<sub>HIGH</sub> -- Alert Limit Register - Over Range

Pointer Address 04h (Read/Write)

Default Value: 0FFFh

| D15 | D14                          | D13   | D12 | D11 D10 D9 D8                 |    |    |    |  |

|-----|------------------------------|-------|-----|-------------------------------|----|----|----|--|

|     | Rese                         | erved |     | V <sub>HIGH</sub> Limit[11:8] |    |    |    |  |

|     |                              |       |     | -                             |    |    |    |  |

| D7  | D6                           | D5    | D4  | D3                            | D2 | D1 | D0 |  |

|     | V <sub>HIGH</sub> Limit[7:0] |       |     |                               |    |    |    |  |

| Bits  | Name     | Description                                                                                                                                                   |

|-------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:12 | Reserved | Always reads zeros. Zeros must be written to these bits.                                                                                                      |

| 11:0  | HIGH     | Sets the upper limit threshold used to determine the alert condition. If the conversion moves higher than this limit, a V <sub>HIGH</sub> alert is generated. |

# 1.6.7 V<sub>HYST</sub> -- Alert Hysteresis Register

Pointer Address 05h (Read/Write)

Default Value: 0000h

| D15             | D14                       | D13 | D12 | D11 | D10 | D9 | D8 |

|-----------------|---------------------------|-----|-----|-----|-----|----|----|

|                 | Reserved Hysteresis[11:8] |     |     |     |     |    |    |

|                 | ·                         |     |     |     |     |    |    |

| D7              | D7 D6 D5 D4 D3 D2 D1 D0   |     |     |     |     |    |    |

| Hysteresis[7:0] |                           |     |     |     |     |    |    |

| Bits  | Name       | Description                                                                                                                  |

|-------|------------|------------------------------------------------------------------------------------------------------------------------------|

| 15:12 | Reserved   | Always reads zeros. Zeros must be written to these bits.                                                                     |

| 11:0  | Hysteresis | Sets the hysteresis value used to determine the alert condition. After a V <sub>HIGH</sub> or V <sub>LOW</sub> alert occurs, |

|       |            | the conversion result must move within the V <sub>HIGH</sub> or V <sub>LOW</sub> limit by more than this value to clear      |

|       |            | the alert condition.                                                                                                         |

|       |            | Note: If the Alert Hold bit is set in the configuration register, alert conditions will not self-clear.                      |

# 1.6.8 V<sub>MIN</sub> -- Lowest Conversion Register

Pointer Address 06h (Read/Write)

Default Value: 0FFFh

| D15                                                                             | D14                              | D13 | D12 | D11 | D10 | D9 | D8 |

|---------------------------------------------------------------------------------|----------------------------------|-----|-----|-----|-----|----|----|

|                                                                                 | Reserved Lowest Conversion[11:8] |     |     |     |     |    |    |

|                                                                                 | ·                                |     |     |     |     |    |    |

| D7         D6         D5         D4         D3         D2         D1         D0 |                                  |     |     |     |     |    |    |

| Lowest Conversion[7:0]                                                          |                                  |     |     |     |     |    |    |

| Bits  | Name              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:12 | Reserved          | Always reads zeros. Zeros must be written to these bits.                                                                                                                                                                                                                                                                                                                                                                                                                |

| 11:0  | Lowest Conversion | Contains the Lowest Conversion result. Each conversion result is compared against the contents of this register. If the value is lower, it becomes the lowest conversion and replaces the current value. If the value is higher, the register contents remain unchanged. The lowest conversion value can be cleared at any time by writting 0FFFh to this register. The value of this register will update automatically when the automatic conversion mode is enabled. |

# 1.6.9 V<sub>MAX</sub> -- Highest Conversion Register

Pointer Address 07h (Read/Write)

Default Value: 0000h

| D15                                   | D14                               | D13 | D12 | D11 | D10 | D9 | D8 |  |

|---------------------------------------|-----------------------------------|-----|-----|-----|-----|----|----|--|

|                                       | Reserved Highest Conversion[11:8] |     |     |     |     |    |    |  |

| · · · · · · · · · · · · · · · · · · · |                                   |     |     |     |     |    |    |  |

| D7 D6 D5 D4 D3 D2 D1 D0               |                                   |     |     |     |     |    |    |  |

| Highest Conversion[7:0]               |                                   |     |     |     |     |    |    |  |

| Bits  | Name               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:12 | Reserved           | Always reads zeros. Zeros must be written to these bits.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 11:0  | Highest Conversion | Contains the Highest Conversion result. Each conversion result is compared against the contents of this register. If the value is higher, it becomes the highest conversion and replaces the previous value. If the value is lower, the register contents remain unchanged. The highest conversion value can be cleared at any time by writting 0000h to this register. The value of this register will update automatically when the automatic conversion mode is enabled. |

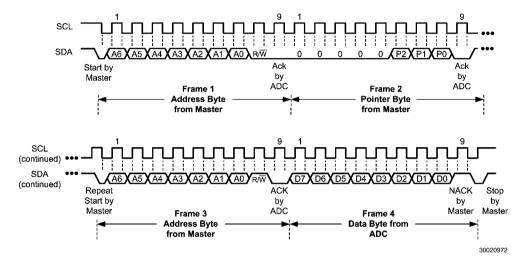

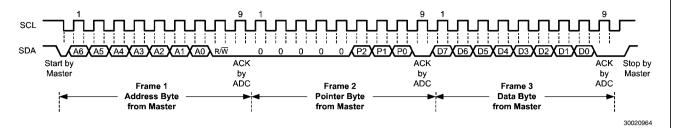

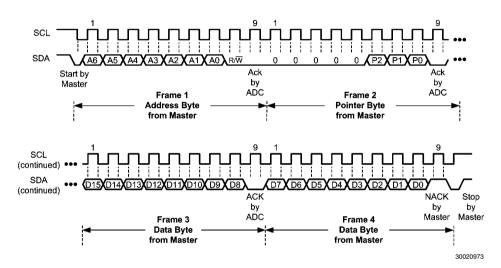

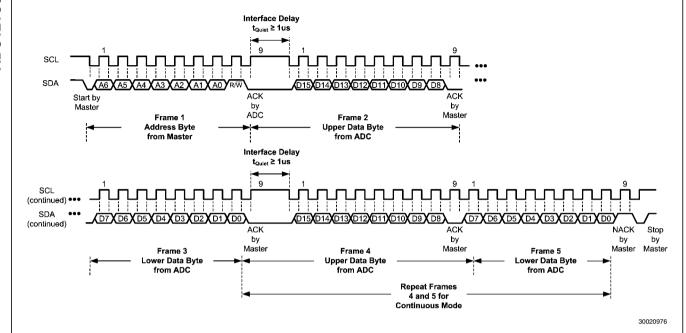

#### 1.7 SERIAL INTERFACE