www.DataS

# ADC128S052

# 8-Channel, 200 kSPS to 500 kSPS, 12-Bit A/D Converter

# **General Description**

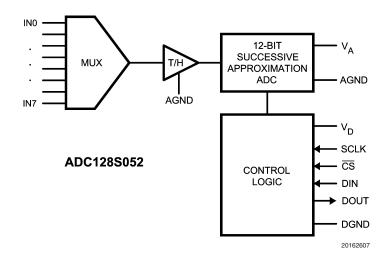

The ADC128S052 is a low-power, eight-channel CMOS 12-bit analog-to-digital converter specified for conversion throughput rates of 200 kSPS to 500 kSPS. The converter is based on a successive-approximation register architecture with an internal track-and-hold circuit. It can be configured to accept up to eight input signals at inputs IN0 through IN7.

The output serial data is straight binary and is compatible with several standards, such as SPI™, QSPI, MICROWIRE, and many common DSP serial interfaces.

The ADC128S052 may be operated with independent analog and digital supplies. The analog supply ( $V_A$ ) can range from +2.7V to +5.25V, and the digital supply ( $V_D$ ) can range from +2.7V to  $V_A$ . Normal power consumption using a +3V or +5V supply is 1.6 mW and 8.7 mW, respectively. The power-down feature reduces the power consumption to 0.06  $\mu$ W using a +3V supply and 0.25  $\mu$ W using a +5V supply.

The ADC128S052 is packaged in a 16-lead TSSOP package. Operation over the extended industrial temperature range of  $-40^{\circ}$ C to  $+105^{\circ}$ C is guaranteed.

#### **Features**

- Eight input channels

- Variable power management

- Independent analog and digital supplies

- SPI™/QSPI™/MICROWIRE™/DSP compatible

- Packaged in 16-lead TSSOP

### **Key Specifications**

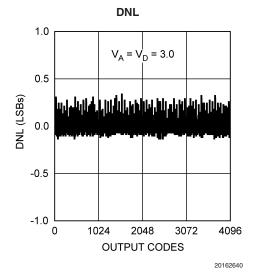

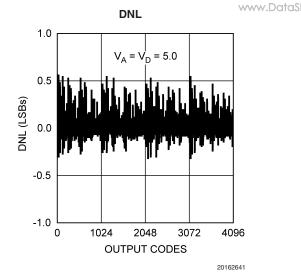

■ Conversion Rate 200 kSPS to 500 kSPS ■ DNL ( $V_A = V_D = 5.0 \text{ V}$ ) +1.3 / -0.9 LSB (max)

■ INL  $(V_A = V_D = 5.0 \text{ V})$  ±1.0 LSB (max)

Power Consumption

— 3V Supply

— 5V Supply

1.6 mW (typ)

8.7 mW (typ)

# **Applications**

- Automotive Navigation

- Portable Systems

- Medical Instruments

- Mobile Communications

- Instrumentation and Control Systems

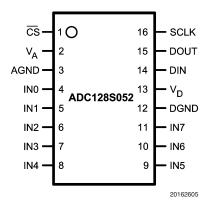

# **Connection Diagram**

# Ordering Information

| Order Code      | Temperature Range | Description                        |

|-----------------|-------------------|------------------------------------|

| ADC128S052CIMT  | -40°C to +105°C   | 16-Lead TSSOP Package              |

| ADC128S052CIMTX | -40°C to +105°C   | 16-Lead TSSOP Package, Tape & Reel |

| ADC128S052EVAL  |                   | Evaluation Board                   |

TRI-STATE® is a trademark of National Semiconductor Corporation.

MICROWIRE™ is a trademark of National Semiconductor Corporation.

QSPI™ and SPI™ are trademarks of Motorola, Inc.

# **Block Diagram**

www.DataSheet4U.com

# Pin Descriptions and Equivalent Circuits

| Pin No.     | Symbol         | <b>Equivalent Circuit</b> | Description                                                                       |  |  |  |  |  |

|-------------|----------------|---------------------------|-----------------------------------------------------------------------------------|--|--|--|--|--|

| ANALOG I/O  |                |                           |                                                                                   |  |  |  |  |  |

| 4 - 11      | IN0 to IN7     |                           | Analog inputs. These signals can range from 0V to V <sub>REF</sub> .              |  |  |  |  |  |

| DIGITAL I/O |                |                           |                                                                                   |  |  |  |  |  |

|             |                |                           | Digital clock input. The guaranteed performance range of                          |  |  |  |  |  |

| 16          | SCLK           |                           | frequencies for this input is 3.2 MHz to 8 MHz. This clock                        |  |  |  |  |  |

|             |                |                           | directly controls the conversion and readout processes.                           |  |  |  |  |  |

| 15          | DOUT           |                           | Digital data output. The output samples are clocked out of this                   |  |  |  |  |  |

| 15          | DOOT           |                           | pin on the falling edges of the SCLK pin.                                         |  |  |  |  |  |

| 14          | DIN            |                           | Digital data input. The ADC128S052's Control Register is                          |  |  |  |  |  |

| 14          | DIIN           |                           | loaded through this pin on rising edges of the SCLK pin.                          |  |  |  |  |  |

| 1           | <del>CS</del>  |                           | Chip select. On the falling edge of $\overline{\text{CS}}$ , a conversion process |  |  |  |  |  |

| '           | 05             |                           | begins. Conversions continue as long as $\overline{\text{CS}}$ is held low.       |  |  |  |  |  |

| POWER SUF   | PPLY           |                           |                                                                                   |  |  |  |  |  |

|             |                |                           | Positive analog supply pin. This voltage is also used as the                      |  |  |  |  |  |

|             |                |                           | reference voltage. This pin should be connected to a quiet                        |  |  |  |  |  |

| 2           | V <sub>A</sub> |                           | +2.7V to +5.25V source and bypassed to GND with 1 μF and                          |  |  |  |  |  |

|             |                |                           | 0.1 µF monolithic ceramic capacitors located within 1 cm of                       |  |  |  |  |  |

|             |                |                           | the power pin.                                                                    |  |  |  |  |  |

|             |                |                           | Positive digital supply pin. This pin should be connected to a                    |  |  |  |  |  |

| 13          | \ \            |                           | +2.7V to V <sub>A</sub> supply, and bypassed to GND with a 0.1 μF                 |  |  |  |  |  |

| 13          | V <sub>D</sub> |                           | monolithic ceramic capacitor located within 1 cm of the power                     |  |  |  |  |  |

|             |                |                           | pin.                                                                              |  |  |  |  |  |

| 3           | AGND           |                           | The ground return for the analog supply and signals.                              |  |  |  |  |  |

| 12          | DGND           |                           | The ground return for the digital supply and signals.                             |  |  |  |  |  |

# **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Analog Supply Voltage VA -0.3V to 6.5V Digital Supply Voltage V<sub>D</sub> -0.3V to  $V_A + 0.3V$ , max 6.5V Voltage on Any Pin to GND -0.3V to  $V_A + 0.3V$ Input Current at Any Pin (Note 3) ±10 mA Package Input Current(Note 3) ±20 mA Power Dissipation at T<sub>A</sub> = 25°C See (Note 4) ESD Susceptibility (Note 5) Human Body Model 2500V Machine Model 250V

10 seconds (Note 6)  $260^{\circ}\text{C}$ Junction Temperature  $+150^{\circ}\text{C}$ Storage Temperature  $-65^{\circ}\text{C}$  to  $+150^{\circ}\text{C}$

Soldering Temperature, Infrared,

### Operating Ratings (Notes 1, 2)

Operating Temperature  $-40^{\circ}\text{C} \leq T_{A} \leq \text{+105}^{\circ}\text{C}$

$\begin{array}{lll} \text{V}_{\text{A}} & \text{Supply Voltage} & +2.7 \text{V to } +5.25 \text{V} \\ \text{V}_{\text{D}} & \text{Supply Voltage} & +2.7 \text{V to } \text{V}_{\text{A}} \\ \text{Digital Input Voltage} & 0 \text{V to } \text{V}_{\text{A}} \\ \text{Analog Input Voltage} & 0 \text{V to } \text{V}_{\text{A}} \\ \text{Clock Frequency} & 3.2 \text{ MHz to } 8 \text{ MHz} \end{array}$

# **Package Thermal Resistance**

| Package            | $\theta_{JA}$ |  |

|--------------------|---------------|--|

| 16-lead TSSOP on   | 96°C / W      |  |

| 4-layer, 2 oz. PCB |               |  |

Soldering process must comply with National Semiconductor's Reflow Temperature Profile specifications. Refer to www.national.com/packaging. (Note 6)

### **ADC128S052 Converter Electrical Characteristics** (Note 8)

The following specifications apply for AGND = DGND = 0V,  $f_{SCLK}$  = 3.2 MHz to 8 MHz,  $f_{SAMPLE}$  = 200 kSPS to 500 kSPS,  $C_L$  = 50pF, unless otherwise noted. **Boldface limits apply for T\_A = T\_{MIN} to T\_{MAX}:** all other limits  $T_A$  = 25°C.

| Symbol                           | Parameter                             | Conditions                                                              | Typical | Limits<br>(Note 7) | Units     |  |  |

|----------------------------------|---------------------------------------|-------------------------------------------------------------------------|---------|--------------------|-----------|--|--|

| STATIC CONVERTER CHARACTERISTICS |                                       |                                                                         |         |                    |           |  |  |

|                                  | Resolution with No Missing Codes      |                                                                         |         | 12                 | Bits      |  |  |

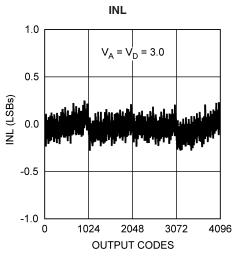

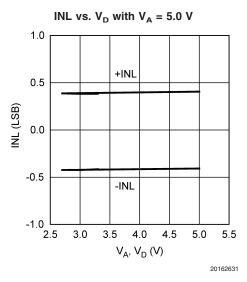

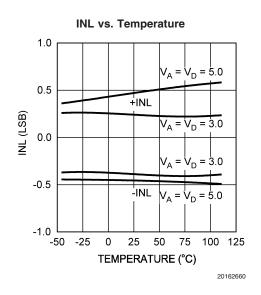

| INL                              | Integral Non-Linearity (End Point     | $V_A = V_D = +3.0V$                                                     | ±0.3    | ±1                 | LSB (max) |  |  |

| IINL                             | Method)                               | $V_A = V_D = +5.0V$                                                     | ±0.4    | ±1                 | LSB (max) |  |  |

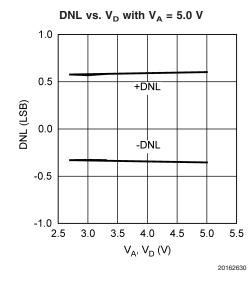

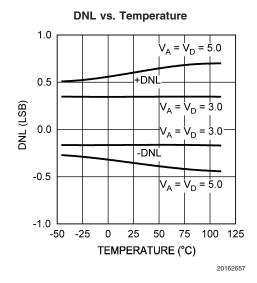

|                                  |                                       | $V_{\Delta} = V_{D} = +3.0V$                                            | +0.3    | +0.9               | LSB (max) |  |  |

| DNL                              | Differential Non-Linearity            | $V_A = V_D = +3.0V$                                                     | -0.2    | -0.7               | LSB (min) |  |  |

| DINL                             | Differential Non-Linearity            | $V_A = V_D = +5.0V$                                                     | +0.6    | +1.3               | LSB (max) |  |  |

|                                  |                                       | $V_A = V_D = +3.0V$                                                     | -0.4    | -0.9               | LSB (min) |  |  |

| V                                | Officet Error                         | $V_A = V_D = +3.0V$                                                     | +0.8    | ±2.3               | LSB (max) |  |  |

| $V_{OFF}$                        | Offset Error                          | $V_A = V_D = +5.0V$                                                     | +1.2    | ±2.3               | LSB (max) |  |  |

| OEM                              | Offset Error Match                    | $V_A = V_D = +3.0V$                                                     | ±0.05   | ±1.5               | LSB (max) |  |  |

| OEIVI                            |                                       | $V_A = V_D = +5.0V$                                                     | ±0.2    | ±1.5               | LSB (max) |  |  |

| FSE                              | Full Scale Error                      | $V_A = V_D = +3.0V$                                                     | +0.6    | ±2.0               | LSB (max) |  |  |

| FSE                              |                                       | $V_A = V_D = +5.0V$                                                     | +0.3    | ±2.0               | LSB (max) |  |  |

| FSEM                             | Full Scale Error Match                | $V_A = V_D = +3.0V$                                                     | ±0.05   | ±1.5               | LSB (max) |  |  |

| FSEIVI                           |                                       | $V_A = V_D = +5.0V$                                                     | ±0.2    | ±1.5               | LSB (max) |  |  |

| DYNAMIC (                        | CONVERTER CHARACTERISTICS             |                                                                         |         |                    |           |  |  |

| FPBW                             | Full Dower Bondwidth ( 2dB)           | $V_A = V_D = +3.0V$                                                     | 8       |                    | MHz       |  |  |

| FFDVV                            | Full Power Bandwidth (-3dB)           | $V_A = V_D = +5.0V$                                                     | 11      |                    | MHz       |  |  |

| SINAD                            | Signal-to-Noise Plus Distortion Ratio | $V_A = V_D = +3.0V,$<br>$f_{IN} = 40.2 \text{ kHz}, -0.02 \text{ dBFS}$ | 73      | 70                 | dB (min)  |  |  |

| SINAD                            |                                       | $V_A = V_D = +5.0V,$<br>$f_{IN} = 40.2 \text{ kHz}, -0.02 \text{ dBFS}$ | 73      | 70                 | dB (min)  |  |  |

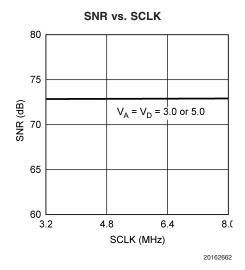

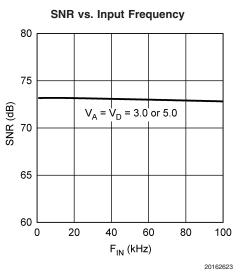

| SNR                              | Signal to Naice Patie                 | $V_A = V_D = +3.0V,$<br>$f_{IN} = 40.2 \text{ kHz}, -0.02 \text{ dBFS}$ | 73      | 70.8               | dB (min)  |  |  |

| SINH                             | Signal-to-Noise Ratio                 | $V_A = V_D = +5.0V,$<br>$f_{IN} = 40.2 \text{ kHz}, -0.02 \text{ dBFS}$ | 73      | 70.8               | dB (min)  |  |  |

ADC128S052 Converter Electrical Characteristics (Note 8) (Continued)

The following specifications apply for AGND = DGND = 0V, f<sub>SCLK</sub> = 3.2 MHz to 8 MHz, f<sub>SAMPLE</sub> = 200 kSPS to 500 kSPS, C<sub>L</sub> = 50pF, unless otherwise noted. Boldface limits apply for T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>: all other limits T<sub>A</sub> = 25°C. www.DataSheet4U.com

| Symbol           | Parameter                                                                                     | Conditions                                                               | Typical             | Limits<br>(Note 7) | Units      |

|------------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|---------------------|--------------------|------------|

| DYNAMIC          | CONVERTER CHARACTERISTICS                                                                     |                                                                          |                     |                    |            |

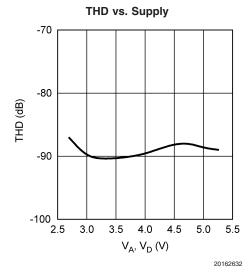

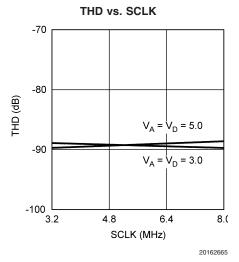

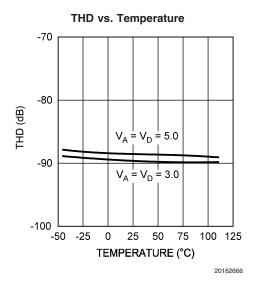

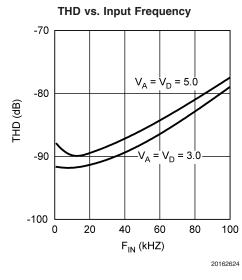

| THD              | Total Harmonic Distortion                                                                     | $V_A = V_D = +3.0V,$<br>$f_{IN} = 40.2 \text{ kHz}, -0.02 \text{ dBFS}$  | -90                 | -74                | dB (max)   |

| לווט             | Total Harmonic Distortion                                                                     | $V_A = V_D = +5.0V,$<br>$f_{IN} = 40.2 \text{ kHz}, -0.02 \text{ dBFS}$  | -89                 | -74                | dB (max)   |

| SFDR             | Spurious-Free Dynamic Range                                                                   | $V_A = V_D = +3.0V,$<br>$f_{IN} = 40.2 \text{ kHz}, -0.02 \text{ dBFS}$  | 92                  | 75                 | dB (min)   |

| SFDN             | Spullous-Free Dynamic Hange                                                                   | $V_A = V_D = +5.0V,$<br>$f_{IN} = 40.2 \text{ kHz}, -0.02 \text{ dBFS}$  | 91                  | 75                 | dB (min)   |

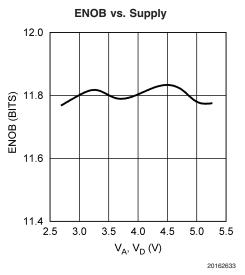

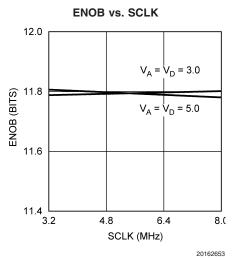

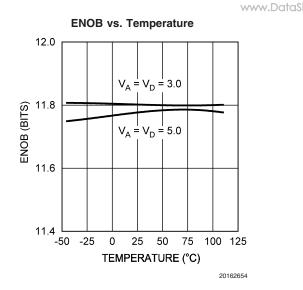

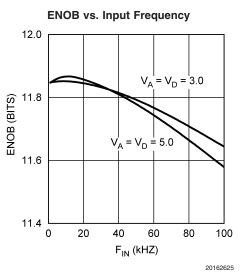

| ENOB             | Effective Number of Pite                                                                      | $V_A = V_D = +3.0V,$<br>$f_{IN} = 40.2 \text{ kHz}$                      | 11.8                | 11.3               | Bits (min) |

| ENOB             | Effective Number of Bits                                                                      | $V_A = V_D = +5.0V,$<br>$f_{IN} = 40.2 \text{ kHz}, -0.02 \text{ dBFS}$  | 11.8                | 11.3               | Bits (min) |

| ISO              | Channel-to-Channel Isolation                                                                  | $V_A = V_D = +3.0V,$<br>$f_{IN} = 20 \text{ kHz}$                        | 81                  |                    | dB         |

| 150              |                                                                                               | $V_A = V_D = +5.0V,$<br>$f_{IN} = 20 \text{ kHz}, -0.02 \text{ dBFS}$    | 81                  |                    | dB         |

|                  | Intermodulation Distortion, Second Order Terms  Intermodulation Distortion, Third Order Terms | $V_A = V_D = +3.0V,$<br>$f_a = 19.5 \text{ kHz}, f_b = 20.5 \text{ kHz}$ | -98                 |                    | dB         |

| IMD              |                                                                                               | $V_A = V_D = +5.0V,$<br>$f_a = 19.5 \text{ kHz}, f_b = 20.5 \text{ kHz}$ | -91                 |                    | dB         |

| IIVID            |                                                                                               | $V_A = V_D = +3.0V,$<br>$f_a = 19.5 \text{ kHz}, f_b = 20.5 \text{ kHz}$ | -89                 |                    | dB         |

|                  |                                                                                               | $V_A = V_D = +5.0V,$<br>$f_a = 19.5 \text{ kHz}, f_b = 20.5 \text{ kHz}$ | -88                 |                    | dB         |

| ANALOG I         | NPUT CHARACTERISTICS                                                                          |                                                                          |                     |                    |            |

| $V_{IN}$         | Input Range                                                                                   |                                                                          | 0 to V <sub>A</sub> |                    | V          |

| I <sub>DCL</sub> | DC Leakage Current                                                                            |                                                                          |                     | ±1                 | μA (max)   |

| C <sub>INA</sub> | Input Capacitance                                                                             | Track Mode                                                               | 33                  |                    | pF         |

|                  |                                                                                               | Hold Mode                                                                | 3                   |                    | pF         |

| DIGITAL IN       | NPUT CHARACTERISTICS                                                                          |                                                                          |                     |                    |            |

| $V_{IH}$         | Input High Voltage                                                                            | $V_A = V_D = +2.7V \text{ to } +3.6V$                                    |                     | 2.1                | V (min)    |

|                  |                                                                                               | $V_A = V_D = +4.75V \text{ to } +5.25V$                                  |                     | 2.4                | V (min)    |

| V <sub>IL</sub>  | Input Low Voltage                                                                             | $V_A = V_D = +2.7V \text{ to } +5.25V$                                   |                     | 0.8                | V (max)    |

| I <sub>IN</sub>  | Input Current                                                                                 | $V_{IN} = 0V \text{ or } V_{D}$                                          | ±0.01               | ±1                 | μA (max)   |

| C <sub>IND</sub> | Digital Input Capacitance                                                                     |                                                                          | 2                   | 4                  | pF (max)   |

# ADC128S052 Converter Electrical Characteristics (Note 8) (Continued)

The following specifications apply for AGND = DGND = 0V,  $f_{SCLK}$  = 3.2 MHz to 8 MHz,  $f_{SAMPLE}$  = 200 kSPS to 500 kSPS,  $C_L$  = 50pF, unless otherwise noted. **Boldface limits apply for T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>**: all other limits T<sub>A</sub> = 25°C. www.DataSh

| Symbol                            | Parameter                                                                                                                 | Conditions                                                                                            | Typical | Limits<br>(Note 7)   | Units       |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|---------|----------------------|-------------|

| ANALOG I                          | NPUT CHARACTERISTICS                                                                                                      |                                                                                                       |         |                      |             |

| DIGITAL O                         | UTPUT CHARACTERISTICS                                                                                                     |                                                                                                       |         |                      |             |

| V <sub>OH</sub>                   | Output High Voltage $ \begin{vmatrix} I_{SOURCE} = 200 \ \mu A, \\ V_A = V_D = +2.7 V \text{ to } +5.25 V \end{vmatrix} $ |                                                                                                       |         | V <sub>D</sub> - 0.5 | V (min)     |

| / <sub>OL</sub>                   | Output Low Voltage                                                                                                        | $I_{SINK} = 200 \mu A \text{ to } 1.0 \text{ mA},$<br>$V_A = V_D = +2.7 \text{V to } +5.25 \text{V}$  |         | 0.4                  | V (max)     |

| <sub>OZH</sub> , I <sub>OZL</sub> | Hi-Impedance Output Leakage<br>Current                                                                                    | $V_A = V_D = +2.7V \text{ to } +5.25V$                                                                |         | ±1                   | μA (max)    |

| Соит                              | Hi-Impedance Output Capacitance (Note 8)                                                                                  |                                                                                                       | 2       | 4                    | pF (max)    |

|                                   | Output Coding                                                                                                             |                                                                                                       | Stra    | aight (Natura        | l) Binary   |

| POWER SI                          | JPPLY CHARACTERISTICS (C <sub>L</sub> = 10                                                                                | pF)                                                                                                   |         |                      |             |

|                                   | Analan and Dinital County Valtage                                                                                         | W S W                                                                                                 |         | 2.7                  | V (min)     |

| $V_A, V_D$                        | Analog and Digital Supply Voltages                                                                                        | $V_A \ge V_D$                                                                                         |         | 5.25                 | V (max)     |

|                                   | Total Supply Current                                                                                                      | $V_A = V_D = +2.7V \text{ to } +3.6V,$<br>$f_{SAMPLE} = 500 \text{ kSPS, } f_{IN} = 40 \text{ kHz}$   | 0.54    | 1.2                  | mA (max)    |

|                                   | Normal Mode ( CS low)                                                                                                     | $V_A = V_D = +4.75V \text{ to } +5.25V,$<br>$f_{SAMPLE} = 500 \text{ kSPS, } f_{IN} = 40 \text{ kHz}$ | 1.74    | 2.6                  | mA (max)    |

| <sub>A</sub> + I <sub>D</sub>     | Total Supply Current<br>Shutdown Mode (CS high)                                                                           | $V_A = V_D = +2.7V \text{ to } +3.6V,$<br>$f_{SCLK} = 0 \text{ kSPS}$                                 | 20      |                      | nA          |

|                                   |                                                                                                                           | $V_A = V_D = +4.75V \text{ to } +5.25V,$<br>$f_{SCLK} = 0 \text{ kSPS}$                               | 50      |                      | nA          |

|                                   | Power Consumption Normal Mode ( CS low)                                                                                   | $V_A = V_D = +3.0V$<br>$f_{SAMPLE} = 500 \text{ kSPS}, f_{IN} = 40 \text{ kHz}$                       | 1.6     | 3.6                  | mW (max)    |

| 2                                 |                                                                                                                           | $V_A = V_D = +5.0V$<br>$f_{SAMPLE} = 500 \text{ kSPS}, f_{IN} = 40 \text{ kHz}$                       | 8.7     | 13.0                 | mW (max)    |

| C C                               | Power Consumption                                                                                                         | $V_A = V_D = +3.0V$<br>$f_{SCLK} = 0 \text{ kSPS}$                                                    | 0.06    |                      | μW          |

|                                   | Shutdown Mode (CS high)                                                                                                   | $V_A = V_D = +5.0V$<br>$f_{SCLK} = 0 \text{ kSPS}$                                                    | 0.25    |                      | μW          |

| C ELECT                           | RICAL CHARACTERISTICS                                                                                                     |                                                                                                       |         |                      |             |

| <sub>SCLK</sub> MIN               | Minimum Clock Frequency                                                                                                   | $V_A = V_D = +2.7V \text{ to } +5.25V$                                                                | 0.8     | 3.2                  | MHz (min)   |

| SCLK                              | Maximum Clock Frequency                                                                                                   | $V_A = V_D = +2.7V \text{ to } +5.25V$                                                                | 16      | 8                    | MHz (max)   |

|                                   | Sample Rate                                                                                                               | $V_A = V_D = +2.7V \text{ to } +5.25V$                                                                | 50      | 200                  | kSPS (min)  |

| S                                 | Continuous Mode                                                                                                           | V <sub>A</sub> - V <sub>D</sub> - +2.7 V to +3.23 V                                                   | 1000    | 500                  | kSPS (max)  |

| CONVERT                           | Conversion (Hold) Time                                                                                                    | $V_A = V_D = +2.7V \text{ to } +5.25V$                                                                |         | 13                   | SCLK cycles |

| DC                                | SCLK Duty Cycle                                                                                                           | $V_A = V_D = +2.7V \text{ to } +5.25V$                                                                | 30      | 40                   | % (min)     |

|                                   | OSER Daty Gyold                                                                                                           | VA - VD - 12.7 V 10 10.20V                                                                            | 70      | 60                   | % (max)     |

| ACQ                               | Acquisition (Track) Time                                                                                                  | $V_A = V_D = +2.7V \text{ to } +5.25V$                                                                |         | 3                    | SCLK cycles |

|                                   | Throughput Time                                                                                                           | Acquisition Time + Conversion Time $V_A = V_D = +2.7V$ to $+5.25V$                                    |         | 16                   | SCLK cycles |

| t <sub>AD</sub>                   | Aperture Delay                                                                                                            | $V_A = V_D = +2.7V \text{ to } +5.25V$                                                                | 4       |                      | ns          |

### **ADC128S052 Timing Specifications**

The following specifications apply for  $V_A = V_D = +2.7V$  to +5.25V, AGND = DGND = 0V,  $f_{SCLK} = 3.2$  MHz to 8 MHz,  $f_{SAMPLE} = 200$  kSPS, and  $C_L = 50$ pF. **Boldface limits apply for T\_A = T\_{MIN} to T\_{MAX}**: all other limits  $T_A = 25$ °CataSheet4U.com

| Symbol            | Parameter                                   | Conditions   | Typical | Limits<br>(Note 7)         | Units    |

|-------------------|---------------------------------------------|--------------|---------|----------------------------|----------|

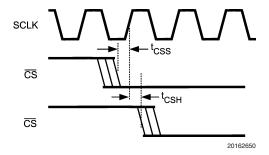

| t <sub>CSH</sub>  | CS Hold Time after SCLK Rising Edge         | (Note 9)     | 0       | 10                         | ns (min) |

| t <sub>css</sub>  | CS Setup Time prior to SCLK Rising Edge     | (Note 9)     | 4.5     | 10                         | ns (min) |

| t <sub>EN</sub>   | CS Falling Edge to DOUT enabled             |              | 5       | 30                         | ns (max) |

| t <sub>DACC</sub> | DOUT Access Time after SCLK Falling Edge    |              | 17      | 27                         | ns (max) |

| t <sub>DHLD</sub> | DOUT Hold Time after SCLK Falling Edge      |              | 4       |                            | ns (typ) |

| t <sub>DS</sub>   | DIN Setup Time prior to SCLK<br>Rising Edge |              | 3       | 10                         | ns (min) |

| t <sub>DH</sub>   | DIN Hold Time after SCLK Rising Edge        |              | 3       | 10                         | ns (min) |

| t <sub>CH</sub>   | SCLK High Time                              |              |         | 0.4 x<br>t <sub>SCLK</sub> | ns (min) |

| t <sub>CL</sub>   | SCLK Low Time                               |              |         | 0.4 x<br>t <sub>SCLK</sub> | ns (min) |

| +                 | CS Rising Edge to DOUT                      | DOUT falling | 2.4     | 20                         | ns (max) |

| t <sub>DIS</sub>  | High-Impedance                              | DOUT rising  | 0.9     | 20                         | ns (max) |

**Note 1:** Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

Note 2: All voltages are measured with respect to GND = 0V, unless otherwise specified.

Note 3: When the input voltage at any pin exceeds the power supplies (that is,  $V_{IN} < AGND$  or  $V_{IN} > V_A$  or  $V_D$ ), the current at that pin should be limited to 10 mA. The 20 mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of 10 mA to two.

Note 4: The absolute maximum junction temperature  $(T_J max)$  for this device is 150°C. The maximum allowable power dissipation is dictated by  $T_J max$ , the junction-to-ambient thermal resistance  $(\theta_{JA})$ , and the ambient temperature  $(T_A)$ , and can be calculated using the formula  $P_D MAX = (T_J max - T_A)/\theta_{JA}$ . In the 16-pin TSSOP,  $\theta_{JA}$  is 96°C/W, so  $P_D MAX = 1,200$  mW at 25°C and 625 mW at the maximum operating ambient temperature of 105°C. Note that the power consumption of this device under normal operation is a maximum of 12 mW. The values for maximum power dissipation listed above will be reached only when the ADC128S052 is operated in a severe fault condition (e.g. when input or output pins are driven beyond the power supply voltages, or the power supply polarity is reversed). Obviously, such conditions should always be avoided.

Note 5: Human body model is 100 pF capacitor discharged through a 1.5 kΩ resistor. Machine model is 220 pF discharged through ZERO ohms

Note 6: Reflow temperature profiles are different for lead-free packages.

Note 7: Tested limits are guaranteed to National's AOQL (Average Outgoing Quality Level).

Note 8: Data sheet min/max specification limits are guaranteed by design, test, or statistical analysis.

Note 9: Clock may be in any state (high or low) when  $\overline{\text{CS}}$  goes high. Setup and hold time restrictions apply only to  $\overline{\text{CS}}$  going low.

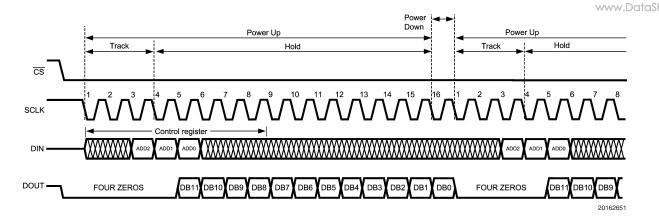

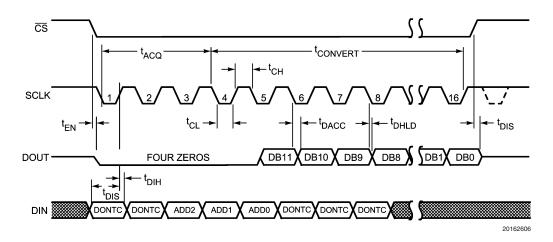

# **Timing Diagrams**

FIGURE 1. ADC128S052 Operational Timing Diagram

FIGURE 2. ADC128S052 Serial Timing Diagram

FIGURE 3. SCLK and  $\overline{\text{CS}}$  Timing Parameters

# **Specification Definitions**

**ACQUISITION TIME** is the time required for the ADC to acquire the input voltage. During this time, the hold capacitor is charged by the input voltage.

**APERTURE DELAY** is the time between the fourth falling edge of SCLK and the time when the input signal is internally acquired or held for conversion.

**CONVERSION TIME** is the time required, after the input voltage is acquired, for the ADC to convert the input voltage to a digital word.

**CHANNEL-TO-CHANNEL ISOLATION** is resistance to coupling of energy from one channel into another channel.

**CROSSTALK** is the coupling of energy from one channel into another channel. This is similar to Channel-to-Channel Isolation, except for the sign of the data.

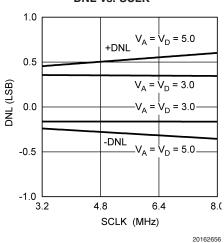

**DIFFERENTIAL NON-LINEARITY (DNL)** is the measure of the maximum deviation from the ideal step size of 1 LSB.

**DUTY CYCLE** is the ratio of the time that a repetitive digital waveform is high to the total time of one period. The specification here refers to the SCLK.

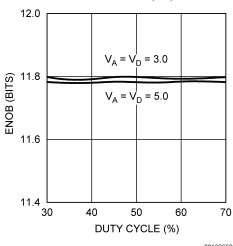

**EFFECTIVE NUMBER OF BITS (ENOB, or EFFECTIVE BITS)** is another method of specifying Signal-to-Noise and Distortion or SINAD. ENOB is defined as (SINAD - 1.76) / 6.02 and says that the converter is equivalent to a perfect ADC of this (ENOB) number of bits.

**FULL POWER BANDWIDTH** is a measure of the frequency at which the reconstructed output fundamental drops 3 dB below its low frequency value for a full scale input.

**GAIN ERROR** is the deviation of the last code transition (111...110) to (111...111) from the ideal ( $V_{REF}$  - 1.5 LSB), after adjusting for offset error.

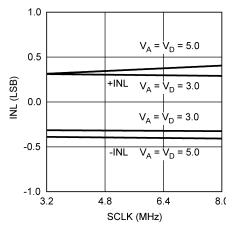

**INTEGRAL NON-LINEARITY (INL)** is a measure of the deviation of each individual code from a line drawn from negative full scale (½ LSB below the first code transition) through positive full scale (½ LSB above the last code transition). The deviation of any given code from this straight line is measured from the center of that code value.

**INTERMODULATION DISTORTION (IMD)** is the creation of additional spectral components as a result of two sinusoidal frequencies being applied to an individual ADC input at the same time. It is defined as the ratio of the power in either the

second or the third order intermodulation products to the sum of the power in both of the original frequencies. Second order products are  $f_a \pm f_b$ , where  $f_a$  and  $f_b$  are the two sine wave input frequencies. Third order products are  $(2f_a \pm f_b)$  and  $(f_a \pm 2f_b)$ . IMD is usually expressed in dB.

**MISSING CODES** are those output codes that will never appear at the ADC outputs. The ADC128S052 is guaranteed not to have any missing codes.

**OFFSET ERROR** is the deviation of the first code transition (000...000) to (000...001) from the ideal (i.e. GND + 0.5 LSB).

**SIGNAL TO NOISE RATIO (SNR)** is the ratio, expressed in dB, of the rms value of the input signal to the rms value of the sum of all other spectral components below one-half the sampling frequency, not including harmonics or d.c.

SIGNAL TO NOISE PLUS DISTORTION (S/N+D or SINAD) Is the ratio, expressed in dB, of the rms value of the input signal to the rms value of all of the other spectral components below half the clock frequency, including harmonics but excluding d.c.

**SPURIOUS FREE DYNAMIC RANGE (SFDR)** is the difference, expressed in dB, between the rms values of the input signal and the peak spurious signal where a spurious signal is any signal present in the output spectrum that is not present at the input, including harmonics but excluding d.c.

**TOTAL HARMONIC DISTORTION (THD)** is the ratio, expressed in dBc, of the rms total of the first five harmonic components at the output to the rms level of the input signal frequency as seen at the output. THD is calculated as

THD = 20 •

$$\log_{10} \sqrt{\frac{A_{f2}^2 + \dots + A_{f10}^2}{A_{f1}^2}}$$

where  $A_{f1}$  is the RMS power of the input frequency at the output and  $A_{f2}$  through  $A_{f10}$  are the RMS power in the first 9 harmonic frequencies.

**THROUGHPUT TIME** is the minimum time required between the start of two successive conversions. It is the acquisition time plus the conversion time.

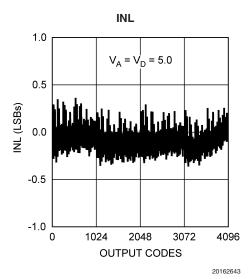

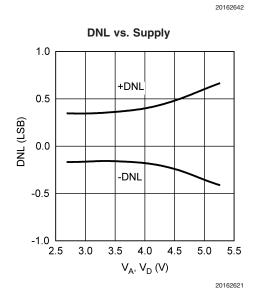

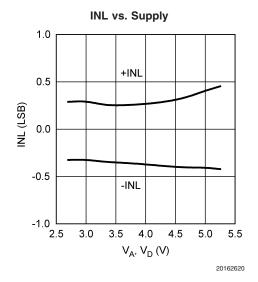

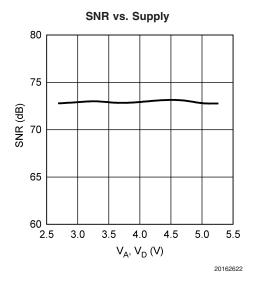

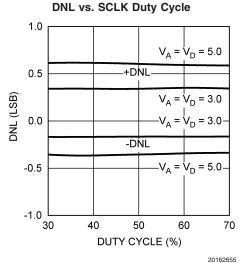

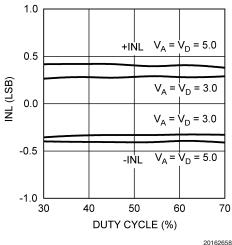

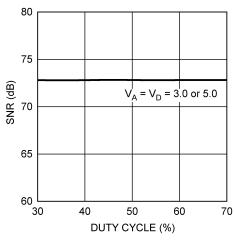

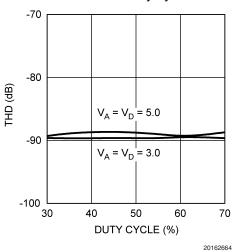

# Typical Performance Characteristics $T_A = +25^{\circ}C$ , $f_{SAMPLE} = 500$ kSPS, $f_{SCLK} = 8$ MHz, $f_{IN} = 40.2$

kHz unless otherwise stated. (Continued)

www.DataSheet4U.com

www.DataSl

# $\textbf{Typical Performance Characteristics} \ T_{\text{A}} = +25^{\circ}\text{C}, \ f_{\text{SAMPLE}} = 500 \ \text{kSPS}, \ f_{\text{SCLK}} = 8 \ \text{MHz}, \ f_{\text{IN}} = 40.2 \ \text{C}$

kHz unless otherwise stated. (Continued)

#### SNR vs. SCLK Duty Cycle

20162661

#### THD vs. SCLK Duty Cycle

#### **ENOB vs. SCLK Duty Cycle**

20162652

#### DNL vs. SCLK

#### INL vs. SCLK

20162659

# Typical Performance Characteristics T<sub>A</sub> = +25°C, f<sub>SAMPLE</sub> = 500 kSPS, f<sub>SCLK</sub> = 8 MHz, f<sub>IN</sub> = 40.2

kHz unless otherwise stated. (Continued)

www.DataSheet4U.com

# $\textbf{Typical Performance Characteristics} \ T_{\text{A}} = +25^{\circ}\text{C}, \ f_{\text{SAMPLE}} = 500 \ \text{kSPS}, \ f_{\text{SCLK}} = 8 \ \text{MHz}, \ f_{\text{IN}} = 40.2 \ \text{C}$

kHz unless otherwise stated. (Continued)

# 1.0 Functional Description

The ADC128S052 is a successive-approximation analog-to-digital converter designed around a charge-redistribution digital-to-analog converter.

#### 1.1 ADC128S052 OPERATION

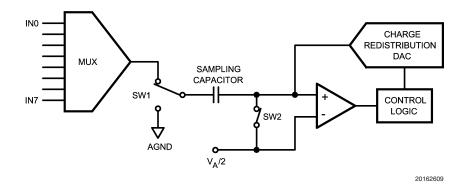

Simplified schematics of the ADC128S052 in both track and hold operation are shown in *Figure 4* and *Figure 5* respectively. In *Figure 4*, the ADC128S052 is in track mode: switch SW1 connects the sampling capacitor to one of eight analog input channels through the multiplexer, and SW2 balances the comparator inputs. The ADC128S052 is in this state for the first three SCLK cycles after  $\overline{\text{CS}}$  is brought low.

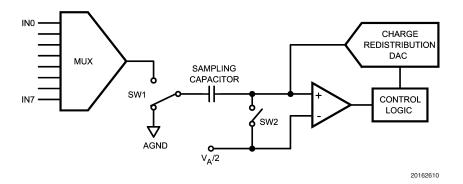

Figure 5 shows the ADC128S052 in hold mode: switch SW1 connects the sampling capacitor to ground, maintaining the sampled voltage, and switch SW2 unbalances the comparator. The control logic then instructs the charge-redistribution DAC to add or subtract fixed amounts of charge to or from the sampling capacitor until the comparator is balanced. When the comparator is balanced, the digital word supplied to the DAC is the digital representation of the analog input voltage. The ADC128S052 is in this state for the last thirteen SCLK cycles after  $\overline{\text{CS}}$  is brought low.

FIGURE 4. ADC128S052 in Track Mode

FIGURE 5. ADC128S052 in Hold Mode

#### 1.2 SERIAL INTERFACE

An operational timing diagram and a serial interface timing diagram for the ADC128S052 are shown in The Timing Diagrams section.  $\overline{CS}$ , chip select, initiates conversions and frames the serial data transfers. SCLK (serial clock) controls both the conversion process and the timing of serial data. DOUT is the serial data output pin, where a conversion result is sent as a serial data stream, MSB first. Data to be written to the ADC128S052's Control Register is placed on DIN, the serial data input pin. New data is written to DIN with each conversion.

A serial frame is initiated on the falling edge of  $\overline{CS}$  and ends on the rising edge of  $\overline{CS}$ . Each frame must contain an integer multiple of 16 rising SCLK edges. The ADC's DOUT pin is in a high impedance state when  $\overline{CS}$  is high and is active when  $\overline{CS}$  is low. Thus,  $\overline{CS}$  acts as an output enable. Similarly, SCLK is internally gated off when  $\overline{CS}$  is brought high.

During the first 3 cycles of SCLK, the ADC is in the track mode, acquiring the input voltage. For the next 13 SCLK cycles the conversion is accomplished and the data is clocked out. SCLK falling edges 1 through 4 clock out leading zeros while falling edges 5 through 16 clock out the conversion result, MSB first. If there is more than one conversion in a frame (continuous conversion mode), the ADC will re-enter the track mode on the falling edge of SCLK after the N\*16th rising edge of SCLK and re-enter the hold/convert mode on the N\*16+4th falling edge of SCLK. "N" is an integer value.

The ADC128S052 enters track mode under three different conditions. In Figure 1,  $\overline{CS}$  goes low with SCLK high and the ADC enters track mode on the first falling edge of SCLK. In the second condition,  $\overline{CS}$  goes low with SCLK low. Under this condition, the ADC automatically enters track mode and the falling edge of  $\overline{CS}$  is seen as the first falling edge of SCLK. In the third condition,  $\overline{CS}$  and SCLK go low simulta-

### 1.0 Functional Description (Continued)

neously and the ADC enters track mode. While there is no timing restriction with respect to the falling edges of  $\overline{\text{CS}}$  and SCLK, see *Figure 3* for setup and hold time requirements for the falling edge of  $\overline{\text{CS}}$  with respect to the rising edge of SCLK.

During each conversion, data is clocked into a control register through the DIN pin on the first 8 rising edges of SCLK

after the fall of  $\overline{CS}$ . The control register is loaded with data indicating the input channel to be converted on the subsequent conversion (see *Tables 1, 2, 3*).

The user does not need to incorporate a power-up delay or dummy conversions as the ADC128S052 is able to acquire the input signal to full resolution in the first conversion immediately following power-up. The first conversion result after power-up will be that of IN0.

**TABLE 1. Control Register Bits**

| ł | DONTC       | DONTC | ADD2  | ADD1  | ADD0  | DONTC | DONTC | DONTC |

|---|-------------|-------|-------|-------|-------|-------|-------|-------|

|   | Bit 7 (MSB) | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

**TABLE 2. Control Register Bit Descriptions**

| Bit #:        | Symbol: | Description                                                           |

|---------------|---------|-----------------------------------------------------------------------|

| 7, 6, 2, 1, 0 | DONTC   | Don't care. The values of these bits do not affect the device.        |

| 5             | ADD2    | These three bits determine which input channel will be sampled and    |

| 4             | ADD1    | converted at the next conversion cycle. The mapping between codes and |

| 3             | ADD0    | channels is shown in <i>Table 3</i> .                                 |

**TABLE 3. Input Channel Selection**

| ADD2 | ADD1 | ADD0 | Input Channel |

|------|------|------|---------------|

| 0    | 0    | 0    | IN0 (Default) |

| 0    | 0    | 1    | IN1           |

| 0    | 1    | 0    | IN2           |

| 0    | 1    | 1    | IN3           |

| 1    | 0    | 0    | IN4           |

| 1    | 0    | 1    | IN5           |

| 1    | 1    | 0    | IN6           |

| 1    | 1    | 1    | IN7           |

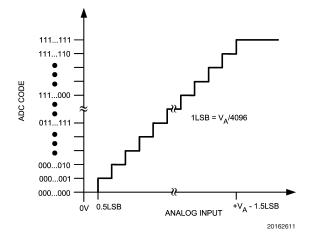

#### 1.3 ADC128S052 TRANSFER FUNCTION

The output format of the ADC128S052 is straight binary. Code transitions occur midway between successive integer LSB values. The LSB width for the ADC128S052 is  $V_A$  / 4096. The ideal transfer characteristic is shown in *Figure 6*. The transition from an output code of 0000 0000 0000 to a code of 0000 0000 0000 0001 is at 1/2 LSB, or a voltage of  $V_A$  / 8192. Other code transitions occur at steps of one LSB.

FIGURE 6. Ideal Transfer Characteristic

#### 1.4 ANALOG INPUTS

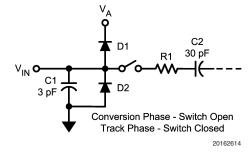

An equivalent circuit for one of the ADC128S052's input channels is shown in  $\it Figure~7$ . Diodes D1 and D2 provide ESD protection for the analog inputs. The operating range for the analog inputs is 0 V to  $V_{A}.$  Going beyond this range will cause the ESD diodes to conduct and result in erratic operation.

The capacitor C1 in *Figure 7* has a typical value of 3 pF and is mainly the package pin capacitance. Resistor R1 is the on resistance of the multiplexer and track / hold switch and is typically 500 ohms. Capacitor C2 is the ADC128S052 sampling capacitor, and is typically 30 pF. The ADC128S052 will deliver best performance when driven by a low-impedance source (less than 100 ohms). This is especially important when using the ADC128S052 to sample dynamic signals. Also important when sampling dynamic signals is a bandpass or low-pass filter which reduces harmonics and noise in the input. These filters are often referred to as anti-aliasing filters.

FIGURE 7. Equivalent Input Circuit

#### 1.5 DIGITAL INPUTS AND OUTPUTS

The ADC128S052's digital inputs (SCLK,  $\overline{CS}$ , and DIN) have an operating range of 0 V to V<sub>A</sub>. They are not prone to latch-up and may be asserted before the digital supply (V<sub>D</sub>) without any risk. The digital output (DOUT) operating range is controlled by V<sub>D</sub>. The output high voltage is V<sub>D</sub> - 0.5V (min) while the output low voltage is 0.4V (max).

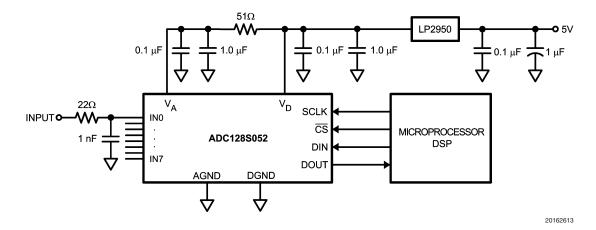

### 2.0 Applications Information

#### 2.1 TYPICAL APPLICATION CIRCUIT

A typical application is shown in *Figure 8*. The split analog and digital supply pins are both powered in this example by the National LP2950 low-dropout voltage regulator. The analog supply is bypassed with a capacitor network located

close to the ADC128S052. The digital supply is separated from the analog supply by an isolation resistor and bypassed with additional capacitors. The ADC128S052 uses the analog supply  $(V_A)$  as its reference voltage, so it is very important that  $V_A$  be kept as clean as possible. Due to the low power requirements of the ADC128S052, it is also possible to use a precision reference as a power supply.

**FIGURE 8. Typical Application Circuit**

#### 2.2 POWER SUPPLY CONSIDERATIONS

There are three major power supply concerns with this product: power supply sequencing, power management, and the effect of digital supply noise on the analog supply.

#### 2.2.1 Power Supply Sequence

The ADC128S052 is a dual-supply device. The two supply pins share ESD resources, so care must be exercised to ensure that the power is applied in the correct sequence. To avoid turning on the ESD diodes, the digital supply  $(V_D)$  cannot exceed the analog supply  $(V_A)$  by more than 300 mV, not even on a transient basis. Therefore,  $V_A$  must ramp up before or concurrently with  $V_D.$

#### 2.2.2 Power Management

The ADC128S052 is fully powered-up whenever  $\overline{\text{CS}}$  is low and fully powered-down whenever  $\overline{\text{CS}}$  is high, with one exception. If operating in continuous conversion mode, the ADC128S052 automatically enters power-down mode between SCLK's 16th falling edge of a conversion and SCLK's 1st falling edge of the subsequent conversion (see *Figure 1*). In continuous conversion mode, the ADC128S052 can perform multiple conversions back to back. Each conversion requires 16 SCLK cycles and the ADC128S052 will perform conversions continuously as long as  $\overline{\text{CS}}$  is held low. Continuous mode offers maximum throughput.

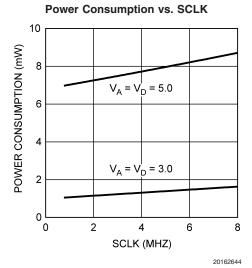

In burst mode, the user may trade off throughput for power consumption by performing fewer conversions per unit time. This means spending more time in power-down mode and less time in normal mode. By utilizing this technique, the user can achieve very low sample rates while still utilizing an SCLK frequency within the electrical specifications. The Power Consumption vs. SCLK curve in the Typical Performance Curves section shows the typical power consumption of the ADC128S052. To calculate the power consumption  $(P_{\rm C})$ , simply multiply the fraction of time spent in the normal mode  $(t_{\rm N})$  by the normal mode power consumption  $(P_{\rm N})$ , and

add the fraction of time spent in shutdown mode  $(t_S)$  multiplied by the shutdown mode power consumption  $(P_S)$  as shown in *Figure 9*.

$$P_C = \frac{t_N}{t_N + t_S} \times P_N + \frac{t_S}{t_N + t_S} \times P_S$$

FIGURE 9. Power Consumption Equation

#### 2.2.3 Power Supply Noise Considerations

The charging of any output load capacitance requires current from the digital supply, V<sub>D</sub>. The current pulses required from the supply to charge the output capacitance will cause voltage variations on the digital supply. If these variations are large enough, they could degrade SNR and SINAD performance of the ADC. Furthermore, if the analog and digital supplies are tied directly together, the noise on the digital supply will be coupled directly into the analog supply, causing greater performance degradation than would noise on the digital supply alone. Similarly, discharging the output capacitance when the digital output goes from a logic high to a logic low will dump current into the die substrate, which is resistive. Load discharge currents will cause "ground bounce" noise in the substrate that will degrade noise performance if that current is large enough. The larger the output capacitance, the more current flows through the die substrate and the greater the noise coupled into the analog channel.

The first solution to keeping digital noise out of the analog supply is to decouple the analog and digital supplies from each other or use separate supplies for them. To keep noise out of the digital supply, keep the output load capacitance as small as practical. If the load capacitance is greater than 50 pF, use a  $100~\Omega$  series resistor at the ADC output, located as

# 2.0 Applications Information

(Continued)

close to the ADC output pin as practical. This will limit the charge and discharge current of the output capacitance and improve noise performance. Since the series resistor and the load capacitor form a low frequency pole, verify signal integrity once the series resistor has been added.

#### 2.3 LAYOUT AND GROUNDING

Capacitive coupling between the noisy digital circuitry and the sensitive analog circuitry can lead to poor performance. The solution is to keep the analog circuitry separated from the digital circuitry and the clock line as short as possible.

Digital circuits create substantial supply and ground current transients. The logic noise generated could have significant impact upon system noise performance. To avoid performance degradation of the ADC128S052 due to supply noise, do not use the same supply for the ADC128S052 that is used for digital logic.

Generally, analog and digital lines should cross each other at  $90^\circ$  to avoid crosstalk. However, to maximize accuracy in

high resolution systems, avoid crossing analog and digital lines altogether. It is important to keep clock lines as short as possible and isolated from ALL other lines, including other digital lines. In addition, the clock line should also be treated as a transmission line and be properly terminated.

The analog input should be isolated from noisy signal traces to avoid coupling of spurious signals into the input. Any external component (e.g., a filter capacitor) connected between the converter's input pins and ground or to the reference input pin and ground should be connected to a very clean point in the ground plane.

We recommend the use of a single, uniform ground plane and the use of split power planes. The power planes should be located within the same board layer. All analog circuitry (input amplifiers, filters, reference components, etc.) should be placed over the analog power plane. All digital circuitry and I/O lines should be placed over the digital power plane. Furthermore, all components in the reference circuitry and the input signal chain that are connected to ground should be connected together with short traces and enter the analog ground plane at a single, quiet point.

### Physical Dimensions inches (millimeters) unless otherwise noted www.DataSheet4U.com В (5.94) 6.4 (16X 0.42) 3.2 (14X 0.65) GAGE PLANE RECOMMENDED LAND PATTERN 0.2 C B A ALL LEAD TIPS -PIN #1 ID SEATING PLANE SEE DETAIL A DETAIL A 1.1 MAX TYP (0.9)16X 0.09-0.20 0.1±0.05 TYP ALL LEAD TIP ⊕ 0.13(M) A B(S) C(S) 14X 0.65 DIMENSIONS ARE IN MILLIMETERS DIMENSIONS IN ( ) FOR REFERENCE ONLY MTC16 (Rev D) 16-Lead TSSOP

16-Lead TSSOP

Order Number ADC128S052CIMT, ADC128S052CIMTX

NS Package Number MTC16

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

For the most current product information visit us at www.national.com.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

### BANNED SUBSTANCE COMPLIANCE

National Semiconductor manufactures products and uses packing materials that meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

Leadfree products are RoHS compliant.

National Semiconductor Americas Customer Support Center

Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560