# Dual-Channel, 0.5 GHz to 32 GHz, Microwave Downconverter

#### **FEATURES**

- Dual-channel, 0.5 GHz to 32 GHz receiver

- Integrated LNA

- Integrated downconversion mixer

- Integrated switch for mixer bypass

- Integrated IF LPF: 8 GHz bandwidth

- Integrated DSA

- ▶ DSA range: 31 dB with 1 dB step

- Single common LO input

- 50 Ω matched input and output

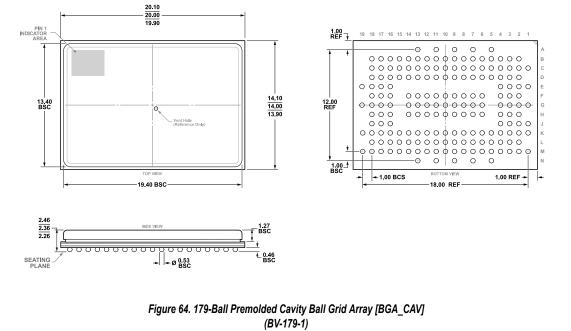

- > 20.00 mm × 14.00 mm, 179-ball CSP BGA

#### **APPLICATIONS**

- Phased array radar receivers

- Satellite communications (satcom) receivers

- ► Electronic warfare

- Electronic test and measurement equipment

- ► Automatic test equipment

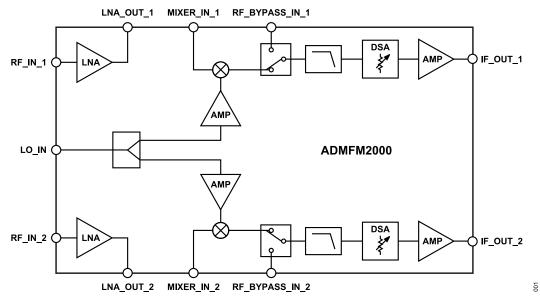

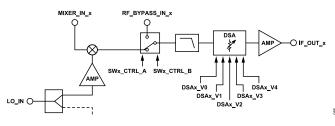

#### FUNCTIONAL BLOCK DIAGRAM

# **GENERAL DESCRIPTION**

The ADMFM2000 is a dual-channel microwave downconverter, with input RF and local oscillator (LO) frequency ranges covering 5 GHz to 32 GHz, with an output intermediate frequency (IF) frequency range from 0.5 GHz to 8 GHz. The downconverting mixer can also be bypassed allowing direct access to the 0.5 to 8 GHz IF path. A common LO input signal is split to feed two separate buffer amplifiers to drive the mixer in each channel. Each down conversion path consists of a low noise amplifier (LNA), a mixer, an IF filter, a digital step attenuator (DSA), and an IF amplifier.

Fabricated using a combination of surface mount and bare die components, the ADMFM2000 provides precise gain adjustment capabilities with low distortion performance. The ADMFM2000 comes in a compact, shielded 20.00 mm × 14.00 mm, 179-ball chip scale package ball grid array (CSP\_BGA) and operates over a temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C.

#### Figure 1. Functional Block Diagram

Information furnished by Analog Devices is believed to be accurate and reliable "as is". However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

# TABLE OF CONTENTS

| 1    |

|------|

| 1    |

| 1    |

| 1    |

| 3    |

| 6    |

| 6    |

| 6    |

| 6    |

| 7    |

| 9    |

| 9    |

| 12   |

| ) 16 |

|      |

| 19   |

| 20   |

|      |

# **REVISION HISTORY**

3/2024—Revision 0: Initial Version

| Theory of Operation              | 21 |

|----------------------------------|----|

| LNA                              |    |

| Mixer                            | 21 |

| LO                               | 21 |

| Switch                           | 21 |

| LPF                              | 22 |

| DSA                              | 22 |

| IF Amplifier                     | 23 |

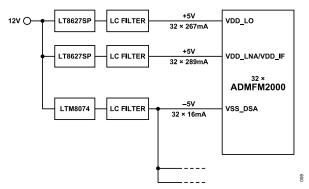

| Applications Information         | 24 |

| Basic Connections                | 24 |

| LNA Mixer Cascaded Performance   | 26 |

| Layout Recommendations           | 27 |

| Vent Hole                        | 27 |

| Power Management Recommendations | 27 |

| Outline Dimensions               | 28 |

| Ordering Guide                   | 28 |

| Evaluation Boards                |    |

|                                  |    |

# SPECIFICATIONS

$\label{eq:VDD_LNA_1 = VDD_LNA_2 = VDD_IF_1 = VDD_IF_2 = VDD_LO_DRIVER_1 = VDD_LO_DRIVER_2 = 5 \text{ V}, \text{ VSS_DSAS} = -5 \text{ V}, \text{ VGG_RFAMP_1 = VGG_RFAMP_2 = VGG_LOAMP_1 = VGG_LOAMP_2 = open, LO_IN power (P_{LO_IN}) = 6 dBm (referenced at the customer evaluation board LO_IN RF connector), and T_A = 25°C, unless otherwise noted.$

| Parameter                           | Test Conditions/Comments                                                                                                                                                              | Min  | Тур  | Max | Unit   |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----|--------|

| OPERATING CONDITIONS                |                                                                                                                                                                                       |      |      |     |        |

| Frequency Range                     |                                                                                                                                                                                       | 0.5  |      | 32  | GHz    |

| LNA Input                           |                                                                                                                                                                                       | 5    |      | 32  | GHz    |

| Mixer Input                         |                                                                                                                                                                                       | 5    |      | 32  | GHz    |

| Direct IF Input                     |                                                                                                                                                                                       | 0.5  |      | 8   | GHz    |

| LNA Output                          |                                                                                                                                                                                       | 5    |      | 32  | GHz    |

| IF Output                           |                                                                                                                                                                                       | 0.5  |      | 8   | GHz    |

| LO Input                            |                                                                                                                                                                                       | 7    |      | 30  | GHz    |

| NA                                  | Input: RF_IN_1 and RF_IN_2 and output: LNA_OUT_1 and LNA_OUT_2                                                                                                                        |      |      |     |        |

| Gain                                | 18 GHz                                                                                                                                                                                |      | 12   |     | dB     |

| Gain Flatness                       | Over any 4 GHz of bandwidth                                                                                                                                                           |      | 1    |     | dB p-p |

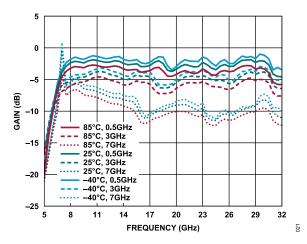

| Gain Variation over Temperature     | -40°C to +85°C                                                                                                                                                                        |      | 1.2  |     | dB     |

| Noise Figure                        | 18 GHz                                                                                                                                                                                |      | 3.5  |     | dB     |

| Input 1 dB Compression Point (P1dB) | 18 GHz                                                                                                                                                                                |      | 2    |     | dBm    |

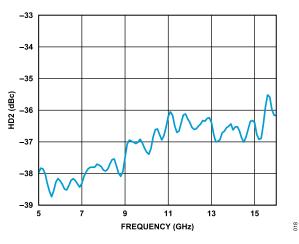

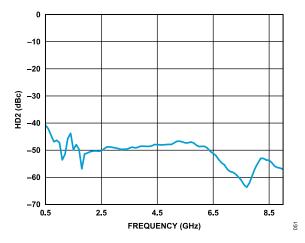

| Second Harmonic (HD2)               | RF_IN_x frequency ( $f_{RF_IN_x}$ ) = 9 GHz, and LNA_OUT_x power ( $P_{LNA_OUT_x}$ ) = -6 dBm                                                                                         |      | -37  |     | dBc    |

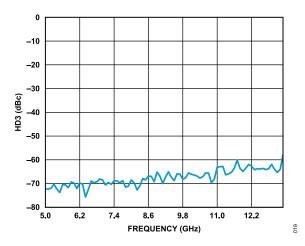

| Third Harmonic (HD3)                | $f_{RF_{IN_x}} = 9 \text{ GHz}$ , and $P_{LNA_{OUT_x}} = -6 \text{ dBm}$                                                                                                              |      | -69  |     | dBc    |

| Input Third-Order Intercept (IP3)   | 18 GHz, 1 MHz tone spacing and an output power ( $P_{OUT}$ ) = -6 dBm per tone                                                                                                        |      | 12   |     | dBm    |

| Input Second-Order Intercept (IP2)  | 9 GHz, 11 MHz tone spacing, P <sub>OUT</sub> = −6 dBm per tone                                                                                                                        |      | 25   |     | dBm    |

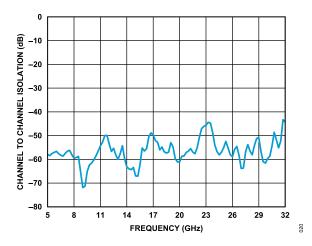

| Channel to Channel Isolation        | $P_{LNA\_OUT\_1}$ to $P_{LNA\_OUT\_2},$ 18 GHz, $P_{RF\_IN\_1}$ = -20 dBm, and RF_IN_2: 50 $\Omega$ termination                                                                       |      | -55  |     | dB     |

| MIXER                               | Input: MIXER_IN_1 and MIXER_IN_2, LO: LO_IN = 6 dBm,<br>SW1_CTRL_A = $-5$ V, SW1_CTRL_B = 0 V, SW2_CTRL_A = 0<br>V, SW2_CTRL_B = $-5$ V, and output: IF_OUT_1 and IF_OUT_2<br>= 3 GHz |      |      |     |        |

| Gain                                | 18 GHz                                                                                                                                                                                |      | -6.3 |     | dB     |

| Gain Flatness                       | Over any 4 GHz of bandwidth                                                                                                                                                           |      | 2    |     | dB p-p |

| Gain Variation over Temperature     | -40°C to +85°C                                                                                                                                                                        |      | 2    |     | dB     |

| DSA Range                           |                                                                                                                                                                                       | 0    |      | 31  | dB     |

| DSA Step Size                       |                                                                                                                                                                                       |      | 1    |     | dB     |

| Noise Figure                        | Single sideband, 18 GHz                                                                                                                                                               |      | 23.5 |     | dB     |

| Input P1dB                          | 18 GHz                                                                                                                                                                                |      | 16.5 |     | dBm    |

| Input IP3                           |                                                                                                                                                                                       | 23.5 |      | dBm |        |

| Input IP2                           | $f1_{MIXER_IN_x}$ = 18 GHz, 11 MHz tone spacing, P <sub>OUT</sub> = -15 dBm per tone                                                                                                  |      | 39.7 |     | dBm    |

| Mixer Isolation                     |                                                                                                                                                                                       |      |      |     |        |

| RF to IF                            | (MIXER_IN_x power ( $P_{MIXER_IN_x}$ ) at 18 GHz) – (IF_OUT_x power ( $P_{IF OUT_x}$ ) at 18 GHz), $P_{MIXER_IN_x} = -10 \text{ dBm}$                                                 |      | 57   |     | dB     |

| LO to RF                            | (P <sub>LO IN</sub> at 18 GHz) – (P <sub>MIXER IN x</sub> at 18 GHz), P <sub>LO IN</sub> = 8 dBm                                                                                      |      | 32   |     | dB     |

| LO to IF                            | (P <sub>LO_IN</sub> at 18 GHz) – (P <sub>IF_OUT_x</sub> at 18 GHz), P <sub>LO_IN</sub> = 8 dBm                                                                                        |      | 77   |     | dB     |

# **SPECIFICATIONS**

# Table 1. Specifications (Continued)

| Parameter                            | Test Conditions/Comments                                                                                                                         | Min   | Тур     | Max   | Unit   |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------|-------|--------|

|                                      |                                                                                                                                                  | (1111 | אני     | IVIAN | Unit   |

| Channel to Channel Isolation         | MIXER_IN_2: 50 $\Omega$ termination, MIXER_IN_1 power<br>(P <sub>MIXER_IN_1</sub> ) = -10 dBm at MIXER_IN_1 frequency (f <sub>MIXER_IN_1</sub> ) |       |         |       |        |

|                                      | $(F_{MXER_IN_1}) = 10 \text{ dBm at MAZEN_IN_1} = 18 \text{ GHz}$ , IF_OUT_1 frequency ( $f_{IF_OUT_1}$ ) = 3.0 GHz                              |       |         |       |        |

| IF to IF                             | $(IF_OUT_1 \text{ power } (P_{IF_OUT_1}) \text{ at } 3 \text{ GHz}) - (IF_OUT_2 \text{ power})$                                                  |       | -80     |       | dB     |

|                                      | (P <sub>IF OUT 2</sub> ) at 3 GHz)                                                                                                               |       |         |       |        |

| DIRECT IF MODE                       | Input: RF_BYPASS_IN_1 and RF_BYPASS_IN_2, output:                                                                                                |       |         |       |        |

|                                      | IF_OUT_1 and IF_OUT_2, SW1_CTRL_A = 0 V, SW1_CTRL_B<br>= -5 V, SW2_CTRL_A = -5 V, and SW2_CTRL_B = 0 V                                           |       |         |       |        |

| Gain                                 | 3.0 GHz                                                                                                                                          |       | 5.0     |       | dB     |

| Gain Flatness                        | 3 GHz ± 1.0 GHz                                                                                                                                  |       | 1.2     |       | dB p-p |

| Gain Variation over Temperature      | -40°C to +85°C                                                                                                                                   |       | 0.6     |       | dB     |

| DSA Range                            |                                                                                                                                                  | 0     |         | 31    | dB     |

| DSA Step Size                        |                                                                                                                                                  |       | 1       |       | dB     |

| Noise Figure                         | 3.0 GHz                                                                                                                                          |       | 12.1    |       | dB     |

| Input P1dB                           | 3.0 GHz                                                                                                                                          |       | 14.5    |       | dBm    |

| HD2                                  | 3.0 GHz, $P_{IF_OUT_x} - P(2 \times f_{IF_OUT_x})$ , and $P_{OUT} = 5 \text{ dBm}$                                                               |       | -50     |       | dBc    |

| HD3                                  | 3.0 GHz, $P_{IF_{OUT_x}} - P(3 \times f_{IF_{OUT_x}})$ , $P_{OUT} = 5 \text{ dBm}$                                                               |       | -77     |       | dBc    |

| Input IP3                            | 3.0 GHz, 1 MHz tone spacing, and P <sub>OUT</sub> = 5 dBm per tone                                                                               |       | 27      |       | dBm    |

| Input IP2                            | 3.0 GHz, 11 MHz tone spacing, and P <sub>OUT</sub> = 5 dBm per tone                                                                              |       | 32.4    |       | dBm    |

| Channel to Channel Isolation         | P <sub>IF_OUT_1</sub> to P <sub>IF_OUT_2</sub> , 3.0 GHz, RF_BYPASS_IN_1 power                                                                   |       | -67     |       | dB     |

|                                      | $(P_{RF_BYPASS_IN_1}) = -20 \text{ dBm}$ , and RF_BYPASS_IN_2: 50 $\Omega$ termination                                                           |       |         |       |        |

| SA SPECIFICATIONS                    |                                                                                                                                                  |       |         |       |        |

| Range                                |                                                                                                                                                  | 0     |         | 31    | dB     |

| Step Size                            | Between any successive attenuation states, 0.5 GHz to 8 GHz                                                                                      |       | 1       |       | dB     |

| Step Error                           | Between any successive attenuation states, 0.5 GHz to 8 GHz                                                                                      |       | ±0.5    |       | dB     |

| Settling Time                        | Minimum attenuation to maximum attenuation, $t_{\mbox{FALL}}$ (90% to 10% $\mbox{RF})$                                                           |       | 38      |       | ns     |

|                                      | Maximum attenuation to minimum attenuation, $t_{\text{RISE}}$ (10% to 90% RF)                                                                    |       | 42      |       | ns     |

|                                      | t <sub>ON</sub> (50% control to 90% RF)                                                                                                          |       | 60      |       | ns     |

|                                      | t <sub>ON</sub> and t <sub>OFF</sub> (50% control to 10% RF)                                                                                     |       | 60      |       | ns     |

| NA MIXER CASCADED                    | Input: RF_IN_1 and RF_IN_2, output: IF_OUT_1 and                                                                                                 |       |         |       |        |

|                                      | IF_OUT_2, 5.5 dB attenuation between LNA_OUT_x and MIXER_IN_x, SW1_CTRL_A = $-5$ V, SW1_CTRL_B = 0 V,                                            |       |         |       |        |

| <b>0</b> ·                           | SW2_CTRL_A = 0 V, and SW2_CTRL_B = -5 V                                                                                                          |       | <u></u> |       |        |

| Gain                                 | $f_{RF_IN_x}$ = 18 GHz and $f_{IF_OUT_x}$ = 3.0 GHz                                                                                              |       | 0.5     | 0.4   | dB     |

| DSA Range                            |                                                                                                                                                  | 0     |         | 31    | dB     |

| DSA Step Size                        |                                                                                                                                                  |       | 1       |       | dB     |

| Noise Figure                         | Single sideband                                                                                                                                  |       | 16.7    |       | dB     |

| Input P1dB                           |                                                                                                                                                  |       | 10.6    |       | dBm    |

| Input IP3                            | 18 GHz, 1 MHz tone spacing, and $P_{OUT} = -15$ dBm per tone                                                                                     |       | 10.2    |       | dBm    |

| Input IP2                            | 9 GHz, 11 MHz tone spacing, and $P_{OUT} = -15$ dBm per tone                                                                                     |       | 24.3    |       | dBm    |

| Channel to Channel Isolation         | $P_{IF\_OUT\_1}$ to $P_{IF\_OUT\_2}$ , 18 GHz, $P_{RF\_IN\_1}$ = -20 dBm, and RF_IN_2: 50 $\Omega$ termination                                   |       | 60      |       | dB     |

| O CHARACTERISTICS                    |                                                                                                                                                  |       |         |       |        |

| LO Drive Level <sup>1</sup>          |                                                                                                                                                  | 4     | 6       | 8     | dBm    |

| OGIC INPUTS                          |                                                                                                                                                  |       |         |       |        |

| SWx_CTRL_x                           | SW1_CTRL_A, SW1_CTRL_B, SW2_CTRL_A, and SW2_CTRL_B                                                                                               |       |         |       |        |

| Input Low Voltage (V <sub>IL</sub> ) |                                                                                                                                                  | -0.2  |         | 0     | V      |

# **SPECIFICATIONS**

#### Table 1. Specifications (Continued)

| Parameter                                               | Test Conditions/Comments                                                                     | Min | Тур  | Max | Unit |

|---------------------------------------------------------|----------------------------------------------------------------------------------------------|-----|------|-----|------|

| Input High Voltage (V <sub>IH</sub> )                   |                                                                                              | -5  |      | -3  | V    |

| DSAx_Vx                                                 | DSA1_V0, DSA1_V1, DSA1_V2, DSA1_V3, DSA1_V4, DSA2_V0, DSA2_V1, DSA2_V2, DSA2_V3, and DSA2_V4 |     |      |     |      |

| V <sub>IL</sub>                                         |                                                                                              | 0   |      | 0.8 | V    |

| V <sub>IH</sub>                                         |                                                                                              | 2   |      | 5   | V    |

| POWER SUPPLIES                                          |                                                                                              |     |      |     |      |

| VDD_LNA_1 and VDD_LNA_2                                 |                                                                                              |     | 5    |     | V    |

| VDD_IF_1 and VDD_IF_2                                   |                                                                                              |     | 5    |     | V    |

| VDD_LO_DRIVER_1 and VDD_LO_DRIVER_2                     |                                                                                              |     | 5    |     | V    |

| VSS_DSAS                                                |                                                                                              |     | -5   |     | V    |

| VDD_LNA_x Current (I <sub>VDD_LNA_x</sub> )             |                                                                                              |     | 66   |     | mA   |

| VDD_IF_x Current (I <sub>VDD_IF_x</sub> )               |                                                                                              |     | 72   |     | mA   |

| VDD_LO_DRIVER_x Current (I <sub>VDD_LO_DRIVER_x</sub> ) |                                                                                              |     | 68   |     | mA   |

| VSS_DSAS Current (I <sub>VSS_DSAS</sub> )               |                                                                                              |     | 12   |     | mA   |

| Total Power Consumption                                 |                                                                                              |     | 2.18 |     | W    |

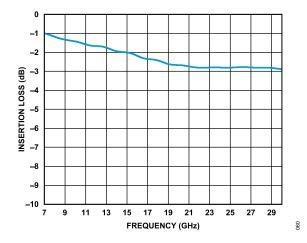

<sup>1</sup> The LO power specification is the power level at the RF connector on the customer evaluation board (LO\_IN). Figure 60 shows a plot of the insertion loss of the LO trace on the customer evaluation board.

# **ABSOLUTE MAXIMUM RATINGS**

#### Table 2. Absolute Maximum Ratings

| Parameter                                                                                         | Rating           |

|---------------------------------------------------------------------------------------------------|------------------|

| Maximum Supply Voltage                                                                            |                  |

| VDD_LNA_1 and VDD_LNA_2                                                                           | 8 V              |

| VDD_IF_1 and VDD_IF_2                                                                             | 7 V              |

| VDD_LO_DRIVER_1, VDD_LO_DRIVER_2                                                                  | 10 V             |

| VSS_DSAS                                                                                          | -7 V             |

| Maximum Input Power                                                                               |                  |

| RF_IN_1 and RF_IN_2                                                                               | 23 dBm           |

| MIXER_IN_1and MIXER_IN_2                                                                          | 21 dBm           |

| RF_BYPASS_IN_1 and RF_BYPASS_IN_2                                                                 | 26 dBm           |

| LO_IN                                                                                             | 24 dBm           |

| Switch Control Inputs                                                                             |                  |

| SW1_CTRL_A, SW1_CTRL_B, SW2_CTRL_A,<br>and SW2_CTRL_B                                             | -7.5 V to +0.5 V |

| DSA Control Inputs                                                                                |                  |

| DSA1_V0, DSA1_V1, DSA1_V2, DSA1_V3,<br>DSA1_V4,DSA2_V0, DSA2_V1, DSA2_V2,<br>DSA2_V3, and DSA2_V4 | 7.5 V            |

| Temperature                                                                                       |                  |

| Operating Range                                                                                   | -40°C to +85°C   |

| Storage Range                                                                                     | -40°C to +150°C  |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

# THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

The Layout Recommendations section details and shows a design that utilizes multiple ground vias to maximize heat dissipation from the device package.

$\theta_{JC}$  is the junction-to-case thermal resistance.

#### Table 3. Thermal Resistance

| Package Type <sup>1</sup> | θ <sub>JC</sub> <sup>2</sup> | Unit |

|---------------------------|------------------------------|------|

| BV-179-1                  | 70                           | °C/W |

<sup>1</sup> Based on simulations with JEDEC standard JESD-51.

$^2~$  The  $\theta_{JC}$  thermal resistance was determined by simulation of the heat transfer from the hottest localized circuit in the package through the ground paddle of the PCB, with the PCB ground paddle held constant at 85°C. The associated power consumption of this circuit is 0.35 W.

# **ELECTROSTATIC DISCHARGE (ESD) RATINGS**

The following ESD information is provided for handling of ESD-sensitive devices in and ESD-protected area only.

Human body model (HBM) per ANSI/ESDA/JEDEC JS-001.

Charged device model (CDM) per ANSI/ESDA/JEDEC JS-002.

# ESD Ratings for ADMFM2000

#### Table 4. ADMFM2000, 179-Ball BGA\_CAV

| ESD Model  | Withstand Threshold (V) | Class |

|------------|-------------------------|-------|

| НВМ        | ±250                    | 1A    |

| CDM        |                         |       |

| RF Pins    | ±175                    | COB   |

| NonRF Pins | ±500                    | C2A   |

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

#### **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

|   |    | ADMFM2000<br>TOP VIEW<br>(Not to Scale) |   |   |   |         |            |         |         |            |            |            |            |         |         |         |    |            |         |         |

|---|----|-----------------------------------------|---|---|---|---------|------------|---------|---------|------------|------------|------------|------------|---------|---------|---------|----|------------|---------|---------|

|   | 1  |                                         | 2 | 3 | 4 | 5       | 6          | 7       | 8       | 9          | 10         | 11         | 12         | 13      | 14      | 15      | 16 | 17         | 18      | 19      |

| A | 7  |                                         |   |   |   | 0       |            | 0       |         | 0          |            | 0          |            | 0       |         |         |    |            |         |         |

| в |    |                                         | Ó | 0 | 0 | 0       | Ó          | Ó       | 0       | 0          | 0          | Ó          | Ó          | Ó       | 0       | Ó       | Ó  | Ó          | Ó       |         |

| с | C  | ì                                       | O | O | 0 | 0       | Ó          | O       | 0       | Ó          | 0          | Ó          | Ó          | Ó       | Ó       | Ó       | Ó  | Ó          | Ó       |         |

| D |    |                                         | O | O | 0 | 0       | Ó          | O       | O       | Ó          | 0          | Ó          | Ó          | Ó       | Ó       | Ó       | Ó  | Ó          | Ó       |         |

| Е | C  | )                                       | O | O | 0 |         |            |         |         |            |            |            |            |         |         |         | Ó  | $^{\circ}$ | O       | 0       |

| F |    |                                         | O | O | 0 |         | $^{\circ}$ | $\odot$ | $\odot$ | $\odot$    | $^{\circ}$ | $^{\circ}$ | $^{\circ}$ | O       | $\odot$ |         | Ó  | $^{\circ}$ | O       |         |

| G | C  | ì                                       | Ó | O | O |         | O          | O       | O       | $\odot$    | O          | O          | Ó          | O       | Ó       |         | Ó  | Ó          | O       | $\odot$ |

| н |    |                                         | Ó | O | O |         | O          | O       | O       | $\odot$    | O          | O          | Ó          | O       | Ó       |         | Ó  | Ó          | O       |         |

| J | C  | ì                                       | Ó | O | O |         |            |         |         |            |            |            |            |         |         |         | Ó  | Ó          | O       |         |

| κ | ζ. | ì                                       | O | 0 | 0 | $\odot$ | $\bigcirc$ | $\odot$ | $\odot$ | $\odot$    | $\odot$    | $\bigcirc$ | $\odot$    | $\odot$ | $\odot$ | $\odot$ | Ó  | $\odot$    | $\odot$ | 0       |

| L |    |                                         | Ó | O | O | O       | O          | O       | O       | $^{\circ}$ | O          | O          | Ó          | O       | Ó       | Ó       | Ó  | Ó          | O       |         |

| м | C  | ì                                       | O | O | 0 | O       | O          | O       | O       | 0          | O          | O          | O          | O       | O       | $\odot$ | Ó  | O          | O       | 0       |

| Ν |    |                                         |   |   |   | O       |            | $\odot$ |         | $\odot$    |            | O          |            | O       |         |         |    |            |         |         |

|   |    |                                         |   |   |   |         |            |         |         |            |            |            |            |         |         |         |    |            |         |         |

Figure 2. BGA Ball Array Configuration (Top View)

|   |     |                 |     |                     |         |               |                     |     | (BAL | TOP VIEW<br>L SIDE DO<br>ot to Scale |           |                    |          |                |                |                |     |              |     |

|---|-----|-----------------|-----|---------------------|---------|---------------|---------------------|-----|------|--------------------------------------|-----------|--------------------|----------|----------------|----------------|----------------|-----|--------------|-----|

|   | 1   | 2               | 3   | 4                   | 5       | 6             | 7                   | 8   | 9    | 10                                   | 11        | 12                 | 13       | 14             | 15             | 16             | 17  | 18           | 19  |

| A |     |                 |     |                     | GND     |               | GND                 |     | GND  |                                      | GND       |                    | GND      |                |                |                |     |              |     |

| в |     | VGG_<br>RFAMP_1 | GND | VDD_<br>LNA_1       | GND     | LNA_<br>OUT_1 | GND                 | GND | GND  | MIXER_<br>IN_1                       | GND       | RF_BYPASS<br>_IN_1 | GND      | GND            | SW1_<br>CTRL_A | SW1_<br>CTRL_B | GND | VSS_<br>DSAS |     |

| с | GND | GND             | GND | GND                 | GND     | GND           | GND                 | GND | GND  | GND                                  | GND       | GND                | GND      | DSA1_V2        | DSA1_V3        | DSA1_V4        | GND | GND          |     |

| D |     | RF_IN_1         | GND | GND                 | GND     | GND           | GND                 | GND | GND  | GND                                  | GND       | GND                | GND      | DSA1_V1        | DSA1_V0        | GND            | GND | VDD_IF_1     |     |

| Е | GND | GND             | GND | VDD_LO_<br>DRIVER_1 |         |               |                     |     |      |                                      |           |                    |          |                |                | GND            | GND | GND          | GND |

| F |     | GND             | GND | VGG_<br>LOAMP_1     |         | GND           | GND                 | GND | GND  | GND                                  | GND       | GND                | GND      | GND            |                | GND            | GND | IF_OUT_1     |     |

| G | GND | GND             | GND | VGG_<br>LOAMP_2     |         | GND           | GND                 | GND | GND  | GND                                  | GND       | GND                | GND      | GND            |                | GND            | GND | GND          | GND |

| н |     | LO_IN           | GND | GND                 |         | GND           | GND                 | GND | GND  | GND                                  | GND       | GND                | GND      | GND            |                | GND            | GND | GND          |     |

| J | GND | GND             | GND | GND                 |         |               |                     |     |      |                                      |           |                    |          |                |                | GND            | GND | VDD_IF_2     |     |

| к | GND | GND             | GND | VGG_<br>RFAMP_2     | GND     | GND           | VDD_LO_<br>DRIVER_2 | GND | GND  | GND                                  | GND       | GND                | GND      | SW2_<br>CTRL_B | GND            | GND            | GND | GND          | GND |

| L |     | RF_IN_2         | GND | GND                 | GND     | GND           | GND                 | GND | GND  | GND                                  | GND       | GND                | GND      | SW2_<br>CTRL_A | DSA2_V3        | DSA2_V4        | GND | IF_OUT_2     |     |

| м | GND | GND             | GND | VDD_<br>LNA_2       | GND     | LNA_<br>OUT_2 | GND                 | GND | GND  | MIXER_<br>IN_2                       | GND       | RF_BYPASS<br>_IN_2 | GND      | DSA2_V0        | DSA2_V1        | DSA2_V2        | GND | GND          | GND |

| N |     |                 |     |                     | GND     |               | GND                 |     | GND  |                                      | GND       |                    | GND      |                |                |                |     |              |     |

|   |     |                 |     |                     |         |               |                     |     |      |                                      |           |                    |          |                |                |                |     |              |     |

|   |     |                 |     |                     | RF I/Os |               | GND                 |     | PWR  |                                      | CTRL +5/0 |                    | CTRL 5/0 |                | NC             |                |     |              |     |

Figure 3. 179-Ball Pin Configuration (Top View)

#### Table 5. Pin Function Descriptions

| Pin No.               | Mnemonic       | Туре   | Description                                               |

|-----------------------|----------------|--------|-----------------------------------------------------------|

| RF Inputs and Outputs |                |        |                                                           |

| D2                    | RF_IN_1        | Input  | Channel 1, RF Input, AC-Coupled, Matched to 50 Ω.         |

| L2                    | RF_IN_2        | Input  | Channel 2, RF Input, AC-Coupled, Matched to 50 Ω.         |

| H2                    | LO_IN          | Input  | LO Input, AC-Coupled, Matched to 50 Ω.                    |

| B6                    | LNA_OUT_1      | Output | Channel 1, LNA Output, AC-Coupled, Matched to 50 Ω.       |

| M6                    | LNA_OUT_2      | Output | Channel 2, LNA Output, AC-Coupled, Matched to 50 $\Omega$ |

| B10                   | MIXER_IN_1     | Input  | Channel 1, Input to Mixer.                                |

| M10                   | MIXER_IN_2     | Input  | Channel 2, Input to Mixer.                                |

| B12                   | RF_BYPASS_IN_1 | Input  | Channel 1, IF Input, AC-Coupled, Matched to 50 Ω.         |

| M12                   | RF_BYPASS_IN_2 | Input  | Channel 2, IF Input, AC-Coupled, Matched to 50 Ω.         |

| F18                   | IF_OUT_1       | Output | Channel 1, IF Output, AC-Coupled, Matched to 50 Ω.        |

| L18                   | IF_OUT_2       | Output | Channel 2, IF Output, AC-Coupled, Matched to 50 $\Omega.$ |

803

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

#### Table 5. Pin Function Descriptions (Continued)

| Pin No.                                                                                                                                                                                                                                                                                                                                                                                          | Mnemonic        | Туре         | Description                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------|------------------------------------------------------------------------------------------------------------------------------|

| Power Supplies                                                                                                                                                                                                                                                                                                                                                                                   |                 |              |                                                                                                                              |

| B2                                                                                                                                                                                                                                                                                                                                                                                               | VGG_RFAMP_1     | Input        | Optional Gain Control Voltage for Channel 1 LNA. This pin is internally self-biased and must normally be left open.          |

| B4                                                                                                                                                                                                                                                                                                                                                                                               | VDD_LNA_1       | Input        | Analog 5.0 V Input for the Channel 1 LNA.                                                                                    |

| B18                                                                                                                                                                                                                                                                                                                                                                                              | VSS_DSAS        | Input        | Analog -5.0 V for DSAs.                                                                                                      |

| D18                                                                                                                                                                                                                                                                                                                                                                                              | VDD_IF_1        | Input        | Analog 5.0 V Input for the Channel 1 IF Amplifier and Channel 1 DSA.                                                         |

| E4                                                                                                                                                                                                                                                                                                                                                                                               | VDD_LO_DRIVER_1 | Input        | Analog 5.0 V Input for the Channel 1 LO Driver.                                                                              |

| F4                                                                                                                                                                                                                                                                                                                                                                                               | VGG_LOAMP_1     | Input        | Optional Gain Control Voltage for Channel 1 LO amplifier. This pin is internally self-biased and must normally be left open. |

| G4                                                                                                                                                                                                                                                                                                                                                                                               | VGG_LOAMP_2     | Input        | Optional Gain Control Voltage for Channel 2 LO Amplifier. This pin is internally self-biased and must normally be left open. |

| J18                                                                                                                                                                                                                                                                                                                                                                                              | VDD_IF_2        | Input        | Analog 5.0 V Input for the Channel 2 IF amplifier and Channel 2 DSA.                                                         |

| K4                                                                                                                                                                                                                                                                                                                                                                                               | VGG_RFAMP_2     | Input        | Optional Gain Control Voltage for the Channel 2 LNA. This pin is internally self-biased and must normally be left open.      |

| K7                                                                                                                                                                                                                                                                                                                                                                                               | VDD_LO_DRIVER_2 | Input        | Analog 5.0 V Input for the Channel 2 LO Driver.                                                                              |

| M4                                                                                                                                                                                                                                                                                                                                                                                               | VDD_LNA_2       | Input        | Analog 5.0 V Input for the Channel 2 LNA.                                                                                    |

| A5, A7, A9, A11, A13, B3, B5, B7 to B9,<br>B11, B13, B14, B17, C1 to C13, C17, C18,<br>D3 to D13, D16, D17, E1 to E3, E16 to E19,<br>F2, F3, F6 to F14, F16, F17, G1 to G3, G6<br>to G14, G16 to G19, H3, H4, H6 to H14,<br>H16 to H18, J1 to J4, J16, J17, K1 to K3,<br>K5, K6, K8 to K13, K15 to K19, L3 to L13,<br>L17, M1 to M3, M5, M7 to M9, M11, M13,<br>M17 to M19, N5, N7, N9, N11, N13 | GND             | Input/Output | Ground.                                                                                                                      |

| Control Signals                                                                                                                                                                                                                                                                                                                                                                                  |                 |              |                                                                                                                              |

| B15                                                                                                                                                                                                                                                                                                                                                                                              | SW1_CTRL_A      | Input        | Channel 1 Switch Control Input A. The SW1_CTRL_A pin must always be kept at a valid logic level (refer to Table 1).          |

| B16                                                                                                                                                                                                                                                                                                                                                                                              | SW1_CTRL_B      | Input        | Channel 1 Switch Control Input B. The SW1_CTRL_B pin must always be kept at a valid logic level (refer to Table 1).          |

| K14                                                                                                                                                                                                                                                                                                                                                                                              | SW2_CTRL_B      | Input        | Channel 2 Switch Control Input B. The SW2_CTRL_A pin must always be kept at a valid logic level (refer to Table 1).          |

| L14                                                                                                                                                                                                                                                                                                                                                                                              | SW2_CTRL_A      | Input        | Channel 2 Switch Control Input A. The SW2_CTRL_B pin must always be kept at a valid logic level (refer to Table 1).          |

| Channel 1 DSA Control Inputs                                                                                                                                                                                                                                                                                                                                                                     |                 |              |                                                                                                                              |

| D15                                                                                                                                                                                                                                                                                                                                                                                              | DSA1_V0         | Input        | Channel 1 DSA Parallel Control Voltage Inputs for the Required Attenuation.                                                  |

| D14                                                                                                                                                                                                                                                                                                                                                                                              | DSA1_V1         | Input        | There is no internal pull-up or pull-down resistor on these pins. Therefore, the                                             |

| C14                                                                                                                                                                                                                                                                                                                                                                                              | DSA1_V2         | Input        | DSA1_Vx pins must always be kept at a valid logic level (5 V $V_{INH}$ or 0 V $V_{INL}$ )                                    |

| C15                                                                                                                                                                                                                                                                                                                                                                                              | DSA1_V3         | Input        | and not be left floating.                                                                                                    |

| C16                                                                                                                                                                                                                                                                                                                                                                                              | DSA1_V4         | Input        |                                                                                                                              |

| Channel 2 DSA Control Inputs                                                                                                                                                                                                                                                                                                                                                                     |                 |              |                                                                                                                              |

| M14                                                                                                                                                                                                                                                                                                                                                                                              | DSA2_V0         | Input        | Channel 2 DSA Parallel Control Voltage Inputs for the Required Attenuation.                                                  |

| M15                                                                                                                                                                                                                                                                                                                                                                                              | DSA2_V1         | Input        | There is no internal pull-up or pull-down resistor on these pins. Therefore, the                                             |

| M16                                                                                                                                                                                                                                                                                                                                                                                              | DSA2_V2         | Input        | DSA2_Vx pins must always be kept at a valid logic level (refer to Table 1) and                                               |

| L15                                                                                                                                                                                                                                                                                                                                                                                              | DSA2_V3         | Input        | not be left floating.                                                                                                        |

| L16                                                                                                                                                                                                                                                                                                                                                                                              | DSA2_V4         | Input        |                                                                                                                              |

# LNA (RF\_IN\_x TO LNA\_OUT\_x)

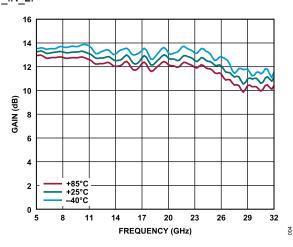

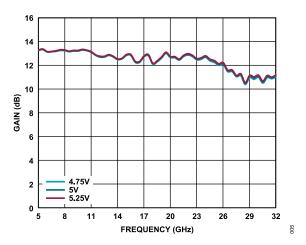

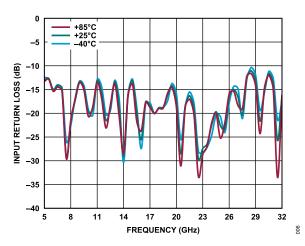

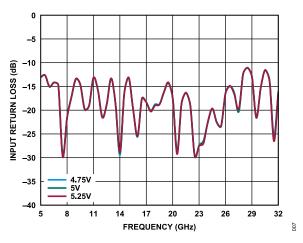

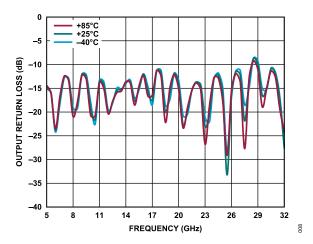

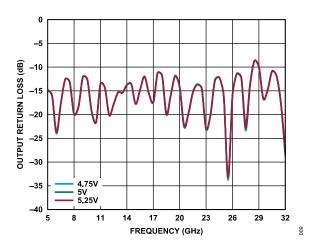

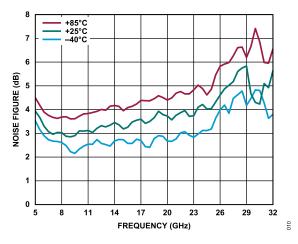

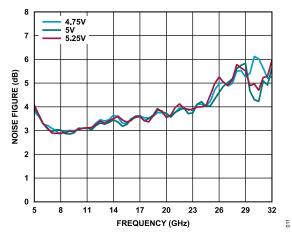

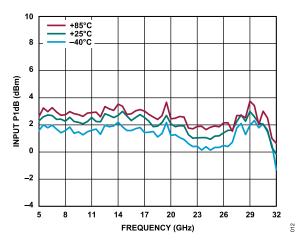

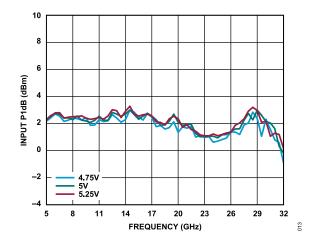

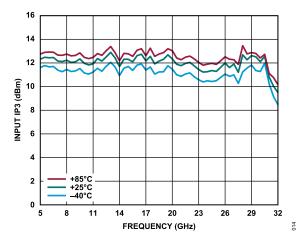

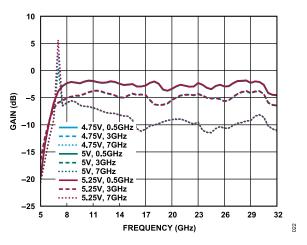

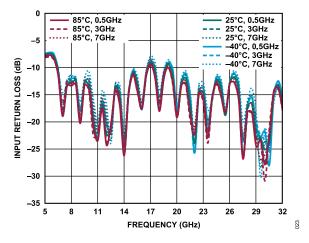

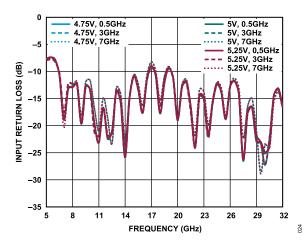

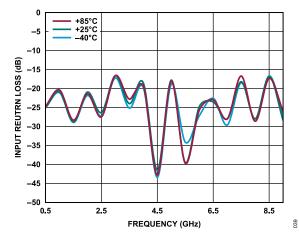

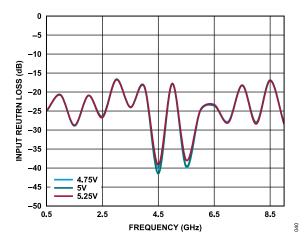

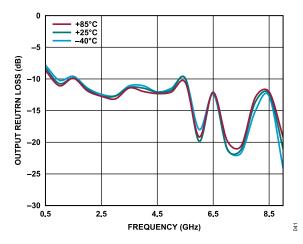

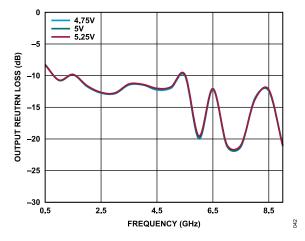

$T_A = 25^{\circ}C$ , VDD\_LNA\_1 = VDD\_LNA\_2 = 5 V, VGG\_RFAMP\_1 = VGG\_RFAMP\_2 = open, RF power ( $P_{RF}$ ) = -20 dBm at RF\_IN\_1 and RF\_IN\_2.

Figure 4. Gain vs. Frequency for Various Temperatures

Figure 5. Gain vs. Frequency for Various Supply Voltages

Figure 6. Input Return Loss vs. Frequency for Various Temperatures

Figure 7. Input Return Loss vs. Frequency for Various Supply Voltages

Figure 8. Output Return Loss vs. Frequency for Various Temperatures

Figure 9. Output Return Loss vs. Frequency for Various Supply Voltages

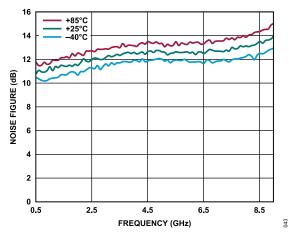

Figure 10. Noise Figure vs. Frequency for Various Temperatures

Figure 11. Noise Figure vs. Frequency for Various Supply Voltages

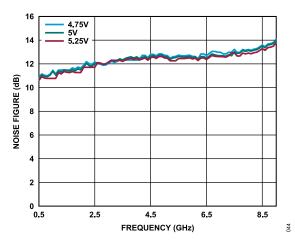

Figure 12. Input P1dB vs. Frequency for Various Temperatures

Figure 13. Input P1dB vs. Frequency for Various Supply Voltages

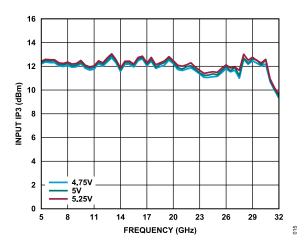

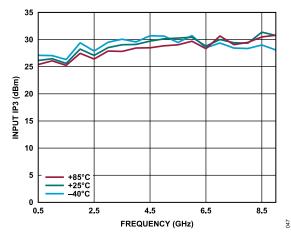

Figure 14. Input IP3 vs. Frequency for Various Temperatures, P<sub>OUT</sub> per Tone = -6 dBm at 1 MHz Tone Spacing

Figure 15. Input IP3 vs. Frequency for Various Supply Voltages,  $P_{OUT}$  per Tone = -6 dBm at 1 MHz Tone Spacing

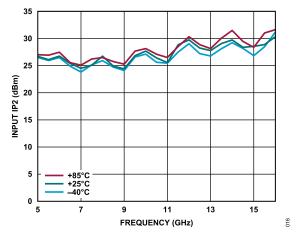

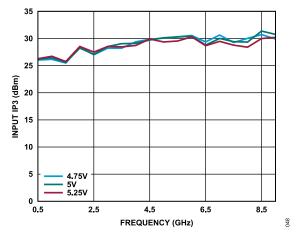

Figure 16. Input IP2 vs. Frequency for Various Temperatures,  $P_{OUT}$  per Tone = -6 dBm at 11 MHz Tone Spacing

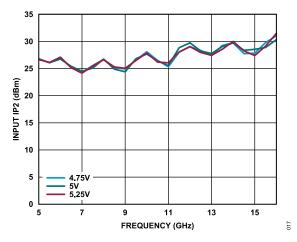

Figure 17. Input IP2 vs. Frequency for Various Supply Voltages, P<sub>OUT</sub> per Tone = -6 dBm at 11 MHz Tone Spacing

Figure 18. HD2 vs. Frequency, P<sub>LNA\_OUT\_x</sub> = -6 dBm

Figure 19. HD3 vs. Frequency, and  $P_{LNA OUT x} = -6 dBm$

Figure 20.  $P_{LNA\_OUT\_1}$  to  $P_{LNA\_OUT\_2}$  Channel to Channel Isolation vs. Frequency,  $P_{RF\_IN\_1} = -20$  dBm and RF\_IN\_2 = 50  $\Omega$  Termination

# MIXER (MIXER\_IN\_x TO IF\_OUT\_x)

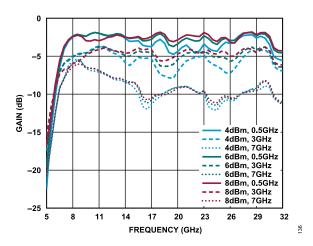

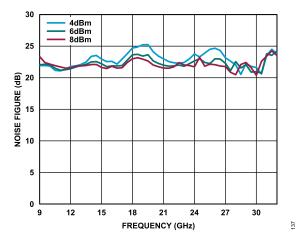

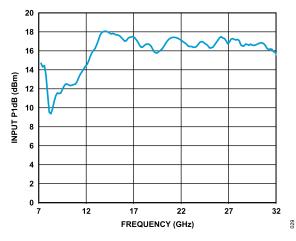

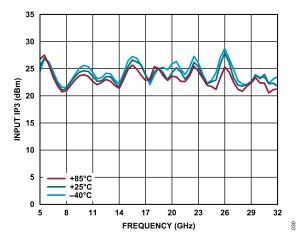

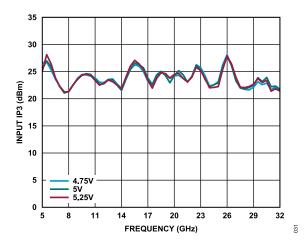

$T_A = 25^{\circ}C$ ,  $VDD_IF_1 = VDD_IF_2 = VDD_LO_DRIVER_1 = VDD_LO_DRIVER_2 = 5 V$ ,  $VSS_DSAS = -5 V$ ,  $VGG_LO_AMP_1 = VGG_LO_AMP_2 = open$ ,  $P_{MIXER_IN_x} = -20 dBm$  at  $MIXER_IN_1$  and  $MIXER_IN_2$ ,  $f_{IF} = 3.0 GHz$  at  $IF_OUT_1$  and  $IF_OUT_2$ , and  $P_{LO_IN} = 6 dBm$  referenced at the characterization and customer evaluation board LO\_IN RF connector.

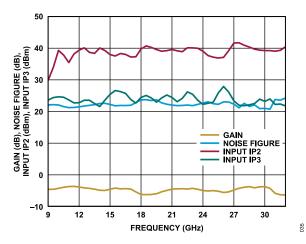

Figure 21. Gain, Noise Figure, Input IP2, and Input IP3 vs. Frequency at an IF Frequency = 3.0 GHz

Figure 22. Gain vs. Frequency for Various Temperatures and IF Frequencies

Figure 23. Gain vs. Frequency for Various Supply Voltages and IF Frequencies

Figure 24. Gain vs. Frequency for Various LO Drive Power Level and Frequencies

Figure 25. Input Return Loss vs. Frequency for Various Temperatures and IF Frequencies

Figure 26. Input Return Loss vs. Frequency for Various Supply Voltages and IF Frequencies

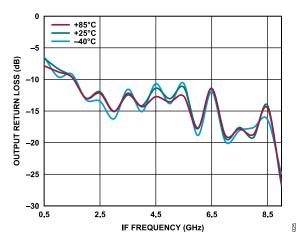

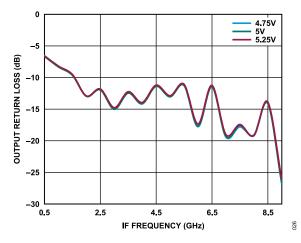

Figure 27. Output Return Loss vs. IF Frequency for Various Temperatures for a Fixed RF Input (18 GHz)

Figure 28. Output Return Loss vs. IF Frequency for Various Supply Voltages and a Fixed RF Input (18 GHz)

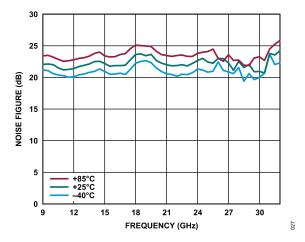

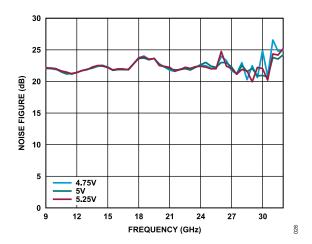

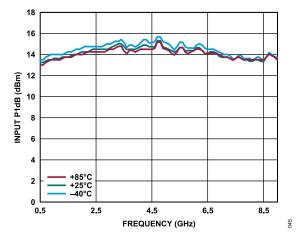

Figure 29. Noise Figure vs. Frequency for Various Temperatures at an IF Frequency = 3.0 GHz

Figure 30. Noise Figure vs. Frequency for Various Supply Voltages at an IF Frequency = 3.0 GHz

Figure 31. Noise Figure vs. Frequency for Various LO Drive Power Levels

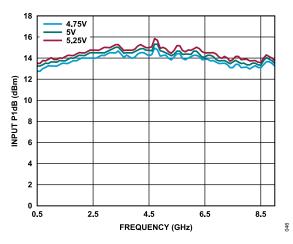

Figure 32. Input P1dB vs. Frequency at IF Frequency = 3.0 GHz

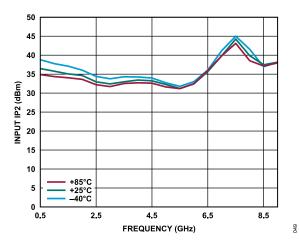

Figure 33. Input IP3 vs. Frequency for Various Temperatures at an IF Frequency = 3.0 GHz,  $P_{OUT}$  per Tone = -15 dBm at 1 MHz Tone Spacing

Figure 34. Input IP3 vs. Frequency for Various Supply Voltages at an IF Frequency = 3.0 GHz,  $P_{OUT}$  per Tone = -15 dBm at 1 MHz Tone Spacing

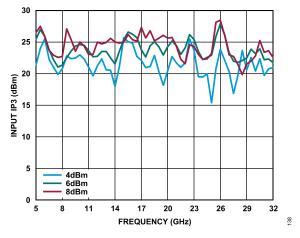

Figure 35. Input IP3 vs. Frequency for Various LO Drive Power Levels

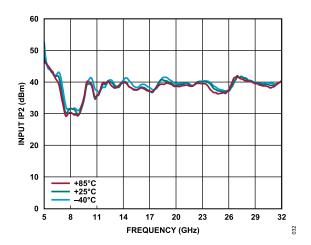

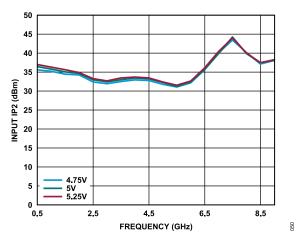

Figure 36. Input IP2 vs. Frequency for Various Temperatures at an IF Frequency = 3.0 GHz,  $P_{OUT}$  per Tone = -15 dBm at 11 MHz Tone Spacing

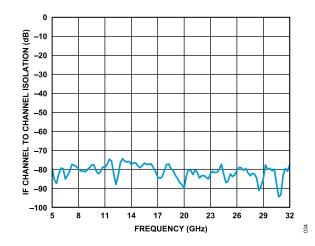

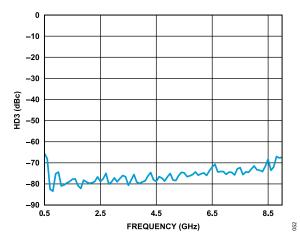

Figure 38. IF Channel to Channel Isolation vs. Frequency,  $(P_{IF\_OUT\_1} \text{ at } 3 \text{ GHz}) - (P_{IF\_OUT\_2} \text{ at } 3 \text{ GHz})$ , MIXER\_IN\_2: 50  $\Omega$  termination,  $P_{MIXER\_IN\_1} = -10 \text{ dBm}$ ,  $f_{IF\_OUT\_1} = 3.0 \text{ GHz}$

# DIRECT IF (RF\_BYPASS\_IN\_x TO IF\_OUT\_x)

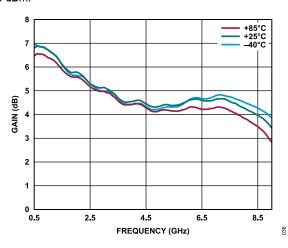

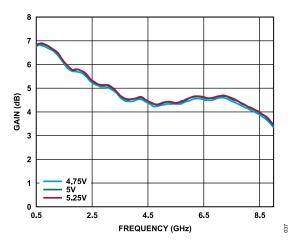

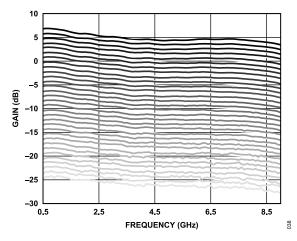

$T_A = 25^{\circ}C$ ,  $VDD_IF_1 = VDD_IF_2 = 5 V$ ,  $VSS_DSAS = -5 V$ ,  $P_{RF_BYPASS_IN_1} = -20 dBm$ , and  $RF_BYPASS_IN_2$  power ( $P_{RF_BYPASS_IN_2}$ ) = -20 dBm.

Figure 39. Gain vs. Frequency for Various Temperatures

Figure 40. Gain vs. Frequency for Various Supply Voltages

Figure 41. Gain vs. Frequency for Various DSA Settings

Figure 42. Input Return Loss vs. Frequency for Various Temperatures

Figure 43. Input Return Loss vs. Frequency for Various Supply Voltages

Figure 44. Output Return Loss vs. Frequency for Various Temperatures

Figure 45. Output Return Loss vs. Frequency for Various Supply Voltages

Figure 46. Noise Figure vs. Frequency for Various Temperatures

Figure 47. Noise Figure vs. Frequency for Various Supply Voltages

Figure 48. Input P1dB vs. Frequency for Various Temperatures

Figure 49. Input P1dB vs. Frequency for Various Supply Voltages

Figure 50. Input IP3 vs. Frequency for Various Temperatures, P<sub>OUT</sub> per Tone = 5 dBm at 1 MHz Tone Spacing

Figure 51. Input IP3 vs. Frequency for Various Supply Voltages, P<sub>OUT</sub> per Tone = 5 dBm at 1 MHz Tone Spacing

Figure 52. Input IP2 vs. Frequency for Various Temperatures, P<sub>OUT</sub> per Tone = 5 dBm at 11 MHz Tone Spacing

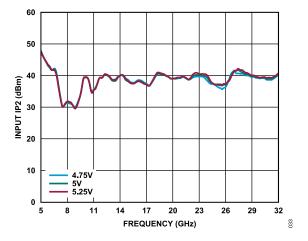

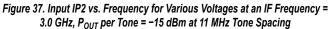

Figure 53. Input IP2 vs. Frequency for Various Supply Voltages,  $P_{OUT}$  per Tone = 5 dBm at 11 MHz Tone Spacing

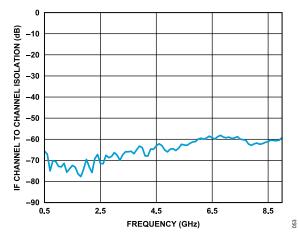

Figure 54. HD2 vs. Frequency, P<sub>OUT</sub> = 5 dBm

Figure 55. HD3 vs. Frequency, P<sub>OUT</sub> = 5 dBm

Figure 56. IF Channel to Channel Isolation vs. Frequency

# LNA-MIXER CASCADED (RF\_IN\_x TO IF\_OUT\_x)

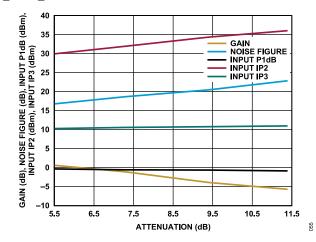

$T_A = 25^{\circ}C$ ,  $VDD_IF_1 = VDD_IF_2 = 5 V$ ,  $VSS_DSAS = -5 V$ ,  $P_{RF_IN_x} = -20 dBm$ , 5.5 dB attenuation between LNA\_OUT\_x and MIXER\_IN, SW1\_CTRL\_A = -5 V, SW1\_CTRL\_B = 0 V, SW2\_CTRL\_A = 0 V, and SW2\_CTRL\_B = -5 V.

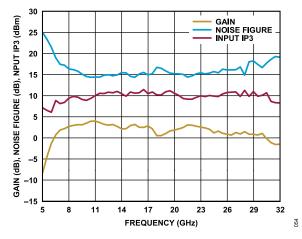

Figure 57. Gain, Noise Figure, and Input IP3 vs. Frequency at an IF Frequency = 3.0 GHz, P<sub>OUT</sub> per Tone = -15 dBm

Figure 58. Gain, Noise Figure, Input P1dB, Input IP2, and Input IP3 vs. Attenuation between LNA\_OUT\_x and MIXER\_IN\_x at an RF Frequency = 18 GHz and IF Frequency = 3.0 GHz, P<sub>OUT</sub> per Tone = -15 dBm

### SPURIOUS PERFORMANCE

Mixer spurious products are measured in dB from the IF output power level. Spurious values are (N × LO) – (M × RF). N/A means not applicable.

#### M × N Spurious Outputs, IF = 1 GHz

RF input frequency = 10 GHz, RF input power at mixer input = -20 dBm, LO frequency = 11 GHz, and the LO input power = 6 dBm.

$M \times N$  spurs other than the RF input and LO input signal at the IF output are more than 51 dB down from the main IF output at 1 GHz. Over 8 GHz, spurs are rejected significantly by the low-pass filter (LPF) on the signal path.

#### Table 6. M x N Spurious at Mixer Mode<sup>1</sup>

|        |   | N × LO |        |        |        |        |        |

|--------|---|--------|--------|--------|--------|--------|--------|

|        |   | 0      | 1      | 2      | 3      | 4      | 5      |

|        | 0 | N/A    | -10.1  | +57.4  | +69.2  | +70.5  | N/A    |

|        | 1 | +3.8   | 0.0    | +51.2  | +87.0  | +83.8  | +94.4  |

| M × RF | 2 | +87.6  | +61.6  | +56.7  | +100.2 | +108.6 | +104.7 |

|        | 3 | +108.9 | +111.6 | +95.6  | +109.0 | +114.0 | +110.5 |

|        | 4 | +105.5 | +108.6 | +112.6 | +117.9 | +100.9 | +114.0 |

|        | 5 | +102.5 | +103.9 | +112.2 | +112.2 | +107.5 | +114.7 |

<sup>1</sup> Level (dB) refers to an IF output = -26 dBm at 1 GHz.

# THEORY OF OPERATION

The ADMFM2000 is a dual-channel, microwave downconverter. Each downconversion path consists of an LNA, mixer, filter, DSA, IF amplifier, and a single LO input that drives both mixers.

Figure 59. ADMFM2000 Simplified Block Diagram

### LNA

The ADMFM2000 has a wideband LNA in each channel that operates between 5 GHz and 32 GHz. The LNAs are self-biased with a required single 5 V supply. Inputs and outputs are internally matched to 50  $\Omega$  and have internal DC blocking capacitors.

Each LNA also has gain control capability using the

VGG\_RFAMP\_1 and VGG\_RFAMP\_2 pins corresponding to each channel. These pins are internally self-biased and must normally be left open.

# MIXER

The ADMFM2000 has a double-balanced mixer in each channel. These mixers down convert the RF from 5 GHz and 32 GHz to a corresponding IF of 0.5 GHz and 8 GHz. These mixers are passive devices and require no external biasing components or RF matching circuitry. The mixers in the ADMFM2000 operate well with a LO drive level of 6 dBm at the LO input pin.

# LO

A common LO input operates from 7 GHz to 30 GHz and is split to feed separate buffer amplifiers for each channel. These amplifiers drive separate mixers in each channel. The buffer amplifiers also have gain control using the VGG\_LOAMP\_1 and the VGG\_LOAMP\_2 pins, one for each channel. The VGG\_LOAMP\_x pins are internally self-biased and must normally be left open. The typical LO drive level at the LO input pin is 6 dBm.

# SWITCH

The ADMFM2000 has a broadband SPDT RF switch in each channel that can be used to bypass the mixer. The SPDTs require negative control voltages at the control pins (SW\_CHx\_CTRL\_A and SW\_CHx\_CTRL\_B, x = 1 or 2). Depending on the logic level applied to those control pins, the IF path is either connected to the mixer or to the RF\_BYPASS\_IN pin (see Figure 59 and Table 7). The required logic level for operating mode on Channel 2 is opposite to the required logic level on Channel 1.

#### Table 7. Switch Control Truth Table for SW1\_CTRL\_A, SW1\_CTRL\_B, SW2\_CTRL\_A, and SW2\_CLRL\_B

| Digital Control Inputs <sup>1</sup> |            |                  | RF Paths         |  |  |

|-------------------------------------|------------|------------------|------------------|--|--|

| SWx_CTRL_A                          | SWx_CTRL_B | Channel 1 Status | Channel 2 Status |  |  |

| High                                | Low        | Direct IF mode   | Mixer mode       |  |  |

| Low                                 | High       | Mixer mode       | Direct IF mode   |  |  |

<sup>1</sup> Refer to logic input in Table 1 for the logic level high and low detailed in Table 7.

# THEORY OF OPERATION

# LPF

A LPF with a bandwidth of 8 GHz after the switch rejects harmonics and other spurs generated from the mixer or induced on the RF\_BYPASS\_IN\_1 and RF\_BYPASS\_IN\_2 input pins when in direct IF mode of operation.

# DSA

The DSA after the LPF provides a 31 dB of gain control range with 1 dB step size. The DSA attenuation is set by the logic levels on the DSAx\_V0 to DSAx\_V4 pins (see Figure 3 and Table 8). All pins at high sets the minimum attenuation level and all pins at low sets the maximum attenuation. Note that the DSA requires a negative supply of -5 V on the VSS\_DSAS pin, and that the logic controls on these pins are positive (0 V and 5 V).

| DSAx_V4 | DSAx_V3 | DSAx_V2 | DSAx_V1 | DSAx_V0 | Attenuation State (dB) |

|---------|---------|---------|---------|---------|------------------------|

| High    | High    | High    | High    | High    | 0 (reference)          |

| High    | High    | High    | High    | Low     | 1                      |

| High    | High    | High    | Low     | High    | 2                      |

| High    | High    | High    | Low     | Low     | 3                      |

| High    | High    | Low     | High    | High    | 4                      |

| High    | High    | Low     | High    | Low     | 5                      |

| High    | High    | Low     | Low     | High    | 6                      |

| High    | High    | Low     | Low     | Low     | 7                      |

| High    | Low     | High    | High    | High    | 8                      |

| High    | Low     | High    | High    | Low     | 9                      |

| High    | Low     | High    | Low     | High    | 10                     |

| High    | Low     | High    | Low     | Low     | 11                     |

| High    | Low     | Low     | High    | High    | 12                     |

| High    | Low     | Low     | High    | Low     | 13                     |

| High    | Low     | Low     | Low     | High    | 14                     |

| High    | Low     | High    | Low     | Low     | 15                     |

| Low     | High    | High    | High    | High    | 16                     |

| Low     | High    | High    | High    | Low     | 17                     |

| Low     | High    | High    | Low     | High    | 18                     |

| Low     | High    | High    | Low     | Low     | 19                     |

| Low     | High    | Low     | High    | High    | 20                     |

| Low     | High    | Low     | High    | Low     | 21                     |

| Low     | High    | Low     | Low     | High    | 22                     |

| Low     | High    | Low     | Low     | Low     | 23                     |

| Low     | Low     | High    | High    | High    | 24                     |

| Low     | Low     | High    | High    | Low     | 25                     |

| Low     | Low     | High    | Low     | High    | 26                     |

| Low     | Low     | High    | Low     | Low     | 27                     |

| Low     | Low     | Low     | High    | High    | 28                     |

| Low     | Low     | Low     | High    | Low     | 29                     |

| Low     | Low     | Low     | Low     | High    | 30                     |

| Low     | Low     | Low     | Low     | Low     | 31                     |

<sup>1</sup> Refer to the logic input in Table 1 for the logic level high and low detailed in Table 8.

# **THEORY OF OPERATION**

#### **IF AMPLIFIER**

A IF amplifier follows the DSA. The amplifier requires a 5 V supply voltage and it features an outputs that is internally matched to 50  $\Omega.$

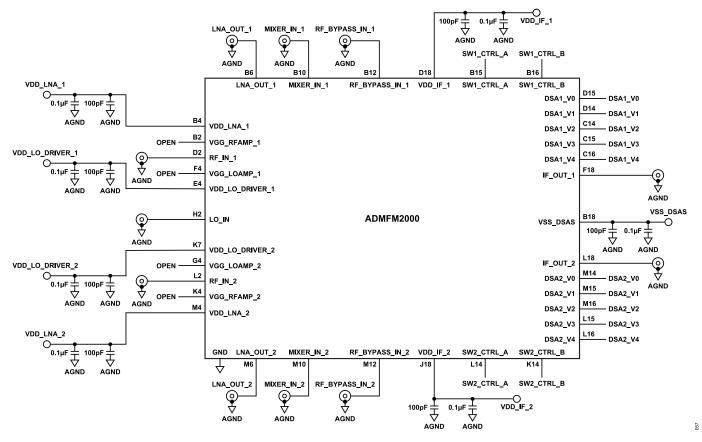

### **BASIC CONNECTIONS**

The basic connections for operating the ADMFM2000 are shown in Figure 61. Table 9 details how to connect each pin. Figure 61 represents the circuit that was used to characterize the ADMFM2000. Note that the specified LO power used during characterization is referenced to the power level at the RF connector and not the power at the LO\_IN pin. Figure 60 shows a plot of the insertion loss between the RF connector and the LO IN pin.

Figure 60. Insertion Loss vs. Frequency of LO Trace on the ADMFM2000 Characterization Board

Figure 61. Basic Connections

#### Table 9. Connection Descriptions

| Functional Blocks                                       | Pin No.                  | Mnemonic                                                 | Description                                                                                                                                                                                                                                                                 | Basic Connection                                                                                    |

|---------------------------------------------------------|--------------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| 5 V Supply Voltage<br>for LNA, DSA, and IF<br>Amplifier | B4, D18, E4, J18, K7, M4 | VDD_LNA_1,<br>VDD_IF_1,<br>VDD_LO_DRIVER_1,<br>VDD_IF_2, | Analog 5.0 V supply voltage for Channel 1 LNA, analog 5.0 V supply voltage for Channel 1 IF amplifier and Channel 1 DSA, analog 5.0 V supply voltage for Channel 1 LO driver, analog 5.0 V supply voltage for Channel 2 IF amplifier and Channel 1 DSA, analog 5.0 V supply | Decouple thes pins using 10 pF and 0.1 µF capacitors to ground. Locate the decoupling capacitors as |

#### Table 9. Connection Descriptions (Continued)

| Functional Blocks              | Pin No.                                                                                                                                                                                                                                                                                                                                                                                                           | Mnemonic                                                    | Description                                                                                                                                           | Basic Connection                                                                                                                      |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

|                                |                                                                                                                                                                                                                                                                                                                                                                                                                   | VDD_LO_DRIVER_2,<br>VDD_LNA_2                               | voltage for Channel 2 LO driver, analog 5.0 V supply<br>voltage for Channel 2 LNA.                                                                    | close as possible to the pins.                                                                                                        |