# Digital Controller for Isolated Power Supply with PMBus Interface

Data Sheet ADP1052

#### **FEATURES**

Peak data telemetry recording

High speed input voltage feedforward control

6 pulse-width modulation (PWM) logic outputs with 625 ps

resolution

Switching frequency: 49 kHz to 625 kHz

Frequency synchronization as master and slave device

Multiple energy saving modes

Adaptive dead time compensation for efficiency optimization

Low power consumption: 100 mW typical

Direct parallel control for power supplies without OR'ing devices

**Accurate droop current share**

**Prebias startup**

**Reverse current protection**

**Conditional overvoltage protection**

**Extensive fault detection and protection**

**PMBus compliant**

Graphical user interface (GUI) for ease of programming

On-board EEPROM for programming and data storage

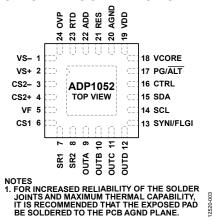

Available in a 24-lead, 4 mm × 4 mm LFCSP

-40°C to +125°C operating temperature

#### **APPLICATIONS**

infrastructure

High density isolated dc-to-dc power supplies

Intermediate bus converters

High availability parallel power systems

Server, storage, industrial, networking, and communications

#### **GENERAL DESCRIPTION**

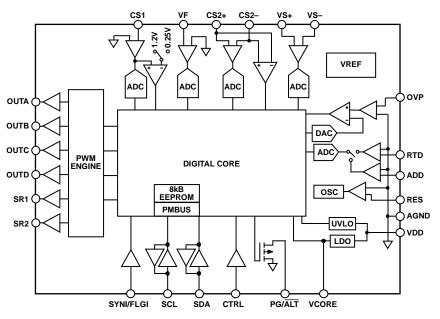

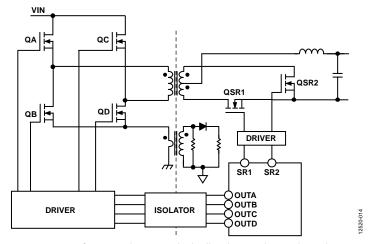

The ADP1052 is an advanced digital controller with a PMBus™ interface targeting high density, high efficiency, dc-to-dc power conversion. This controller implements voltage mode control with high speed, input line feedforward for enhanced transient and improved noise performance. The ADP1052 has six programmable pulse-width modulation (PWM) outputs capable of controlling most high efficiency power supply topologies, with added control of synchronous rectification (SR). The device includes adaptive dead time compensation to improve efficiency over the load range, and programmable light load mode operation, combined with low power consumption, to reduce system standby power losses.

The ADP1052 implements several features to enable a robust system of parallel and redundant operation for customers that require high availability or parallel connection. The device provides synchronization, reverse current protection, prebias startup, accurate current sharing between power supplies, and conditional overvoltage techniques to identify and safely shut down an erroneous power supply in parallel operation mode.

The ADP1052 is based on flexible state machine architecture and is programmed using an intuitive GUI. The easy to use interface reduces design cycle time and results in a robust, hardware coded system loaded into the built-in EEPROM. The small size (4 mm  $\times$  4 mm) LFCSP package makes the ADP1052 ideal for ultracompact, isolated dc-to-dc power module or embedded power designs.

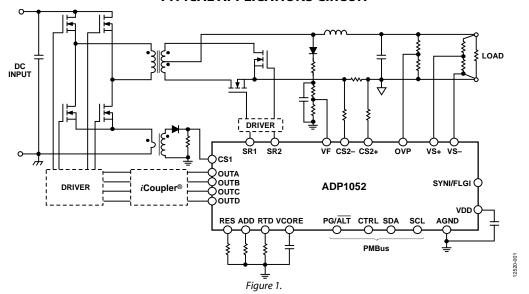

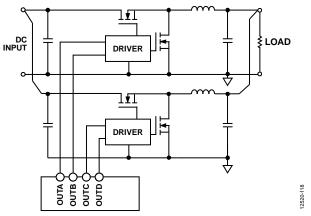

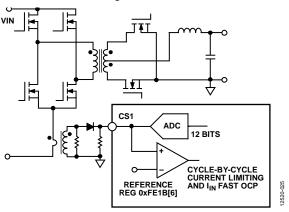

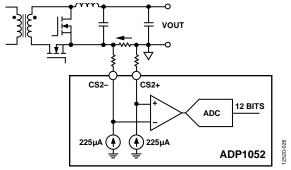

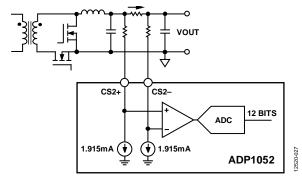

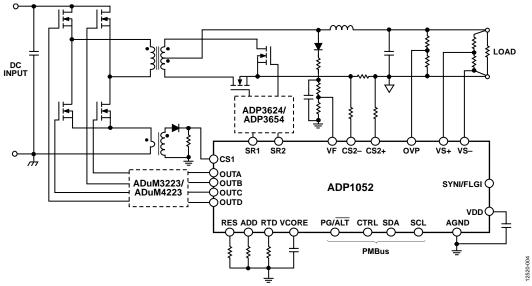

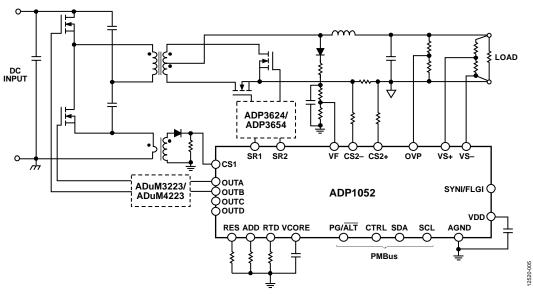

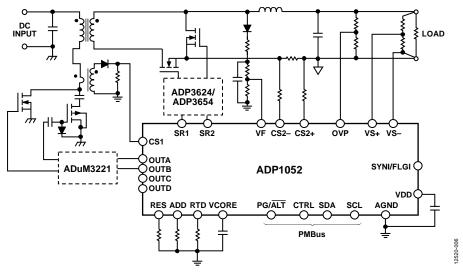

#### TYPICAL APPLICATIONS CIRCUIT

Rev. A Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

# **ADP1052\* PRODUCT PAGE QUICK LINKS**

Last Content Update: 02/23/2017

# COMPARABLE PARTS 🖵

View a parametric search of comparable parts.

## **DOCUMENTATION**

#### **Data Sheet**

ADP1052: Digital Controller for Isolated Power Supply with PMBus Interface Data Sheet

# SOFTWARE AND SYSTEMS REQUIREMENTS $\Box$

ADP1050/ADP1051/ADP1052 Software

### DESIGN RESOURCES 🖳

- ADP1052 Material Declaration

- PCN-PDN Information

- · Quality And Reliability

- · Symbols and Footprints

### **DISCUSSIONS**

View all ADP1052 EngineerZone Discussions.

### SAMPLE AND BUY

Visit the product page to see pricing options.

### TECHNICAL SUPPORT 🖳

Submit a technical question or find your regional support number.

## DOCUMENT FEEDBACK 🖳

Submit feedback for this data sheet.

# **ADP1052**

# **TABLE OF CONTENTS**

| Features                                              | Duty Cycle Reading                         | 34 |

|-------------------------------------------------------|--------------------------------------------|----|

| Applications1                                         | Switching Frequency Reading                | 34 |

| General Description1                                  | Temperature Reading                        | 34 |

| Typical Applications Circuit1                         | Temperature Linearization Scheme           | 35 |

| Revision History3                                     | PMBus Protection Commands                  | 35 |

| Specifications4                                       | Manufacturer Specific Protection Commands  | 37 |

| Absolute Maximum Ratings9                             | Manufacturer Specific Protection Responses | 39 |

| Thermal Resistance9                                   | Peak Data Telemetry                        | 40 |

| Soldering9                                            | Power Supply Calibration and Trim          | 41 |

| ESD Caution9                                          | I <sub>IN</sub> Trim (CS1 Trim)            | 41 |

| Pin Configuration and Function Descriptions10         | I <sub>OUT</sub> Trim (CS2 Trim)           | 41 |

| Typical Performance Characteristics12                 | V <sub>OUT</sub> Trim (VS Trim)            | 41 |

| Theory of Operation14                                 | V <sub>IN</sub> Trim (VF Gain Trim)        | 42 |

| PWM Outputs (OUTA, OUTB, OUTC, OUTD, SR1, and         | RTD and OTP Trim                           | 42 |

| SR2)                                                  | Applications Configurations                | 43 |

| Synchronous Rectification                             | Layout Guidelines                          |    |

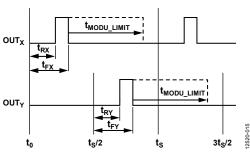

| PWM Modulation Limit and 180° Phase Shift16           | CS1 Pin                                    | 45 |

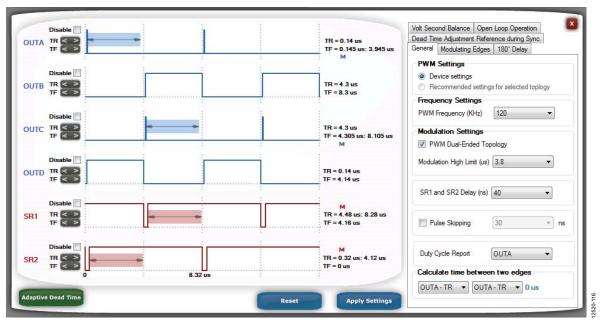

| Adaptive Dead Time Compensation (ADTC)17              | CS2+ and CS2- Pins                         | 45 |

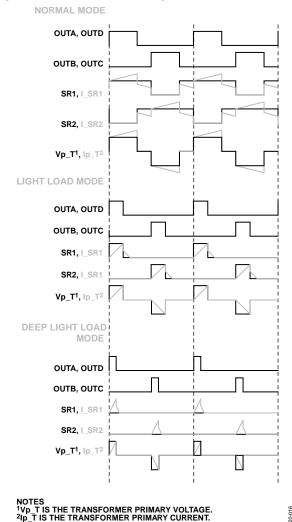

| Light Load Mode and Deep Light Load Mode17            | VS+ and VS- Pins                           | 45 |

| Frequency Synchronization                             | OUTA to OUTD, SR1 AND SR2 PWM Outputs      |    |

| Output Voltage Sense and Adjustment20                 | VDD Pin                                    |    |

| Digital Compensator21                                 | VCORE Pin                                  | 45 |

| Closed-Loop Input, Voltage Feedforward Control and VF | RES Pin                                    | 45 |

| Sense                                                 | SDA and SCL Pin                            |    |

| Open-Loop Input, VF Operation23                       | Exposed Pad                                |    |

| Open-Loop Operation                                   | RTD Pin                                    |    |

| Current Sense                                         | AGND Pin                                   |    |

| Soft Start and Shutdown                               | PMBus/I <sup>2</sup> C Communication       |    |

| Volt-Second Balance Control27                         | PMBus Features                             |    |

| Constant Current Mode                                 | Overview                                   |    |

| Pulse Skipping28                                      | PMBus/I <sup>2</sup> C Address             |    |

| Prebias Startup                                       | Data Transfer                              |    |

| Output Voltage Drooping Control28                     | General Call Support                       |    |

| VDD and VCORE29                                       | 10-Bit Addressing                          |    |

| Chip Password29                                       | Fast Mode                                  |    |

| Power Monitoring, Flags, and Fault Responses          | Fault Conditions                           |    |

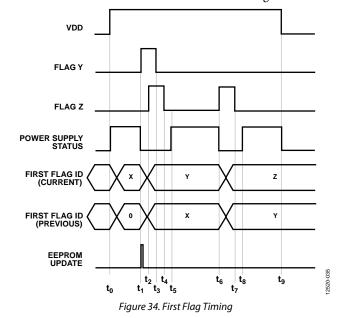

| Flags30                                               | Timeout Conditions                         |    |

| Voltage Readings                                      | Data Transmission Faults                   |    |

| Current Readings                                      | Data Content Faults                        |    |

| Power Readings                                        | EEPROM                                     |    |

|                                                       | LLI IOM                                    | 50 |

| EEPROM Features50                                      |

|--------------------------------------------------------|

| EEPROM Overview50                                      |

| Page Erase Operation50                                 |

| Read Operation (Byte Read and Block Read)50            |

| Write Operation (Byte Write and Block Write)51         |

| EEPROM Password51                                      |

| Downloading EEPROM Settings to Internal Registers52    |

| Saving Register Settings to the EEPROM52               |

| EEPROM CRC Checksum52                                  |

| GUI Software53                                         |

| PMBus Command Set54                                    |

| Extended Command List: Manufacturer Specific57         |

| PMBus Command Descriptions60                           |

| Basic PMBus Commands60                                 |

| Manufacturer Specific Extended Commands Descriptions80 |

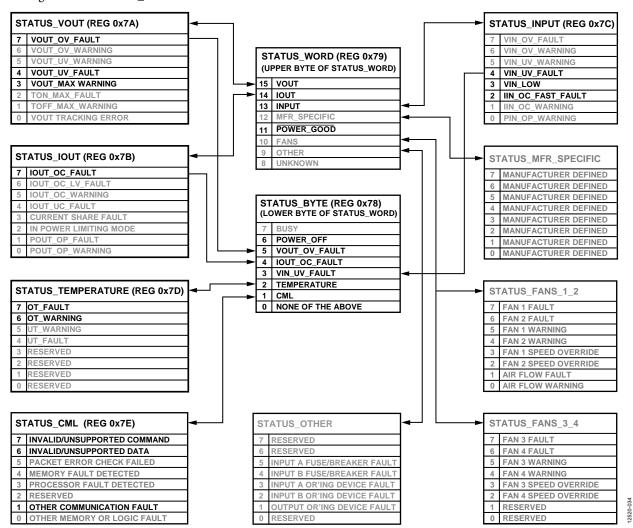

| Flag Configuration Registers80                         |

|                                                        |

| REVISION HISTORY                                       |

| 4/15—Rev. 0 to Rev. A                                  |

| Changes to Ordering Guide113                           |

|   | Soft Start and Software Reset Registers              | .82 |

|---|------------------------------------------------------|-----|

|   | Blanking and PGOOD Setting Registers                 | .83 |

|   | Switching Frequency and Synchronization Registers    | .86 |

|   | Current Sense and Limit Setting Registers            | .87 |

|   | Voltage Sense and Limit Setting Registers            | .92 |

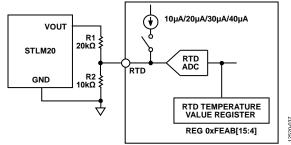

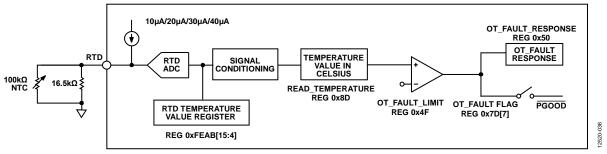

|   | Temperature Sense and Protection Setting Registers   | .93 |

|   | Digital Compensator and Modulation Setting Registers | .94 |

|   | PWM Outputs Timing Registers                         | .97 |

|   | Volt-Second Balance Control Registers                | .99 |

|   | Duty Cycle Reading Setting Registers                 | 101 |

|   | Adaptive Dead Time Compensation Registers            | 101 |

|   | Other Register Settings                              | 104 |

|   | Manufacturer Specific Fault Flag Registers           | 108 |

|   | Manufacturer Specific Value Reading Registers        | 111 |

| С | Outline Dimensions                                   | 113 |

|   | Ordering Guide                                       | 113 |

#### 1/15—Revision 0: Initial Version

# **SPECIFICATIONS**

$V_{\rm DD}$  = 3.0 V to 3.6 V,  $T_{\rm J}$  = -40°C to +125°C, unless otherwise noted; FSR = full-scale range.

Table 1.

| Parameter                                                         | Symbol            | Min            | Тур          | Max  | Unit   | Test Conditions/Comments                                    |

|-------------------------------------------------------------------|-------------------|----------------|--------------|------|--------|-------------------------------------------------------------|

| SUPPLY                                                            |                   |                |              |      |        |                                                             |

| Supply Voltage                                                    | $V_{DD}$          | 3.0            | 3.3          | 3.6  | V      | 2.2 μF capacitor connected to AGND                          |

| Supply Current                                                    | I <sub>DD</sub>   |                | 33           |      | mA     | Normal operation; PWM pins unloaded                         |

|                                                                   |                   |                | $I_{DD} + 6$ |      | mA     | During EEPROM programming                                   |

|                                                                   |                   |                | 50           | 100  | μΑ     | Shutdown; V <sub>DD</sub> below undervoltage                |

|                                                                   |                   |                |              |      |        | lockout (UVLO)                                              |

| POWER-ON RESET                                                    |                   |                |              |      |        |                                                             |

| Power-On Reset                                                    |                   |                |              | 3.0  | V      | V <sub>DD</sub> rising                                      |

| UVLO Threshold                                                    | UVLO              | 2.75           | 2.85         | 2.97 | V      | V <sub>DD</sub> falling                                     |

| UVLO Hysteresis                                                   |                   |                | 35           |      | mV     |                                                             |

| Overvoltage Lockout (OVLO) Threshold                              | OVLO              | 3.7            | 3.9          | 4.1  | V      |                                                             |

| OVLO Debounce                                                     |                   |                | 2            |      | μs     | VDD_OV flag debounce set to 2 μs                            |

|                                                                   |                   |                | 500          |      | μs     | VDD_OV flag debounce set to 500 μs                          |

| VCORE PIN                                                         |                   |                |              |      |        |                                                             |

| Output Voltage                                                    | V <sub>CORE</sub> | 2.45           | 2.6          | 2.75 | V      | 330 nF capacitor connected to AGND                          |

| OSCILLATOR AND PLL                                                |                   |                |              |      |        |                                                             |

| PLL Frequency                                                     |                   | 190            | 200          | 210  | MHz    | RES input = $10 \text{ k}\Omega \text{ (}\pm 0.1\%\text{)}$ |

| Digital PWM Resolution                                            |                   |                | 625          |      | ps     |                                                             |

| OUTA, OUTB, OUTC, OUTD, SR1, SR2 PINS                             |                   |                |              |      |        |                                                             |

| Output Voltage                                                    |                   |                |              |      |        |                                                             |

| Low                                                               | Vol               |                |              | 0.4  | V      | I <sub>OH</sub> = 10 mA                                     |

| High                                                              | V <sub>OH</sub>   | $V_{DD} - 0.4$ |              |      | V      | $I_{OL} = -10 \text{ mA}$                                   |

| Rise Time                                                         | t <sub>R</sub>    |                | 3.5          |      | ns     | $C_{LOAD} = 50 \text{ pF}$                                  |

| Fall Time                                                         | t <sub>F</sub>    |                | 1.5          |      | ns     | C <sub>LOAD</sub> = 50 pF                                   |

| Output Current                                                    |                   |                |              |      |        |                                                             |

| Source                                                            | loL               | -10            |              |      | mA     |                                                             |

| Sink                                                              | Іон               |                |              | 10   | mA     |                                                             |

| Synchronization Signal Output (SYNO) Positive Pulse Width         |                   | 600            | 640          | 680  | ns     | OUTC or OUTD programmed as SYNO                             |

| VS+, VS- VOLTAGE SENSE PINS                                       |                   |                |              |      |        |                                                             |

| Input Voltage Range                                               | V <sub>IN</sub>   | 0              | 1            | 1.6  | V      | Differential voltage from VS+ to VS-                        |

| Leakage Current                                                   |                   |                |              | 1.0  | μΑ     |                                                             |

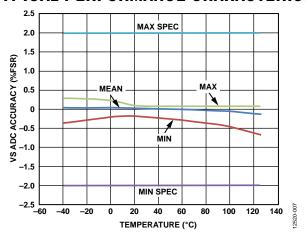

| Voltage Sense (VS) Accurate Analog-to-<br>Digital Converter (ADC) |                   |                |              |      |        |                                                             |

| Valid Input Voltage Range                                         |                   | 0              |              | 1.6  | V      |                                                             |

| ADC Clock Frequency                                               |                   |                | 1.56         |      | MHz    |                                                             |

| Register Update Rate                                              |                   |                | 10           |      | ms     |                                                             |

| Measurement                                                       |                   |                |              |      |        |                                                             |

| Resolution                                                        |                   |                | 12           |      | Bits   |                                                             |

| Accuracy                                                          |                   |                |              |      |        | Factory trimmed at 1.0 V                                    |

|                                                                   |                   | -5             |              | +5   | % FSR  | 0% to 100% of input voltage range                           |

|                                                                   |                   | -80            |              | +80  | mV     |                                                             |

|                                                                   |                   | -2             |              | +2   | % FSR  | 10% to 90% of input voltage range                           |

|                                                                   |                   | -32            |              | +32  | mV     |                                                             |

|                                                                   |                   | -1.0           |              | +1.0 | % FSR  | 900 mV to 1.1 V                                             |

|                                                                   |                   | -16            |              | +16  | mV     |                                                             |

| Temperature Coefficient                                           |                   |                |              | 70   | ppm/°C |                                                             |

| Voltage Differential from VS- to AGND                             |                   | -200           |              | +200 | mV     |                                                             |

| Parameter                                | Symbol            | Min   | Тур      | Max    | Unit  | Test Conditions/Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------------------------------|-------------------|-------|----------|--------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VS High Speed ADC                        |                   |       |          |        |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Equivalent Sampling Frequency            | f <sub>SAMP</sub> |       | $f_{SW}$ |        | kHz   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Equivalent Resolution                    | - 57              |       | 6        |        | Bits  | f <sub>sw</sub> = 390.5 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Dynamic Range                            |                   |       | ±25      |        | mV    | Regulation voltage = 0 mV to 1.6 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| VS Undervoltage Protection (UVP) Digital |                   |       | ±23      |        |       | Triggers VOUT_UV_FAULT flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Comparator                               |                   |       |          |        |       | Inggers voor_ov_r/toer nag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Threshold Accuracy                       |                   | -2    |          | +2     | % FSR | 10% to 90% of input voltage range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Comparator Update Speed                  |                   |       | 82       |        | μs    | The state of the |

| OVP PIN                                  |                   |       |          |        |       | Triggers VOUT_OV_FAULT flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Leakage Current                          |                   |       |          | 1.0    | μΑ    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Overvoltage Protection (OVP) Comparator  |                   |       |          |        | '     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Voltage Range                            |                   | 0.75  |          | 1.5    | V     | Differential voltage from OVP to VS-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Threshold Accuracy                       |                   | -1.6  | 1        | +1.6   | %     | 0.75 V to 1.5 V voltage range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Propagation Delay (Latency)              |                   | 1.0   | 61       | 85     | ns    | Debounce time not included                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| VF VOLTAGE SENSE PIN                     |                   |       |          |        | 113   | Debourie time not included                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Input Voltage Range                      | V <sub>IN</sub>   | 0     | 1        | 1.6    | V     | Voltage from VF to AGND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Leakage Current                          | V IIV             |       | •        | 1.0    | μΑ    | voltage nom vi to Adivo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| General ADC                              |                   |       |          | 1.0    | μΛ    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Valid Input Voltage Range                |                   | 0     |          | 1.6    | V     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ADC Clock Frequency                      |                   | 0     | 1.56     | 1.0    | MHz   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Register Update Rate                     |                   |       | 1.31     |        |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Measurement                              |                   |       | 1.51     |        | ms    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                          |                   |       | 11       |        | D:+-  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Resolution                               |                   | _     | 11       | . 2    | Bits  | 100/ 1 000/ 6: 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

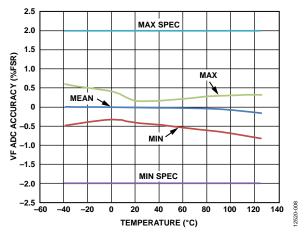

| Accuracy                                 |                   | -2    |          | +2     | % FSR | 10% to 90% of input voltage range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

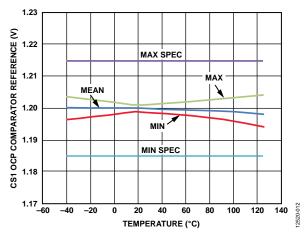

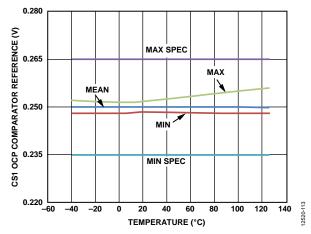

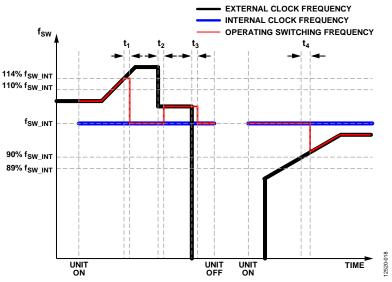

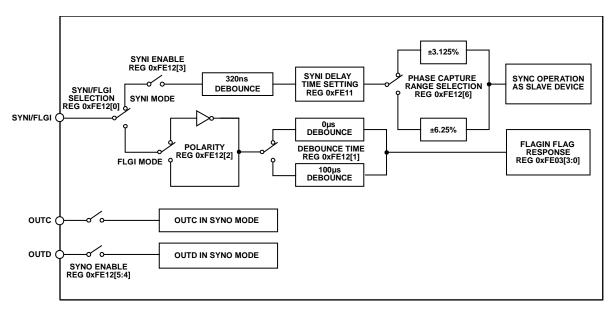

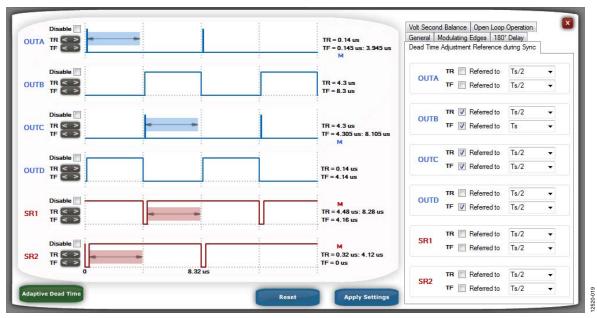

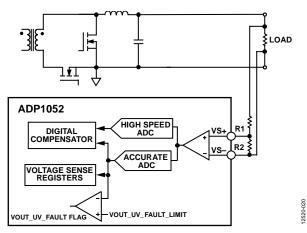

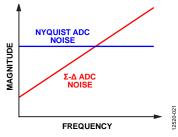

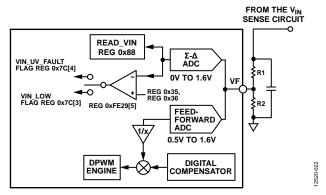

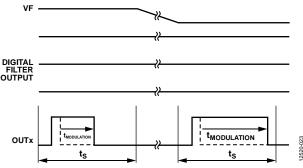

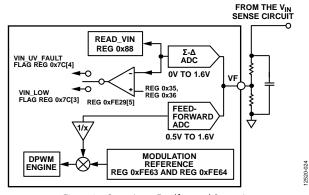

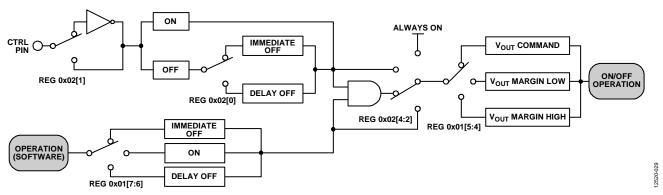

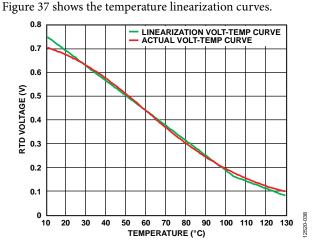

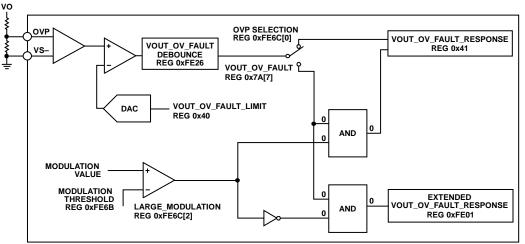

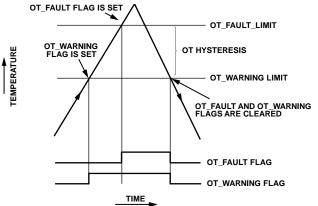

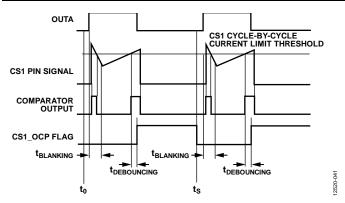

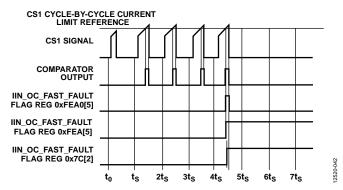

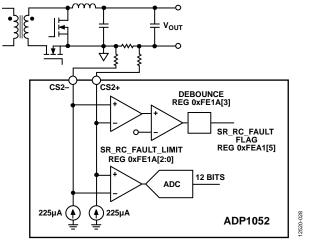

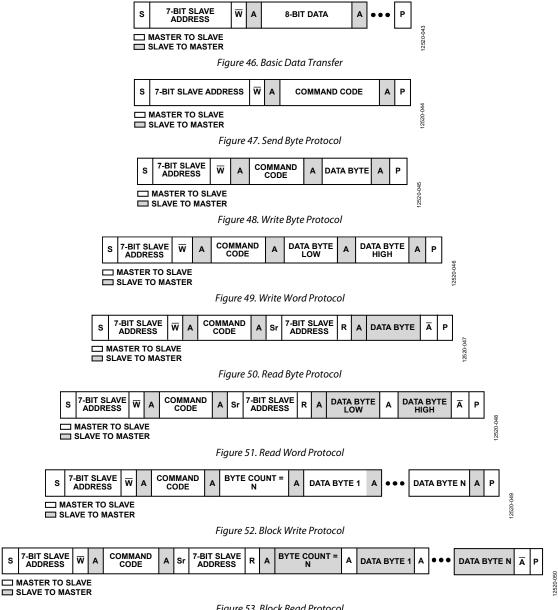

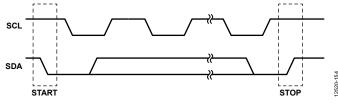

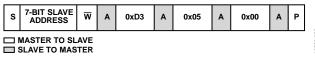

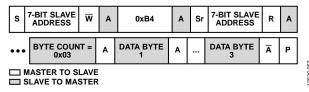

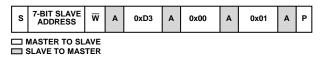

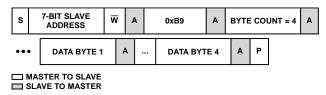

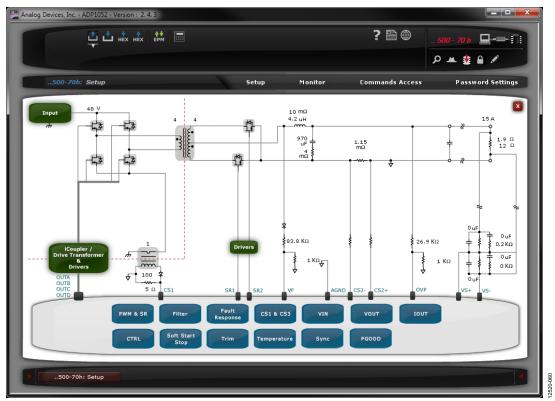

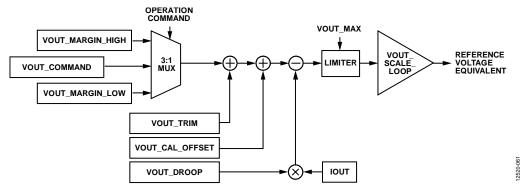

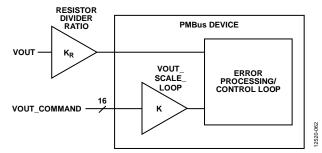

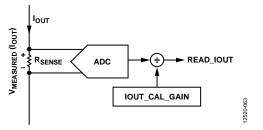

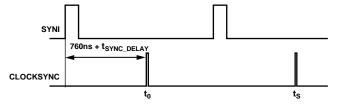

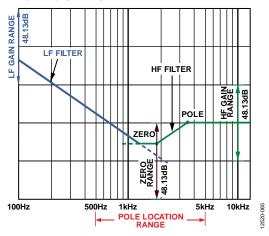

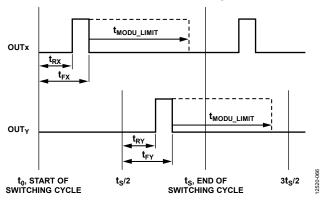

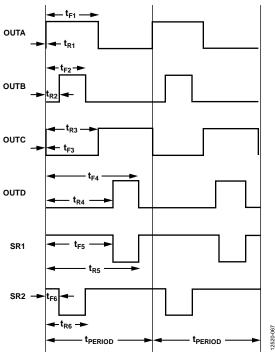

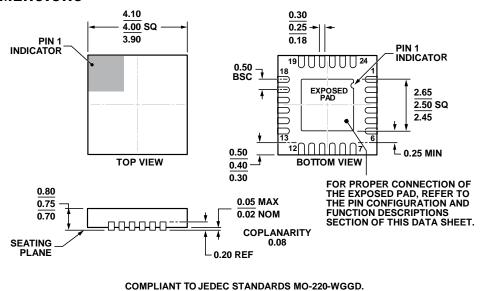

|                                          |                   | -32   |          | +32    | mV    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |