## **SCRs**

## **General Description**

Available either in sensitive or standard gate triggering levels, the 4A SCR series is suitable to fit all modes of control found inapplications such as overvoltage crowbar protection, motor control circuits in power tools and kitchen aids, in-rush current limiting circuits, capacitive discharge ignition, voltage regulation circuits...

#### **Features**

- ◆ Repetitive Peak Off-State Voltage: 600V and 800V

- ◆ R.M.S On-State Current (IT(RMS)= 4A)

- ♦ These are Pb-Free Devices

## **Absolute Maximum Ratings**

| Symbol              | Items                                     | Conditions                                                    |          | Ratings          | Unit |

|---------------------|-------------------------------------------|---------------------------------------------------------------|----------|------------------|------|

| V <sub>DRM</sub>    | Repetitive Peak Off-State Voltage         | ADT4A60E                                                      |          | 600              | V    |

| $V_{RRM}$           | Repetitive peak reverse voltage           | Tj=25°C                                                       | ADT4A80E | 800              | ٧    |

| I <sub>T(AV)</sub>  | Average On-State Current                  | Half Sine Wave , To                                           | 3.5      | Α                |      |

| I <sub>T(RMS)</sub> | R.M.S On-State Current                    | Half Sine Wave , Tc = 100°C                                   |          | 4                | А    |

| I <sub>TSM</sub>    | Surge On-State Current                    | 1/2 Cycle, Sine Wave Non-Repetitive,<br>tp=10ms(50Hz)Tj =25°C |          | 36               | А    |

| I <sup>2</sup> t    | I <sup>2</sup> t for Fusing               | Tj =25°C,tp =10ms                                             | 4.5      | A <sup>2</sup> S |      |

| dl/dt               | Critical rate of rise of on-state current | Tj =125°C, tr≤ 100ns                                          |          | 50               | A/µs |

| P <sub>GM</sub>     | Forward Peak Gate Power Dissipation       | Tj =125°C, Pulse Width ≤ 20μs                                 |          | 2                | W    |

| P <sub>G(AV)</sub>  | Forward Average Gate Power Dissipation    | Tj =25°C, tp =10ms                                            |          | 0.2              | W    |

| I <sub>GM</sub>     | Peak Gate Current                         | Tj =125°C, Pulse Width ≤ 20μs                                 |          | 1.2              | Α    |

| Tj                  | Operating Junction Temperature            |                                                               |          | - 40 ~ 125       | °C   |

| T <sub>STG</sub>    | Storage Temperature                       |                                                               |          | - 40 ~ 150       | °C   |

# ADT4A60E/80E

# **Electrical Characteristics** (Tj = 25°C unless otherwise specified)

| Symbol               | Items                                                  | Conditions                                  |           | ADT4A60E/80E |       | Unit     |  |

|----------------------|--------------------------------------------------------|---------------------------------------------|-----------|--------------|-------|----------|--|

| -                    |                                                        |                                             |           | Т            | S     | <b> </b> |  |

|                      |                                                        | $V_{DRM} = V_{RRM}, R_{GK} = 1K\Omega$      |           | 5            |       | uA       |  |

| $I_{DRM}$            | Peak Forward Reverse                                   | Tj = 25°C                                   | Max       | 5            |       | u/ t     |  |

| I <sub>RRM</sub>     | Blocking Current                                       | $V_{DRM} = V_{RRM}, R_{GK} = 1K\Omega$      | Max.      |              |       | mA       |  |

|                      |                                                        | Tj = 125°C                                  |           | 1            |       | IIIA     |  |

| $V_{TM}$             | Peak On-State Voltage                                  | $I_{TM}$ = 10A, $t_p$ = 380 $\mu$ s         | Max.      | 1.7          |       | V        |  |

| $V_{GD}$             | Non Trigger Cate Veltage                               | $V_D = V_{DRM}$ $R_L = 3.3 \text{ k}\Omega$ | Min.      | 0.2          |       | V        |  |

| V GD                 | Non-Trigger Gate Voltage                               | $R_{GK} = 1K\Omega$ $Tj = 125$ °C           | WIIII. U. |              | .2    | V        |  |

| $V_{GT}$             | Gate Trigger Voltage                                   | Max. 1.3                                    |           | V            |       |          |  |

| I <sub>GT</sub>      | Gate Trigger Current                                   | $V_D = 12V$ , $R_L = 33\Omega$              | Max.      | 0.2          | 15    | mA       |  |

| I <sub>H</sub>       | Holding Current                                        | $I_T = 0.05A$ $R_{GK} = 1K\Omega$           | Max.      | 5            | 40    | mA       |  |

| ال                   | Latching Current                                       | $I_G$ = 1.2 $I_{GT}$ $R_{GK}$ = 1K $\Omega$ | Max.      | 6            | 50    | mA       |  |

| dV/dt                | Critical Rate of Rise of                               | $V_D = 2/3V_{DRM}$ gate open                | Min.      |              | 5 150 | \//··-   |  |

|                      | Off-State Voltage                                      | $R_{GK} = 1K\Omega$ Tj = 125°C              |           | 5            |       | V/µs     |  |

| R <sub>th(j-c)</sub> | Junction to case                                       |                                             | Max.      | 6.5          |       | °C/W     |  |

| $R_{th(j-a)}$        | Junction to ambient(Copper surface under tab:S=0.5cm²) |                                             | Max.      | 70           |       | °C/W     |  |

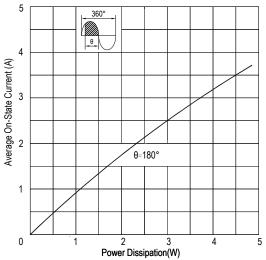

FIG.1: Maximum average power dissipation (Single phase half wave)

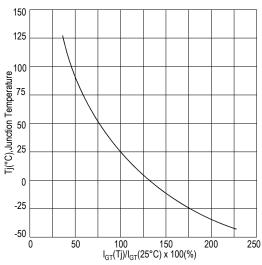

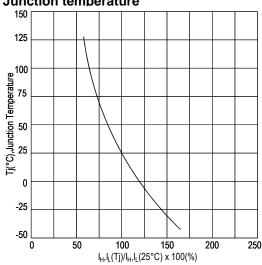

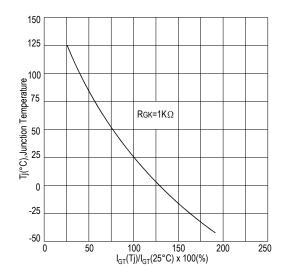

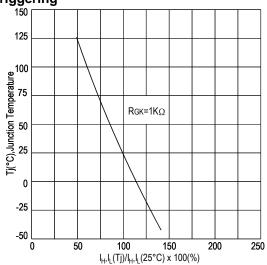

FIG.3: Gate trigger current VS **Junction** temperature

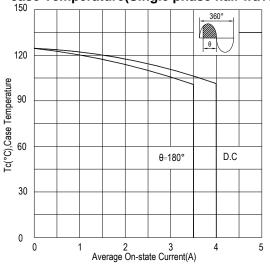

FIG.2: Average on-state current VS Allowable case Temperature(Single phase half wave)

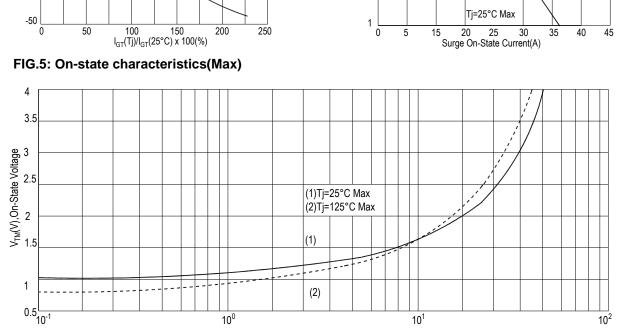

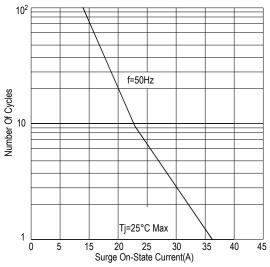

FIG.4: Rated surge on-state current (Non-Repetitive)

I<sub>TM</sub>(A),On-State Current

10<sup>1</sup>

10<sup>0</sup>

FIG.6:Holding current and Latching current VS Junction temperature

FIG.8: Gate trigger current VS Junction temperature for type T gate triggering

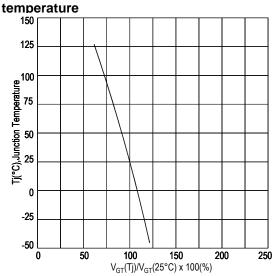

FIG.7: Gate trigger voltage VS Junction

FIG.8:Holding current and Latching current

VS Junction temperature for type T gate

triggering

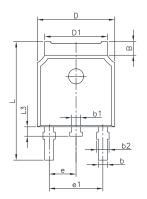

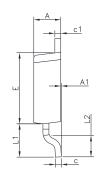

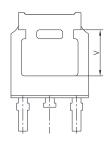

#### **PACKAGE MECHANICAL DATA**

#### **TO-252-2 Package Dimension**

| Cumala | Dimensions     |       | Dimensions |       |  |

|--------|----------------|-------|------------|-------|--|

| Symb   | In Millimeters |       | In Inches  |       |  |

| ol     | Min.           | Max.  | Min.       | Max.  |  |

| Α      | 2.200          | 2.400 | 0.087      | 0.094 |  |

| A1     | 0.000          | 0.127 | 0.000      | 0.005 |  |

| В      | 1.070          | 1.220 | 0.042      | 0.048 |  |

| b      | 0.720          | 0.850 | 0.028      | 0.033 |  |

| b1     | 0.720          | 0.850 | 0.028      | 0.033 |  |

| С      | 0.450          | 0.620 | 0.017      | 0.024 |  |

| c1     | 0.450          | 0.620 | 0.017      | 0.024 |  |

| D      | 6.350          | 6.650 | 0.250      | 0.262 |  |

| D1     | 5.200          | 5.400 | 0.205      | 0.213 |  |

| E      | 5.900          | 6.200 | 0.232      | 0.244 |  |

| е      | 2.300 TYP.     |       | 0.091 TYP. |       |  |

| e1     | 4.500          | 4.700 | 0.177      | 0.185 |  |

| L      | 9.500          | 10.60 | 0.374      | 0.396 |  |

| L1     | 2.550          | 2.900 | 0.100      | 0.114 |  |

| L2     | 1.400          | 1.780 | 0.055      | 0.070 |  |

| L3     | 0.600          | 0.900 | 0.024      | 0.035 |  |

| V      | 3.950 REF.     |       | 0.155 REF. |       |  |

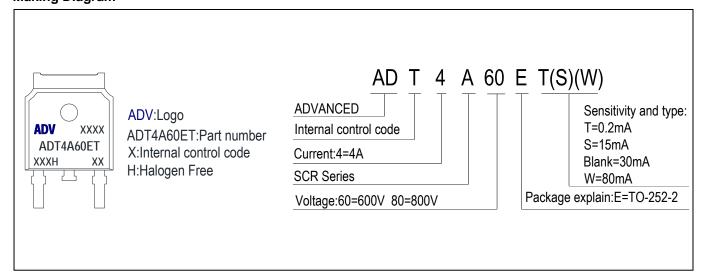

## **Making Diagram**

## **Ordering information**

| Part number                                        | number Package Marking Packing |           | Packing       | Quantity |  |  |

|----------------------------------------------------|--------------------------------|-----------|---------------|----------|--|--|

| ADT4A60E#                                          | TO-252-2                       | ADT4A60E# | Tube          | 80pcs    |  |  |

| ADT4A60E#                                          |                                |           | Embossed tape | 2500pcs  |  |  |

| ADT 4 A 00 F#                                      | TO-252-2                       | ADT4A80E# | Tube          | 80pcs    |  |  |

| ADT4A80E#                                          |                                |           | Embossed tape | 2500pcs  |  |  |

| Note:# = Gate Trigger Current Sensitivity and type |                                |           |               |          |  |  |

## **ADT4A60E/80E**

#### Notice

- 1. All information included in this document such as product data, diagrams, charts, programs, algorithms, and application circuit examples, is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any ADV products listed in this document, please confirm the latest product information with a ADV sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by ADV such as that disclosed through our website. (http://www.advsemi.com)

- 2 . ADV has used reasonable care in compiling the information included in this document, but ADV assumes no liability whatsoever for any damages incurred as a result of errors or omissions in the information included in this document.

- 3. You should use the products described herein within the range specified by ADV, especially with respectvto the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. ADV shall have no liability for malfunctions or damages arising out of the use of ADV products beyond such specified ranges.

- 4. When using or otherwise relying on the information in this document, you should evaluate the information in light of the total system before deciding about the applicability of such information to the intended application. ADV makes no representations, warranties or guaranties regarding the suitability of its products for any particular application and specifically disclaims any liability arising out of the application and use of the information in this document or ADV products.

- 5 . Although ADV endeavors to improve the quality and reliability of its products, IC products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Please be sure to implement safety measures to guard against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a ADV product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other applicable measures. Among others, since the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 6. This document is provided for reference purposes only so that ADV customers may select the appropriate ADV products for their use. ADV neither makes warranties or representations with respect to the accuracy or completeness of the information contained in this document nor grants any license to any intellectual property rights or any other rights of ADV or any third party with respect to the information in this document.

- 7 . ADV shall have no liability for damages or infringement of any intellectual property or other rights arising out of the use of any information in this document, including, but not limited to, product data, diagrams, charts, programs, algorithms, and application circuit examples.

- 8. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written approval from ADV.

6 / 6 www.advsemi.com Feb,2017 -Rev.3.05