# Puma AEL2005 10 Gbps SFP+ Transceiver With Integrated EDC

Data Sheet Production Revision C1

Revision 1.2 December 18, 2007

Aeluros, Inc. 201 San Antonio Circle, Suite 172 Mountain View, CA. 94040 (650) 917-7051 www.aeluros.com support@aeluros.com

Copyright © 2007 Aeluros, Inc. All rights reserved. Aeluros, the stylized Aeluros logo, and all other words and logos that are identified as trademarks are, unless noted otherwise, the trademarks of Aeluros Inc. in the U.S. and other countries. All other trademarks mentioned in this document are the property of their respective owners.

| No | Date          | Page<br>Number | Old<br>Rev | New<br>Rev | Description                                                                         |

|----|---------------|----------------|------------|------------|-------------------------------------------------------------------------------------|

| 1  | Nov. 9, 2007  | 8              | 1.0        | 1.1        | Changed the LOSthresh and LOSthreshhyst fields to 6 bits.                           |

| 2  | Nov. 9, 2007  | 17             | 1.0        | 1.1        | Formatting of tables 4, 5, and 6.                                                   |

| 3  | Nov. 9, 2007  | 14             | 1.0        | 1.1        | Updated text in Section 6, SGMII Mode.                                              |

| 4  | Nov. 9, 2007  | 77             | 1.0        | 1.1        | Modified contents of LOS Mask register.                                             |

| 5  | Nov. 9, 2007  | 81             | 1.0        | 1.1        | Added Table 106, SGMII Configuration register.                                      |

| 6  | Nov. 9, 2007  | 109            | 1.0        | 1.1        | Reorganized Section 10, Mechanical Specifications                                   |

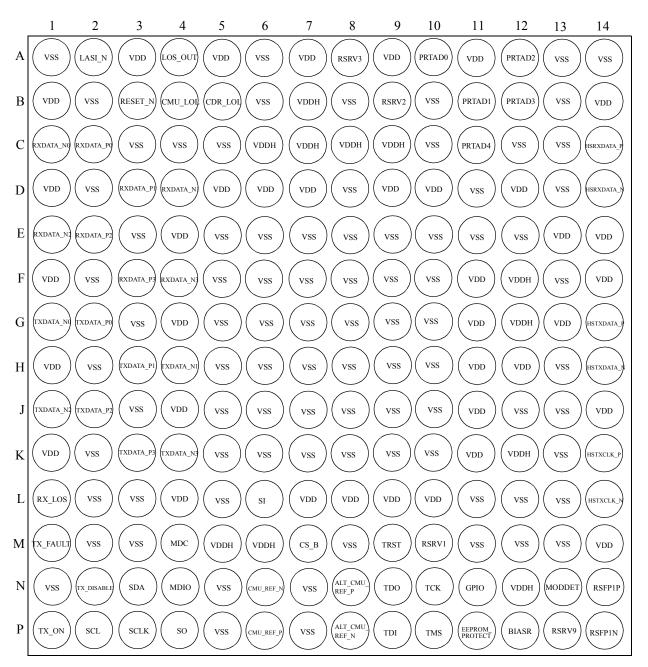

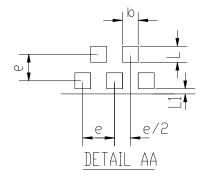

| 7  | Nov. 9, 2007  | 112            | 1.0        | 1.1        | Updated Figure 60, AEL2005 package pinout.                                          |

| 8  | Nov. 9, 2007  |                | 1.0        | 1.1        | Removed references to 'un-retimed paths' throughout document.                       |

| 9  | Dec. 18, 2007 | 15             | 1.1        | 1.2        | Added Section 7, On-Chip Micro-Controller.                                          |

| 10 | Dec 18, 2007  | 99, 100        | 1.1        | 1.2        | Fixed typo - changed 2.5V to 3.3 V in power sequence diagram                        |

| 11 | Dec 18, 2007  | 51, 52         | 1.1        | 1.2        | Added register 1.C04A, 1.C04B, 1.CA00, 1.CA12, 1.CA13, 1.CA1C, 1.CA1E to Section 15 |

1

| 1 | Introduction                                                                                       | 1  |

|---|----------------------------------------------------------------------------------------------------|----|

| 2 | Features and Benefits                                                                              | 2  |

| 3 | Applications                                                                                       | 3  |

| 4 | Functional Description                                                                             | 4  |

|   | 4.1 Parallel to Serial Path (Transmit)                                                             | 5  |

|   | 4.1.1 XAUI Parallel Receive                                                                        |    |

|   | 4.1.2 Word Align and Decode                                                                        |    |

|   | 4.1.3 10GBASE-R Scrambler/Encoder, FIFO, and Rate Adjustment                                       |    |

|   | 4.1.4 Serial Output Transmitter                                                                    |    |

|   | <ul><li>4.2 Serial to Parallel Path (Receive)</li><li>4.2.1 HSRXDATA Receive Channel</li></ul>     |    |

|   | 4.2.1 HSRADATA Receive Channel.<br>4.2.2 64b/66b Serial Descramble/Decode, Alignment, Receive FIFO |    |

|   | 4.2.3 Receive 8b/10b Encoding                                                                      |    |

|   | 4.2.4 XAUI Parallel Transmit                                                                       |    |

|   | 4.3 EDC (Electronic Dispersion Compensation) Functionality                                         |    |

|   | 4.3.1 Feed Forward Stage                                                                           |    |

|   | 4.3.2 Feedback Stage                                                                               |    |

|   | 4.3.3 EDC Adaptation                                                                               | 12 |

| 5 | 10G Transmit Pre-emphasis                                                                          | 13 |

| 6 | SGMII Mode                                                                                         | 14 |

| 7 | On-Chip Micro-Controller                                                                           | 15 |

|   | 7.1 uC Block Diagram                                                                               | 15 |

|   | 7.2 uC Configuration                                                                               | 15 |

|   | 7.3 uC Control and Status                                                                          | 16 |

| 8 | GPIO Interface                                                                                     | 17 |

| - | 8.1 LED Drivers                                                                                    |    |

|   | 8.1.1 Example 1: Configure CDR LOL Pin to Indicate Link-up Status                                  |    |

|   | 8.1.2 Example 2: Configure CMU_LOL Pin to Indicate Traffic Activity                                |    |

|   | 8.2 MODDET Input                                                                                   | 18 |

|   | 8.3 Rate Select Output                                                                             | 18 |

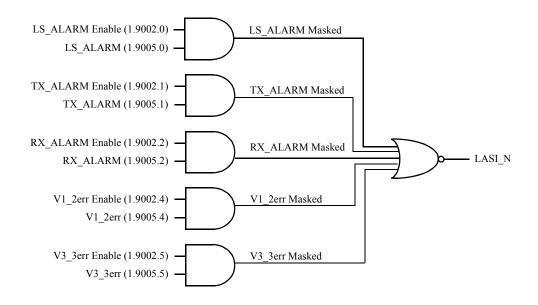

|   | 8.4 Link Alarm Status Interrupt                                                                    | 19 |

| 9 | Clocking Modes                                                                                     | 24 |

|   | 9.1 Basic LAN Clocking                                                                             | 24 |

|   | 9.2 Basic SAN Clocking                                                                             | 24 |

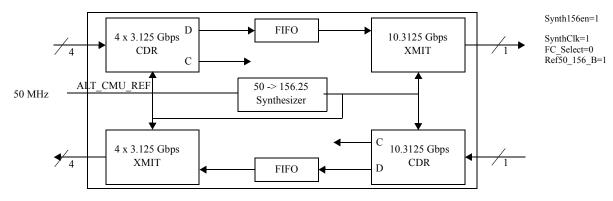

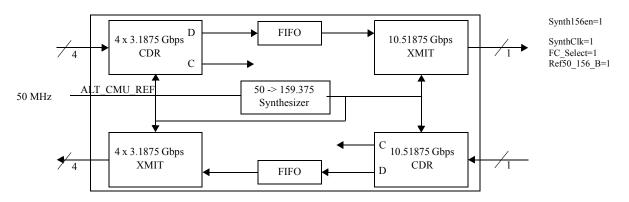

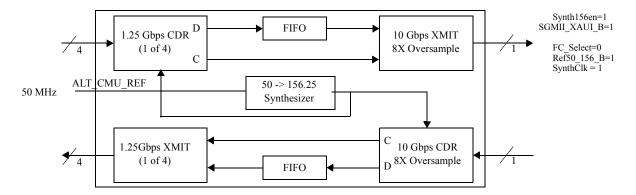

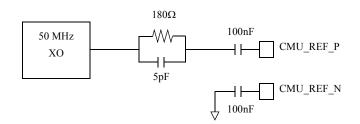

|   | 9.3 50 MHz Clocking                                                                                | 25 |

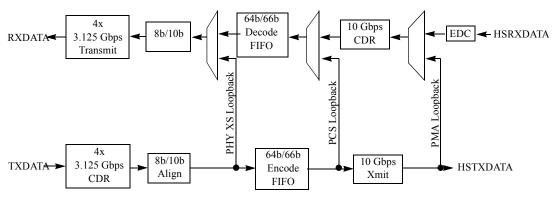

| 1 | 0 Test & Loopback Modes                                                                            | 27 |

| - | 10.1 System Loopback Modes (XAUI CDR to XAUI Transmit)                                             |    |

|   | 10.1.1 PHY XS System Loopback                                                                      |    |

|   | 10.1.2 PCS System Loopback                                                                         |    |

|   | 10.1.3 PMA System Loopback                                                                         |    |

|   | 10.1.4 System Loopback Clocking Modes                                                              | 28 |

|   | 10.2 Line Loopback Modes (HSRXDATA to HSTXDATA)                                                    |    |

|   | 10.2.1 PMA Line Loopback                                                                           |    |

|   | 10.2.2 PHY XS Line Loopback                                                                        |    |

|   | 10.2.3 PMA Line Loopback Clocking Modes                                                            |    |

|   | 10.3 PRBS Pattern Generators and Checkers                                                          |    |

|   | 10.4 Internal Packet Generators and Checkers                                                       |    |

|   |                                                                                                    |    |

|    | 10.4.2 Initiating Packet Transmission                                     |    |

|----|---------------------------------------------------------------------------|----|

|    | 10.4.3 Using the Checker                                                  |    |

|    | 10.4.4 Example Sequences of Operation                                     |    |

| 11 |                                                                           |    |

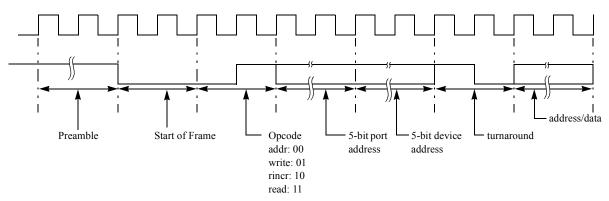

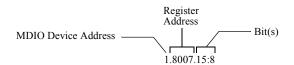

| 11 | 1 MDIO Port                                                               |    |

|    | 11.1 MDIO Address Transaction                                             |    |

|    | 11.2 MDIO Write Transaction                                               |    |

|    | 11.3 MDIO Read Transaction                                                |    |

|    | 11.4 MDIO Read Increment Transaction                                      |    |

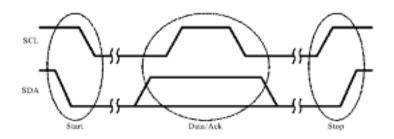

| 12 | 2 SDA/SCL Interface                                                       |    |

|    | 12.1 Configuration                                                        |    |

|    | 12.2 Update via Control/Status Register                                   |    |

|    | 12.3 Reading Optical Monitoring Information                               |    |

|    | 12.4 Format for Serial Bus Operations                                     |    |

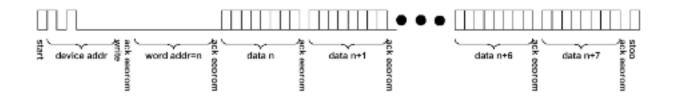

|    | 12.5 EEPROM Read and Write                                                |    |

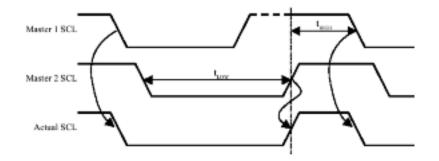

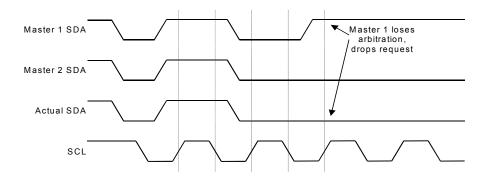

|    | 12.6 Multi-master Operation and Arbitration                               |    |

|    | 12.7 4Kb Serial EEPROM Support                                            |    |

|    | 12.8 SDA/SCL Byte-by-Byte Operations                                      |    |

|    | 12.9 EEPROM-Based Patching Support                                        |    |

| 13 | 3 SPI Interface                                                           |    |

|    | 13.1 SPI Operations                                                       |    |

|    | 13.2 SPI Instructions                                                     |    |

|    | 13.3 Example SPI Operation                                                |    |

| 14 | 4 Pin Descriptions                                                        | 45 |

| 15 | 5 Registers                                                               |    |

|    | 15.1 Register Overview                                                    |    |

|    | 15.2 PMA/PMD Registers                                                    |    |

|    | 15.3 PMA/PMD Registers                                                    |    |

|    | 15.4 PCS Registers                                                        |    |

|    | 15.5 PHY XS Registers                                                     | 61 |

|    | 15.6 XENPAK Registers                                                     | 64 |

|    | 15.6.1 XENPAK Nonvolatile Registers                                       |    |

|    | 15.6.2 Link Alarm Status Interrupt (LASI) Registers                       |    |

|    | 15.6.3 Digital Optical Monitoring Registers                               |    |

|    | 15.7 AEL2005 Device-Specific Registers                                    |    |

| 16 | 6 Electrical Specifications                                               |    |

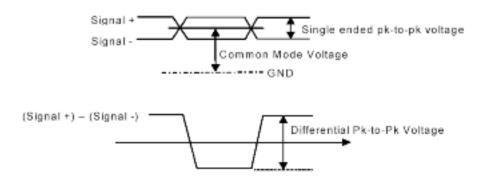

|    | 16.1 Conventions                                                          |    |

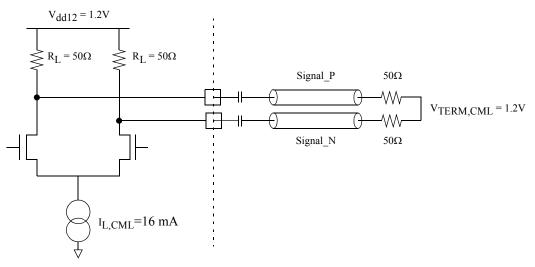

|    | 16.2 SFP+ Interface DC and AC Specifications                              |    |

|    | 16.3 XAUI Interface AC Specifications                                     |    |

|    | 16.3.1 XAUI SerDes Inputs (TXDATA)<br>16.3.2 XAUI SerDes Outputs (RXDATA) |    |

|    | 16.3.3 XAUI SerDes Specification Table                                    |    |

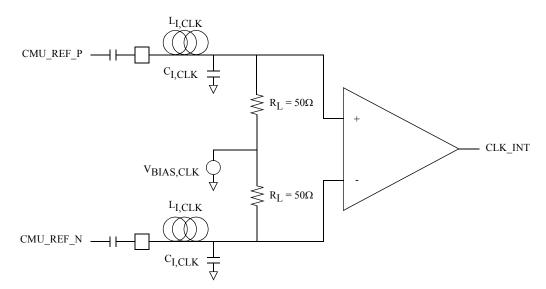

|    | 16.4 CMU REF Clock Input                                                  |    |

|    | 16.5 CMOS Interface                                                       |    |

|    | 16.6 MDIO Interface                                                       |    |

|    | 16.7 SDA/SCL Interface                                                    |    |

|    | 16.8 Power-On Sequence                                                    |    |

|    | The Tower on Sequence                                                     |    |

| 16.8.1 Basic AEL2005 Device Power-On Sequence                  |     |

|----------------------------------------------------------------|-----|

| 16.8.2 AEL2005 Device Low Power Startup (LPS) Power Sequencing |     |

| 16.8.3 AEL2005 Device TX_ON Timing                             | 106 |

| 16.8.4 Power-on Timing Specifications                          | 107 |

| 16.9 Operating Conditions                                      | 107 |

| 17 Mechanical Specifications                                   | 109 |

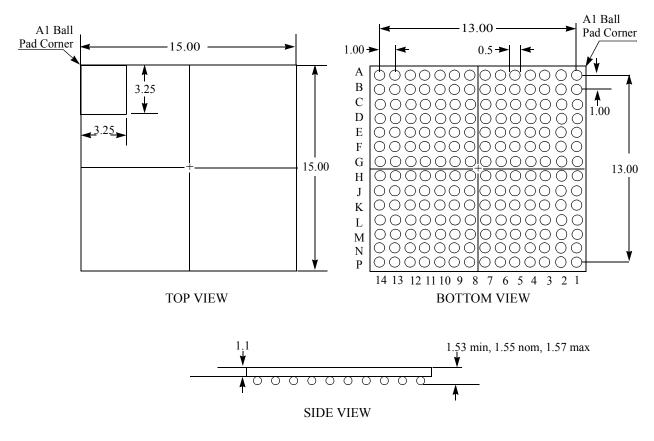

| 17.1 196-Pin PBGA Package                                      | 109 |

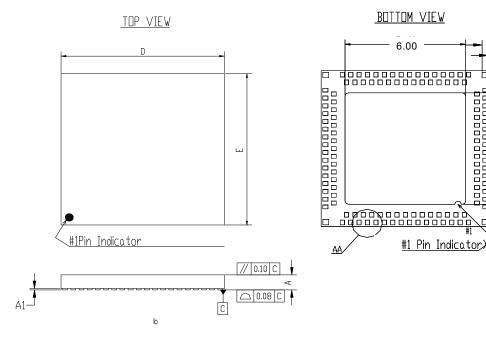

| 17.2 124-Pin QFN Package                                       | 111 |

| 18 Boundary Scan Test Access Port (TAP)                        | 113 |

| 19 Ordering Information                                        | 114 |

| Table 1. Puma AEL2005 Features and Benefits                                                                                                                                                                       | 2  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 2. Serial Transmit Clock Frequencies                                                                                                                                                                        |    |

| Table 3. Serial Receive Clock Frequencies                                                                                                                                                                         |    |

| Table 4. Encoding of LED Indicators                                                                                                                                                                               |    |

| Table 5. Configuring CDR LOL Pin to Indicate Link-up Status                                                                                                                                                       |    |

| Table 6. Configuring CMU LOL Pin to Indicate Traffic Activity                                                                                                                                                     |    |

| Table 7. GPIO Control Mode Table A                                                                                                                                                                                |    |

| Table 8. GPIO Status Mode Table B                                                                                                                                                                                 |    |

| Table 9. AEL2005 Loopback Modes                                                                                                                                                                                   |    |

| Table 10. Packet Generator Modes for Receive Path                                                                                                                                                                 |    |

| Table 11. Packet Generator Modes for Transmit Path                                                                                                                                                                |    |

| Table 12. Example Register Settings for Patch Support                                                                                                                                                             |    |

| Table 13. SPI Instructions                                                                                                                                                                                        |    |

| Table 14. SPI Status Register                                                                                                                                                                                     |    |

| Table 15. AEL2005 Pin Descriptions                                                                                                                                                                                | 45 |

| Table 16. PMA/PMD, PCS and PHY XS Registers                                                                                                                                                                       | 48 |

| Table 17. XENPAK Register Set                                                                                                                                                                                     | 49 |

| Table 18. AEL2005 Device Specific Registers                                                                                                                                                                       | 51 |

| Table 19. PMA/PMD Control 1 Register (MDIO Device Address = 1, Register Address = 0x0000)                                                                                                                         | 53 |

| Table 20. PMA/PMD Status 1 Register (MDIO Device Address = 1, Register Address = 0x0001)                                                                                                                          | 53 |

| Table 21. PMA/PMD Device Identifier Upper 16 Bits (MDIO Device Address = 1, Register Address = 0x0002)                                                                                                            |    |

| Table 23. PMA/PMD Speed Ability (MDIO Device Address = 1, Register Address = 0x0004)                                                                                                                              |    |

| Table 24. PMA/PMD Devices in Package: Upper 16 Bits (MDIO Device Address = 1, Register Address = 0x0005)                                                                                                          |    |

| Table 25. PMA/PMD Devices in Package: Lower 16 Bits (MDIO Device Address = 1, Register Address = 0x0006)                                                                                                          |    |

| Table 26. 10G PMA/PMD Control 2 Register (MDIO Device Address = 1, Register Address = 0x0007)                                                                                                                     |    |

| Table 22. PMA/PMD Device Identifier Lower 16 Bits (MDIO Device Address = 1, Register Address = 0x0003)                                                                                                            |    |

| Table 27. 10G PMA/PMD Status 2 Register (MDIO Device Address = 1, Register Address = 0x0008)                                                                                                                      |    |

| Table 28. 10G PMA/PMD Transmit Disable Register (MDIO Device Address = 1, Register Address = 0x0009)                                                                                                              |    |

| Table 29. 10G PMA/PMD Receive Signal Detect Register (MDIO Device Address = 1, Register Address = 0x000A)                                                                                                         |    |

| Table 30. 10G PMA/PMD Receive Signal Detect Register (MDIO Device Address = 1, Register Address = 0x000B)                                                                                                         |    |

| Table 31. PMA/PMD Package Identifier: Upper 16 Bits (MDIO Device Address = 1, Register Address = 0x000E)                                                                                                          |    |

| Table 32. PMA/PMD Package Identifier: Lower 16 Bits (MDIO Device Address = 1, Register Address = 0x000F)                                                                                                          |    |

| Table 33. PCS Control 1 Register (MDIO Device Address = 3, Register Address = 0x0000)                                                                                                                             |    |

| Table 34. PCS Status 1 Register (MDIO Device Address = 3, Register Address = 0x0001)         Table 35. PCG Device Address = 16 Device Address = 3, Register Address = 0x0001)                                     |    |

| Table 35. PCS Device Identifier Upper 16 Bits (MDIO Device Address = 3, Register Address = 0x0002)                                                                                                                |    |

| Table 36. PCS Device Identifier Lower 16 Bits (MDIO Device Address = 3, Register Address = $0x0003$ )                                                                                                             |    |

| Table 37. PCS Speed Ability (MDIO Device Address = 3, Register Address = 0x0004)         Table 38. PCS Device Address = 16 Pic (MDIO Device Address = 0x0004)                                                     |    |

| Table 38. PCS Devices in Package: Upper 16 Bits (MDIO Device Address = 3, Register Address = 0x0005)         Table 39. PCS Devices in Package Lower: 16 Bits (MDIO Device Address = 3, Register Address = 0x0006) |    |

| Table 39. PCS Devices in Package Lower. To Bits (MDIO Device Address = 5, Register Address = 0x0000)                                                                                                              |    |

| Table 40. 10G PCS Control 2 Register (MDIO Device Address – 3, Register Address – 0x0007)                                                                                                                         |    |

| Table 42. PCS Package Identifier Upper: 16 Bits (MDIO Device Address = 3, Register Address = 0x0008)                                                                                                              |    |

| Table 43. PCS Package Identifier Lower: 16 Bits (MDIO Device Address = 3, Register Address = 0x000E)                                                                                                              |    |

| Table 44. 10GBASE-X PCS Status (MDIO Device Address = 3, Register Address = 0x0018)                                                                                                                               |    |

| Table 45. 10GBASE-X PCS Test Control (MDIO Device Address = 3, Register Address = 0x0010)                                                                                                                         |    |

| Table 46. 10GBASE-R PCS Status 1 (MDIO Device Address = 3, Register Address = 0x0020)                                                                                                                             |    |

| Table 47. 10GBASE-R PCS Status 2 (MDIO Device Address = 3, Register Address = 0x0020)                                                                                                                             |    |

| Table 48. 10GBASE-R Test Patterns (MDIO Device Address = 3)                                                                                                                                                       |    |

| Table 49. 10GBASE-R PCS Test Pattern Control (MDIO Device Address = 3, Register Address = 0x002A)                                                                                                                 |    |

| Table 50. 10GBASE-R PCS Test Pattern Error Counter (MDIO Device Address = 3, Register Address = 0x002B)                                                                                                           |    |

| Table 51. PCS System Loopback Control (MDIO Device Address = 3, Register Address = 0xC000)                                                                                                                        |    |

| Table 52. PHY XS Control 1 Register (MDIO Device Address = 4, Register Address = 0x0000)                                                                                                                          |    |

| Table 53. PHY XS Status 1 Register (MDIO Device Address = 4, Register Address = 0x0001)                                                                                                                           |    |

| Table 54. PHY XS Device Identifier: Upper 16 Bits (MDIO Device Address = 4, Register Address = 0x0002)                                                                                                            |    |

| Table 55. PHY XS Device Identifier: Lower 16 Bits (MDIO Device Address = 4, Register Address = 0x0003)                                                                                                            |    |

| Table 56. PHY XS Speed Ability (MDIO Device Address = 4, Register Address = 0x0004)                                                                                                                               |    |

| Table 57. PHY XS Devices in Package: Upper 16 Bits (MDIO Device Address = 4, Register Address = 0x0005)                                                                                                           |    |

| Table 59. PHY XS Status 2 Register (MDIO Device Address = 4, Register Address = 0x0008)                                                                                                                           | 63 |

| ble 60. PHY XS Package Identifier: Upper 16 Bits (MDIO Device Address = 4, Register Address = 0x000                                                                                        | )E) 63 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| ble 61. PHY XS Package Identifier Lower: 16 Bits (MDIO Device Address = 4, Register Address = 0x000                                                                                        |        |

| ble 62. PHY XS Lane Status (MDIO Device Address = 4, Register Address = 0x0018)                                                                                                            |        |

| ble 58. PHY XS Devices in Package Lower: 16 Bits (MDIO Device Address = 4, Register Address = 0x00                                                                                         |        |

| ble 63. 10GBASE-X PHY XS Test Control (MDIO Device Address = 4, Register Address = 0x0019)                                                                                                 |        |

| ble 64. PHY XS System Loopback Control (MDIO Device Address = 4, Register Address = 0xC000)                                                                                                |        |

| ble 65. NVR Control/Status Register (MDIO Device Address = 1, Register Address = 0x8000)                                                                                                   |        |

| ole 66. XENPAK Registers                                                                                                                                                                   |        |

| ole 67. Vendor Specific Registers                                                                                                                                                          |        |

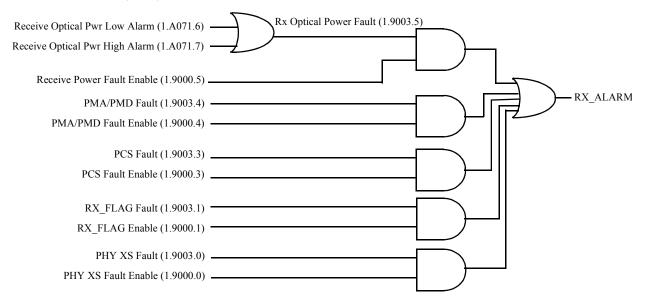

| ble 68. RX ALARM Control (MDIO Device Address = 1, Register Address = 0x9000)                                                                                                              |        |

| ble 69. TX ALARM Control (MDIO Device Address = 1, Register Address = 0x9001)                                                                                                              |        |

| ole 70. LASI Control (MDIO Device Address = 1, Register Address = 0x9002)                                                                                                                  |        |

| ble 71. RX_ALARM Status (MDIO Device Address = 1, Register Address = 0x9003)                                                                                                               |        |

| ble 72. TX_ALARM Status (MDIO Device Address = 1, Register Address = 0x9004)                                                                                                               |        |

| ble 73. LASI Status (MDIO Device Address = 1, Register Address = 0x9005)                                                                                                                   |        |

| ble 74. TX_FLAG Control (MDIO Device Address = 1, Register Address = 0x9006)                                                                                                               |        |

| ble 75. RX_FLAG Control (MDIO Device Address = 1, Register Address = 0x9007)                                                                                                               |        |

| ble 76. TX_FLAG Status (MDIO Device Address = 1, Register Address = 0xA070)                                                                                                                |        |

| ble 77. RX_FLAG Status (MDIO Device Address = 1, Register Address = 0xA071)                                                                                                                |        |

| ble 78. TX_FLAG Status 2 (MDIO Device Address = 1, Register Address = 0xA074)                                                                                                              |        |

| ble 79. RX_FLAG Status 2 (MDIO Device Address = 1, Register Address = 0xA075)                                                                                                              |        |

| ble 80. Digital Optical Monitoring Capability (MDIO Device Address = 1, Register Address = 0x807A)                                                                                         |        |

| ble 81. DOM Status Bits (MDIO Device Address = 1, Register Address = 0xA06E)                                                                                                               |        |

| ble 82. Extended DOM Capability (MDIO Device Address = 1, Register Address = 0xA06F)                                                                                                       |        |

| ble 83. Optional Digital Optical Monitoring Control/Status (MDIO Device Address = 1, Register Address                                                                                      |        |

| ble 84. Temperature Monitoring Registers                                                                                                                                                   |        |

| ble 85. Laser Bias Monitoring Registers                                                                                                                                                    |        |

| ble 86. Laser Output Power Monitoring Registers                                                                                                                                            |        |

| ble 87. Receive Optical Power Monitoring Registers                                                                                                                                         |        |

| ble 88. AEL2005 Mode Selection Register (MDIO Device Address = 1, Register Address = 0xC001)<br>ble 89. Transmit Configuration Register 1 (MDIO Device Address 1, Register Address 0xC002) |        |

| ble 90. Receive Configuration Register (MDIO Device Address 1, Register Address 0xC002)                                                                                                    |        |

| ble 91. XAUI Configuration Register: Upper 16 Bits (MDIO Device Address 1, Register Address = 1, Register Address = 0xC                                                                    |        |

| ble 92. XAUI Configuration Register: Lower 16 Bits (MDIO Device Address = 1, Register Address = 0xC                                                                                        |        |

| ble 93. XAUI Transmit Register: Upper 16 Bits (MDIO Device Address = 1, Register Address = 0xC00B)                                                                                         |        |

| ble 94. XAUI Transmit Register: Lower 16 Bits (MDIO Device Address = 1, Register Address = 0xC00C)                                                                                         | /      |

| ble 95. Power Supply Sensing Threshold Register (MDIO Device Address 1, Register Address 0xC00F).                                                                                          |        |

| ble 96. LOS Mask Register (MDIO Device Address = 1, Register Address = 0xC010)                                                                                                             |        |

| ble 97. Powerdown Register (MDIO Device Address = 1, Register Address = 0xC010)                                                                                                            |        |

| ble 98. TX DISABLE Register (MDIO Device Address = 1, Register Address = 0xC012)                                                                                                           |        |

| ble 99. Transmit Pre-emphasis Register (MDIO Device Address = 1, Register Address = 0xC014)                                                                                                |        |

| ble 100. Transmit Pre-emphasis Enable Register (MDIO Device Address = 1, Register Address = 0xC015                                                                                         |        |

| ble 101. Rate Adjustment Configuration Register (MDIO Device Address = 1, Register Address = $0xC010$                                                                                      |        |

| ble 102. Optional Settings Register (MDIO Device Address = 1, Register Address = 0xC017)                                                                                                   |        |

| ole 103. Transmit Configuration Register 2 (MDIO Device Address 1, Register Address 0xC018)                                                                                                |        |

| ble 104. Fault Mask Register (MDIO Device Address = 1, Register Address = 0xC019)                                                                                                          |        |

| ole 105. 10 Gbps Clock Output Swing Register (MDIO Device Address = 1, Register Address = 0xC01E)                                                                                          |        |

| ble 106. SGMII Configuration Register — (MDIO Device Address, Register Address = 0xC01F)                                                                                                   |        |

| ole 107. Programmable Rise Time Control Register (MDIO Device Address 1, Register Address 0xC02B)                                                                                          | )      |

| ole 108. Override Register 1 (MDIO Device Address 1, Register Address 0xC07A)                                                                                                              |        |

| ble 109. Embedded Micro-Controller Configuration Register                                                                                                                                  |        |

| ble 110. Embedded Micro-Controller EEPROM Address                                                                                                                                          |        |

| ble 111. Override Register 2 (MDIO Device Address 1, Register Address 0xC07B)                                                                                                              |        |

| ble 112. DOM Update Limit Register 1 (MDIO Device Address 1, Register Address 0xC07C)                                                                                                      |        |

| ble 113. DOM Update Limit Register 2 (MDIO Device Address 1, Register Address 0xC07D)                                                                                                      |        |

| ble 114. DOM Update Limit Register 3 (MDIO Device Address 1, Register Address 0xC07E)                                                                                                      |        |

| ble 115. Transmit Seed for 10 Gbps and XAUI PRBS Generators                                                                                                                                |        |

| Table 116. Logic Configuration Register (MDIO Device Address 1, Register Address 0xC202)   |     |

|--------------------------------------------------------------------------------------------|-----|

| Table 117. Logic Configuration Register (MDIO Device Address 1, Register Address 0xC20C)   |     |

| Table 119. Checksum Verification Register (MDIO Device Address 1, Register Address 0xC20F) |     |

| Table 120. GPIO and Activity LED Register (MDIO Device Address 1, Register Address 0xC214) |     |

| Table 118. SGMII Configuration Register (MDIO Device Address 1, Register Address 0xC20D)   |     |

| Table 121. GPIO and Activity LED Register (MDIO Device Address 1, Register Address 0xC215) |     |

| Table 122. LED Activity Truth Table Register                                               |     |

| Table 123. SDA/SCL Read/Write Registers                                                    |     |

| Table 124. BER Counter Registers                                                           |     |

| Table 125. Pattern Tester Receive Registers                                                |     |

| Table 126. Pattern Tester Transmit Registers                                               |     |

| Table 127. Error Slicer Threshold Register                                                 | 90  |

| Table 128. Initial / Override FFE Register                                                 | 91  |

| Table 129. Initial / Override DFE Register                                                 | 91  |

| Table 130. Initial / Override Flag FFE / DFE Register                                      | 91  |

| Table 131. Adaptation Observation Register                                                 | 91  |

| Table 132. AGCP Parameter Registers                                                        | 92  |

| Table 133. uC Control / Status Registers                                                   | 93  |

| Table 134. SFI DC and AC Characteristics                                                   | 96  |

| Table 135. XAUI SerDes Specifications                                                      |     |

| Table 136. CMU_REF Specifications                                                          | 101 |

| Table 137. CMOS I/O Specifications                                                         | 101 |

| Table 138. MDIO DC and AC Characteristics                                                  |     |

| Table 139. SDA/SCL DC and AC Characteristics                                               | 105 |

| Table 140. Power-on Timing Specifications                                                  | 107 |

| Table 141. Operating Conditions                                                            | 107 |

| Table 142. Absolute Maximum Ratings                                                        | 108 |

| Table 143. Boundary Scan Register Order                                                    | 113 |

| Table 144. Puma AEL2005 Ordering Information (PBGA Package)                                | 114 |

| Table 145. Puma AEL2005 Ordering Information (QFN Package)                                 | 114 |

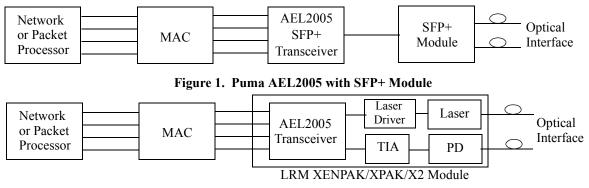

| Figure 1. Puma AEL2005 with SFP+ Module                                         |    |

|---------------------------------------------------------------------------------|----|

| Figure 2. Puma AEL2005 Inside the Optical Module                                |    |

| Figure 3. AEL2005 Transceiver Interfaces                                        | 4  |

| Figure 4. AEL2005 Block Diagram                                                 | 5  |

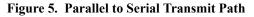

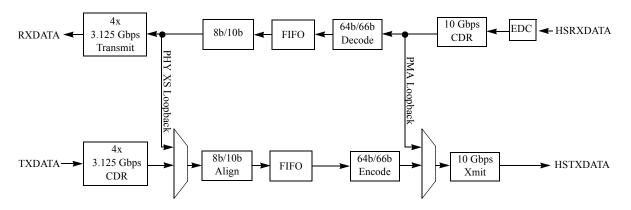

| Figure 5. Parallel to Serial Transmit Path                                      | 5  |

| Figure 6. Serial Output Transmitter                                             | 6  |

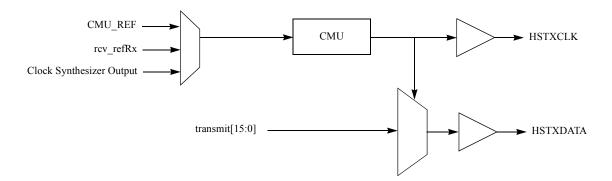

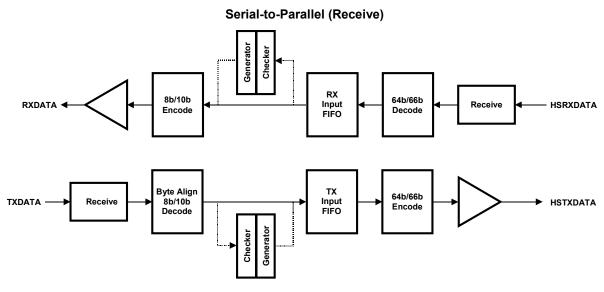

| Figure 7. Serial to Parallel Receive Path                                       | 7  |

| Figure 8. XAUI Parallel Transmit                                                | 9  |

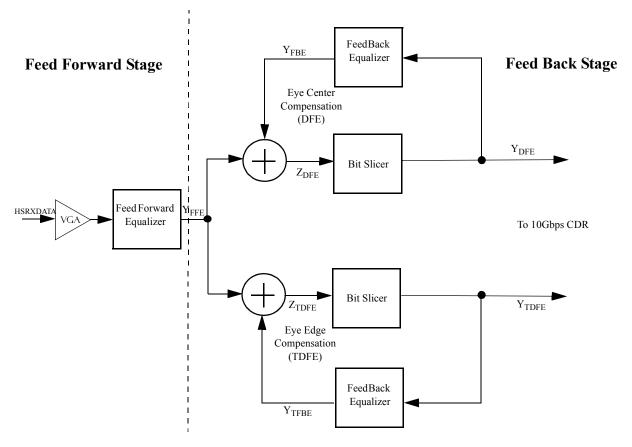

| Figure 9. Electronic Dispersion Compensation Block Diagram                      |    |

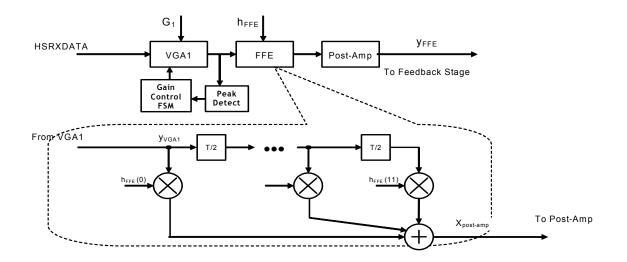

| Figure 10. Feed Forward Stage Block Diagram                                     | 11 |

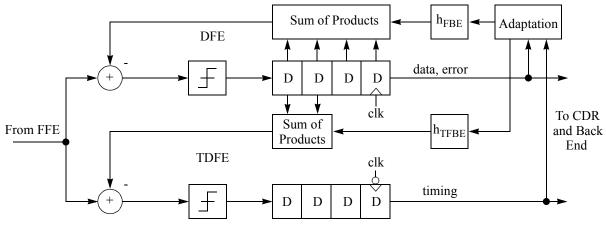

| Figure 11. Feed Back Stage Block Diagram                                        |    |

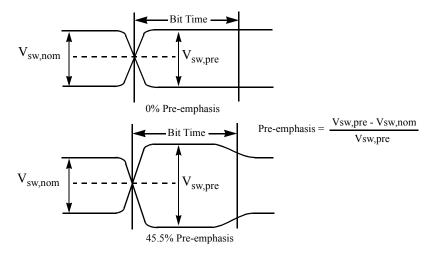

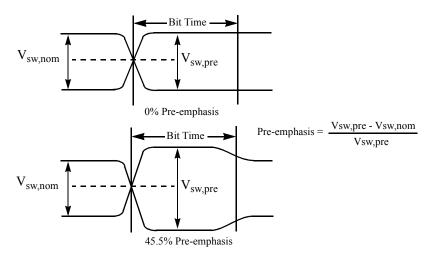

| Figure 12. Effects of Transmit Pre-emphasis                                     |    |

| Figure 13. Embedded Micro-Controller                                            |    |

| Figure 14. Link Alarm Status Interrupt Generation                               |    |

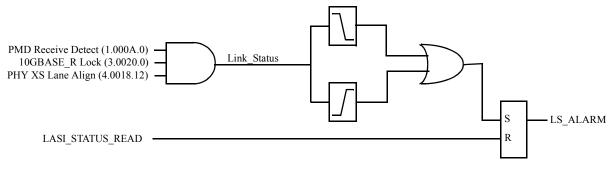

| Figure 15. LS_ALARM Generation                                                  |    |

| Figure 16. Transmit Alarm (TX_ALARM) Generation                                 |    |

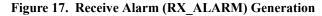

| Figure 17. Receive Alarm (RX_ALARM) Generation                                  |    |

| Figure 18. Power Supply Sensing Error Generation                                |    |

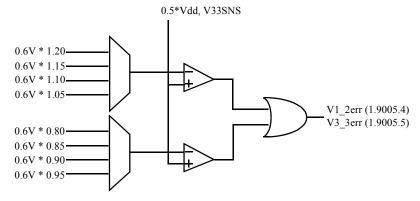

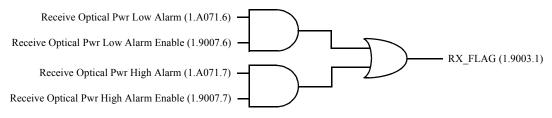

| Figure 19. Transmit Flag (TX FLAG) Generation                                   |    |

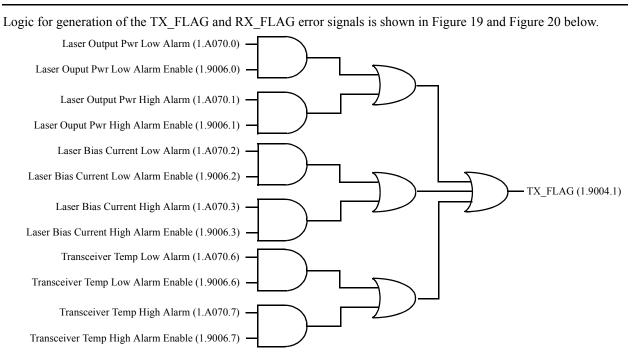

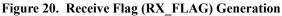

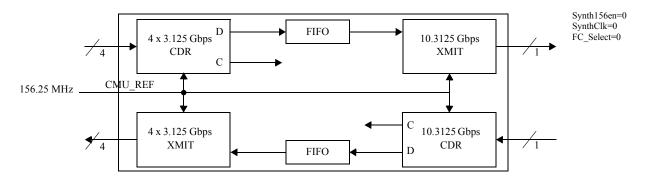

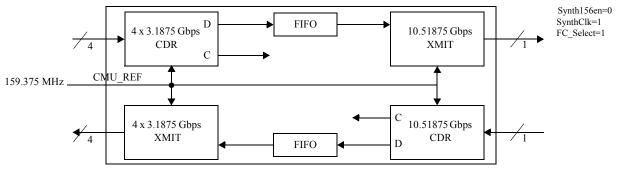

| Figure 20. Receive Flag (RX_FLAG) Generation                                    |    |

| Figure 21. Basic LAN Clocking Mode                                              |    |

| Figure 22. One XO SAN Clocking Mode (159.375 MHz)                               |    |

| Figure 23. One XO SAN Clocking Mode (156.25 MHz)                                |    |

| Figure 24. 50 MHz LAN Clocking Mode                                             |    |

| Figure 25. 50 MHz SAN Clocking Mode                                             |    |

| Figure 26. 50 MHz SGMII Clocking Mode                                           |    |

| Figure 27. System Loopback Modes                                                |    |

| Figure 28. PHY XS System Loopback Clocking Configuration                        |    |

| Figure 29. Line Loopback Modes                                                  |    |

| Figure 30. PMA Line Loopback Clocking                                           |    |

| Figure 31. Packet Generator & Checker Locations                                 |    |

| Figure 32. AEL2005 Example Configuration for Packet Generator & Checker Testing |    |

| Figure 33. MDIO Transaction Format                                              |    |

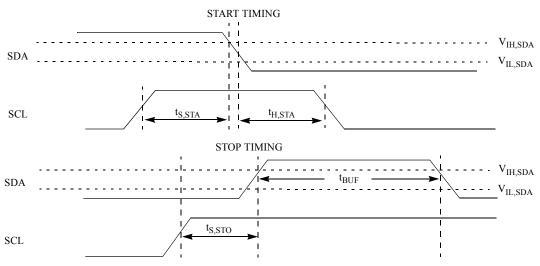

| Figure 34. SDA/SCL Serial Bus Symbols                                           |    |

| Figure 35. EEPROM Serial Read                                                   |    |

| Figure 36. EEPROM Page Write Sequence                                           |    |

| Figure 37. Clock Synchronization on the SDA/SCL Serial Bus                      |    |

| Figure 38. Arbitration on the SDA/SCL Serial Bus                                |    |

| Figure 39. SPI Operations                                                       |    |

| Figure 40. Voltage Parameter Definitions                                        |    |

| Figure 41. AC-coupled CML Output Equivalent Circuit                             |    |

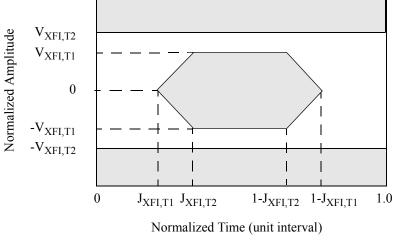

| Figure 42. High Speed CML Transmit Jitter Mask                                  | 95 |

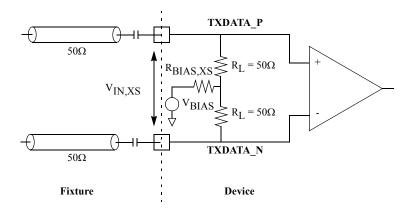

| Figure 43. Equivalent Input Circuit for XAUI Receiver                           |    |

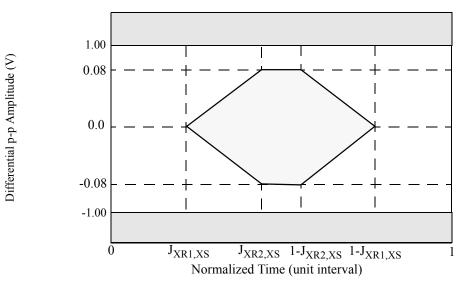

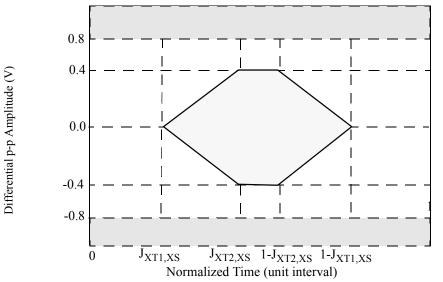

| Figure 44. Receive Eye Mask for XAUI Receiver                                   |    |

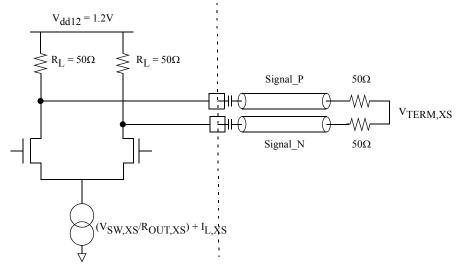

| Figure 45. CML AC-Coupled Equivalent Output Circuit                             |    |

| Figure 46. Effects of Transmit Pre-emphasis                                     |    |

| Figure 47. Transmit Eye Mask for SerDes Outputs                                 |    |

| Figure 48. CMU_REF Representative Circuit                                       |    |

| Figure 49. CMOS Clock Source Configuration                                      |    |

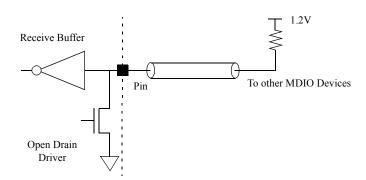

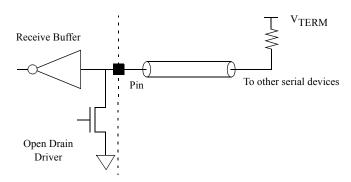

| Figure 50. Representative MDIO Circuit                                          |    |

| Figure 51. MDIO Input and Output Waveforms                                      |    |

|                                                                                 |    |

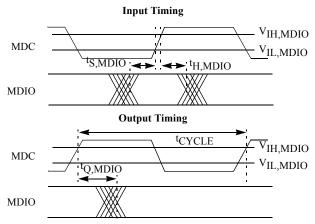

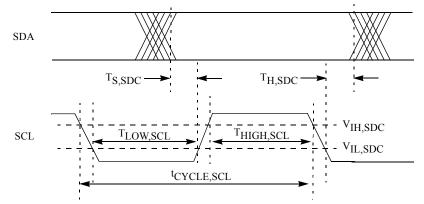

| Figure 52. Representative SDA/SCL Circuit          | 103 |

|----------------------------------------------------|-----|

| Figure 53. SDA/SCL Data Input and Output Waveforms |     |

| Figure 54. SDA/SCL Output Start and Stop Timing    | 104 |

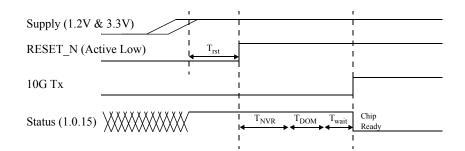

| Figure 55. Standard Power-On Sequence              | 106 |

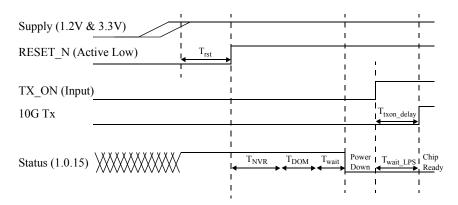

| Figure 56. LPS Power-On Sequence                   | 106 |

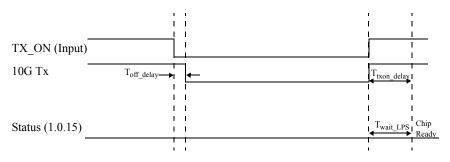

| Figure 57. TX_ON Timing Sequence                   | 106 |

| Figure 58. AEL2005 PBGA Package Drawing            | 109 |

| Figure 59. AEL2005 PBGA Package Pinout — Top View  | 110 |

| Figure 60. AEL2005 124-Pin QFN Package Drawing     | 111 |

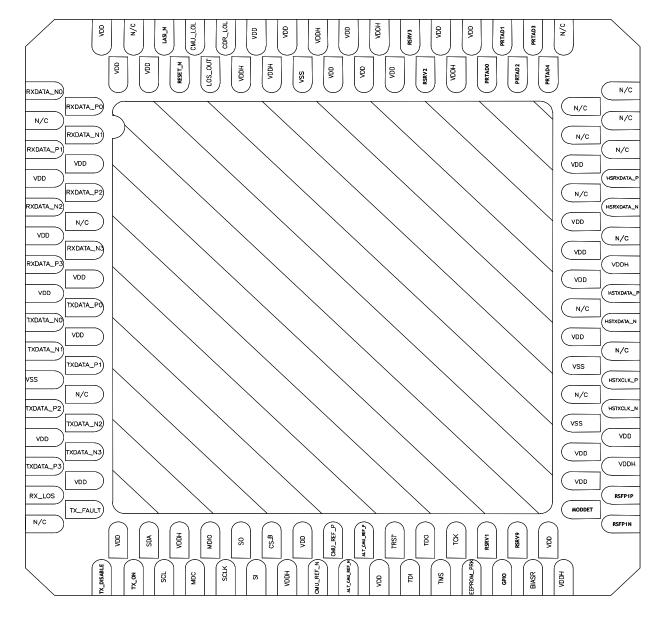

| Figure 61. AEL2005 Package Pinout                  | 112 |

# **1** Introduction

The Puma AEL2005 is a bidirectional single-channel 10 Gigabit Ethernet/10 Fibre Channel transceiver containing integrated EDC (Electronic Dispersion Compensation) circuits targeted for 10GBASE-LRM optical modules and 10Gbps SFP+ applications. The device also has a special SGMII mode which allows 1Gbps operation with SFP modules. The AEL2005 device offers an advanced combination of high performance and low power consumption. The consolidation of the receiver and transmitter physical layer (PHY) functions on a single chip is combined with the integration of an EDC block, integrated clock drivers, multiple loopback and PRBS for both the line side and the system side.

The high speeds and high integration of Puma make it the optimal choice for the SerDes device in XAUI-based transceiver designs. A flexible on-chip clock synthesis capability enables operation from a standard 156.25 MHz or 159.275 MHz crystal oscillator, or from a low-cost 50 MHz LVPECL or CMOS clock source. The CML serial interface supports a data rate of 10.3125 Gbps for datacom applications and 10.51875 for storage applications.

The Puma AEL2005 device is compliant with the following industry specifications:

- IEEE 802.3ae 10 Gigabit Ethernet

- IEEE 802.3aq 10 GBASE-LRM

- INCITS T11 10 Gigabit Fibre Channel

- XENPAK MSA, Revision 3.0

- X2 MSA, Revision 1.0b

- XPAK MSA, Revision 2.3

- SFP+ MSA, Draft Revision 2.2

# 2 Features and Benefits

| Feature                                             | Benefit                                         |  |

|-----------------------------------------------------|-------------------------------------------------|--|

| Minimal power consumption                           | Enables increased port density and less cooling |  |

| Integrated EDC                                      | Allows operation with linear SFP+ modules       |  |

| Advanced clock synthesis capability                 | Low-cost 50 MHz crystal oscillator support      |  |

| 1.2V and 3.3V power supplies                        | Dissipates very low power                       |  |

| On-chip clock generation and data recovery          | Simplifies system clocking                      |  |

| Programmable bit and lane ordering                  | Eases board layout                              |  |

| Programmable 10 Gbps rise time control              | Enhances data eye & power consumption           |  |

| XAUI adjustable transmit pre-emphasis               | Enables transmission across extended distances  |  |

| XAUI receive equalization                           | Enables transmission across extended distances  |  |

| 3-tap 10Gbps transmit pre-emphasis                  | Enables extended reach to SFP+ module           |  |

| Support for XENPAK DOM register set                 | Augments monitoring capabilities                |  |

| Special SGMII mode                                  | Allows operation with 1Gbps SFP modules         |  |

| Multiple loopback features                          | Improves testability                            |  |

| PRBS, IEEE and packet-based test pattern generation | Improves testability                            |  |

| MDIO interface for device control and configuration | Industry standard                               |  |

| SDA/SCL interface for EEPROM communication          | Industry standard                               |  |

| Traffic indicator LEDs                              | Improves testability and monitorability         |  |

| Direct byte-by-byte SDA/SCL bus control             | Enables design flexibility                      |  |

| 10x10 mm QFN Package with 0.5mm pad pitch           | Consumes minimal board space                    |  |

| 15x15 mm BGA Package with 1.0mm pad pitch           | Works with most PCB manufacturing processes     |  |

| 0.13 µm CMOS process                                | Enhanced power, cost, and integration           |  |

Table 1. Puma AEL2005 Features and Benefits

# **3** Applications

The Puma AEL2005 is ideal for use in high-speed 10 Gbps multi-mode fiber applications and either resides inside a XAUI module or on the linecard for SFP+ applications. For applications not requiring an integrated EDC, the AEL1002 device will provide an effective solution, while LAN/WAN applications can be addressed by the AEL1005 device.

Figure 2. Puma AEL2005 Inside the Optical Module

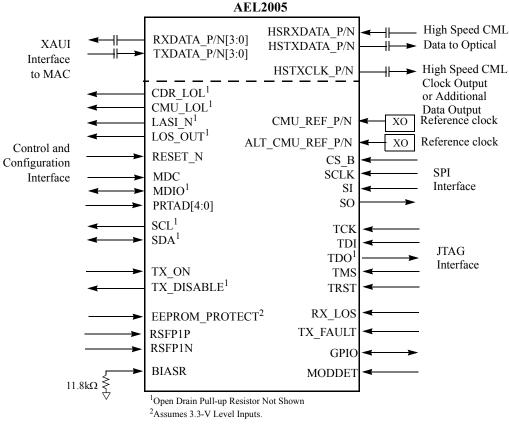

# **4** Functional Description

A top-level view of the AEL2005 transceiver is shown in Figure 3, outlining the general interfaces of the device. The high-speed data path, including the 10 Gbps interface to the optical device and the XAUI MAC interface, are shown at the top of the drawing above the dotted line. The clocking, control, and configuration interfaces are shown below the dotted line. Additional details regarding each pin are available in Section 14.

Figure 3. AEL2005 Transceiver Interfaces

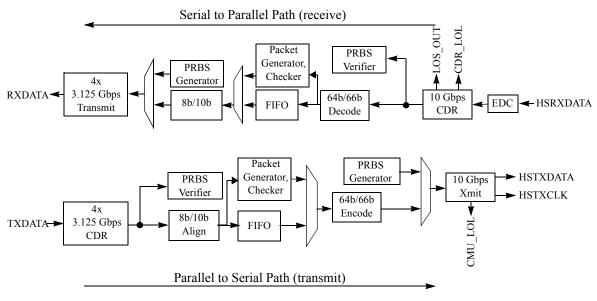

An overall block diagram of the AEL2005 is shown in Figure 4. The Parallel-to-Serial path includes four 3.125 Gbps receivers, decode/alignment logic, a FIFO, an output encoder, and a 10 Gbps transmitter/clock driver. The Serial-to-Parallel path contains an EDC block, 10 Gbps receiver, decode logic, a FIFO, parallel output encoding logic, and four 3.125 Gbps transmitters. The AEL2005 also contains a management data I/O (MDIO) interface for device control and configuration, an SDA/SCL interface for EEPROM communication, (SPI interface) and loopback modes for the parallel and serial interfaces. A variety of loopback paths are also available and described in more detail in Section 10. The following subsections describe each block in Figure 4.

Figure 4. AEL2005 Block Diagram

## 4.1 Parallel to Serial Path (Transmit)

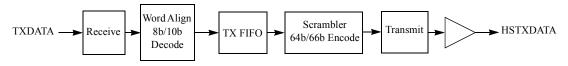

In normal operation, the AEL2005 receives parallel data on its four lane interface in XAUI format and retransmits it in serial fashion over the HSTXDATA pins. During this process, the incoming data has to be framed, aligned, and coded before transmission. An overall block diagram is shown in Figure 5. The function of each block is described in more detail in the following subsections.

#### 4.1.1 XAUI Parallel Receive

The first components in the receive path are the four XAUI data input receivers and clock recovery units. These function at 3.125 Gbps or 3.1875 Gbps data rates for Ethernet & Fibre Channel operation, respectively. These units are connected to the four differential TXDATA\_P/N[3:0] pairs and convert the four parallel streams into four 10-bit code words. The reference clock used for this is the external signal CMU\_REF.

#### 4.1.2 Word Align and Decode

The unaligned 10-bit words from the receive block are aligned and decoded before they are stored in the transmit input FIFO.

For each XAUI lane, the AEL2005 finds the 10-bit character boundary. The 10-bit character from each lane is converted into an 8-bit byte plus control information. The AEL2005 compares the control information from all four lanes to align the streams relative to one another and then writes the bytes into the transmit FIFO.

#### 4.1.3 10GBASE-R Scrambler/Encoder, FIFO, and Rate Adjustment

After alignment, data is read out of the transmit FIFO, scrambled, encoded with 64b/66b, and then sent to the serial output transmitter.

The AEL2005 device includes on-chip rate adjustment capability via the insertion and deletion of IEEE 802.3ae |I| XGMII idle characters. This feature allows the device to be run in full plesiochronous mode.

#### 4.1.4 Serial Output Transmitter

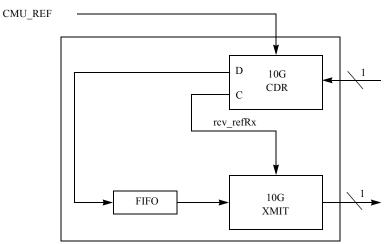

The serial output transmitter is shown in Figure 6 and is used to drive the HSTXDATA and HSTXCLK pins on the high speed CML interface. The CMU can take its reference clock from three sources: the external clock CMU\_REF, the rcv\_refRx clock from the serial receive block, or the output of the clock synthesizer. For 10GBASE-R, the reference is 156.25 MHz, so the CMU multiplies the frequency by 66 to produce its 10 GHz reference clock. For 10 Gigabit Fibre Channel, the reference is 159.375 MHz. This clock is used to clock out data on the HSTXDATA pins.

The HSTXCLK output clock can be configured in one of four ways:

- left turned off via the *pwrdnTranClock* bit in the Powerdown register at 1.C011 (default state).

- enabled to output the full frequency (10 GHz).

- set as a divide by 64 feedback clock using the *HSTXCLK\_src* bits in the Transmit Config 1 register (address 1.C002).

- Enabled to output 10Gbps data

The CML serial interface supports the 10.3125 Gbps data rate for Ethernet applications and the 10.51875 Gbps data rate for Fibre Channel applications.

The CML channel can also be configured to support a range of options regarding differential output voltage, as summarized in Section 15.7.

Figure 6. Serial Output Transmitter

| Mode                        | Reference                    | Input<br>Frequency | Output Frequency<br>(HSTXCLK) | Output Frequency<br>(HSTXCLK)<br>Divide by 64 Mode |

|-----------------------------|------------------------------|--------------------|-------------------------------|----------------------------------------------------|

| 10 Gigabit<br>Ethernet      | CMU_REF<br>Clock Synthesizer | 156.25 MHz         | 10.3125 GHz                   | 161.13 MHz                                         |

| 10 Gigabit<br>Fibre Channel | CMU_REF<br>Clock Synthesizer | 159.375 MHz        | 10.51875 GHz                  | 164.36 MHz                                         |

| Table 2. Ser | ial Transmit Clock | Frequencies |

|--------------|--------------------|-------------|

|--------------|--------------------|-------------|

## CMU Loss of Lock (CMU\_LOL)

The CMU\_LOL loss of lock signal is asserted whenever the multiplied frequency of the reference clock (CMU\_REF) and the output clock (HSTXCLK) differ by more than 1%.

## **Output Coupling for HSTXDATA and HSTXCLK**

The AEL2005 includes two high speed differential outputs: the 10 Gbps data transmit channel HSTXDATA and the 10 GHz output clock HSTXCLK. Both 10 Gbps signals on the AEL2005 device are designed to be AC coupled.

#### Output Data Transmission Enable & XENPAK Low Power Startup (LPS) Mode

The AEL2005 includes an active low CMOS input pin, TX\_ON, which serves as an enable for the high speed serial transmitter. When this pin is high, 10 Gbps transmission is enabled. When this pin is low, the AEL2005 device is placed into a global powerdown mode, and will dissipate less than 30 mW of power.

The TX\_ON also provides access to the XENPAK Low Power Startup (LPS) mode. After an AEL2005 power-on reset operation is complete, the AEL2005 device will perform NVR and DOM read operations as usual. Following those, if the TX\_ON signal is asserted, the AEL2005 device will start up in global powerdown mode. Upon de-assertion of TX\_ON, the reset controller will complete its operation, after which the AEL2005 will be ready to pass data.

# 4.2 Serial to Parallel Path (Receive)

The serial to parallel path transfers data from the high speed CML interface (HSRXDATA) to the XAUI interface (RXDATA). During normal operation, the AEL2005 receives serial data on its HSRXDATA pins, then demuxes, descrambles, re-encodes, and transmits the resulting data on the four differential RXDATA\_P/N[3:0] pairs. The exact operations depend on whether the part is configured to produce XAUI data, or is in loopback mode.

## 4.2.1 HSRXDATA Receive Channel

HSRXDATA is a 10 Gbps nominal data rate input. This channel can only be designed to be AC coupled. The EDC block cleans up any ISI in the received signal while the Clock and Data Recovery (CDR) unit for the AEL2005 samples HSRXDATA at the center and edges of the data eye, tracks any variations in its rate, and demultiplexes the incoming serial stream into a lower frequency parallel stream. This unit has a number of properties:

• The frequency of the incoming data can vary by up to t<sub>TOL,HSRX</sub> parts per million (Table 134) from the multiplied frequency of the reference clock CMU\_REF.

| Mode                     | Reference                   | Frequency   |

|--------------------------|-----------------------------|-------------|

| 10 Gigabit Ethernet      | CMU_REF<br>Clock Syntheizer | 156.25 MHz  |

| 10 Gigabit Fibre Channel | CMU_REF<br>Clock Syntheizer | 159.375 MHz |

| Table 3. | Serial | Receive | Clock | Frequencies |

|----------|--------|---------|-------|-------------|

|----------|--------|---------|-------|-------------|

#### Loss of Signal (LOS\_OUT)

The LOS of Signal (LOS\_OUT) pin is asserted when the incoming signal amplitude on the HSRXDATA line is below a specified threshold during a 20 us period or when the RX\_LOS input indicates an upstream loss of signal. The LOS detector is deasserted when the incoming amplitude rises above a hysteresis threshold to avoid LOS toggling on noise. The LOS assert and deassert thresholds are programmable LOSthresh[5:0] and LOSthreshhyst[5:0] in register 1.C010 shown in Table 96. The voltages indicated are the comparison thresholds at the output of the LOS peak detector.

#### CDR Loss of Lock (CDR\_LOL)

The CDR\_LOL signal is asserted whenever the CMU\_REF reference clock and the divided-down recovered clock differ by more than 270 ppm.

#### 4.2.2 64b/66b Serial Descramble/Decode, Alignment, Receive FIFO

Data from the HSRXDATA pins enters the front end decoding/descrambling block and is processed and stored in the receive FIFO. 10GBASE-R systems employ scrambling and 64b/66b encoding on the data input stream. The data is descrambled and written to the FIFO.

Rate adjustment support for insertion and deletion of IEEE 802.3ae |I| XGMII idle characters is also included in the receive path, allowing the device to be run in full plesiochronous mode.

#### 4.2.3 Receive 8b/10b Encoding

After alignment, one byte is read from the FIFO each cycle and encoded by the 8b/10b logic. The resulting 10-bit value is sent to the XAUI transmitter.

#### 4.2.4 XAUI Parallel Transmit

The final components in the parallel output path are the four 3.125 Gbps data output drivers. Figure 8 shows a simplified block diagram of the XAUI parallel interface. For simplicity, only one of the four channels is shown. The other three channels are identical.

These channels can also be configured to support a range of options regarding pre-emphasis and differential output voltage.

Figure 8. XAUI Parallel Transmit

#### 4.3 EDC (Electronic Dispersion Compensation) Functionality

A multi-mode fiber (MMF) disperses the light from a laser, such that an optical pulse is split into multiple paths ("modes") traveling at different speeds through the fiber, yielding multiple pulses that arrive at the receiver at different times. At 10Gbps data rates, the spread of these additional arrivals around the fundamental mode (the primary path carrying the most optical energy) can cause significant inter-symbol interference (ISI), preventing accurate recovery of the signal. Each transmitted symbol causes pre-cursor ISI to the preceding symbols due to stray modes that travel faster than its fundamental mode. It also causes post-cursor ISI to the subsequent symbols, due to the modes traveling slower than the fundamental mode. The EDC function in AEL2005 cancels out these effects, allowing customers to deploy 10GbE using their existing installed base of multi-mode fiber.

Figure 9 shows the EDC block diagram. It consists of a feed forward equalizer stage (FFE) to cancel the pre-cursor ISI, and a decision feedback equalizer stage (DFE) to cancel out post-cursor ISI. Both stages are self-adaptive, allowing the AEL2005 to adapt to a variety of MMFs with even time-varying dispersive conditions automatically. Note that the AEL2005 includes separate branches in the feedback stage to accurately compensate for signal distortions at the center of the data eye, as well as the edge of the data eye.

Figure 9. Electronic Dispersion Compensation Block Diagram

#### 4.3.1 Feed Forward Stage

The feed forward stage is shown in Figure 10. It consists of a feed forward equalizer (FFE), situated between a preamplification stage and a post-amplification stage.

The pre-amplification stage consists of a variable gain amplifier (VGA1), while post-amplification is performed by a cascaded amplifier pair. The gain level of the pre-amplification stage is controlled by digitally tuned gain level  $G_1$ . VGA1 is designed to provide the FFE with an ample input signal level while maintaining linearity, while the post-amplification stage yields sufficient range of gain, to compensate for attenuation in the signal as it passes through the FFE. The FFE is a fractional (T/2) adaptive finite impulse response (FIR) filter, made up of a 12-tap delay line with digitally tuned h<sub>FFE</sub> coefficients.

Figure 10. Feed Forward Stage Block Diagram

It is set to T/2 nominally, where T represents the symbol interval. This provides a high degree of adaptation flexibility. The FIR filter coefficients are adapted using a proprietary variant of the least-mean-squared (LMS) algorithm, designed to cancel distortions caused by the laser transmitter, the channel and the detector, while also removing pre-cursor ISI for the signal. In general, pre-cursor ISI is eliminated from the signal when it leaves the feed forward stage.

#### 4.3.2 Feedback Stage

The feedback stage contains separate branches to correct for post-cursor ISI at the center, as well as at the edge of the data eye, with the former (the DFE, or data branch) ensuring accurate symbol detection, and the latter (the TDFE, or timing branch) reducing jitter in the CDR's recovered clock output.

The block diagram of the feedback stage is shown in Figure 11. The eye-center correction branch (DFE) contains a feedback equalizer (FBE, a 4-tap filter). The filter co-efficients  $h_{FBE}$  are digitally tuned and are adapted using a proprietary LMS type algorithm to minimize the data error.

The eye-edge timing compensation branch (TDFE) produces a signal that enables the CDR unit to perform accurate clock recovery. It similarly contains a decision feedback equalizer (TFBE, a 4-tap filter). The co-efficients  $h_{TFBE}$  are digitally tuned and adapted using a proprietary LMS type algorithm to cause the zero crossings to coincide with the edge of the data eye.

Figure 11. Feed Back Stage Block Diagram

#### 4.3.3 EDC Adaptation

The EDC adaptation consists of a carefully sequenced multi-step process which is controlled by the on-chip adaptation controller block. The purpose of the adaptation controller is to initialize adaptation settings such as feedforward equalizer filter coefficients and gain targets at a good point when the chip is brought out of reset. Adaptation parameters such as FFE, FBE and TFBE coefficients and VGA gain are updated continuously to account for changes in the operating environment ( power supply and temperature) and channel conditions over time at a rate of 10s of Hz.

A variety of registers control adaptation initialization and timing. The error slicer threshold in 1.C503 is used by the LMS algorithm to calculate the adaptation error at a given point in time. The front-end VGA peak target (at the VGA)

output) is set in (1.C847 to maintain a good signal level into the feedforward equalizer as a compromise between noise

and linearity and will be set based on ROSA chacteristics. The feedforward equalizer coefficients can be initializeded at the start of adaptation in 1.C620-1.C62C to provide a good starting filter response.

The adaptation microcode which will be provided by Aeluros in 1.C800-1.C820 controls the timing of coefficient and gain updates to ensure correct tracking of changing conditions. The equalizer coefficients may be read back in 1.C62D - 1.C636 to determine where the equalizer has landed.

# 5 10G Transmit Pre-emphasis

The AEL2005 device supports transmit pre-emphasis on the 10G transmitter. There are 3 taps of pre-emphasis which are controlled from the 1.C014 and 1.C015 registers.

Figure 12. Effects of Transmit Pre-emphasis

The effects of pre-emphasis have been shown above. The 3 taps equate to pre, post and main tap of pre-emphasis. When pre-emphasis is turned off the main tap is added to the pre and post tap without any inversion. When pre-emphasis is turned on the side taps are shifted in time and have sign inversion.

The pre and post taps have 5 bits of programmability and the main tap have 6 bits of programmability.

# 6 SGMII Mode

The AEL2005 supports two 1.25Gbps SGMII low latency pass-thru channels, which can be configured through registers 1.C01F and 1.C220. The HSRXDATA\_P/N and the HSTXDATA\_P/N pins serve as the input and output ports of channel0 on the network side, while RSFP1\_P/N and HSTXCLK\_P/N pins serve similar functions for channel 1. On the system side, any Xaui lane can be configured as the system interface for either of the two channels.

The register used for configuring SGMII mode is described in Table 106.

# 7 **On-Chip Micro-Controller**

Sabercat contains a proprietary on-chip micro-controller (uC). It is designed to be used for internal management tasks within the chip, and is generally not available for user applications.

# 7.1 uC Block Diagram

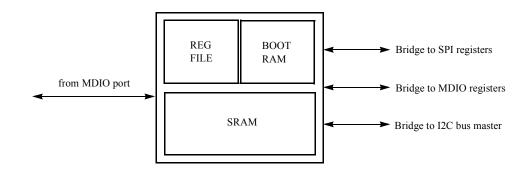

Figure 13. Embedded Micro-Controller

A block diagram for the embedded micro-controller is shown in Figure 13. As shown, the micro-controller consists of a *boot memory* and an *embedded SRAM* in addition to the program register file. The boot memory contains a hardwired boot program which, upon power up, may be configured to automatically load additional firmware from an external EEPROM into the embedded SRAM. This newly loaded firmware subsequently executes out of the SRAM, making the boot memory available for use as a scratch space or as a stack. Sixteen program registers are available for use by the firmware.

All state information within the uC can be accessed from the chip's MDIO port. This includes inspecting and altering the boot program, the SRAM content, and all program registers in the controller.

The uC module has access to every SPI and MDIO register in the chip, as well as its I2C bus. As such, uC may be used to perform a variety of tasks, such as:

- Patching configuration register (beyond the C000 C07F range)

- Monitoring status registers and taking corrective actions (e.g. EDC parameter optimization)

All MDIO/SPI/I2C accesses issued by uC go through an arbitrator unit to ensure that they can proceed concurrently with accesses coming from the MDIO/SPI ports, without causing any conflicts.

# 7.2 uC Configuration

By default, the uC is held in reset upon power up. Its subsequent behavior is determined by two configuration registers (mapped to MDIO registers 1.C04A and 1.C04B), which may be modified either through the I2C patch process or via MDIO write operations. These registers are defined in Table 109 and Table 110.

To enable the embedded micro-controller, 1.C04A.15 should be cleared to 0. This initiates the boot process, where the hardwired boot program fetches additional instructions from an external EEPROM into its on-chip SRAM, using

the patchable parameters *uc\_eepaddr* (1.C04B) and *uc\_eepsize* (1.C04A.7:4). Subsequently, program flow is transferred to the newly loaded program.

# 7.3 uC Control and Status

All internal states of the on-chip micro-controller can be accessed through MDIO registers. Several registers of particular interest are shown in Table 133. Note however that these registers are accessible only when the uC is enabled (1.C04A.15 = 0).

The program counter contains the current instruction pointer. When the micro-controller is running, the value of the program counter should change periodically when read via MDIO.

The PAUSE and SSTEP bits can be used to place the micro-controller into a single-step operation mode. When the PAUSE bit is set to 1, the execution of the firmware is stopped. Subsequently, the user may cause n more instructions to be executed, by writing the integer n into the SSTEP register. The status bit PAUSED returns 1 whenever program execution is stopped. For debug purposes, the micro-controller may also be configured to immediately enter single-step mode (PAUSED) when enabled. This is accomplished by setting 1.C04A.14 to 1 before enabling the micro-controller.

The firmware for the microcontroller on the AEL2005 can also be downloaded directly into the device either through MDIO or by using the SPI interface on an external microcontroller.

# 8 GPIO Interface

AEL2005 has 4 configurable GPIO pins, which are CDR\_LOL (B5), CMU\_LOL (B4), MODDET (N13) and GPIO (N11). These pins can be programmed into inputs, outputs or LED drivers according to specific applications.

1.C214 contains control and status bits for the 4 GPIO pins (4 bits for each lane), as shown in Table 120. Table illustrates all available operation modes. Writing 0x0 to any lane will not change its operation mode. For example, if some one writes 0xA000 to 0.C214 to configure lane 3 (pin N11), the other three GPIO pins won't be affect by this write. GPIO status is accessible by reading 1.C214. Table 4 shows definitions of status bits.

To simplify the scenario, only describes one of the common ways of using these GPIO pins: CDR\_LOL and CMU\_LOL drive status LEDs; MODDET monitors SFP+ MOD\_ABS signal; GPIO controls SFP+ rate select pin RS0 and RS1. However, all of these functions can be extended to any other lanes.

## 8.1 LED Drivers

By setting GPIO control register 1.C214 to 0x0099, CMU\_LOL (B4) and CDR\_LOL (B5) are configured to drive external LED indicators. The integrated truth tables define the meaning of LED indicators. 1.C216 (LED0\_TT) contains the truth table index for CDR\_LOL, while 1.C217 (LED1\_TT) contains the truth table index for CMU\_LOL. As shown in Table 1, the truth table index is defined by the variable {rx\_status, rx\_active, tx\_status, tx\_active}. A LED is light on when the conditions that corresponds to bit '1' in the truth table are satisfied. Two examples are given in the following.

|               |                 | tx_status = 1 |               | tx_status = 0 |               |  |

|---------------|-----------------|---------------|---------------|---------------|---------------|--|

|               |                 | tx_active = 1 | tx_active = 0 | tx_active = 1 | tx_active = 0 |  |

| rx_status = 1 | $Rx_active = 1$ | Led_TT[15]    | Led_TT[14]    | Led_TT[13]    | Led_TT[12]    |  |

|               | $Rx_active = 0$ | Led_TT[11]    | Led_TT[10]    | Led_TT[9]     | Led_TT[8]     |  |

| rx_status = 0 | $Rx_active = 1$ | Led_TT[7]     | Led_TT[6]     | Led_TT[5]     | Led_TT[4]     |  |

|               | $Rx_active = 0$ | Led_TT[3]     | Led_TT[2]     | Led_TT[1]     | Led_TT[0]     |  |

Table 4. Encoding of LED Indicators

## 8.1.1 Example 1: Configure CDR\_LOL Pin to Indicate Link-up Status

In this case, LED needs to turn ON when both tx\_status and rx\_status are TRUE (ignoring the state of tx\_active and rx\_active). Therefore, bits 15, 14, 11, and 10 of the corresponding led0\_TT register (1.C216) should be set to 1 as shown in the table below, indicating that the LED is ON whenever tx\_status = 1 and rx\_status = 1, and OFF otherwise. In other words, led0\_TT (1.C216) = 0b1100\_1100\_0000\_0000 = 0xcc00.

|               |                 | tx_status = 1 |               | tx_status = 0 |               |  |

|---------------|-----------------|---------------|---------------|---------------|---------------|--|

|               |                 | tx_active = 1 | tx_active = 0 | tx_active = 1 | tx_active = 0 |  |

| rx_status = 1 | $Rx_active = 1$ | 1             | 1             | 0             | 0             |  |

|               | $Rx_active = 0$ | 1             | 1             | 0             | 0             |  |

| rx_status = 0 | $Rx_active = 1$ | 0             | 0             | 0             | 0             |  |

|               | $Rx_active = 0$ | 0             | 0             | 0             | 0             |  |

| Table 5  | Configuring CDR | LOL Pin to Indicate Link-up Status   |

|----------|-----------------|--------------------------------------|

| Table 5. | Configuring CDR | LOL I III to Indicate Link up Status |

#### 8.1.2 Example 2: Configure CMU\_LOL Pin to Indicate Traffic Activity

In this case, the LED needs to turn ON when both tx\_active and rx\_active are TRUE (ignoring the state of tx\_status and rx\_status). Therefore, bits 15, 13, 7 and 5 of 1.C216 should be set to 1, indicating that the LED is ON whenever tx\_active = 1 and rx\_active =1, and OFF otherwise. In other words,  $led1_TT(1.C217) = 0b1010_0000_1010_0000 = 0xa$ .

|               |                 | tx_status = 1 |               | tx_status = 0 |               |  |

|---------------|-----------------|---------------|---------------|---------------|---------------|--|

|               |                 | tx_active = 1 | tx_active = 0 | tx_active = 1 | tx_active = 0 |  |

| rx_status = 1 | $Rx_active = 1$ | 1             | 0             | 1             | 0             |  |

|               | $Rx_active = 0$ | 0             | 0             | 0             | 0             |  |

| rx_status = 0 | $Rx_active = 1$ | 1             | 0             | 1             | 0             |  |

|               | $Rx_active = 0$ | 0             | 0             | 0             | 0             |  |

Table 6. Configuring CMU\_LOL Pin to Indicate Traffic Activity

#### **8.2 MODDET Input**

MOD\_ABS is an output from the SFP+, which is asserted low when modules are inserted. (Note that a pull-up resistor is required on the system side for MOD\_ABS) In many cases, it is useful to generate an interrupt on LASI signal when module presence is changed. AEL2005 supports this feature with its GPIO pins. Not only can all GPIO pins be configured to inputs, users can also choose the interrupt mode. The available options are: no interrupt; raise interrupt on any state transition; raise interrupt on 1 to 0 transition; raise interrupt on 0 to 1 transition. The interrupt status for each lane is available at 1.C215:3:0. By writing "1101" to the corresponding control bits in 1.C214, LASI will be de-asserted. Note that LASI is not clear-after-read in this case.

For instance, one could connect MOD\_ABS to MODDET (N13) and set GPIO control register 1.C214 to 0x0200. In this way, the MODDET (N13) pin is configured to input and it generates an interrupt to LASI both when SFP+ is inserted or removed. The input value is available at bit 8 of 1.C214. After an interrupt is issued, 1.C215 bit 2 will become and stay '1'. LASI and the status bit won't be cleared until one writes "1101" to 1.C214.11:8.

## 8.3 Rate Select Output

SFP+ requires control signals to select operation rate via RS0 and RS1. By setting GPIO control register 1.C214 to 0xa000/0xb000, the GPIO (N11) pin of AEL2005 drives '0'/'1' statically.

\* Mapping between internal signals and pin number: gpio0->CDR\_LOL(B5), gpio1 ->CMU\_LOL(B4), gpio2->MODDET(N13), gpio3->GPIO(N11)

| Write gpio_ctrl with<br>this value | Operating Mode                                         |

|------------------------------------|--------------------------------------------------------|

| 0000                               | No change to operating mode, data or interrupt states. |