# EntréPad AES2510 FINGERPRINT SENSOR Product Family Specification For Serial or Parallel Interface Applications

AuthenTec, Inc.

Post Office Box 2719

Melbourne, Florida 32902-2719

321-308-1300

www.authentec.com

AuthenTec welcomes your suggestions. We try to make our publications useful, interesting, and informative, and we hope you will take the time to help us improve them. Please send any comments or suggestions by mail or e-mail.

#### **Disclaimer of Warranty**

AUTHENTEC SOFTWARE, INCLUDING INSTRUCTIONS FOR ITS USE, IS PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND. AUTHENTEC FURTHER DISCLAIMS ALL IMPLIED WARRANTIES INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR OF FITNESS FOR A PARTICULAR PURPOSE. THE ENTIRE RISK ARISING OUT OF THE USE OR PERFORMANCE OF THE SOFTWARE AND DOCUMENTATION REMAINS WITH YOU.

IN NO EVENT SHALL AUTHENTEC, ITS AUTHORS, OR ANYONE ELSE INVOLVED IN THE CREATION, PRODUCTION, OR DELIVERY OF THE SOFTWARE BE LIABLE FOR ANY DAMAGES WHATSOEVER (INCLUDING, WITHOUT LIMITATION, DAMAGE FOR LOSS OF BUSINESS PROFITS, BUSINESS INTERRUPTION, LOSS OF BUSINESS INFORMATION, OR OTHER PECUNIARY LOSS) ARISING OUT OF THE USE OF OR INABILITY TO USE THE SOFTWARE OR DOCUMENTATION, EVEN IF AUTHENTEC HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. BECAUSE SOME STATES OR COUNTRIES DO NOT ALLOW THE EXCLUSION OR LIMITATION OF LIABILITY FOR CONSEQUENTIAL OR INCIDENTAL DAMAGES, THE ABOVE LIMITATION MAY NOT APPLY TO YOU.

#### **U.S. Government Restricted Rights**

AuthenTec software and documentation are provided with RESTRICTED RIGHTS. Use, duplication, or disclosure by the government is subject to restrictions as set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013 or subparagraph (c)(1) and (2) of the Commercial Computer Software – Restricted Rights 48 CFR 52.227-19, as applicable. Manufacturer is AuthenTec, Inc.; Melbourne, Florida 32901-2719. This Agreement is governed by the laws of the State of Florida.

AuthenTec, Inc.

Post Office Box 2719

Melbourne, Florida 32902-2719

321-308-1300

www.authentec.com

apps@authentec.com

AuthenTec, FingerLoc, EntréPad, Aware, AES2510, AES3550, AES4000, AF-S2, ISX, TruePrint, the AuthenTec colophons and logotypes, and the phrase "Personal Security for the Real World" are trademarks of AuthenTec, Inc. Microsoft and Windows 98 are registered trademarks of Microsoft Corp. Microwire™ is a trademark of National Semiconductor Corp. SPI™ is a registered trademark of Motorola. All other trademarks are the property of their respective owners.

#### **Product Specification for the AES2510 Fingerprint Sensor**

Copyright ©2004 by AuthenTec, Inc. No part of this publication may be reproduced in any form or by any means without prior written permission. Printed in the United States of America.

# **Table of Contents**

| 1.   | INTRO            | DUCING THE ENTRÉPAD AES2510 SLIDE SENSOR                                                                     | 6        |

|------|------------------|--------------------------------------------------------------------------------------------------------------|----------|

| -    |                  | JEPRINT TECHNOLOGY IS                                                                                        |          |

|      |                  | TURE SUMMARY                                                                                                 |          |

|      |                  | ERATIONAL DESCRIPTION                                                                                        |          |

|      |                  | DLE MODE                                                                                                     |          |

| -    |                  | MAGING MODE                                                                                                  |          |

|      |                  | /IGATION USING THE AES2510                                                                                   |          |

|      |                  | de 1 (NAV) – cursor control mode                                                                             |          |

|      |                  | de 2 (NAVI) – graphical navigation mode                                                                      |          |

| 2.   | DC ELE           | CTRICAL CHARACTERISTICS                                                                                      | 11       |

| 2    |                  | SOLUTE MAXIMUM RATINGS                                                                                       |          |

|      |                  | COMMENDED OPERATING CONDITIONS                                                                               |          |

| 2    | 2.3 DC           | CHARACTERISTICS @ RECOMMENDED OPERATING CONDITIONS                                                           | 12       |

| 3.   | SENSO            | R OPERATION                                                                                                  | 13       |

|      |                  | ERATION DESCRIPTION                                                                                          |          |

|      |                  |                                                                                                              |          |

| 4. F | PIN DEFII        | NITIONS                                                                                                      | 14       |

| 4    | .1 Pac           | KAGING INFORMATION                                                                                           | 14       |

| 4    |                  | LIST                                                                                                         |          |

|      | 4.2.1            | Pin Type and Activity Definitions                                                                            |          |

|      |                  | DESCRIPTIONS (ALPHABETICAL LISTING)                                                                          |          |

| 4    |                  | OCK SELECT CONTROL                                                                                           |          |

|      | 4.4.1            | Clock Specification                                                                                          |          |

| 1    |                  | RING INFORMATION                                                                                             |          |

| 4    | 4.5.1            | Imaging Scan Timing / Frame Rates:                                                                           |          |

|      | 4.5.2            | Finger Detect Auto-calibration                                                                               |          |

|      |                  | Г                                                                                                            |          |

| 4    |                  |                                                                                                              |          |

|      |                  | 2510 Start-up:                                                                                               |          |

| 5.   | SYSTE            | M INTERFACE DESCRIPTIONS                                                                                     | 22       |

| 5    | 5.1 INTI         | ERFACE SELECT CONTROL                                                                                        | 22       |

| 5    | 5.2 As\          | NCHRONOUS SERIAL INTERFACE                                                                                   |          |

|      | 5.2.1            | Asynchronous Serial Interface RTR Response                                                                   | 25       |

|      | 5.2.2            | Asynchronous Protocol                                                                                        |          |

| 5    |                  | ICHRONOUS SERIAL INTERFACE [SSI]                                                                             |          |

|      | 5.3.1            | Synchronous Serial Interface Description                                                                     |          |

|      | 5.3.2            | Synchronous Serial Receive/Transmit Interface Timing                                                         |          |

|      | 5.3.3<br>5.3.4   | Synchronous Serial Interrupt behaviorSPI and McBSP Compatible M/S Synchronous Serial Interface Specification | 30<br>21 |

|      | 5.3.4<br>5.3.4.1 |                                                                                                              | 31<br>21 |

|      |                  | AES2510 to CPU Transfers                                                                                     |          |

| 5    |                  | T Parallel Interface                                                                                         |          |

| _    |                  | MPLE HARDWARE CHECKOUT COMMUNICATION SEQUENCE                                                                |          |

| _    | 5.5.1            | Initialization                                                                                               |          |

|      | 5.5.2            | Read Registers Sequence                                                                                      | 38       |

| 6.   | DATA F           | ORMATS                                                                                                       | 40       |

| 6.1    | Overview                                 | 40 |

|--------|------------------------------------------|----|

| 6.1.   | 1 Registers Message Format               | 41 |

| 6.1.2  | 2 Image Data Format – Grey Scale 500 ppi | 41 |

| 6.1.3  |                                          |    |

| 6.1.4  | 4 Image Data Format – Monochrome         | 43 |

| 6.1.3  | 5 Histogram Message Format               | 44 |

| 6.1.6  |                                          |    |

| 6.2    | SENSOR I/O                               | 46 |

| 6.2.   | 1 Control Registers                      | 46 |

| 6.2.2  | 2 Sensor ID Message                      | 46 |

| 6.2.3  | 3 Register Message                       | 46 |

| 6.2.4  | 4 Image Message                          | 47 |

| 6.2.3  | 5 Authentication Word Message            | 49 |

| 6.2.6  |                                          |    |

| 6.2.   |                                          |    |

| 6.2.8  |                                          |    |

| 6.2.9  | 9 SensorID Message                       | 49 |

| 7. SOF | TWARE INTERFACE DETAILS                  | 50 |

| 7.1    | REGISTER MAP                             | 50 |

| B. PAR | RT NUMBERING SCHEME                      | 52 |

|        | WOLON LUCTORY                            | 50 |

## **LIST OF FIGURES**

| Figure 1-1 Co                  | olumn and Row Numbering                                          | 7        |

|--------------------------------|------------------------------------------------------------------|----------|

| Figure 1-2 Cu                  | ursor Control Navigation                                         | 9        |

| Figure 2-1 Ab                  | solute Maximum Ratings                                           | 11       |

| Figure 2-2 Re                  | ecommended Operating Conditions                                  | 11       |

|                                | C Characteristics                                                |          |

| Figure 3-1 AE                  | S2510 Functional Diagram                                         | 13       |

| Figure 8 48                    | BGA Thick Style                                                  | 15       |

| Figure 4-4 Pi                  | n List by Interface                                              | 17       |

| Figure 4-5 AE                  | S2510 Active Pin Functional Description                          | 18       |

| Figure 4-6 Ex                  | ternal Clock Specifications                                      | 20       |

|                                | SEL[1:0] Decode                                                  |          |

| Figure 5-2 SI                  | O Pin Definitions for each Selected Interface Option             | 22       |

|                                | ynchronous Interface diagram                                     |          |

|                                | ynchronous Serial Interface Signal Descriptions                  |          |

| •                              | (D low duration for Autobaud                                     |          |

|                                | FR Response Timing Diagram                                       |          |

|                                | ynchronous Serial Timing Diagram – One Byte                      |          |

|                                | SI-compatible Interface Diagram                                  |          |

|                                | ynchronous Serial Interface IO Port Assignment                   |          |

|                                | eceive/Transmit Interface, SPI-compatible mode, SSI_NORM = 1     |          |

|                                | SI Receive/Transmit Timing Parameters, SSI_NORM = 1              |          |

|                                | eceive/Transmit Interface, SPI-compatible mode, SSI_NORM = 0     |          |

|                                | SI Receive/Transmit Timing Parameters, SSI_NORM = 0              |          |

| Figure 5-15 R                  | ead Register Sequence in SSI Mode                                | 38       |

|                                | LICT OF TABLES                                                   |          |

| T-1-1- 4044                    | LIST OF TABLES                                                   | 40       |

| Table 4.2.1-1                  | CLKSEL[2:0] Decode                                               | 19       |

| Table 5.5.2-1                  | Command Byte Definition                                          | 40       |

| Table 6.1.2-1                  | Gray Scale Message Format                                        | 41       |

| Table 6.1.3-1                  | 4 Bit 250 ppi Gray Scale Message Format                          | 42       |

| Table 6.1.4-1                  | Monochrome Packed Message Format                                 | 43<br>44 |

| Table 6.1.5-1<br>Table 6.1.6-1 | Histogram Message Format Authentication Word Message Format      | 44<br>45 |

| Table 6.1.6-1                  | Column Data – 4-bit Pixel Depth                                  | 45<br>48 |

| Table 6.2.4-1                  | Column Data – 4-bit Pixel Depth  Column Data – 1-bit Pixel Depth | 48       |

| Table 6.2.4-2                  | Column Data – 1-bit Pixel Depth  Column Data – 2-bit Pixel Depth | 48<br>48 |

| Table 6.2.4-3                  | Registers Summary                                                | 40<br>51 |

| 1 able 0.2.9-1                 | registers outlittary                                             | 31       |

## 1. Introducing the EntréPad AES2510 Slide Sensor...

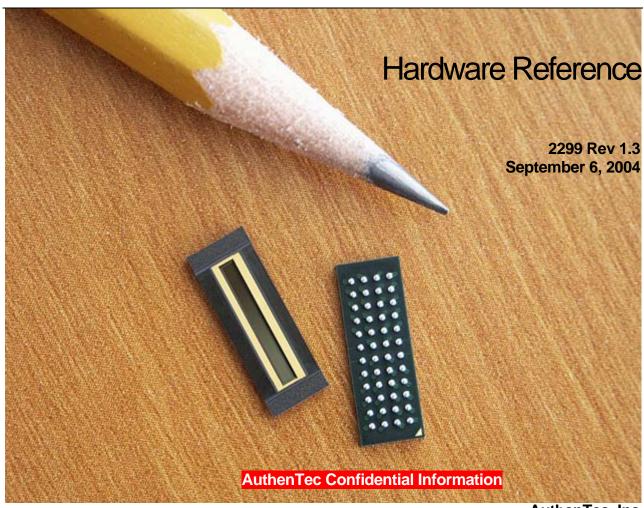

..., the latest, lowest cost fingerprint sensor IC. AuthenTec has adapted its patented, award winning TruePrint Technology to read fingerprints while the finger is pulled across the AES2510's rectangular surface. In this manner, the fingerprint images are acquired AND the sensor is substantially reduced in size.

The AES2510 combines both an advanced Master-mode Serial Peripheral Interface with an on-chip DMA engine as well as a convenient easy-to-use 8-bit parallel interface. These interfaces permit easy integration with nearly all of the top baseband and application processors utilized in mobile phones.

## 1.1 TruePrint Technology is...

...AuthenTec's unique patented fingerprint reading technology. During imaging, a small signal is generated between the IC and the finger's living tissue layer. 3072 individual sensing elements in the slide sensor matrix form a planar antenna array that receives this signal, creating a digital pattern that accurately reproduces the fingerprint's underlying structure.

A powerful utility contained within TruePrint Technology<sup>™</sup> is Dynamic Optimization<sup>™</sup>. This tool analyzes each image, controlling a variety of parameters real-time to optimize the fingerprint image slices, regardless of skin conditions or surface contamination.

## 1.2 Feature Summary

- ✓ Patented TruePrint Technology for best Ability To Acquire (ATA)

- ✓ High Definition 192 X 16 TruePrint Technology Based Pixel Array

- o 500 pixels per inch (ppi) native

- o 9.75mm X 0.81mm array area

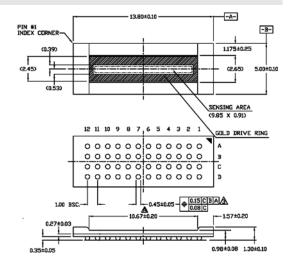

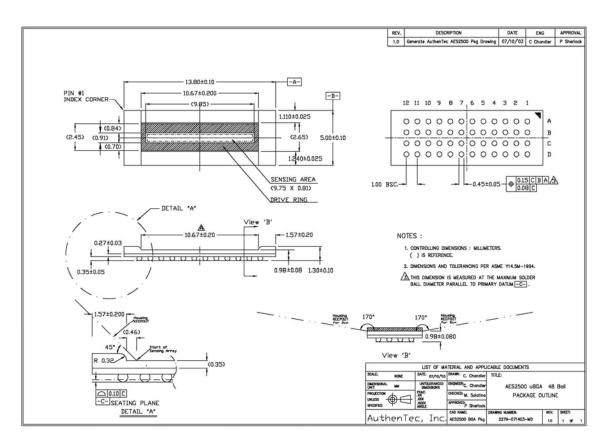

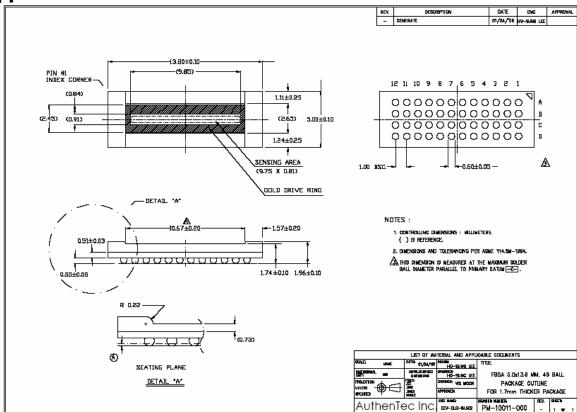

- ✓ Compact 48 Ball Grid Array (BGA) Pkg.

- o 13.8mm X 5mm X (1.3mm or 1.96mm)

- ✓ Extended Operating Voltage Range

- o 2.4V to 3.6V single supply

- ✓ -20°C to +70°C Mobile Phone Compatible Operating Temperature Range

- ✓ Easy to Integrate System Interfaces

- o 8-bit Parallel

- o Synchronous Serial (SPI™ & McBSP™ compatible) Master & Slave mode

- o On-chip DMA support for simplified image slice transfer during authentication

- ✓ Operation with Crystal, Resonator, or with external clock input

- ✓ Ultra-hard scratch resistance surface coating > 10 Million rubs w/o degradation

- ✓ IEC 61000-4-2 Level 4 ESD Immunity (+/- 15KV)

- ✓ Built-in low power Finger Detection w/system interrupt capability

- ✓ Multiple battery-friendly operating modes @ 2.5V

- o Imaging @ <38mA typ.

- o Graphical Cursor Control mode @ < 2 mA typ.

#### 1.3 Conventions

For vectors (groups of bits), ordering will always be from most significant to least significant bit (MSB to LSB, e.g. Pixel\_Data[63:0] where bit 63 is the MSB and bit 0 is the LSB).

When vectors that span multiple bytes are transmitted, the lower byte (bits [7:0]) is transmitted first. This applies to pixel data and the authentication word returned after each imaging frame.

Numbers followed by a 'b' are shown in binary. Numbers followed by an 'h' are in hexadecimal.

## 1.4 Operational Description

The Sensor begins operation in the 'idle' state after a reset. In the idle state, array power is turned off and clocking is disabled (except interface activity). It is then necessary for the system SW to setup the sensor for the desired operation (Imaging or Navigation). The requested operation is enabled by setting the Sensor Mode bits (located in Register 80h:D3-D2). If Imaging is selected, the Sensor enters finger detect mode checks for a finger present at a rate programmed by the Finger Detect Rate setting. The default reset value sets the detect period to ~62 ms.

After finger detection, the sensor will begin the programmed operation and will enter Imaging mode until the finger is removed. Once the finger is removed, the sensor returns to the Low Power Finger Detect mode. When no activity is detected on the system interface bus for approximately 200uS, power is reduced by disabling the internal clocks and the array power is once again turned off.

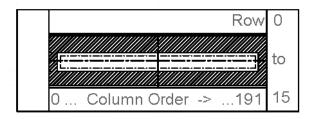

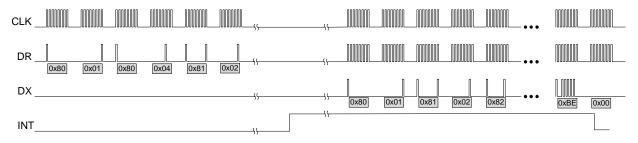

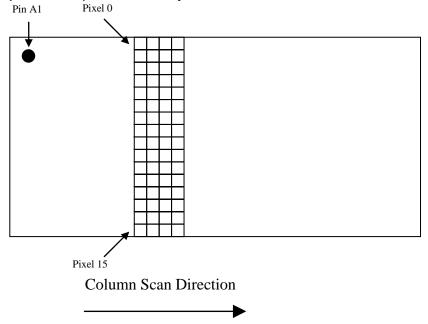

Figure 1-1 Column and Row Numbering

The array consists of 192 columns of 16 pixels each. During imaging, the columns are powered up and the signals from each of the 16 pixels/column are sampled, digitized and returned to the host computer over the selected interface sequentially in order on a per-column basis. The sensor has the capability to utilize only the center 128 columns during imaging mode to facilitate higher finger sliding speeds. During fingerprint enrollment, a 192 pixel wide template is created. Then, optionally, either a 192 pixel wide or 128 pixel wide verify can be performed. This mode is

entirely controlled via software using sensor register settings for start and stop columns.

If the finger detect is not active when it is rechecked at the end of a scan, the array is powered down and the sensor reverts back to checking for a finger at the programmed detect rate.

AuthenTec has application notes to support the integration of the AES2510 for all available interface options. Contact AuthenTec for availability.

#### 1.4.1 Idle Mode

In Idle Mode the Sensor does not perform any finger detect functions since imaging and navigation modes are disabled (analog power remains off and the finger ring is never driven). The sensor will respond to read register commands. Timer 1 and Timer 2 are available to be used as interval timers. They are started by bits in REG80 and return REG9B when complete.

#### 1.4.2 Imaging Mode

The on-chip imaging buffers affect imaging only when slave interfaces are selected. Master interfaces send data when it becomes available.

## 1.5 Navigation Using the AES2510

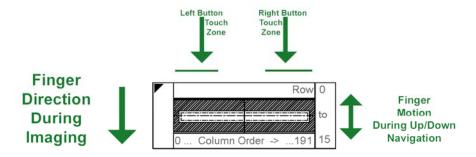

There are two navigation modes offered by the AES2510. Mode 1 provides for simple menu scrolling, the typical Left / Right / Up / Down button functionality can be easily emulated on the sensor by statically touching the sensor to indicate desired left or right direction and by sliding the finger at normal finger speeds in the up or down direction to indicate up or down. This mode is identical to the functionality contained within the AES250x products. Mode 2 navigation is a hardware assisted full motion dx/dy system providing functionality similar to a touchpad on a PC. This functionality can be employed for a variety of applications where graphical cursor control is required.

Mode 1 provides for 4 / 5 way navigation (NAV mode), the operations are enabled (via the SENSOR MODE bits as described previously) and Navigation mode is selected, the sensor will provide constant, periodic indications of direction and finger presence by sending a 2-byte message to the selected interface.

## Nav Mode 1 (NAV) - cursor control mode

After NAV mode is enabled, the sensor takes 10 samples of the center column approximately every 100 us. After producing an output message, the sensor then enters a low power state for a programmable amount of

time, and then repeats the above sequence. Output generation rates are programmable and range from 100 Hz down to 26 Hz.

Figure 1-2 Cursor Control Navigation

#### Nav Mode 2 (NAVI) - graphical navigation mode

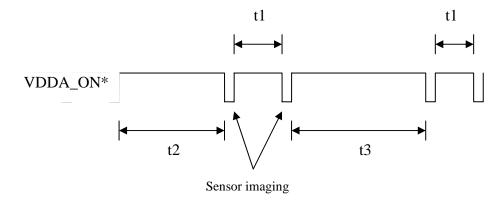

For accurate cursor placement the AES2510 has implemented an imagebased navigation system supported by on-chip hardware timing of the images. By accurately timing the image capture, accurate dx/dy motions can be calculated. In this mode the sensor takes four images. The figure below shows the profile. The PWR\_ON\_N pin is low to turn analog power on for finger detect or imaging.

The Nav Mode 2 cycle starts with two image segments separated by a programmable delay t1. The t1 delay is controlled by the GP TIMER 1 value (REGBA and REGBB). The timer has a 14-bit range and 16 us resolution.

The two image segments are followed by a second programmable delay t2. The t2 delay is controlled by the GP TIMER 2 value (REGBC). The timer has a 7-bit range and 1 ms resolution. The t2 delay is followed by another set of two image segments also separated by the t1 delay.

These image segments are followed by a third delay t3. The t3 delay is controlled by the GP TIMER 3 value (REGBD). The timer has a 7-bit range and 1 ms resolution. The cycle then starts over.

If the Ultra Low Power bit (D6 in REG84) is set, the oscillator and PLL are shut off during the t2 and t3 delay periods. When the oscillator and PLL are re-started, there is a delay period where the clock output is blocked. The delay (tdelay) in milliseconds is set by the Osc On Delay field in REG94. The delays between the sets of image segments are extended to (t2 + tdelay) and (t3 + tdelay).

In Nav Mode 2, mode the sensor always behaves as if the column interrupt depth is set to 8. Image headers are disabled, authentication data is disabled, histogram messages are disabled, and register messages are disabled. The sensor now returns only navigation data.

The sensor uses the programmed register settings for gain, drive, frequency, column scan rate, start column, end column, and data format.

For master interfaces, image data is transmitted as it is captured. For slave interfaces, an interrupt (or data available) will be generated after 8 columns of data are available or the four image segment sequence is complete.

# 2. DC ELECTRICAL CHARACTERISTICS

## 2.1 Absolute Maximum Ratings

An absolute maximum rating is the maximum value guaranteed by the AuthenTec. The use of a product in violation of these ratings can result in significant loss of device reliability or cause damage to the IC.

| Symbol           | Parameter                                                           | Min. | Max.                 | Units |

|------------------|---------------------------------------------------------------------|------|----------------------|-------|

| $V_{DD}$         | Supply Voltage                                                      | -0.5 | 4.3                  | V     |

| VI               | Input Voltage                                                       | -0.5 | V <sub>DD</sub> +0.5 | V     |

| Vo               | Output Voltage                                                      | -0.5 | V <sub>DD</sub> +0.5 | V     |

| I <sub>IK</sub>  | Input Clamp Current VI < V <sub>SS</sub> of VI > V <sub>DD</sub>    |      | ±20                  | mA    |

| I <sub>OK</sub>  | Output Clamp Current<br>VO < V <sub>SS</sub> of VO> V <sub>DD</sub> |      | ±20                  | mA    |

| T <sub>STG</sub> | Storage Temperature                                                 | -65  | 150                  | °C    |

| Latch-Up         | Latch-Up Immunity                                                   | ±100 |                      | mΑ    |

| T <sub>SOL</sub> | Maximum Soldering Temperature (MSL=3)                               |      | +240                 | °C    |

| T <sub>SOL</sub> | Maximum Soldering Temperature (MSL= TBD)                            |      | +260                 | °C    |

Figure 2-1 Absolute Maximum Ratings

## 2.2 Recommended Operating Conditions

| Symbol         | Parameter                        | Min.          | Тур | Max.          | Units    |

|----------------|----------------------------------|---------------|-----|---------------|----------|

| $V_{DD}$       | Power Supply Voltage             | 2.4           |     | 3.6           | V        |

| $V_{DDACp-p}$  | Power Supply Ripple peak to peak | -50           |     | +50           | mV       |

| $V_{l}$        | Input Voltage                    | 0             |     | $V_{DD}$      | V        |

| Vo             | Output Voltage                   | 0             |     | $V_{DD}$      | V        |

| $V_{IH}$       | High Level Input Voltage         | $70\% V_{DD}$ |     | $V_{DD}$      | V        |

| $V_{IL}$       | Low Level Input Voltage          | 0             |     | $30\% V_{DD}$ | <b>V</b> |

| t <sub>t</sub> | Digital Input Transition (Rise   | 0             |     | 3             | ns       |

|                | and Fall) Time                   |               |     |               |          |

| T <sub>A</sub> | Ambient operating                | -20           |     | 70*           | ô        |

|                | temperature                      |               |     |               |          |

Figure 2-2 Recommended Operating Conditions

#### \*Warning

The AES2510 remains fully operational at temperatures that are high enough to be uncomfortable for the user.

For reasons of safety and protection, AuthenTec reference designs include circuitry that serves to manage the junction temperature by controlling the supply current. If the hardware developer elects not to use the AuthenTec-provided control circuit design, it will then be essential that an equivalent design be developed and implemented.

## 2.3 DC Characteristics @ Recommended Operating Conditions

Unless otherwise specified, V<sub>I</sub> = V<sub>DD</sub> or V<sub>SS</sub>, T<sub>Ambient</sub> = 25°C

| Symbol           | Parameter                                  | Conditions   | Min.                     | Тур | Max. | Units |

|------------------|--------------------------------------------|--------------|--------------------------|-----|------|-------|

| V <sub>OH</sub>  | High Level Output Voltage                  | IOH=2mA      | V <sub>dd</sub> -<br>0.3 |     |      | V     |

| V <sub>OL</sub>  | Low Level Output Voltage                   | IOL=2mA      |                          |     | 0.3  | V     |

| I <sub>IL</sub>  | Low Level Input Current                    | VI=VIL(min.) |                          |     | ±1   | μΑ    |

| I <sub>IH</sub>  | High Level Input Current                   | VI=VIH(max.) |                          |     | ±1   | μΑ    |

| l <sub>OZ</sub>  | High Impedance State Output Current        |              |                          |     | ±20  | μA    |

| Power S          | upply Currents                             |              |                          |     |      |       |

| I <sub>DDQ</sub> | Supply Current<br>Imaging mode             | Vdd=2.5V     |                          | 38  | 46   | mA    |

| I <sub>DDQ</sub> | Supply Current<br>Imaging mode             | Vdd=2.8V     |                          | 43  | 51   | mA    |

| I <sub>DDQ</sub> | Supply Current<br>Imaging mode             | Vdd=3.3V     |                          | 50  | 60   | mA    |

| I <sub>DDQ</sub> | Supply Current<br>Imaging mode (peak)      | Vdd=3.6V     |                          | 55  | 65   | mA    |

| I <sub>DDQ</sub> | Supply Current Navigation or Finger Detect | Vdd=2.5V     |                          | 2.3 | 2.8  | mA    |

| I <sub>DDQ</sub> | Supply Current Navigation or Finger Detect | Vdd=2.8V     |                          | 2.5 | 3.0  | mA    |

| I <sub>DDQ</sub> | Supply Current Navigation or Finger Detect | Vdd=3.3V     |                          | 3.0 | 3.6  | mA    |

| I <sub>DDQ</sub> | Supply Current Navigation or Finger Detect | Vdd=3.6V     |                          | 3.3 | 4.0  | mA    |

Figure 2-3 DC Characteristics

All I<sub>DDQ</sub> Currents measured RMS using standard AuthenTec software and drivers. Use of other software or customized register settings may effect actual power consumption.

# 3. Sensor Operation

## 3.1 Operation Description

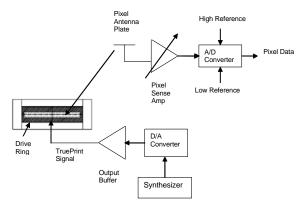

During an imaging event, the RF TruePrint Signal is conducted via the Drive Ring to the users' finger. The TruePrint Signal is then conducted through and modulated by the "live layer" of the finger where the true fingerprint originates. The imaging array (center strip region of the chip) measures the TruePrint signal; the strength of which corresponds to either a ridge or valley region.

The image array of the AES2510 sensor is composed of 16x192 pixels. The array is scanned similarly to a sub-array in AuthenTec's touch sensors. During the imaging process, 16 pixels in a column are powered up, sampled, and converted to 4, 2 or 1-bit values. The high and low reference voltages for the ADC are programmable via 7-bit DACs.

Figure 3-1 AES2510 Functional Diagram

The sensing element of each pixel is an RF sense-amplifier, which picks up the TruePrint (high frequency AC) signal (125 KHz – 2MHz) that is applied to the finger via the Finger Drive Ring located prominently on the top and bottom of the sensor surface. The pixel sense amps receive, amplify, and buffer the signal.

Each pixel output is then converted into a level corresponding to the strength of the received signal. Stronger signals are picked up from ridges than valleys. This output is converted by an A/D converter whose endpoints are adjustable via the Reference High and Reference Low voltages.

The AES2510 device has three selectable interfaces:

- 1) Asynchronous Serial up to 3Mbps

- 2) Synchronous Serial SPI™ compatible (both clock normal and clock opposite) up to 8 Mbps in both slave and master modes

- 3) 8-bit parallel microprocessor interface running down to 110nS cycle time

# 4. Pin Definitions

## 4.1 Packaging Information

The AES2510 sensor is housed in either of two 48 Ball Grid Array packages.

Figure 7 - 48 BGA - Thin Version

The package drawing shows both the mechanical dimensions of the package as well as recommended housing "keep-out" areas and angles of approach to and from the slide surface. For additional information, contact AuthenTec Applications Engineering for more details.

Figure 3 - 48 BGA Thick Style

It is important to note that the solder ball diameter for these two packages are not the same.

Other Information:

Gold Ring Nickel Ring

Package Mass: 0.1183g ±0.000388g 0.1159g±0.000877

Interface Specific pin assignments and pin function descriptions of the AES2510 sensor are given below. Shared pin definitions for SIO[13:0] are selected by the state of the IOSEL[1:0] pins. Refer to section 5.1 for the interface-specific SIO definitions. The following pin list matches AuthenTec's certified reference designs. Certain pin functions will be required to change for other implementations.

| Pin       | Туре     | Digital  | Signal              | Signal              | Signal           |

|-----------|----------|----------|---------------------|---------------------|------------------|

|           | Type     | Activity | Name (Async Serial) | Name (Sync. Serial) | Name (8-bit Par) |

| <b>A1</b> | Passive  | Static   | VREF                | VREF                | VREF             |

| A2        | Passive  | Static   | CT2                 | CT2                 | CT2              |

| A3        | Passive  | Static   | CT1                 | CT1                 | CT1              |

| A4        | Output   | Active   | FINGERDRIVE         | FINGERDRIVE         | FINGERDRIVE      |

| A5        | Input    | Static   | RESET*              | RESET*              | RESET*           |

| A6        | Reserved | Otatio   | N/C                 | N/C                 | N/C              |

| A7        | Reserved |          | N/C                 | N/C                 | N/C              |

| A8        | Power    |          | VDD                 | VDD                 | VDD              |

| A9        | Power    |          | VSS                 | VSS                 | VSS              |

| A10       | Power    |          | VDD                 | VDD                 | VDD              |

| A11       | Input    | Active   | SYS CLK             | SYS CLK             | SYS CLK          |

| A12       | Output   | Active   | DRIVE_RING          | DRIVE RING          | DRIVE_RING       |

| B1        | Input    | Static   | CLKSEL2             | CLKSEL2             | CLKSEL2          |

| B2        | Power    | - Clarit | VSS                 | VSS                 | VSS              |

| B3        | Power    |          | VDD                 | VDD                 | VDD              |

| B4        | Input    | Static   | VDDL                | VDDL=Master out     | VSSL             |

|           | mpat     | Otatio   | 7552                | VSSL=Slave out      | 1002             |

| B5        | Input    | Static   | VSSL                | VDDL                | VSSL             |

| B6        | Input    | Static   | CLKSEL1             | CLKSEL1             | CLKSEL1          |

| B7        | I/O      | Active   | RTR                 | FS                  | D1               |

| B8        | I/O      | Active   | RXD                 | DR                  | D0               |

| B9        | I/O      | Active   | N/C                 | N/C                 | D7               |

| B10       | I/O      | Active   | N/C                 | SSI_NORM            | D6               |

| B11       | I/O      | Active   | BAUD1               | A0                  | D5               |

| B12       | I/O      | Active   | BAUD0               | INT                 | D4               |

| C1        | Reserved |          | N/C                 | N/C                 | N/C              |

| C2        | Power    |          | VSS                 | VSS                 | VSS              |

| C3        | Power    |          | VDDA                | VDDA                | VDDA             |

| C4        | Input    | Static   | VSSL                | VSSL                | VSSL             |

| C5        | Input    | Static   | CLKSEL0             | CLKSEL0             | CLKSEL0          |

| C6        | Input    | Static   | VSSL                | VSSL                | VSSL             |

| <b>C7</b> | I/O      | Active   | AUTOBAUD_EN         | CLK                 | D2               |

| C8        | I/O      | Active   | TXD                 | DX                  | D3               |

| C9        | 1/0      | Active   | N/C                 | N/C                 | A0               |

| C10       | Output   | Active   | VDDA_ON*            | VDDA_ON*            | VDDA_ON*         |

| C11       | 1/0      | Active   | N/C                 | N/C                 | RD*              |

| C12       | Power    |          | GPIO0               | GPIO0               | WR*              |

| D1        | Output   | Active   | DRIVE_RING          | DRIVE_RING          | DRIVE_RING       |

| D2        | Reserved |          | N/C                 | N/C                 | N/C              |

| D3        | Reserved |          | N/C                 | N/C                 | N/C              |

| D4        | Reserved |          | N/C                 | N/C                 | N/C              |

| D5        | Reserved |          | N/C                 | N/C                 | N/C              |

|     |          | 2.       |                     |                     |                  |

|-----|----------|----------|---------------------|---------------------|------------------|

| Pin | Туре     | Digital  | Signal              | Signal              | Signal           |

|     |          | Activity | Name (Async Serial) | Name (Sync. Serial) | Name (8-bit Par) |

| D6  | Reserved |          | N/C                 | N/C                 | N/C              |

| D7  | Reserved |          | N/C                 | N/C                 | N/C              |

| D8  | I/O      | Active   | GPIO1               | GPIO1               | CE*              |

| D9  | I/O      | Active   | GPIO2               | GPIO2               | READY            |

| D10 | I/O      | Active   | GPIO3               | GPIO3               | INT              |

| D11 | Power    |          | VSS                 | VSS                 | VSS              |

| D12 | Power    |          | VDDA                | VDDA                | VDDA             |

Figure 4-4 Pin List by Interface

## 4.2.1 Pin Type and Activity Definitions

VDD, VSS: Power Supply Connections

Passive: Connections to passive components (ex: Filter caps, etc)

Input: Active Inputs to the sensor

Output: Active Outputs from the sensor

I/O: Active I/O's from the sensor (state / configuration dependent)

Reserved: Do Not Connect anything to these pins

Static: DC or slowly changing voltages

Active: Active Signals, Digital or Analog

VDDL: Fixed Active High Logic Level

VSSL: Fixed Active Low Logic Level

VDDA: Pixel Array Power supply pin

N/C: No Connection externally

# 4.3 Pin Descriptions (alphabetical listing)

| Pin           | Signal<br>Name | Function Description                                                                                                                                                                            |

|---------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |                | For pins D8-D12, Refer to the appropriate AuthenTec Reference Design for connection details                                                                                                     |

| C5            | CLKSEL0        | Clock input option selection. Refer to section 4.4                                                                                                                                              |

| B6            | CLKSEL1        | Clock input option selection. Refer to section 4.4                                                                                                                                              |

| B1            | CLKSEL2        | Clock input option selection. Refer to section 4.4                                                                                                                                              |

| A3            | CT1            | Filter Capacitor - connect to pin A2 through a 0.1uF capacitor, standard bypass type                                                                                                            |

| A2            | CT2            | Filter Capacitor - connect to pin A3 through a 0.1uF capacitor, standard bypass type                                                                                                            |

| D1            | DRIVERING      | DriveRing - connection to the metal ring on the sensor surface. No other connections made.                                                                                                      |

| A12           | DRIVERING      | DriveRing - connection to the metal ring on the sensor surface. No other connections made.                                                                                                      |

| A4            | FINGERDRIVE    | TruePrint Signal output used to drive radio frequency signal through external circuitry to finger ring pins (A12 and D1). Controlled by internal excitation generator.                          |

| B4            | IOSEL0         | Interface option selection. Refer to Section 5.1                                                                                                                                                |

| B5            | IOSEL1         | Interface option selection. Refer to Section 5.1                                                                                                                                                |

| A5            | RESET*         | Reset input - 2/3 threshold voltage with hysteretic input. Approximately 57 Kohm pull-up resistor internal, with tolerance of 30%. See section 2.1 for additional definition of a proper reset. |

| B8            | SIO0           | Refer to Figure 5-2 SIO Pin Definitions for each Selected Interface Option                                                                                                                      |

| B7            | SIO1           | Refer to Figure 5-2 SIO Pin Definitions for each Selected Interface Option                                                                                                                      |

| C7            | SIO2           | Refer to Figure 5-2 SIO Pin Definitions for each Selected Interface Option                                                                                                                      |

| C8            | SIO3           | Refer to Figure 5-2 SIO Pin Definitions for each Selected Interface Option                                                                                                                      |

| B12           | SIO4           | Refer to Figure 5-2 SIO Pin Definitions for each Selected Interface Option                                                                                                                      |

| B11           | SIO5           | Refer to Figure 5-2 SIO Pin Definitions for each Selected Interface Option                                                                                                                      |

| B10           | SIO6           | Refer to Figure 5-2 SIO Pin Definitions for each Selected Interface Option                                                                                                                      |

| B9            | SIO7           | Refer to Figure 5-2 SIO Pin Definitions for each Selected Interface Option                                                                                                                      |

| C9            | SIO8           | Refer to Figure 5-2 SIO Pin Definitions for each Selected Interface Option                                                                                                                      |

| C11           | SIO9           | Refer to Figure 5-2 SIO Pin Definitions for each Selected Interface Option                                                                                                                      |

| C12           | SIO10          | Refer to Figure 5-2 SIO Pin Definitions for each Selected Interface Option                                                                                                                      |

| D8            | SIO11          | Refer to Figure 5-2 SIO Pin Definitions for each Selected Interface Option                                                                                                                      |

| D9            | SIO12          | Refer to Figure 5-2 SIO Pin Definitions for each Selected Interface Option                                                                                                                      |

| D10           | SIO13          | Refer to Figure 5-2 SIO Pin Definitions for each Selected Interface Option                                                                                                                      |

| A11           | SYS_CLK        | Clock input pin - input clock used for all chip functions. See Figure 4-5 and Section 4.4 for input characteristics and requirements.                                                           |

| D12           | VDDA           | Pixel Array Power Connection                                                                                                                                                                    |

| C3            | VDDA           | Pixel Array Power Connection                                                                                                                                                                    |

| C10           | VDDA_ON*       | External Array Power FET control - If used this pin may drive a high side P-channel                                                                                                             |

|               |                | FET. See AuthenTec Reference Designs for connection details.                                                                                                                                    |

| A1,<br>A2, A3 |                | N/C – Refer to AuthenTec reference design for appropriate connections                                                                                                                           |

Figure 4-4 AES2510 Active Pin Functional Description

#### 4.4 Clock Select Control

AES2510 can support a variety of clock sources, ranging in frequency from 6MHz up through 48MHz. The AES2510 uses a single pin crystal/resonator oscillator circuit that can also be overdriven with an external clock source capable of driving >+/-5mA. Clock frequency selection [including clocks driven into the SYS\_CLK pin] is done via the CLKSEL[2:0] input pins. The following table shows the CLKSEL[2:0] pin configurations:

| CLKSEL2<br>Pin B1 | CLKSEL1<br>Pin B6 | CLKSEL0<br>Pin C5 | Crystal/Resonator or Clock<br>Frequency Ranges |

|-------------------|-------------------|-------------------|------------------------------------------------|

| 0                 | 0                 | 0                 | 6 MHz                                          |

| 0                 | 0                 | 1                 | 8 – 9.6 MHz                                    |

| 0                 | 1                 | 0                 | 12 - 13 MHz                                    |

| 0                 | 1                 | 1                 | 18 - 19.5 MHz                                  |

| 1                 | 0                 | 0                 | 24 MHz                                         |

| 1                 | 0                 | 1                 | Reserved                                       |

| 1                 | 1                 | 0                 | Reserved                                       |

| 1                 | 1                 | 1                 | 48 – 52 MHz (Direct Clock Input)               |

Table 4.2.1-1 CLKSEL[2:0] Decode

Frequency related operating parameters (e.g. asynchronous serial baud rates or excitation frequencies) are accurate when the internal clock (MCLK) is 48 MHz. Otherwise these parameters scale appropriately with the actual system clock frequency.

## 4.4.1 Clock Specification

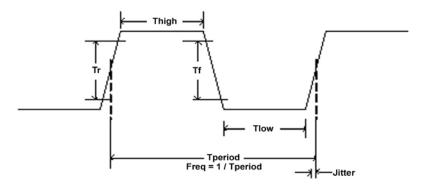

For the AES2510, there are several different clocking options available: Crystal connection, ceramic resonator connection, and external clock driven. Appropriate application of clock sources is driven the desired circuit application (interface type) and reference design. This section addresses the specification requirements for an externally driven clock. All electrical and environmental conditions from the device specification apply as well. When driving an external clock into the SYSCLK device pin (A11), the following timing diagram applies:

| [1]  | Parameter                      | [1]  | Minimum                | [1]  | Maximum                |

|------|--------------------------------|------|------------------------|------|------------------------|

| [2]  | Freq.(Async.<br>Serial Int.)   | [2]  | Freq.(nominal)<br>– 1% | [2]  | Freq.(nominal) + 1%    |

| [3]  | Jitter (Async.<br>Serial Int.) | [3]  |                        | [3]  | Tperiod*1%             |

| [4]  | Freq.(Sync.<br>Serial Int.)    | [4]  | Freq.(nominal)<br>– 1% | [4]  | Freq.(nominal) +<br>1% |

| [5]  | Jitter (Sync.<br>Serial Int.)  | [5]  |                        | [5]  | Tperiod*1%             |

| [6]  | Tr                             | [6]  | -                      | [6]  | 3ns                    |

| [7]  | Tf                             | [7]  | -                      | [7]  | 3ns                    |

| [8]  | Thigh                          | [8]  | 45%*[Tperiod]          | [8]  | 55%*[Tperiod]          |

| [9]  | Tlow                           | [9]  | 45%*[Tperiod]          | [9]  | 55%*[Tperiod]          |

| [10] | VIH (Pin A11)                  | [10] | 70% VDD                | [10] | -                      |

| [11] | VIL (Pin A11)                  | [11] | -                      | [11] | 30% VDD                |

| [12] | IIL (Pin A11)                  | [12] | -1uA                   | [12] | +1uA                   |

| [13] | VOH (Clk<br>Source)            | [13] | VDD-0.25V              | [13] | -                      |

| [14] | VOL (Clock<br>Source)          | [14] | -                      | [14] | VDD+0.25V              |

Figure 4-5 External Clock Specifications

## 4.5 Other Timing Information

## 4.5.1 Imaging Scan Timing / Frame Rates:

Frame rate is highly correlated to maximum finger sweeping speed. The AES2510 column scan timing is 32us per sixteen pixel column and will limit image frame rates to less than [16x192 pixels \* 32us/16 pixels = 6.144 ms] or ~162 fps maximum. Transferring register data, histogram data, and authentication data will reduce this frame

rate. When the sensor is utilized in 128 column mode, the frame rate scales proportionally to 244. External system latencies and other external factors beyond the control of the sensor and control software can reduce the maximum effective frame rate to lower values. With appropriate overlap of image slices, the effective generalized finger slide rates are estimated to be 10-11cm/sec in 192 column mode and 14-16 cm/sec in 128 column mode.

#### 4.5.2 Finger Detect Auto-calibration

When using Finger Detect [delay method], the device is automatically calibrated once on power up. Sending a master reset to the device does not affect the setting of the reference delay value used for the finger detect calculation. If desired, the device can be re-calibrated by setting the Recalibrate FD bit [Reg82-D2], which is self-clearing.

#### 4.6 Reset

#### 4.6.1 2510 Start-up:

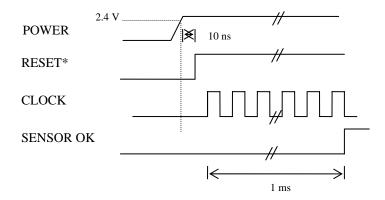

The RESET\* (and SYS\_CLK if the SYS\_CLK pin is driven externally) pin should be held in the low state until Vdd reaches at least 2.4V. This prevents powering up the sensor through the input protection network on those pins.

RESET\* can be released 10 ns after Vdd reaches 2.4V. The clock may be active or inactive when reset is applied or released. Internally reset does not go inactive until two internal clocks after reset is released.

SYS\_CLK can be applied any time after Vdd reaches 2.4V. If using the internal PLL, time is required for it to stabilize before operating the sensor. The PLL lock time is 1 ms worst case. The lock time starts from either clock starting or reset being released, whichever comes last.

# 5. System Interface Descriptions

## 5.1 Interface Select Control

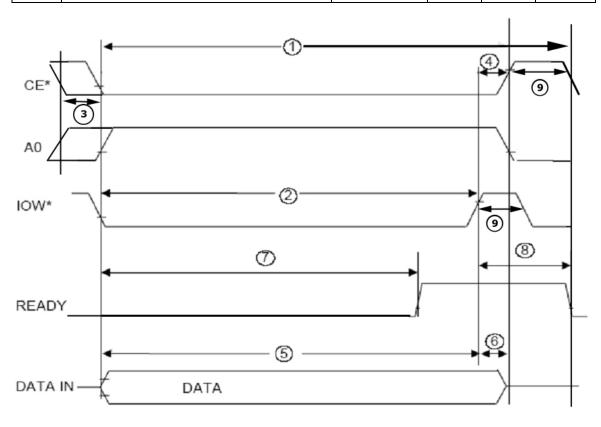

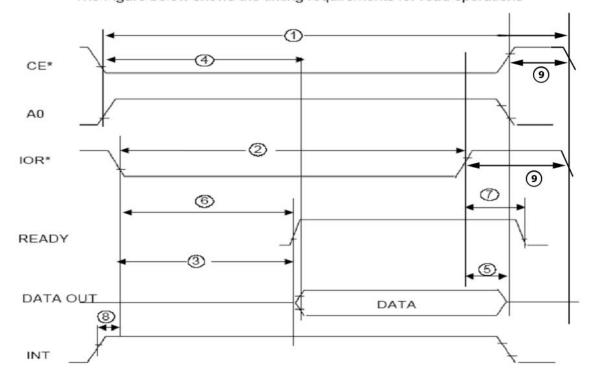

Interface selection is done via the IOSEL[1:0] input pins. The following table shows how. See section 4.2 for the IOSEL[1:0] pin assignments.

| IOSEL1 | IOSEL0 | Interface Selection                   |

|--------|--------|---------------------------------------|

| 0      | 0      | 8-bit Parallel                        |

| 0      | 1      | Asynchronous Serial (not recommended) |

| 1      | 0      | SPI-compatible Synchronous Serial     |

| 1      | 1      | SPI-compatible Master Out/Slave In    |

|        |        | Synchronous Serial                    |

Figure 5-1 IOSEL[1:0] Decode

For each interface selection, the following pin assignments apply:

| SIO/Pin | Parallel |     | Async Serial   | Sync Serial – |               | Sync Serial – |                |     |

|---------|----------|-----|----------------|---------------|---------------|---------------|----------------|-----|

|         |          |     |                |               | Slave SPI     |               | Master SPI or  |     |

|         |          |     |                |               |               |               | McBSP          |     |

| 0/B8    | D0       | I/O | RXD            |               | DR            | I             | DR             | I   |

| 1/B7    | D1       | I/O | RTR            | ı             | FS            | I             | FSR            | 1   |

| 2/C7    | D2       | I/O | AUTOBAUD_EN    |               | CLK           | I             | CLKR           | 1   |

| 3/C8    | D3       | I/O | TXD            | 0             | DX            | 0             | DX             | 0   |

| 4/B12   | D4       | I/O | BAUD_SEL[0]    |               | INT           | 0             | FSX            | 0   |

| 5/B11   | D5       | I/O | BAUD_SEL[1]    |               | A0            | I             | CLKX [Out when | I/O |

|         |          |     |                |               |               |               | SPI, In when   |     |

|         |          |     |                |               |               |               | Mcbsp]         |     |

| 6/B10   | D6       | I/O | Unused, drives | 0             | SPI_NORMAL    | I             | RTR            | ı   |

|         |          |     | low            |               |               |               |                |     |

| 7/B9    | D7       | I/O | Unused, drive  | 0             | Unused, drive | 0             | Unused, drive  | 0   |

|         |          |     | low            |               | low           |               | low            |     |

| 8/C9    | A0       | ı   | Unused, drive  | 0             | Unused, drive | 0             | Frame Per Byte | I   |

|         |          |     | low            |               | low           |               |                |     |

| 9/C11   | IOR_N    | ı   | Unused, drive  | 0             | Unused, drive | 0             | McBsp Mode     | I   |

|         |          |     | low            |               | low           |               |                |     |

| 10/C12  | IOW_N    | ı   | GPIO[0]        | I/O           | GPIO[0]       | I/O           | GPIO[0]        | I/O |

| 11/D8   | CE*      | I   | GPIO[1]        | I/O           | GPIO[1]       | I/O           | GPIO[1]        | I/O |

| 12/D9   | READY    | 0   | GPIO[2]        | I/O           | GPIO[2]       | I/O           | GPIO[2]        | I/O |

| 13/D10  | INT      | 0   | GPIO[3]        | I/O           | GPIO[3]       | I/O           | GPIO[3]        | I/O |

Figure 5-2 SIO Pin Definitions for each Selected Interface Option

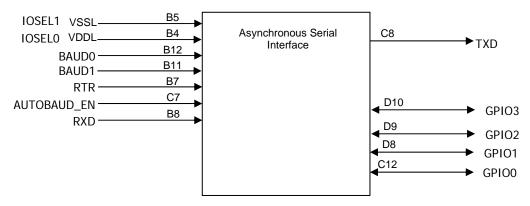

## 5.2 Asynchronous Serial Interface

## Asynchronous Serial Connection Diagram

Figure 5-3 Asynchronous Interface diagram

The Asynchronous Serial Interface provides a serial data in and out for communication with the sensor. In addition, the interface has a Ready-To-Receive signal (RTR) that allows the host to throttle data from the sensor. The sensor is always ready to accept input data, so no throttling is necessary for data written to the sensor. Fixed baud rates are provided for test purposes only as the data rates are too slow for use with a slide-type fingerprint sensor.

| Async Serial Signal<br>Name | Pin | Pin<br>Type | Driver<br>Type | Freq.<br>MHz | Description                                                                                                                                                           |

|-----------------------------|-----|-------------|----------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXD [SIO0]                  | B8  | I           | TTL            | 2            | Serial data received from host.                                                                                                                                       |

| RTR [SIO1]                  | B7  | I           | CMOS           | N/A          | Ready To Receive. High to enable sending serial data to host.                                                                                                         |

| AUTOBAUD_EN<br>[SIO2]       | C7  | ı           | CMOS           | N/A          | Enables autobaud feature of interface when tied high: The first character received after reset must be '0x0F'. When tied low, BAUD[1:0] pins select a fixed bit rate. |

| TXD [SIO3]                  | C8  | 0           | CMOS           | 2            | Serial data transmitted to host.                                                                                                                                      |

| BAUD0 [SIO4]                | B12 | Ī           | CMOS           | N/A          | Usage below 2Mbaud not recommend                                                                                                                                      |

| Async Serial Signal                                              |                          | Pin                      | Driver                       | Freq.                    | Description                                                                                                                                                                                                                                          |

|------------------------------------------------------------------|--------------------------|--------------------------|------------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                                                             | Pin                      | Туре                     | Туре                         | MHz                      | 2000                                                                                                                                                                                                                                                 |

| BAUD1 [SIO5]                                                     | B11                      | Ī                        | CMOS                         | N/A                      | When AUTOBAUD_EN is low [not active], select fixed baud rate according to the table below:                                                                                                                                                           |

|                                                                  |                          |                          |                              |                          | BAUD[1:0]         Baud Rate           00         115.2k bps           01         460.8k bps           10         750.0k bps           11         921.6k bps           In general, the product can only be used in Autobaud mode at bit rates >=2Mbps |

| GPIO0 [SIO10]<br>GPIO1 [SIO11]<br>GPIO2 [SIO12]<br>GPIO3 [SIO13] | C12,<br>D8,<br>D9<br>D10 | I/O<br>I/O<br>I/O<br>I/O | CMOS<br>CMOS<br>CMOS<br>CMOS | N/A<br>N/A<br>N/A<br>N/A | General Purpose Input/Output – Input/Output definition by register B3h                                                                                                                                                                               |

Figure 5-4 Asynchronous Serial Interface Signal Descriptions

For all data rates and formats, the data is formatted using a standard asynchronous protocol, see section 5.2.2. When autobaud mode is selected, the sensor sends a break character (constant low) after the RESET\* pin goes high. The amount of time is selected by the BAUD[1:0] pins.

When Autobaud is enabled, the sensor sends a break character (sets the TXD pin low) after reset goes inactive. TXD is kept low for an amount of time controlled by the BAUD[1,0] select pins.

| BAUD[1,0] | TXD low duration |

|-----------|------------------|

| 00b       | 1000 us          |

| 01b       | 500 us           |

| 10b       | 250 us           |

| 11b       | 75 us            |

Figure 5-5 TXD low duration for Autobaud

After sending the break character, the sensor interprets the next data byte as 0x0F and uses that to determine the bit rate.

After the break character terminates, the sensor interprets the next character received as a 0Fh and sets the bit timing based on that character. Thus, to support automatic baud rate detection after power-on reset, the communication session should begin with the transmission of '0F'h for the sensor to perform a bit time calculation. No further delay in sending data is required after sending the 0Fh byte.

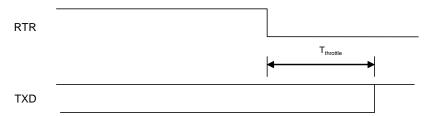

## 5.2.1 Asynchronous Serial Interface RTR Response

The RTR input can be used to throttle the data output from the chip. Figure 2-2 shows the timing associated with RTR disabling.

Figure 5-6 RTR Response Timing Diagram

The serial out circuitry in the sensor consists of a one byte buffer feeding an output shift register. The RTR input is sampled whenever the output shift register is empty; the shift register is not loaded until RTR is active. As long as RTR is de-asserted more than 35 ns before the end of the stop bit, data transmission will stop at the end of the current byte.

#### 5.2.2 Asynchronous Protocol

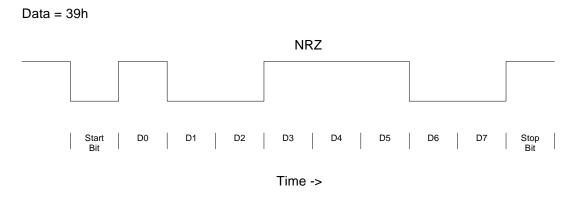

The bit timing for both serial in data and serial out data is shown in Fig. 2-3. Transmit and receive have 1 bit interval for START, 8 data bits and 1 STOP bit with no parity.

The idle state of the TXD line is high. Each data byte sent is preceded by a low start bit and followed by a high stop bit. Each byte is sent LSB first.

The following figure illustrates the asynchronous protocol.

Figure 5-7 Asynchronous Serial Timing Diagram – One Byte

## 5.3 Synchronous Serial Interface [SSI]

Relevant Registers:

RegBE-bit D4 – Interrupt enable

RegBE-bit D5 – Address control. Selects either the Register Address/Data port (A0 = 0) or the Status port (A0 = 1) for the type of data to be transmitted from the sensor.

NOTE: External signal A0 pin should be held low when using the register control method, register BE bit D5 above. Likewise, the register bit should be kept low when using the A0 pin.

The Synchronous Serial Interface provides serial data in and out for communication with the sensor. This interface acts as a <u>slave mode</u> interface only. External data transmit/receive clocks control the data transmission rate. The synchronous serial interface supports 8-bit mode only.

The SSI supports both clock normal and clock opposite phases controlled by the SSI\_NORM pin B11. The SPI<sup>™</sup>-compatible modes support either continuous clock – gated frame protocol or continuous select – gated clock protocol. For all data rates and formats, the data is formatted for a SPI<sup>™</sup>-compatible synchronous protocol. Each byte is sent most significant bit first. For power cycling/control of these interfaces, please refer to the section of sensor power cycling and application notes supporting the AES2510 sensor.

The usage model of the SSI is similar to other AuthenTec sensors. The host processor has the ability read data when the sensor has no data to provide. For that reason, the transmit data byte source is selectable between both a status register and the sensor data register. In normal operation, the host selects the status register, and reads that until the register indicates data is available. A preferred alternative is to use the INT pin [D10] as a data available indicator.

The host then selects the data register and reads the correct number of bytes from the sensor. The Port Address is set either via an internal register bit or via a package pin (A0) as noted above.

By design the SSI is a full duplex communication scheme, so the host processor (master side of the SSI) must manage the 'filler' data produced when reading or writing to the sensor. Inactive filler data should be FFh.

## 5.3.1 Synchronous Serial Interface Description

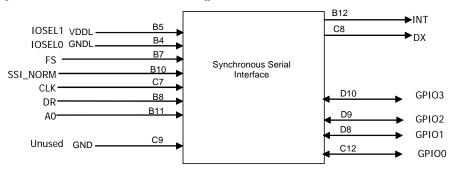

## SSI Synchronous Serial Connection Diagram

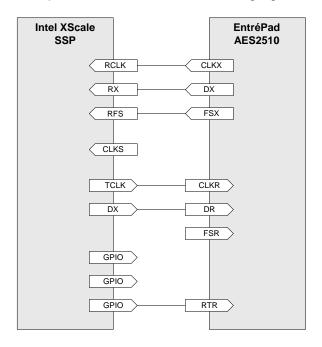

Figure 5-8 SSI-compatible Interface Diagram

| SSI Signal                                                       |                        | Pin                      | Description                                                                                            |

|------------------------------------------------------------------|------------------------|--------------------------|--------------------------------------------------------------------------------------------------------|

| Name                                                             | Pin                    | Type                     | •                                                                                                      |

| DR [SIO0]                                                        | B8                     | ı                        | Receive Data                                                                                           |

| FS [SIO1]                                                        | B7                     |                          | Frame Sync. Signal                                                                                     |

| CLK [SIO2]                                                       | C7                     |                          | Receive Clock                                                                                          |

| DX [SIO3]                                                        | C8                     | 0                        | Transmit Data. This signal goes high impedance when FS is high                                         |

| SSI_NORM<br>[SIO6]                                               | B10                    | I                        | Selects Normal phase (non-inverted clock) when high, selects Opposite phase (inverted clock) when low. |

| INT [SIO4]                                                       | B12                    | 0                        | Interrupt output to indicate data is available when high                                               |

| A0 [SIO5]                                                        | B11                    | I                        | Address, when low selects data, when high selects status byte                                          |

| GPIO0 [SIO10]<br>GPIO1 [SIO11]<br>GPIO2 [SIO12]<br>GPIO3 [SIO13] | C12<br>D8<br>D9<br>D10 | I/O<br>I/O<br>I/O<br>I/O | General Purpose Input/Output – Input/Output definition by register B3h                                 |

Figure 5-9 SSI Synchronous Serial Interface Signal Descriptions

| Port Address Value [A0] either Register bit or A0 Pin | Port Function                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0                                                   | Address/Data port                                                                                                                                                                                                                                                                                                                                               |

| 0x1                                                   | Control/Status port Bits [7:4] - 0000 Bits [3:1] - Encoded Data Available bits (valid when Bit 0 is low) 000 or 001 - Row Header(1 byte – data will always be E0h) 010 - Pixel Data(8 bytes) 011 - Histogram Data (33 bytes) 100 - Authentication Data(9 bytes) 101 - Register Data(2 or 64 or 126 bytes; mode dependent. 2 is for Nav or single register mode) |

|                                                       | Bit 0 - Data available handshake bit for Polled operation, active low                                                                                                                                                                                                                                                                                           |

Figure 5-10 Synchronous Serial Interface IO Port Assignment

## 5.3.2 Synchronous Serial Receive/Transmit Interface Timing

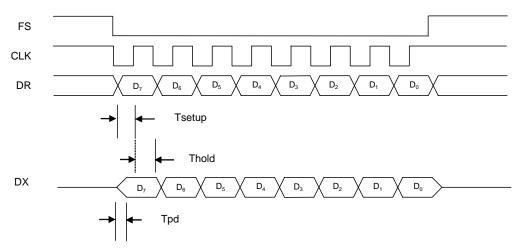

Figure 5-11 Receive/Transmit Interface, SPI-compatible mode, SSI\_NORM = 1 shows timing diagrams for the receive interface in SSI mode with SSI\_NORM = 1.

Figure 5-11 Receive/Transmit Interface, SPI-compatible mode, SSI\_NORM = 1

| Parameter | Description                                         | Min | Max | Unit |

|-----------|-----------------------------------------------------|-----|-----|------|

| Tsetup    | Setup time, data to CLK rising edge                 | 10  | -   | ns   |

| Thold     | Hold time, frame sync or data from CLK rising edge  | 45  | -   | ns   |

| Tpd       | Propagation delay time, CLK rising edge to DX valid | -   | 55  | ns   |

|           | CLK low time                                        | 65  |     | ns   |

|           | CLK high time                                       | 65  |     | ns   |

Figure 5-12 SSI Receive/Transmit Timing Parameters, SSI\_NORM = 1

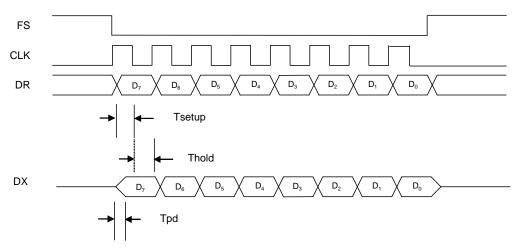

Figure 5-13 Receive/Transmit Interface, SPI-compatible mode, SSI\_NORM = 0 shows timing diagrams for the receive interface in SSI mode with SSI\_NORM = 0.

Figure 5-13 Receive/Transmit Interface, SPI-compatible mode, SSI\_NORM = 0

| Parameter | Description                                         | Min | Max | Unit |

|-----------|-----------------------------------------------------|-----|-----|------|

| Tsetup    | Setup time, data to CLK rising edge                 | 10  | -   | ns   |

| Thold     | Hold time, frame sync or data from CLK rising edge  | 45  | -   | ns   |

| Tpd       | Propagation delay time, CLK rising edge to DX valid | -   | 55  | ns   |

|           | CLK low time                                        | 65  |     | ns   |

|           | CLK high time                                       | 65  |     | ns   |

Figure 5-14 SSI Receive/Transmit Timing Parameters, SSI\_NORM = 0

## 5.3.3 Synchronous Serial Interrupt behavior

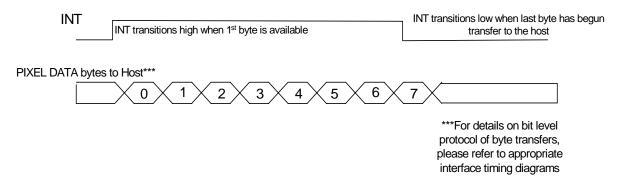

When employing any of the synchronous serial interfaces, an interrupt signal [INT, active High] is available to support coordination of data transfers. There are two different types of operational modes possible with the sensor, Imaging Mode and Navigation Mode. The following examples will describe the behavior of the INT signal for both operational modes.

#### **IMAGING MODE**

For imaging mode, there are several different types of data packets that can be sourced from the sensor, please refer back to Figure 5-10 Synchronous Serial Interface IO Port Assignment.

An interrupt is generated for each one of these unique data packets and is held active until the beginning of the last data byte is read from the sensor by the host processor. This includes one byte transfers, as in the case of the Row Header packet. In the case of a Pixel Data packet, the following timing would apply:

It is important to note that the INT signal does not transition low until the last data byte of the packet has begun transfer on the selected interface. If there were more data from another source available, the INT would again transition high after being low for ~40nS to let the host know that more data is available from the sensor.

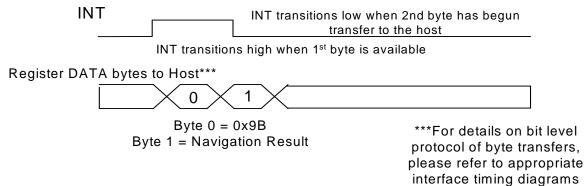

#### **NAVIGATION MODE**

When in navigation mode, there is only one possible data source type, Register Data, since the only data produced during Navigation mode is a 2-byte packet consisting of the register address 0x9B and the data value indicating finger presence and direction. So the INT timing for this packet would be as shown in the figure below.

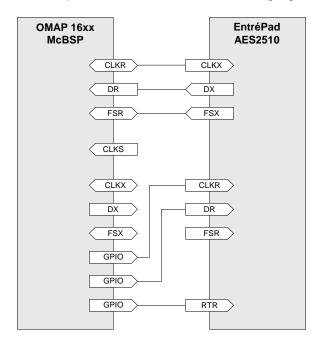

## 5.3.4 SPI and McBSP Compatible M/S Synchronous Serial Interface Specification

The Master / Slave (M/S) Synchronous Serial Interface shall be capable of the following data transfer:

#### 5.3.4.1 CPU to AES2510 Transfers

- This operation shall utilize AES2510's "Receive" path, and the CPU's "Transmit" path.

- CPU will transfer register data information to the sensor in the following format:

<Register Header> <Register Content>

Register Header has its MSB is set (D7 = 1);

Register Content has its MSB is clear (D7 = 0);

It is possible to send an infinite stream of Register Headers;

Register Content is effective only in the register pointed to by the preceding Register Header; Sending Register Content without preceding Register Header has no effect;

- A "bit banging" implementation at the CPU side shall be possible to accomplish a register information transfer;

- This interface may be operating at 256Kbps;

- Note absence of the A0 control pin:

This interface shall have the ability to be configured in two modes:

- TI OMAP 15xx, 16xx compatible McBSP Master or Slave mode

- Intel XScale SPI Master or Slave mode

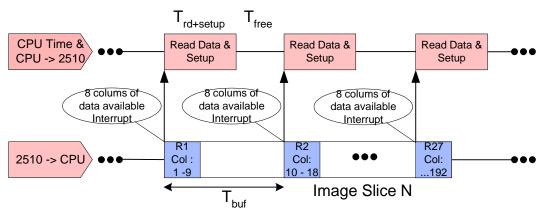

#### 5.3.4.2 **AES2510 to CPU Transfers**

- This operation shall utilize AES2510's "Transmit" path and the CPU's "Receive" path.

- This path will be able to operate at the bit rates up to 8 Mbps; programmable in register 0xBE: D1-D0.

- The data transfers shall have the following format:

<Header> <Data Byte 1>...<Data Byte n>

Header – this value signifies what type of information is transferred (see Sensor Data Types); Data Bytes – 8 bit values that contain the information for the given data types;

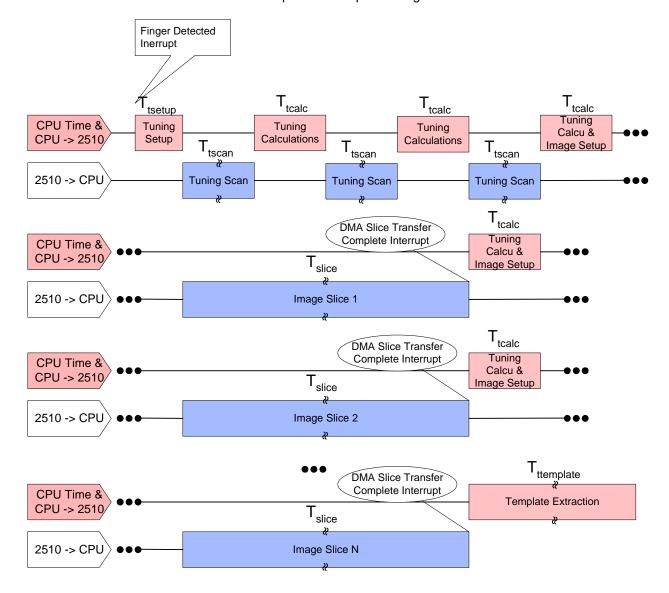

• The Master/Slave architecture allows the AES2510 to be the Master on the Serial Bus. This, coupled with the CPU's port functionality that allows the DMA transfers from the peripheral (serial port) to a memory location (a buffer for the finger print data) allows the off-loading of the CPU processing time.

The M/S Synchronous Serial Interface will allow a high degree of CPU off-loading. The following line diagram illustrates the imaging mode of the AES2510 for this interface. It is assumed that the