# 3-wire Serial EEPROMs 16K AF93BC86

#### FEATURES:

- Internally organized as 2048 x 8 or 1024 x 16

- Wide-voltage range operation o 1.8V-5.5 V

- 3-wire serial interface bus

- Data retention: 100 years

- High endurance: 1,000,000 Write Cycles

- 2 MHz (5V) clock rate

- Sequential read operation

- Self-timed write cycle (10ms max)

- Lead free package

- 8-pin PDIP, 8-pin JEDEC SOIC, and 8pin TSSOP Packages

#### DESCRIPTION

Aplus Flash Technology's AF93BC86 family provides 16K of serial electrically erasable and programmable read-only memory (EEPROM). The wide Vdd range allows for low-voltage operation down to 1.8V. The device, fabricated using traditional CMOS EEPROM technology, is optimized for many industrial and commercial applications where low-voltage and low-power operation is essential. The AF93BC86 is available in 8-pin PDIP, 8-lead JEDEC SOIC, and 8-lead TSSOP packages and is accessed via a 3-wire serial interface.

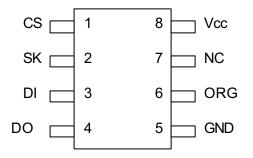

#### Figure 1. Pin Configurations

8-pin PDIP/TSSOP/SOIC

| Pin Name | Function           |

|----------|--------------------|

| CS       | Chip Select        |

| SK       | Serial Data Clock  |

| DI       | Serial Data Input  |

| DO       | Serial Data Output |

| GND      | Ground             |

| Vcc      | Power Supply       |

| ORG      | Internal           |

|          | Organization       |

| NC       | No Connect         |

#### **ABSOLUTE MAXIMUM RATINGS**

| Operating Temperature     | 55°C to +125°C     |

|---------------------------|--------------------|

| Storage Temperature       | 65°C to +150°C     |

| Voltage on Any Pin with   |                    |

| Respect to Ground         | 1.0V to Vcc + 7.0V |

| Maximum Operating Voltage | 6.25V              |

| DC Output Current         | 5.0 mA             |

Note: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

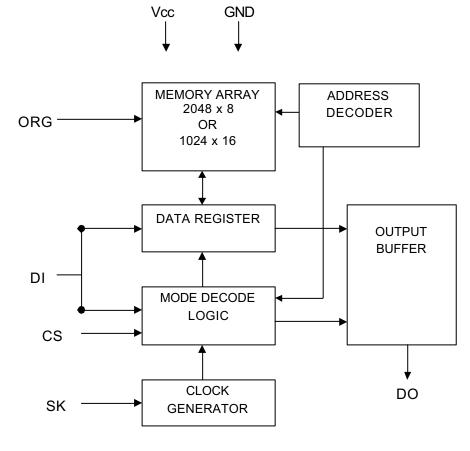

#### Figure 2. Block Diagram

#### <u>Notes</u>

1. The ORG pin is used to select between x8 and x16 mode. When the pin is connected to Vcc, x16 mode is selected. Otherwise, the ORG pin should be grounded in order to select x8 mode.

The interface for the AF93CBC86 is accessed through four different signals: Chip Select (CS), Data Input (DI), Data Output (DO), and Serial Data Clock (SK). The Chip Select (CS) signal must be pulled high before issuing a command through the Data Input (DI) pin. The Serial Data Clock (SK) signal is used in conjunction with the Data Input (DI) pin.

### **PIN CAPACITANCE**

| Applicable over recommended operating range from $T_A = 25^{\circ}C$ , f = 1.0 MHz, Vcc = +5.0V |                                          |             |    |                |  |  |

|-------------------------------------------------------------------------------------------------|------------------------------------------|-------------|----|----------------|--|--|

| Symbol Test Condition Max Units Condition                                                       |                                          |             |    |                |  |  |

| C <sub>OUT</sub>                                                                                | Output Capacitance (DO)                  | 5           | pF | $V_{OUT} = 0V$ |  |  |

| C <sub>IN</sub>                                                                                 | Input Capacitance (CK, SK, DI)           | 5           | pF | $V_{IN} = 0V$  |  |  |

| Noto: 1 T                                                                                       | his parameter is characterized and not 1 | 100% tested |    |                |  |  |

Note: 1. This parameter is characterized and not 100% tested.

#### **DC CHARACTERISTICS**

Applicable over recommended operating range from:

$T_{AMB}$  = -40°C to +85°C, Vcc = +1.8V to +5.5V (unless otherwise noted)

| Symbol                          | Parameter                              | Test Condition                                        | Min       | Тур | Max     | Units |

|---------------------------------|----------------------------------------|-------------------------------------------------------|-----------|-----|---------|-------|

| V <sub>CC1</sub>                | Supply Voltage                         |                                                       | 1.8       |     | 5.5     | V     |

| V <sub>CC2</sub>                | Supply Voltage                         |                                                       | 2.7       |     | 5.5     | V     |

| V <sub>CC3</sub>                | Supply Voltage                         |                                                       | 4.5       |     | 5.5     | V     |

| lcc                             | Supply Current V <sub>CC</sub> = 5.0V  | READ at 1 MHz                                         |           | 0.5 | 2.0     | mA    |

| lcc                             | Supply Current Vcc = 5.0V              | WRITE at 1 MHz                                        |           | 0.5 | 2.0     | mA    |

| I <sub>SB1</sub>                | Standby Current V <sub>CC</sub> = 1.8V | CS = 0V                                               |           | 0   | 0.1     | μA    |

| I <sub>SB2</sub>                | Standby Current V <sub>CC</sub> = 2.7V | CS = 0V                                               |           | 6.0 | 10.0    | μA    |

| I <sub>SB3</sub>                | Standby Current V <sub>CC</sub> = 5.0V | CS = 0V                                               |           | 17  | 30      | μA    |

| ILI                             | Input Leakage Current                  | $V_{IN} = 0V$ to $V_{CC}$                             |           | 0.1 | 3.0     | μA    |

| I <sub>LO</sub>                 | Output Leakage Current                 | $V_{IN} = 0V$ to $V_{CC}$                             |           | 0.1 | 3.0     | μA    |

| V <sub>IL1</sub> <sup>(1)</sup> | Input Low Level                        | 2.7V < V <sub>CC</sub> < 5.5V                         | -0.6      |     | 0.8     | V     |

| V <sub>IH1</sub> <sup>(1)</sup> | Input High Level                       |                                                       | 2.0       |     | Vcc + 1 |       |

| $V_{IL2}^{(1)}$                 | Input Low Level                        | 1.8V < V <sub>CC</sub> < 2.7V                         | -0.6      |     | Vccx0.3 | V     |

| V <sub>IH2</sub> <sup>(1)</sup> | Input High Level                       |                                                       | Vcc x 0.7 |     | Vcc + 1 |       |

| V <sub>OL1</sub>                | Output Low Level                       | 2.7V < V <sub>CC</sub> < 5.5V; <sub>bL</sub> =2.1mA   |           |     | 0.4     | V     |

| V <sub>Oh1</sub>                | Output High Level                      | I <sub>OH</sub> = -0.4mA                              | 2.4       |     |         |       |

| V <sub>OL2</sub>                | Output Low Level                       | 1.8V < V <sub>CC</sub> < 2.7V; <sub>bL</sub> =0.15 mA |           |     | 0.2     | V     |

| V <sub>OH2</sub>                | Output High Level                      | Ι <sub>ΟΗ</sub> = -100μΑ                              | Vcc - 0.2 |     |         |       |

Note: 1.  $V_{IL}$  and  $V_{IH}$  max are reference only and are not tested.

#### **AC CHARACTERISTICS**

Applicable over recommended operating range from:

$T_{AMB}$  = -40°C to +85°C, Vcc = As specified, CL = 1 TTL Gate & 100pF (unless otherwise noted).

| Symbol           | Parameter          | Test Condi             | tion                          | Min  | Тур | Max  | Units  |

|------------------|--------------------|------------------------|-------------------------------|------|-----|------|--------|

| f <sub>sк</sub>  | Clock Frequency,   | $4.5V < V_{CC}$        |                               | 0    |     | 2    | MHz    |

| 0.1              | SK                 | $2.7V < V_{CC}$        |                               | 0    |     | 1    |        |

|                  |                    | $1.8V < V_{CC}$        |                               | 0    |     | 0.25 |        |

| t <sub>SKH</sub> | SK High Time       | $4.5V < V_{CC}$        |                               | 250  |     |      | ns     |

| 0.01             | Ŭ                  | 2.7V < V <sub>CC</sub> |                               | 250  |     |      |        |

|                  |                    | $1.8V < V_{CC}$        |                               | 1000 |     |      |        |

| t <sub>skL</sub> | SK Low Time        | $4.5V < V_{CC}$        |                               | 250  |     |      | ns     |

| one              |                    | 2.7V < V <sub>CC</sub> |                               | 250  |     |      |        |

|                  |                    | $1.8V < V_{CC}$        | < 5.5V                        | 1000 |     |      |        |

| t <sub>cs</sub>  | Minimum CS Low     | $4.5V < V_{CC}$        | < 5.5V                        | 250  |     |      | ns     |

|                  | Time               | 2.7V < V <sub>CC</sub> |                               | 250  |     |      |        |

|                  |                    | $1.8V < V_{CC}$        |                               | 1000 |     |      |        |

| t <sub>CSS</sub> | CS Setup Time      | Relative               | 4.5V < V <sub>CC</sub> < 5.5V | 50   |     |      | ns     |

| 000              |                    | to SK                  | $2.7V < V_{CC} < 5.5V$        | 50   |     |      |        |

|                  |                    |                        | 1.8V < V <sub>CC</sub> < 5.5V | 200  |     |      |        |

| t <sub>DIS</sub> | DI Setup Time      | Relative               | $4.5V < V_{CC} < 5.5V$        | 100  |     |      | ns     |

| 510              |                    | to SK                  | $2.7V < V_{CC} < 5.5V$        | 100  |     |      |        |

|                  |                    |                        | $1.8V < V_{CC} < 5.5V$        | 400  |     |      |        |

| t <sub>CSH</sub> | CS Hold Time       | Relative               |                               | 0    |     |      | ns     |

| 00.1             |                    | to SK                  |                               |      |     |      |        |

| t <sub>DIH</sub> | DI Hold Time       | Relative               | 4.5V < V <sub>CC</sub> < 5.5V | 100  |     |      | ns     |

| Bill             |                    | to SK                  | $2.7V < V_{CC} < 5.5V$        | 100  |     |      |        |

|                  |                    |                        | 1.8V < V <sub>CC</sub> < 5.5V | 400  |     |      |        |

| t <sub>PD1</sub> | Output Delay to    | AC Test                | $4.5V < V_{CC} < 5.5V$        |      |     | 250  | ns     |

|                  | "1"                |                        | 2.7V < V <sub>CC</sub> < 5.5V |      |     | 250  |        |

|                  |                    |                        | 1.8V < V <sub>CC</sub> < 5.5V |      |     | 1000 |        |

| t <sub>PD0</sub> | Output Delay to    | AC Test                | $4.5V < V_{CC} < 5.5V$        |      |     | 250  | ns     |

|                  | "0"                |                        | $2.7V < V_{CC} < 5.5V$        |      |     | 250  |        |

|                  |                    |                        | 1.8V < V <sub>CC</sub> < 5.5V |      |     | 1000 |        |

| t <sub>sv</sub>  | CS to Status Valid | AC Test                | $4.5V < V_{CC} < 5.5V$        |      |     | 250  | ns     |

|                  |                    |                        | 2.7V < V <sub>CC</sub> < 5.5V |      |     | 250  |        |

|                  |                    |                        | 1.8V < V <sub>CC</sub> < 5.5V |      |     | 1000 |        |

| t <sub>DF</sub>  | CS to DO in High   | AC Test                | $4.5V < V_{CC} < 5.5V$        |      |     | 100  | ns     |

|                  | Impedance          | CS = V <sub>IL</sub>   | $2.7V < V_{CC} < 5.5V$        |      |     | 100  |        |

|                  |                    |                        | 1.8V < V <sub>CC</sub> < 5.5V |      |     | 400  |        |

| t <sub>wP</sub>  | Write Cycle Time   | •                      | 1.8V < V <sub>CC</sub> < 5.5V | 1    | 3   | 10   | ms     |

| Endurance        | 5.0V, 25° C        |                        |                               | 1M   |     |      | Write  |

| (1)              |                    |                        |                               | 1    |     | 1    | Cycles |

Note: 1. This parameter is characterized and not 100% tested.

| Instruction | SB | Ор   | Address        |             | Data        |                   | Comments                           |

|-------------|----|------|----------------|-------------|-------------|-------------------|------------------------------------|

|             |    | Code | X8             | X16         | X8          | X16               |                                    |

| READ        | 1  | 10   | $A_{10} - A_0$ | $A_9 - A_0$ |             |                   | Reads data stored at specified     |

|             |    |      |                |             |             |                   | memory location.                   |

| EWEN        | 1  | 00   | 11xxxxxxxx     | 11xxxxxxxx  |             |                   | Write enable command (must         |

|             |    |      |                |             |             |                   | be issued before any erase or      |

|             |    |      |                |             |             |                   | write operation).                  |

| ERASE       | 1  | 11   | $A_{10} - A_0$ | $A_9 - A_0$ |             |                   | Erase memory location $A_n - A_0$  |

| WRITE       | 1  | 01   | $A_{10} - A_0$ | $A_9 - A_0$ | $D_7 - D_0$ | D <sub>15</sub> – | Writes memory location $A_n - A_0$ |

|             |    |      |                |             |             | D <sub>0</sub>    |                                    |

| ERAL        | 1  | 00   | 10xxxxxxxx     | 10xxxxxxxx  |             |                   | Erases all memory locations.       |

|             |    |      |                |             |             |                   | Valid only at Vcc = 4.5V to 5.5V   |

| WRAL        | 1  | 00   | 01xxxxxxxx     | 01xxxxxxxx  | $D_7 - D_0$ | D <sub>15</sub> – | Writes all memory locations.       |

|             |    |      |                |             |             | D <sub>0</sub>    | Valid only at Vcc = 4.5V to        |

|             |    |      |                |             |             |                   | 5.5V.                              |

| EWDS        | 1  | 00   | 00xxxxxxxx     | 00xxxxxxxx  |             |                   | Disables all erase or write        |

|             |    |      |                |             |             |                   | instructions                       |

#### **INSTRUCTION SET FOR THE AF93BC86**

Note: The X's in the address field represent don't care values and must be clocked.

#### FUNCTIONAL DESCRIPTION

The AF93BC86 supports 7 different instructions, which must be clocked serially using the CS, SK and DI pins. Before sending each of these instructions, the CS pin must first be pulled high followed by a START bit (logic '1'). The next sequence includes a 2-bit Op Code and usually an 8 or 16-bit address. The next description describes the various functions in the chip.

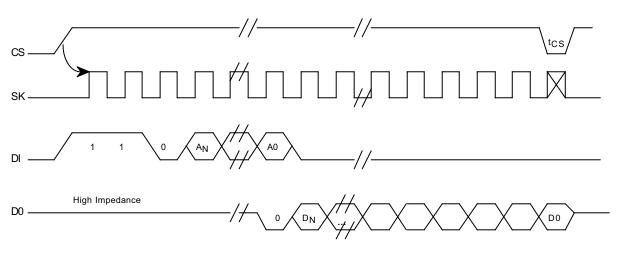

**READ (READ):** The Read (READ) instruction includes the Op Code ("10") followed by the memory address location to be read. After the instruction and address is sent, the data from the memory location can be clocked out using the serial output pin DO. The data changes on the rising edge of the clock, so the falling edge can be used to strobe the output.

Note that during shifting the last address bit, the DO pin is a dummy bit (logic "0").

**ERASE/WRITE (EWEN):** When the chip is first powered-on, no erase or write instructions c an be issued. Only when the Erase/Write Enable (EWEN) instruction is sent will the system be allowed to write to the chip. The EWEN command only needs to be issued once after being powered-on. To disable the chip again, the Erase/Write Disable (EWDS) command can be used.

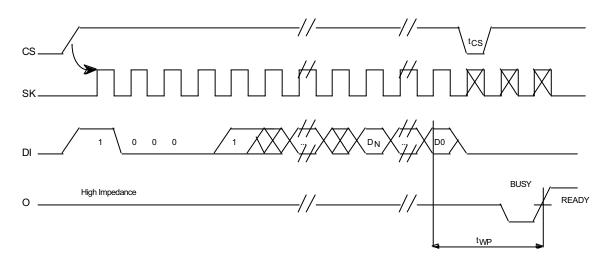

**ERASE (ERASE):** The Erase (ERASE) instruction clears the designated memory location to a logical '1' state. After the Op Code and address location is inputted, the chip will enter into an erase cycle. When the cycle completes, the chip will automatically enter into standby mode.

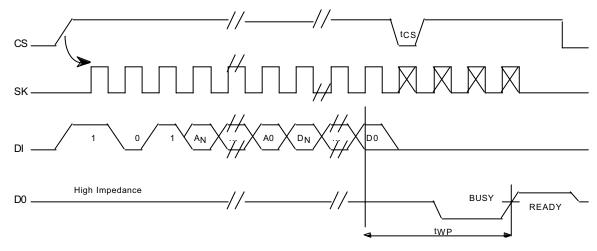

**WRITE (WRITE):** The Write (WRITE) instruction is used to write to a specific memory location. If word mode (x16) is selected, then 16 bits of data will be written into the location. If byte mode (x8) is chosen, then 8 bits of data will be written into the location. The write cycle will begin automatically after the 8 or 16 bits are shifted into the chip.

**ERASE ALL (ERAL):** The Erase All (ERAL) instruction is primarily used for testing purposes and only functions when Vcc=4.5 V to 5.5 V. This instruction will clear the entire memory array to '1'.

**WRITE ALL (WRAL)**: The Write All (WRAL) instruction will program the entire memory array according to the 8 or 16-bit data pattern provided. The instruction will only be valid when Vcc=4.5 V to 5.5 V.

**ERASE/WRITE DISABLE (EWDS):** The Erase/Write Disable (EWDS) instruction blocks any kind of erase or program operations from modifying the contents of the memory array. This instruction should be executed after erasing or programming to prevent accidental data loss.

Note also that the READ instruction will operate regardless of whether the chip is disabled from program and write operations.

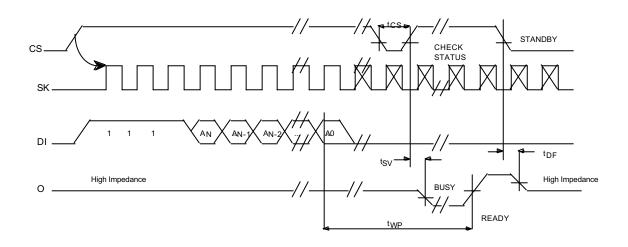

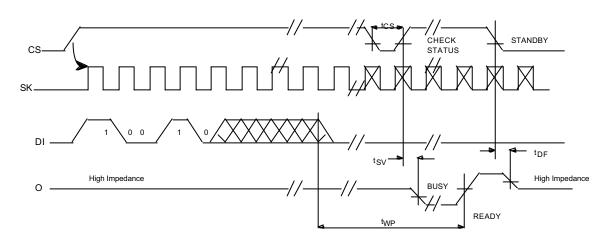

#### Ready/Busy

To determine whether the chip has completed an erase or write operation, the CS signal can be pulled LOW for a minimum of 250 ns ( $t_{cs}$ ) and then pulled back HIGH to enter Ready/Busy mode. If the chip is currently in the programming cycle,  $t_{WP}$ , then the DO pin will go low (logical "0"). When the write cycle completes, the DO pin is pulled high (logical "1") to indicate that the part can receive another instruction. Note that the Ready/Busy polling cannot be done if the chip has already finished and returned back to standby mode.

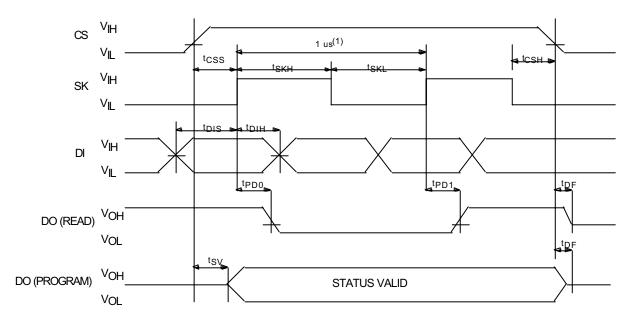

# TIMING DIAGRAMS

# Synchronous Data Timing

Note (1): This is the minimum SK period.

# Organization Key for Timing Diagrams

| I/O            | AF93BC86(16K)   |                 |  |  |  |  |

|----------------|-----------------|-----------------|--|--|--|--|

|                | X8 X16          |                 |  |  |  |  |

| A <sub>N</sub> | A <sub>10</sub> | A <sub>9</sub>  |  |  |  |  |

| D <sub>N</sub> | D <sub>7</sub>  | D <sub>15</sub> |  |  |  |  |

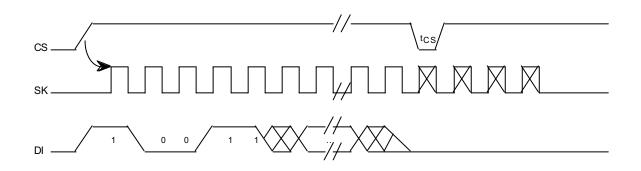

#### **READ TIMING**

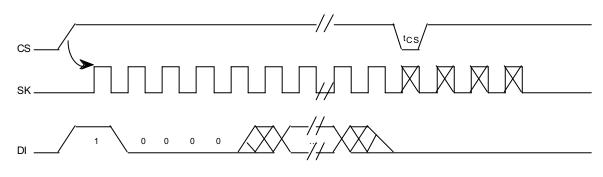

#### **EWEN TIMING**

#### **EWDS TIMING**

#### WRITE TIMING

(1) Valid only at Vcc = 4.5V to 5.5V

#### **ERASE TIMING**

ERAL TIMING<sup>1)</sup>

(1) Valid only at Vcc = 4.5V to 5.5V

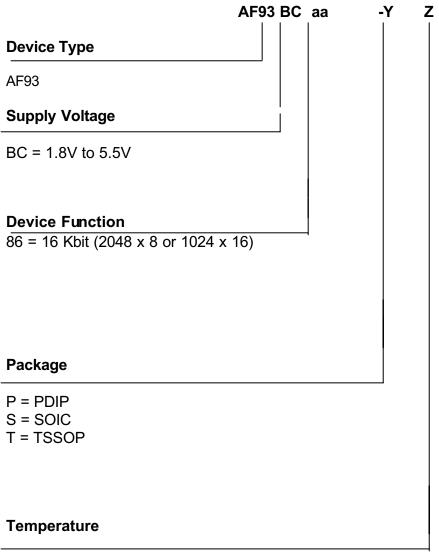

# AF93BC86 Ordering Information

| Ordering Code | Package | Operating Ranges |

|---------------|---------|------------------|

| AF93BC86 – P1 | P       | Lead free        |

| AF93BC86 – SI | S       | Industrial       |

| AF93BC86 – TI | Т       | (-40°C to +85°C) |

|               |         | . , ,            |

|   | Package Type                                                      |  |  |  |  |  |

|---|-------------------------------------------------------------------|--|--|--|--|--|

| Р | 8-pin, 0.300" Wide, Plastic Dual Inline Package (PDIP)            |  |  |  |  |  |

| S | 8-lead, 0.150" Wide, Plastic Gull Wing Small Outline (JEDEC SOIC) |  |  |  |  |  |

| Т | 8-lead, 0.170" Wide, Thin Shrink Small Outline Package (TSSOP)    |  |  |  |  |  |

#### **PRODUCT ORDERING INFORMATION**

I = Industrial (-40°C ~  $85^{\circ}$ C)

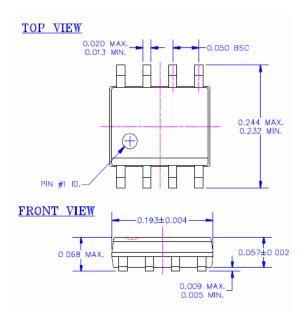

#### PACKAGING INFORMATION

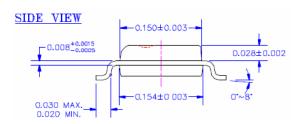

## 8-pin SOIC

| TITLE NAME | 8L SOIC MATRIX<br>PACKAGE OUTLINE DRAWING |                       |                           |  |  |

|------------|-------------------------------------------|-----------------------|---------------------------|--|--|

| SCALE: 9:1 | DATE                                      | TOL                   | MAT'L: N/A                |  |  |

| DWG:       |                                           |                       | SURF.FIN: N/A             |  |  |

| CHKD:      |                                           | XXXX N/A              | HARDNESS: N/A             |  |  |

| APPD.      |                                           | ongle N/A<br>frao N/A | Drawing # P0-S0-8-001 RE\ |  |  |

|            |                                           | 1 OF 1                | REF. N/A F                |  |  |

# 4

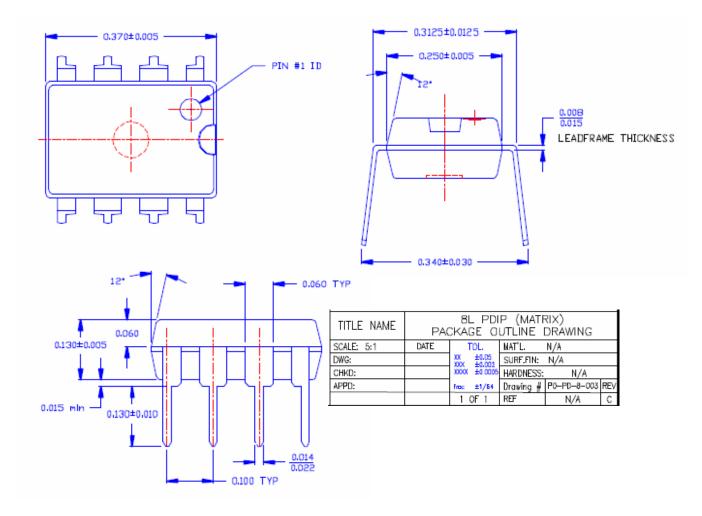

#### 8-pin PDIP

Note:

- 1. All package dimensions do not include mold flash. Mold flash shall not exceed 5 mils.

- 2. Lead dimensions does not include protrusions. Lead protrusions does not exceed 10 mils and lead intrusion is not allowed.

- **3.** All dimensions are in inches.

# 4

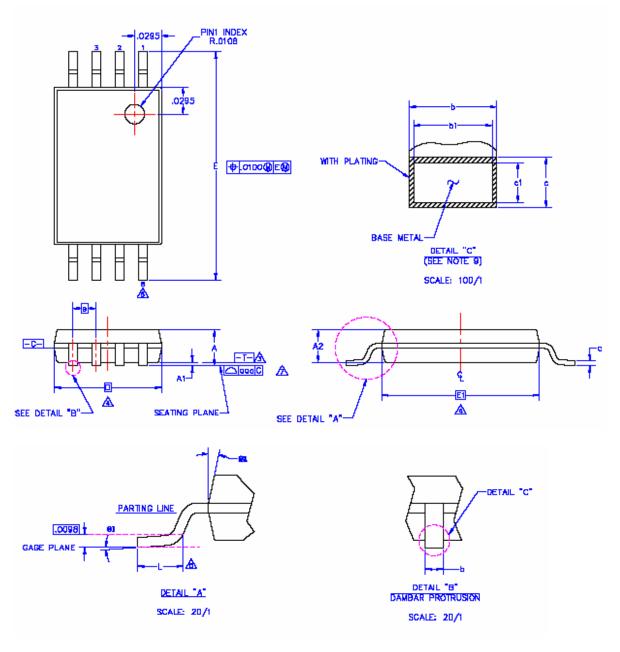

### 8-pin TSSOP

(continued on next page)

#

| SYMBOL |                |          | DIME | ISION  |            |        |  |  |  |

|--------|----------------|----------|------|--------|------------|--------|--|--|--|

|        | JEDEC STANDARD |          |      |        |            |        |  |  |  |

|        |                | IN MAK   |      |        | IN INCH    |        |  |  |  |

|        | MIN.           | NOM.     | MAX. | MIN.   | NOM.       | MAX.   |  |  |  |

| A      | -              | -        | 1.20 | -      | -          | 0.0472 |  |  |  |

| A1     | 0.05           | -        | 0.15 | 0.0020 | -          | 0.0059 |  |  |  |

| A2     | 0.80           | 1.00     | 1.05 | 0.0315 | 0.0394     | 0.0413 |  |  |  |

| Ъ      | 0.19           | -        | 0.30 | 0.0075 | -          | 0.0118 |  |  |  |

| bi     | 0.19           | 0.22     | 0.25 | 0.0075 | 0.0087     | 0.0098 |  |  |  |

| С      | 0.09           | -        | 0.20 | 0.0035 | -          | 0.0079 |  |  |  |

| c1     | 0.09           | -        | 0.16 | 0.0035 | -          | 0.0063 |  |  |  |

| D      | 2.90           | 3.00     | 3.10 | 0.1142 | 0.1181     | 0.1220 |  |  |  |

| e      |                | 0.65 BSC |      |        | 0.0256 BSC |        |  |  |  |

| E      |                | 6.4 BSC  |      |        | 0.2520 BSC |        |  |  |  |

| Ei     | 4,30           | 4.40     | 4.50 | 0,1693 | 0.1732     | 0.1772 |  |  |  |

| L      | 0.45           | 0.60     | 0.75 | 0.0177 | 0.0236     | 0.0295 |  |  |  |

| A1     | 0              | _        | 8    | 0      | _          | 8      |  |  |  |

| 62     |                | 12°REF   |      |        | 12°REF     |        |  |  |  |

| 900    |                | 0.10     |      |        | 0.0039     |        |  |  |  |

| TITLE NAME  | 8L TSSOP<br>PACKAGE OUTLINE DRAWING |                     |        |             |     |  |

|-------------|-------------------------------------|---------------------|--------|-------------|-----|--|

| SCALE: 10:1 | DATE                                | DATE TOL MAT'L: N/A |        |             |     |  |

| DWG:        |                                     |                     | SURF.F | IN: N/A     |     |  |

| CHKD:       |                                     | N/A                 | HARDNE | SS: N/A     |     |  |

| APPD:       |                                     |                     | DG NO  | P0-TS-8-001 | REV |  |

|             |                                     | 1 OF 1              | REF.   | N/A         | В   |  |

#### REVISIONS

| Version Number | Description               | Page  | Date       |

|----------------|---------------------------|-------|------------|

| 1.04           | Add lead free description | 1, 11 | 10/15/2007 |

Aplus Flash Technology, Inc. 1982A Zanker Road San Jose, CA 95112 www.aplusflash.com

Note the following details:

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. Aplus takes no responsibility to ensure that the application meets the required specifications. No representation or warranty is given and no liability is assumed by Aplus Flash Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Aplus' products as critical components in life support systems is not authorized except with express written approval by Aplus. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

Aplus makes no warranty, representation or guarantee, express or implied, regarding the suitability of its IP or products for any particular purpose, nor that the use of its products or IP will not infringe its intellectual property rights or the rights of third parties with respect to particular use or application and specifically disclaims any and all liability arising out of any such use or application, including but not limited to , consequential or incidental damages. Aplus' products and IP are not designed, intended or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application and specifically disclaims any and all liability arising out of any such use or application and specifically disclaims any and all liability arising out of any other application and specifically disclaims any and all liability arising out of any such use or application, including but not limited to, consequential or incidental damages.