# 1 Introduction

## 1.1 FEATURES

- 14-Bit 85-MSPS High-Performance Single ADC

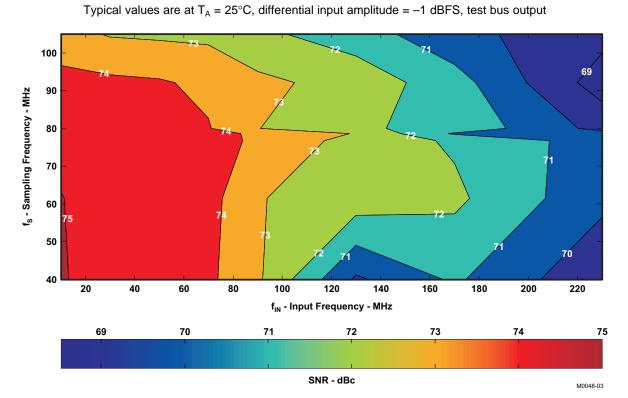

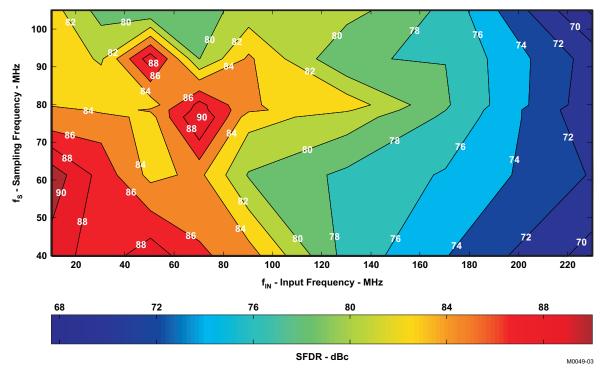

- At  $f_{\text{IN}}$  = 140 MHz, SNR  $\geq$  71 dBFS, SFDR  $\geq$  79 dBc

- At  $f_{\text{IN}}$  = 70 MHz, SNR  $\geq$  73 dBFS, SFDR  $\geq$  85 dBc

- Independent Clocks for ADC and DDC With Built-In FIFO

- Programmable Closed-Loop VGA Control With 6-Bit Outputs for ADC

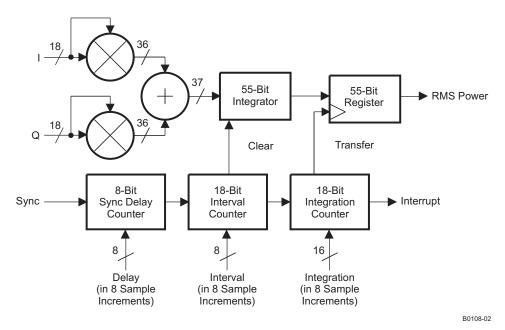

- Received Total Wideband Power (RTWP) Measurement for the Composite Power Across Carriers With Programmable Time Window for Measurement

- 8 UMTS Digital Downconverter (DDC) Channels or 16 CDMA/TD-SCDMA DDC Channels With Programmable 18-Bit Filter Coefficients

- Each DDC Channel Provides:

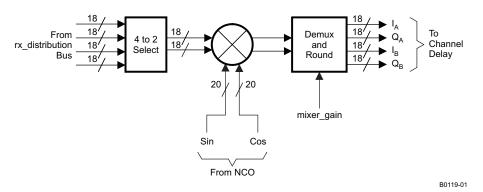

- Real or Complex DDC Inputs

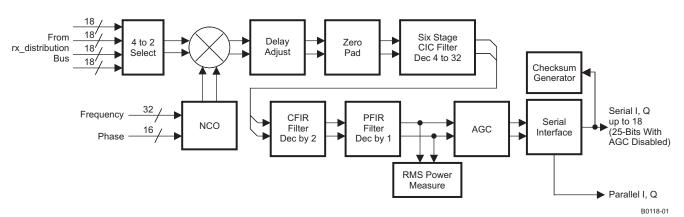

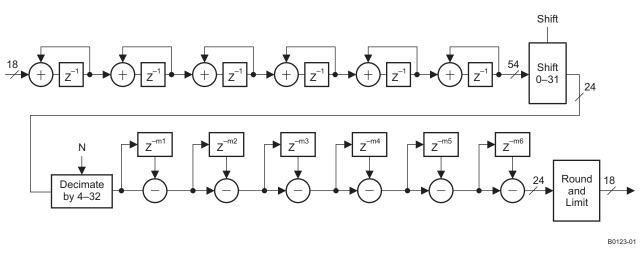

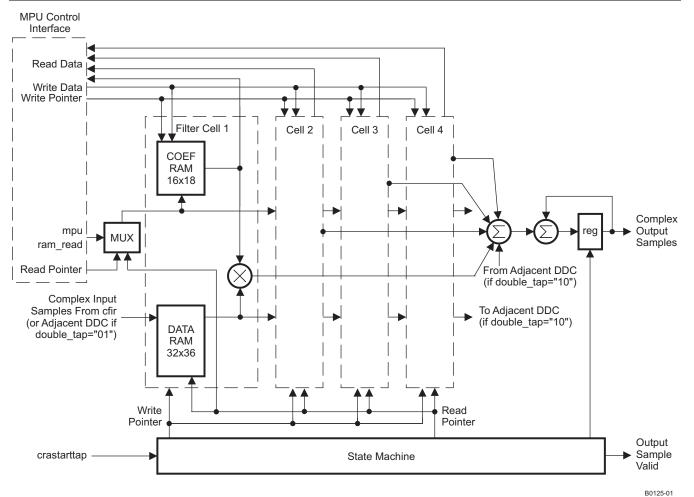

- UMTS Mode Rx Filtering: 6-Stage CIC (m = 1 or 2), up to 40-Tap CFIR, up to 64-Tap PFIR

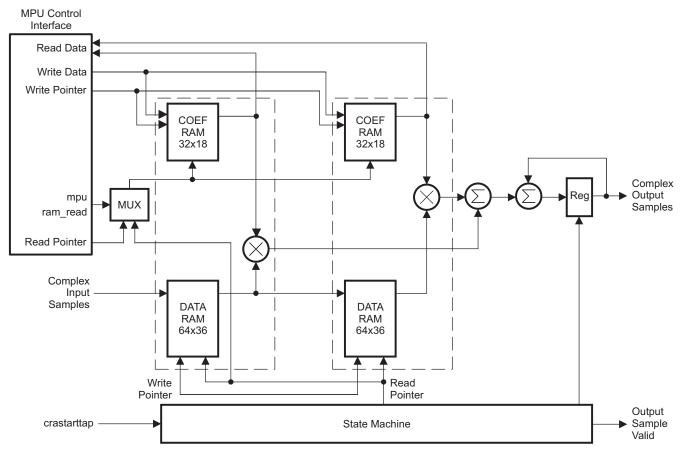

- CDMA Mode Rx Filtering: 6-Stage CIC (m = 1 or 2), up to 64-Tap CFIR, up to 64-Tap PFIR

- Individual Channel-Specific Power Measurements

- A Dedicated Final AGC

- Test Bus to Monitor Data at Different Stages of the DDC Signal Path

- 3.3-V Analog Supplies, 1.5-V Digital Core Supply, 3.3-V Digital I/O Supply

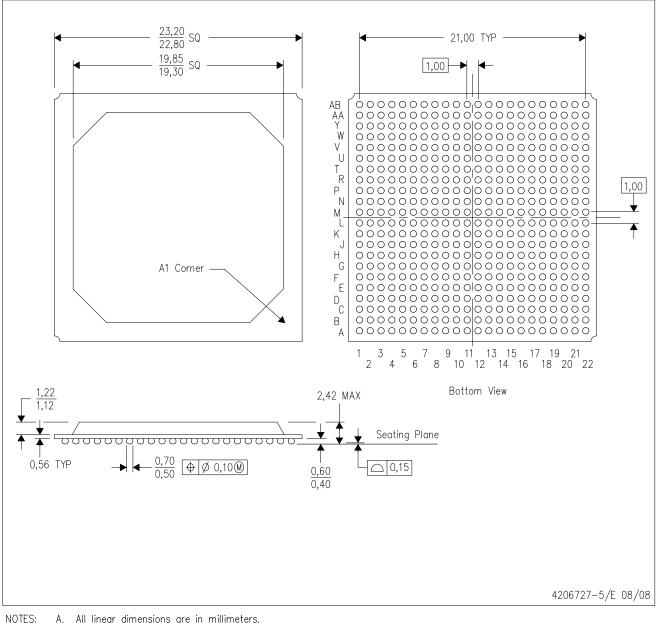

- 484-Ball Plastic BGA (23 mm  $\times$  23 mm) With 1,0-mm Pitch

- Power Dissipation (Eight Active DDC Channels): 2.3 W

## **1.2 APPLICATIONS**

- Wireless Base Station Receiver

- Multi-Carrier Digital Receiver

- UMTS (8 Carriers-1 Sector)

- CDMA (16 Carriers-1 Sector)

- TD-SCDMA (16 Carriers-1 Sector)

- Digital Radio Receivers

- Wideband Receivers

- Software Radios

- Wireless Local Loop

- Intelligent Antenna Systems

#### Contents

| Intro | duction 1                                                                                              |

|-------|--------------------------------------------------------------------------------------------------------|

| 1.1   | FEATURES 1                                                                                             |

| 1.2   | APPLICATIONS 1                                                                                         |

| Gene  | eral Description <u>3</u>                                                                              |

| SPE   | CIFICATIONS 4                                                                                          |

| 3.1   | PACKAGE ORDERING INFORMATION 4                                                                         |

| 3.2   | ABSOLUTE MAXIMUM RATINGS 4                                                                             |

| 3.3   | RECOMMENDED OPERATING CONDITIONS 4                                                                     |

| 3.4   | THERMAL CHARACTERISTICS 5                                                                              |

| 3.5   | POWER DISSIPATION                                                                                      |

| 3.6   | ANALOG ELECTRICAL CHARACTERISTICS 6                                                                    |

| 3.7   | DIGITAL CHIP DC CHARACTERISTICS                                                                        |

| 3.8   | DIGITAL CHIP AC TIMING CHARACTERISTICS 9                                                               |

| AFE   | 8405 PINS <u>10</u>                                                                                    |

| 4.1   | Analog Section Signals10                                                                               |

| 4.2   | Digital Receive Section Signals 11                                                                     |

| 4.3   | Microprocessor Signals 14                                                                              |

| 4.4   | JTAG Signals                                                                                           |

|       | 1.1<br>1.2<br>Gene<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>AFE<br>4.1<br>4.2<br>4.3 |

|   | 4.5   | Factory Test and No-Connect Signals             | <u>15</u> |

|---|-------|-------------------------------------------------|-----------|

|   | 4.6   | Power and Ground Signals                        | <u>15</u> |

|   | 4.7   | Digital Supply Monitoring                       | <u>16</u> |

|   | 4.8   | JTAG                                            | <u>16</u> |

|   | 4.9   | AFE8405 and AFE8406 PCB Design Compatibility.   | <u>16</u> |

| 5 | Туріс | cal Characteristics                             | 17        |

| 6 | ANA   | LOG-TO-DIGITAL CONVERTERS                       | <u>24</u> |

|   | 6.1   | ADC Operation                                   | <u>24</u> |

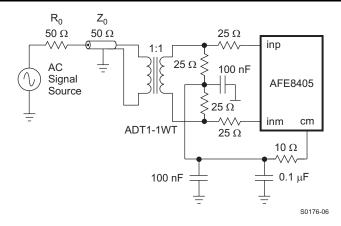

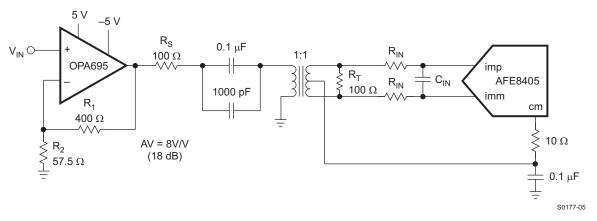

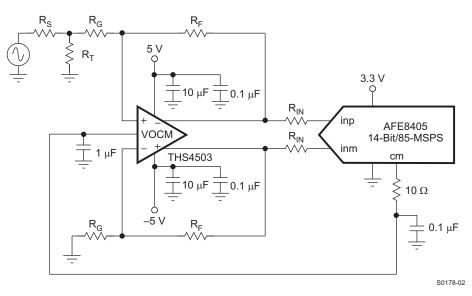

|   | 6.2   | ADC Input Configuration                         | <u>24</u> |

|   | 6.3   | ADC Input Voltage Overstress                    | <u>28</u> |

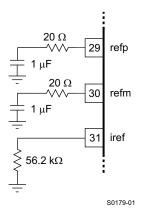

|   | 6.4   | ADC Reference Circuit                           | <u>28</u> |

|   | 6.5   | ADC Clock Input                                 | <u>28</u> |

| 7 | REC   | EIVE DIGITAL SIGNAL PROCESSING                  | <u>30</u> |

|   | 7.1   | Receive Input Interface                         | <u>30</u> |

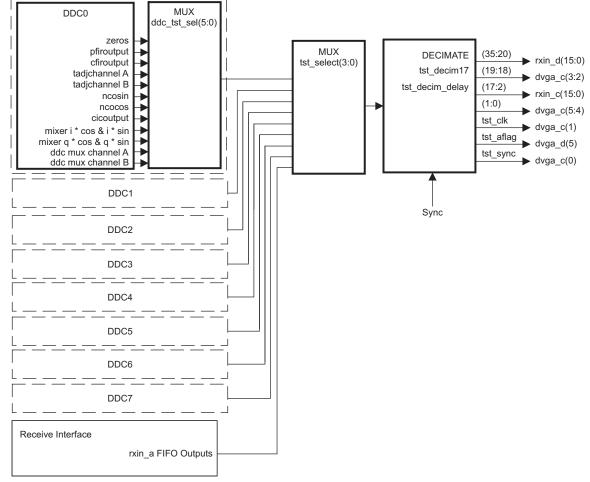

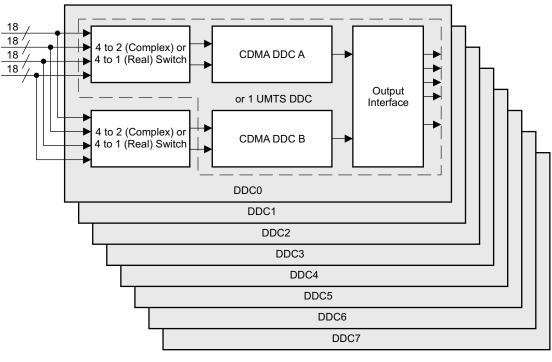

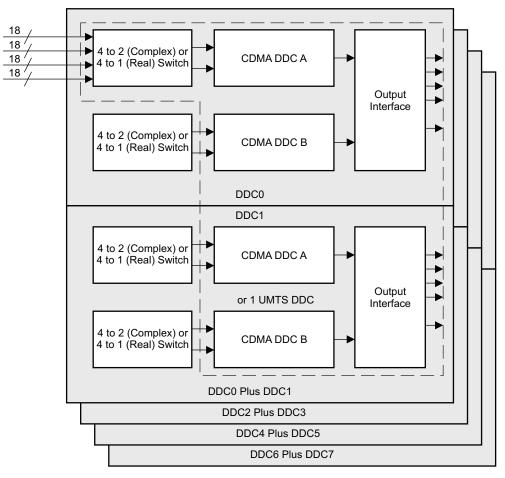

|   | 7.2   | DDC Organization                                | <u>43</u> |

| 8 | AFE8  | 3405 GENERAL CONTROL                            | <u>73</u> |

|   | 8.1   | Microprocessor Interface Control Data, Address, |           |

|   |       | and Strobes                                     | <u>73</u> |

|   |       |                                                 |           |

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this document.

SLWS212A-OCTOBER 2008-REVISED JANUARY 2009

8.2

AFE8405 Programming ..... 77

8.4

8.3

#### 2 General Description

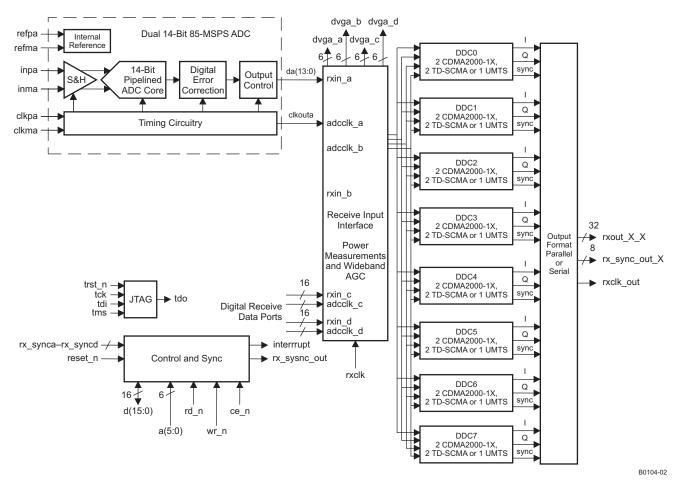

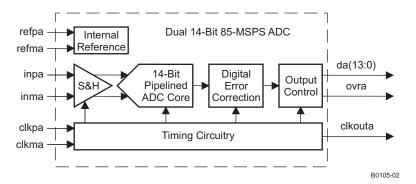

The AFE8405 is a multichannel communications signal processor that provides analog-to-digital conversion and digital downconversion optimized for cellular base transceiver systems. The device supports UMTS, CDMA-1X, and TD-SCDMA air-interface cellular standards.

The AFE8405 provides up to 8 UMTS digital downconverter channels (DDC), 16 CDMA DDCs or 16 TD-SCDMA DDCs. The DDC channels are independent and operate simultaneously.

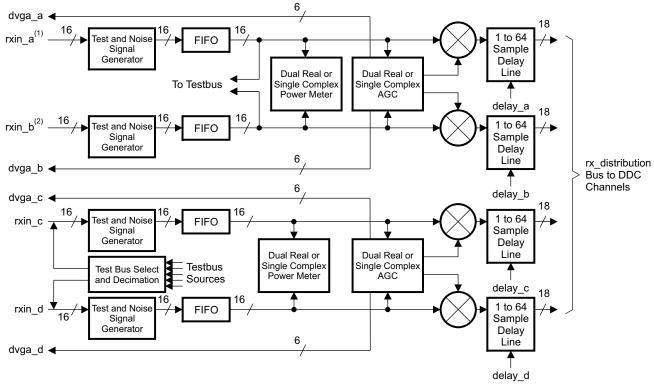

The AFE8405 DDCs have three input ports; one is hardwired to the internal 14-bit analog-to-digital converter (rxin\_a) and two are 16-bit digital inputs (rxin\_c, rxin\_d). Each DDC channel can be programmed to accept data from any one of the three input ports; rxin\_b is not used.

Figure 2-1. Functional Block Diagram

TEXAS INSTRUMENTS

www.ti.com

# 3 SPECIFICATIONS

### 3.1 PACKAGE ORDERING INFORMATION

| PRODUCT | PACKAGE-LEADS   | PACKAGE<br>DESIGNATOR | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER | TRANSPORT<br>MEDIA,<br>QUANTITY |

|---------|-----------------|-----------------------|-----------------------------------|--------------------|--------------------|---------------------------------|

| AFE8405 | Plastic BGA-484 | ZDQ                   | $-40^{\circ}$ C to $85^{\circ}$ C | AFE8405I           | AFE8405IZDQ        | Tray, 60                        |

# 3.2 ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

|                  |                                                  | UNIT                    |

|------------------|--------------------------------------------------|-------------------------|

| Analog Chi       | p                                                |                         |

| AVDD             | Analog supply voltage                            | –0.3 V to 3.7 V         |

| DRVDD            | I/O ring supply voltage                          | –0.3 V to 3.7 V         |

|                  | Ground difference DRVSS to AVSS                  | -0.1 V to 0.1 V         |

|                  | Analog input voltage                             | –0.15 V to 3.6 V        |

|                  | Digital input voltage                            | -0.3 V to DRVDD + 0.3 V |

| Digital Chip     | )                                                |                         |

| VDDS             | Pad ring supply voltage                          | –0.3 V to 3.7 V         |

| DVDD             | Core supply voltage                              | -0.3 V to 1.8 V         |

|                  | Digital input voltage                            | -0.3 V to VDDS + 0.3 V  |

| Entire Chip      |                                                  |                         |

|                  | Clamp current for an input or output             | -20 mA to 20 mA         |

| T <sub>STG</sub> | Storage temperature                              | −65°Cto 140°C           |

| TJ               | Junction temperature                             | 105°C                   |

|                  | Lead soldering temperature (10 seconds)          | 300°C                   |

|                  | ESD classification (tested to EIA/JESD22-A114-B) | Class 2                 |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 3.3 RECOMMENDED OPERATING CONDITIONS

|                               |                                        | MIN   | NOM | MAX   | UNIT     |

|-------------------------------|----------------------------------------|-------|-----|-------|----------|

| Analog C                      | Chip                                   |       |     |       |          |

| AVDD                          | Analog supply voltage                  | 3     | 3.3 | 3.6   | V        |

| DRVDD                         | I/O ring supply voltage                | 3     | 3.3 | 3.6   | V        |

| V <sub>ID</sub>               | Differential input voltage range       |       | 2.3 |       | V        |

| VCM                           | Common-mode input voltage              | 1.5   |     | 1.6   | V        |

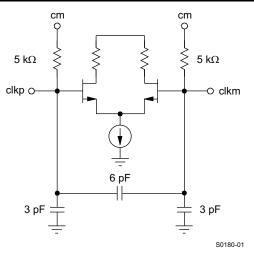

|                               | Differential clock inputs              |       | 3   |       | $V_{PP}$ |

|                               | Clock input duty cycle                 |       | 50% |       |          |

| Digital C                     | hip                                    |       |     |       |          |

| VDDS                          | I/O ring supply voltage                | 3     |     | 3.6   | V        |

| DVDD                          | Core supply voltage                    | 1.425 |     | 1.575 | V        |

|                               | Supply voltage difference, VDDS – DVDD |       |     | 2     | V        |

| Entire Ch                     | nip                                    |       |     |       |          |

| T <sub>A</sub>                | Temperature ambient, no air flow       | -40   |     | 85    | °C       |

| T <sub>J</sub> <sup>(1)</sup> | Junction temperature                   |       |     | 105   | °C       |

(1) Thermal management is required for full-rate operation. The circuit is designed for junction temperatures up to 125°C. Sustained operation at elevated temperatures reduces long-term reliability. Lifetime calculations based on maximum junction temperature of 105°C.

# 3.4 THERMAL CHARACTERISTICS

|                | THERMAL CONDUCTIVITY <sup>(1)</sup>  | MIN | TYP  | MAX | UNIT |

|----------------|--------------------------------------|-----|------|-----|------|

|                | Theta junction-to-ambient (0 LFPM)   |     | 14   |     | °C/W |

| P              | Theta junction-to-ambient (100 LFPM) |     | 13   |     | °C/W |

| $R_{\thetaJA}$ | Theta junction-to-ambient (250 LFPM) |     | 12.2 |     | °C/W |

|                | Theta junction-to-ambient (500 LFPM) |     | 11.6 |     | °C/W |

| $R_{\thetaJC}$ | Theta junction-to-case               |     | 2.8  |     | °C/W |

(1) Air flow reduces  $R_{\theta JA}$  and is highly recommended.

# 3.5 POWER DISSIPATION

Typical values at T<sub>A</sub> = 25°C, UMTS mode, sampling rate = 61.44 MSPS, and rxclk = 122.88 MHz (unless otherwise noted)

|                                              | PARAMETER                                 | TEST CONDITIONS           | MIN TYP MAX | UNIT |

|----------------------------------------------|-------------------------------------------|---------------------------|-------------|------|

| I <sub>AVDD</sub>                            | Analog supply current                     | Six active DDC channels   | 123         | mA   |

| I <sub>DRVDD</sub> Analog I/O supply current |                                           |                           | 21.5        | mA   |

| I <sub>DVDD</sub>                            | Digital core supply current               |                           | 959         | mA   |

| I <sub>VDDS</sub>                            | Digital I/O supply current <sup>(1)</sup> |                           | 100         | mA   |

|                                              | Analog power dissipation                  |                           | 477         | mW   |

|                                              | Digital power dissipation <sup>(2)</sup>  |                           | 1.439       | W    |

|                                              | Total power dissipation <sup>(2)</sup>    |                           | 1.9         | W    |

| I <sub>AVDD</sub>                            | Analog supply current                     | Eight active DDC channels | 123         | mA   |

| I <sub>DRVDD</sub>                           | Analog I/O supply current                 |                           | 21.5        | mA   |

| I <sub>DVDD</sub>                            | Digital core supply current               |                           | 1.198       | А    |

| $I_{VDDS}$                                   | Digital I/O supply current <sup>(1)</sup> |                           | 115         | mA   |

|                                              | Analog power dissipation                  |                           | 477         | mW   |

|                                              | Digital power dissipation <sup>(2)</sup>  |                           | 1.797       | W    |

|                                              | Total power dissipation <sup>(2)</sup>    |                           | 2.3         | W    |

(1) Current consumption on the digital I/O supply is primarily due to the external loads and follows C × V × F. Internal loads are estimated at 2 pF per terminal. Data outputs transition once every four clocks, whereas clock outputs transition every cycle. In general, I<sub>VDDS</sub> = Σ (DataPad/4) × C × V × F + Σ ClockPad × C × V × F.

(2) Excluding current consumption from the digital I/O supply, which is dependent on external loads

www.ti.com

SLWS212A-OCTOBER 2008-REVISED JANUARY 2009

# 3.6 ANALOG ELECTRICAL CHARACTERISTICS

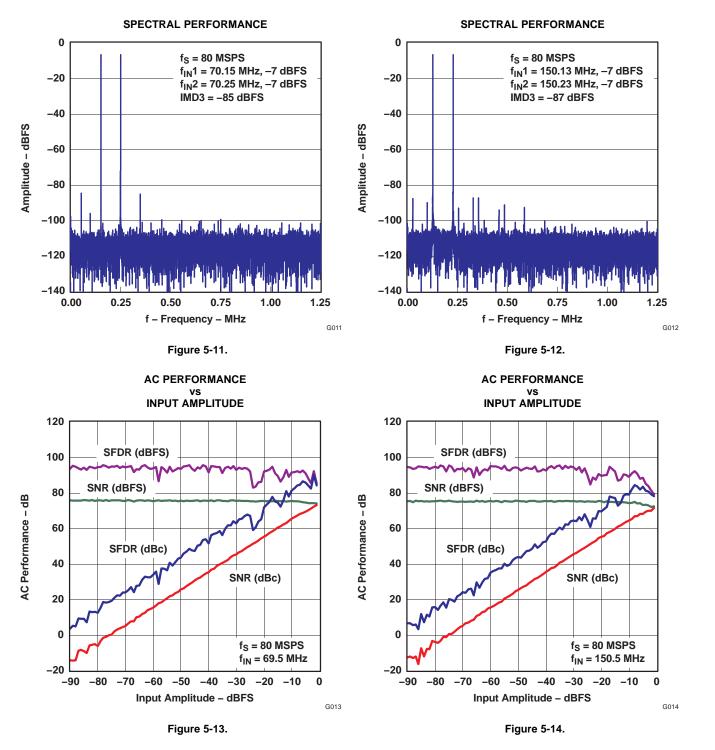

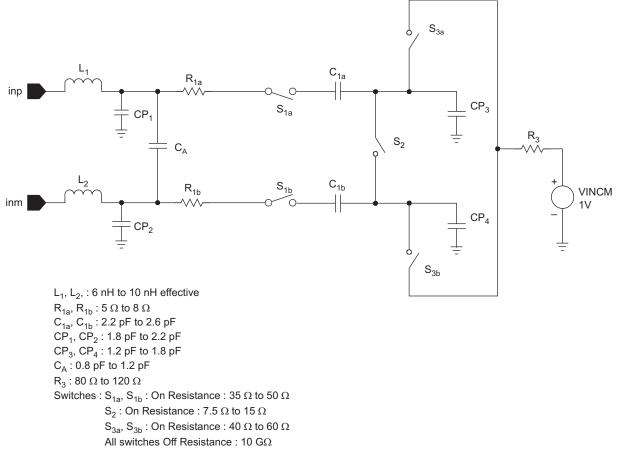

Typical values at  $T_A = 25^{\circ}$ C, minimum and maximum values over temperature range of  $T_A = -40^{\circ}$ C to 85°C, sampling rate = 80 MSPS, 50% clock duty cycle, AVDD = DRVDD = 3.3 V, -1-dBFS differential input, internal reference, and 3-VPP differential clock (unless otherwise noted)

|                  | PARAMETER                                                                    | TEST CONDITIONS                                                            | MIN TYP       | MAX | UNIT            |

|------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------|---------------|-----|-----------------|

|                  | Resolution                                                                   |                                                                            | 14            |     | Bits            |

| Analog           | Inputs                                                                       |                                                                            |               |     |                 |

| V <sub>ID</sub>  | Differential input voltage range                                             |                                                                            | 2.3           |     | V <sub>PP</sub> |

| C <sub>ID</sub>  | Differential input capacitance                                               |                                                                            | 3.2           |     | pF              |

| I <sub>IC</sub>  | Common-mode input current                                                    | 2 mA per input, 4 mA total                                                 | 4             |     | mA              |

|                  | Analog input bandwidth                                                       | Source impedance = 50 $\Omega$                                             | 750           |     | MHz             |

| Convers          | sion Characteristics                                                         |                                                                            | 1             |     |                 |

|                  |                                                                              | $f_{rxclk} = 1 \times f_{ADC} ch_rate_sel = rate_sel = 00$                 |               | 85  |                 |

| f                | ADC clock rate ( $f_{clkpa} = f_{clkma} = f_{ADC}$ )                         | $f_{rxclk} = 2 \times f_{ADC} ch_rate_sel = rate_sel = 01$                 |               | 80  | MSPS            |

| f <sub>ADC</sub> | ADC CIOCK TALE (I <sub>clkpa</sub> = I <sub>clkma</sub> = I <sub>ADC</sub> ) | $f_{rxclk} = 4 \times f_{ADC} ch_rate_sel = rate_sel = 10$                 |               | 40  | INIOF O         |

|                  |                                                                              | $f_{rxclk} = 8 \times f_{ADC} ch_rate_sel = rate_sel = 11$                 |               | 20  |                 |

|                  | Data latency – ADC input to FIFO input                                       |                                                                            | 16.5          |     | Clock<br>Cycles |

| Internal         | Reference Voltages                                                           |                                                                            |               |     |                 |

| refma            | Lower reference voltages                                                     |                                                                            | 1             |     | V               |

| refpa            | Upper reference voltages                                                     |                                                                            | 2.15          |     | V               |

|                  | Reference error                                                              |                                                                            | ±3.5          |     | % of FS         |

| cma              | Common-mode output voltages                                                  |                                                                            | 1.55<br>±0.05 |     | V               |

| Dynamie          | c DC Characteristics and Accuracy                                            |                                                                            |               |     |                 |

|                  | No missing codes                                                             |                                                                            | tested        |     |                 |

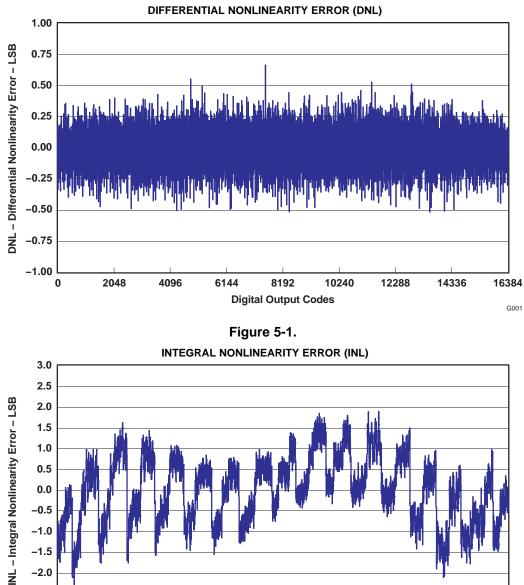

| DNL              | Differential linearity error                                                 | f <sub>IN</sub> = 1 MHz                                                    | ±0.65         |     | LSBs            |

| INL              | Integral linearity error                                                     | f <sub>IN</sub> = 1 MHz                                                    | ±4            |     | LSBs            |

|                  | Offset error                                                                 |                                                                            | ±4            |     | mV              |

|                  | Offset temperature coefficient                                               |                                                                            | 7             |     | μV/°C           |

|                  | Gain error                                                                   |                                                                            | ±0.5          |     | % of FS         |

|                  | Gain temperature coefficient                                                 |                                                                            | 0.0015        |     | Δ%/°C           |

| Dynami           | c AC Characteristics                                                         |                                                                            |               |     |                 |

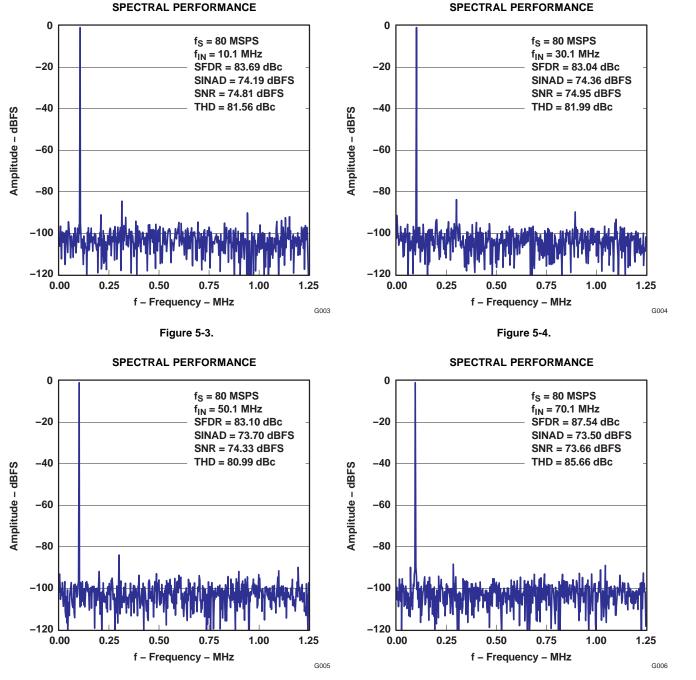

|                  |                                                                              | f <sub>IN</sub> = 10 MHz, T <sub>A</sub> = 25°C                            | 74.5          |     |                 |

|                  |                                                                              | f <sub>IN</sub> = 30 MHz                                                   | 74            |     |                 |

|                  |                                                                              | f <sub>IN</sub> = 50 MHz                                                   | 73.5          |     |                 |

|                  |                                                                              | f <sub>IN</sub> = 70 MHz, T <sub>A</sub> = 25°C                            | 73.5          |     | 1               |

| SNR              | Signal-to-noise ratio                                                        | $f_{IN} = 70 \text{ MHz}, T_A = 25^{\circ}\text{C to } 85^{\circ}\text{C}$ | 70 73         |     | dBFS            |

|                  |                                                                              | $f_{IN} = 70 \text{ MHz}, T_A - 40^{\circ}\text{C}$                        | 69 73         |     |                 |

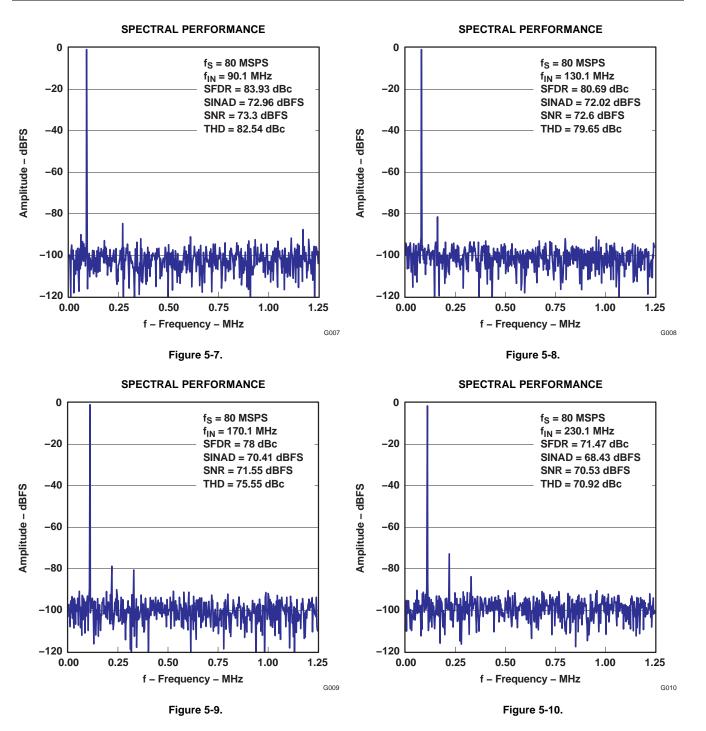

|                  |                                                                              | f <sub>IN</sub> = 130 MHz                                                  | 71.5          |     |                 |

|                  |                                                                              | f <sub>IN</sub> = 170 MHz                                                  | 70.5          |     |                 |

|                  |                                                                              | f <sub>IN</sub> = 230 MHz                                                  | 69            |     |                 |

|                  | RMS output noise                                                             | INPA and INMA tied to CMA                                                  | 1.1           |     | LSBs            |

#### ANALOG ELECTRICAL CHARACTERISTICS (continued)

Typical values at  $T_A = 25^{\circ}$ C, minimum and maximum values over temperature range of  $T_A = -40^{\circ}$ C to 85°C, sampling rate = 80 MSPS, 50% clock duty cycle, AVDD = DRVDD = 3.3 V, -1-dBFS differential input, internal reference, and 3-VPP differential clock (unless otherwise noted)

|         | PARAMETER                                 | TEST CONDITIONS                                                            | MIN TYP | MAX | UNIT  |  |  |

|---------|-------------------------------------------|----------------------------------------------------------------------------|---------|-----|-------|--|--|

| Dynamic | AC Characteristics (Continued)            |                                                                            |         |     |       |  |  |

|         |                                           | $f_{IN}$ = 10 MHz, $T_A$ = 25°C                                            | 84      |     |       |  |  |

|         |                                           | f <sub>IN</sub> = 30 MHz                                                   | 83.5    |     |       |  |  |

|         |                                           | f <sub>IN</sub> = 50 MHz                                                   | 84      |     |       |  |  |

| SFDR    | Sourious free dynamic range               | $f_{IN}$ = 70 MHz, $T_A$ = 25°C                                            | 85      |     | dBc   |  |  |

| SFDR    | Spurious free dynamic range               | $f_{\text{IN}}$ = 70 MHz, $T_{\text{A}}$ = -40°C to 85°C                   | 77 82   |     |       |  |  |

|         |                                           | f <sub>IN</sub> = 130 MHz                                                  | 81      |     |       |  |  |

|         |                                           | f <sub>IN</sub> = 170 MHz                                                  | 76      |     |       |  |  |

|         |                                           | f <sub>IN</sub> = 230 MHz                                                  | 68.5    |     |       |  |  |

|         |                                           | f <sub>IN</sub> = 10 MHz, T <sub>A</sub> = 25°C                            | 95.8    |     |       |  |  |

|         |                                           | f <sub>IN</sub> = 30 MHz                                                   | 95      |     |       |  |  |

|         |                                           | f <sub>IN</sub> = 50 MHz                                                   | 97.5    |     |       |  |  |

| HD2     | Second harmonic                           | f <sub>IN</sub> = 70 MHz, T <sub>A</sub> = 25°C                            | 95      |     | dBc   |  |  |

|         |                                           | f <sub>IN</sub> = 130 MHz                                                  | 81.5    |     |       |  |  |

|         |                                           | f <sub>IN</sub> = 170 MHz                                                  | 76      |     |       |  |  |

|         |                                           | f <sub>IN</sub> = 230 MHz                                                  | 68.5    |     |       |  |  |

|         |                                           | f <sub>IN</sub> = 10 MHz, T <sub>A</sub> = 25°C                            | 84      |     |       |  |  |

|         |                                           | f <sub>IN</sub> = 30 MHz                                                   | 83.5    |     |       |  |  |

|         | Third harmonic                            | f <sub>IN</sub> = 50 MHz                                                   | 82.5    |     | dBc   |  |  |

| HD3     |                                           | f <sub>IN</sub> = 70 MHz, T <sub>A</sub> = 25°C                            | 85      |     |       |  |  |

|         |                                           | f <sub>IN</sub> = 130 MHz                                                  | 92      |     |       |  |  |

|         |                                           | f <sub>IN</sub> = 170 MHz                                                  | 79      |     |       |  |  |

|         |                                           | f <sub>IN</sub> = 230 MHz                                                  | 83      |     |       |  |  |

|         |                                           | $f_{IN} = 10 \text{ MHz}, T_A = 25^{\circ}\text{C}$                        | 95.5    |     |       |  |  |

|         | Worst harmonic/spur other than HD2 or HD3 | $f_{IN} = 70 \text{ MHz}, T_A = 25^{\circ}\text{C}$                        | 95      |     | dBc   |  |  |

|         |                                           | $f_{IN} = 10 \text{ MHz}, T_A = 25^{\circ}\text{C}$                        | 74      |     |       |  |  |

|         |                                           | $f_{IN} = 30 \text{ MHz}$                                                  | 73.5    |     |       |  |  |

|         |                                           | f <sub>IN</sub> = 50 MHz                                                   | 73.5    |     |       |  |  |

|         |                                           | $f_{IN} = 70 \text{ MHz}, T_A = 25^{\circ}\text{C}$                        | 73      |     |       |  |  |

| SINAD   | Signal-to-noise plus distortion           | $f_{IN} = 70 \text{ MHz}, T_A = 25^{\circ}\text{C to } 85^{\circ}\text{C}$ | 70 72   |     | dBFS  |  |  |

|         |                                           | $f_{IN} = 70 \text{ MHz}, T_A = -40^{\circ}\text{C}$                       | 69 72   |     |       |  |  |

|         |                                           | f <sub>IN</sub> = 130 MHz                                                  | 71      |     |       |  |  |

|         |                                           | f <sub>IN</sub> = 170 MHz                                                  | 69      |     |       |  |  |

|         |                                           | f <sub>IN</sub> = 230 MHz                                                  | 66      |     |       |  |  |

|         |                                           | $f_{IN} = 10 \text{ MHz}, T_A = 25^{\circ}\text{C}$                        | 82.5    |     |       |  |  |

|         |                                           | $f_{IN} = 30 \text{ MHz}$                                                  | 82      |     |       |  |  |

|         |                                           | $f_{IN} = 50 \text{ MHz}$                                                  | 82      |     |       |  |  |

| THD     | Total harmonic distortion                 | $f_{IN} = 70 \text{ MHz}, T_A = 25^{\circ}\text{C}$                        | 83.5    |     | dBc   |  |  |

|         |                                           | $f_{IN} = 130 \text{ MHz}$                                                 | 80      |     | . = • |  |  |

|         |                                           | $f_{\rm IN} = 170 \text{ MHz}$                                             | 74      |     |       |  |  |

|         |                                           | $f_{\rm IN} = 230 \text{ MHz}$                                             | 68      |     |       |  |  |

|         | Channel-to-channel crosstalk              | $f_{IN} = 225 \text{ MHz}$                                                 | 95      |     | dBc   |  |  |

SLWS212A-OCTOBER 2008-REVISED JANUARY 2009

www.ti.com

# 3.7 DIGITAL CHIP DC CHARACTERISTICS

$T_A = -40^{\circ}C$  to  $85^{\circ}C$  (unless otherwise noted)

|                  | PARAMETER <sup>(1)</sup> <sup>(2)(3)</sup>                                  | TEST CONDITIONS                                                                  | VDDS = | 3 V to 3 | 3.6 V |      |

|------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------|--------|----------|-------|------|

|                  | PARAMETER                                                                   | TEST CONDITIONS                                                                  | MIN    | TYP      | MAX   | UNIT |

| VIL              | Voltage input, low                                                          |                                                                                  |        |          | 0.8   | V    |

| VIH              | Voltage input, high                                                         |                                                                                  | 2      |          |       | V    |

| V <sub>OL</sub>  | Voltage output, low <sup>(4)</sup>                                          | $I_{OL} = 2 \text{ mA}$                                                          |        |          | 0.5   | V    |

| V <sub>OH</sub>  | Voltage output high <sup>(4)</sup>                                          | $I_{OH} = -2 \text{ mA}$                                                         | 2.4    |          | VDDS  | V    |

| I <sub>PU</sub>  | Pullup current (tdi, tms, trst_n, ce_n, wr_n, rd_n, reset_n) <sup>(4)</sup> | V <sub>IN</sub> = 0 V, nominal 20 A                                              | 5      |          | 35    | μA   |

| I <sub>PD</sub>  | Pulldown current (all other inputs and bidirectionals) <sup>(4)</sup>       | V <sub>IN</sub> = VDDS, nominal 20 μA                                            | 5      |          | 35    | μA   |

| I <sub>IN</sub>  | Leakage current <sup>(4)</sup>                                              | V <sub>IN</sub> = 0V or VDDS, outputs in high-impedance state                    |        |          | 20    | μA   |

| I <sub>DDQ</sub> | Quiescent supply current, IDVDD or IVDDS <sup>(4)</sup>                     | $V_{IN} = 0$ for pads with pulldowns,<br>$V_{IN} = VDDS$ for inputs with pullups |        | 8        |       | mA   |

| C <sub>IN</sub>  | Capacitance for inputs <sup>(5)</sup>                                       |                                                                                  |        | 5        |       | pF   |

| C <sub>BI</sub>  | Capacitance for bidirectionals <sup>(5)</sup>                               |                                                                                  |        | 5        |       | pF   |

(1) Voltages are measured at low speed. Output voltages are measured with the indicated current load.

(2) Currents are measured at nominal voltages, high temperature.

(3) reset\_n and interrupt have no timing specifications because they are asynchronous signals. die\_id pins fa002\_out, fa002\_clk, and fa002\_scan are not specified and are for factory use only. fuse pin fuse\_out is not specified and is for factory use only. test pins zero, scanen, testmode0 and testmode1 are not specified and are for factory use only.

(4) Each part is tested at high temperature for the given specification. Lots are sample tested at  $-40^{\circ}$ C.

(5) Controlled by design and process and not directly tested.

#### SLWS212A-OCTOBER 2008-REVISED JANUARY 2009

# 3.8 DIGITAL CHIP AC TIMING CHARACTERISTICS<sup>(1)</sup>

$T_A = -40^{\circ}C$  to  $85^{\circ}C$  (unless otherwise noted)

|                    | PARAMETER                                                                                                                                                                                                                  | MIN | ΤΥΡ Μ | AX | UNIT |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|----|------|

| f <sub>CK</sub>    | Clock frequency (adcclk_a/b/c/d, rxclk) <sup>(2)</sup>                                                                                                                                                                     |     | 1     | 60 | MHz  |

| t <sub>CKL</sub>   | Clock low period (below V <sub>IL</sub> ) (adcclk_a/b/c/d, rxclk) <sup>(2)</sup>                                                                                                                                           | 2   |       |    | ns   |

| t <sub>CKH</sub>   | Clock high period (above V <sub>IH</sub> ) (adcclk_a/b/c/d, rxclk) <sup>(2)</sup>                                                                                                                                          | 2   |       |    | ns   |

| t <sub>RF</sub>    | Clock rise and fall times (V <sub>IL</sub> to V <sub>IH</sub> ) (adcclk_a/b/c/d, rxclk) <sup>(3)</sup>                                                                                                                     |     |       | 2  | ns   |

|                    | Input setup (rx_sync[a-d]) before rxclk rises <sup>(2)</sup>                                                                                                                                                               | 2   |       |    |      |

| t <sub>SU</sub>    | Input setup (rxin_a/b/c/d_[0-15]) before rxclk rises (ADC FIFO blocks bypassed) <sup>(2)</sup>                                                                                                                             | 2   |       |    | ns   |

|                    | Input setup (rxin_a/b/c/d_[0-15]) before adcclk_a/b/c/d rises (ADC FIFO blocks enabled) <sup>(2)</sup>                                                                                                                     | 2   |       |    |      |

|                    | Input hold ( <b>rx_sync[a-d</b> ]) after <b>rxclk</b> rises <sup>(2)</sup>                                                                                                                                                 | 1   |       |    |      |

| t <sub>HD</sub>    | Input hold (rxin_a/b/c/d_[0-15]) after rxclk rises (adc fifo blocks bypassed) <sup>(2)</sup>                                                                                                                               | 2.5 |       |    | ns   |

|                    | Input hold (rxin_ a/b/c/d_[0-15]) after adcclk_a/b/c/d rises (adc fifo blocks enabled) <sup>(2)</sup>                                                                                                                      | 1   |       |    |      |

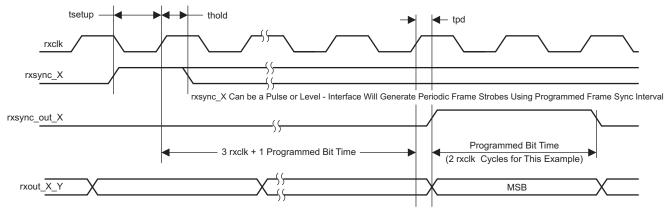

| t <sub>DLY</sub>   | Data output delay (rx_sync_out_[0-7], rxout_[0-7]_a/b/c/d, rxclk_out, rx_sync_out, dvga_[a-d]_[5-0]) after rxclk rises. <sup>(2)</sup>                                                                                     |     |       | 7  | ns   |

| t <sub>OHD</sub>   | Data output hold (rx_sync_out_[0-7], rxout_[0-7]_a/b/c/d, rxclk_out, rx_sync_out, dvga_[a-d]_[5-0]) after rxclk rises. <sup>(2)</sup>                                                                                      | 0.5 |       |    | ns   |

| f <sub>JCK</sub>   | JTAG clock frequency ( <b>tck</b> ) <sup>(2)</sup>                                                                                                                                                                         |     |       | 40 | MHz  |

| t <sub>JCKL</sub>  | JTAG clock low period (below V <sub>IL</sub> ) ( <b>tck</b> ) <sup>(2)</sup>                                                                                                                                               | 10  |       |    | ns   |

| t <sub>JCKH</sub>  | JTAG clock high period (above V <sub>IH</sub> ) ( <b>tck</b> ) <sup>(2)</sup>                                                                                                                                              | 10  |       |    | ns   |

| t <sub>JSU</sub>   | JTAG input ( <b>tdi</b> or <b>tms</b> ) setup before <b>tck</b> goes high <sup>(2)</sup>                                                                                                                                   | 2   |       |    | ns   |

| t <sub>JHD</sub>   | JTAG input ( <b>tdi</b> or <b>tms</b> ) hold time after <b>tck</b> goes high <sup>(2)</sup>                                                                                                                                | 10  |       |    | ns   |

| t <sub>JDLY</sub>  | JTAG output (tdo) delay from falling edge of tck. <sup>(2)</sup>                                                                                                                                                           |     |       | 10 | ns   |

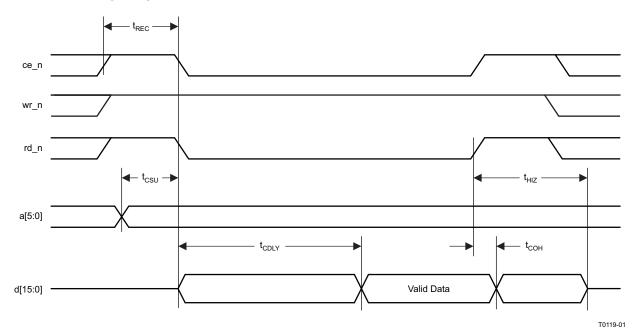

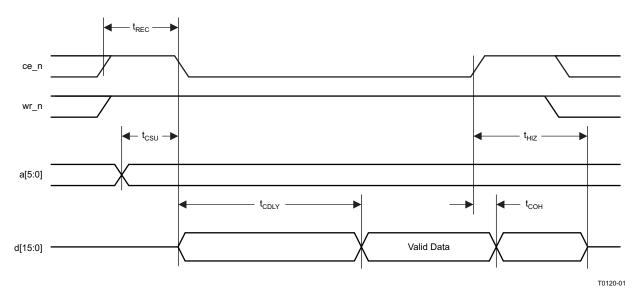

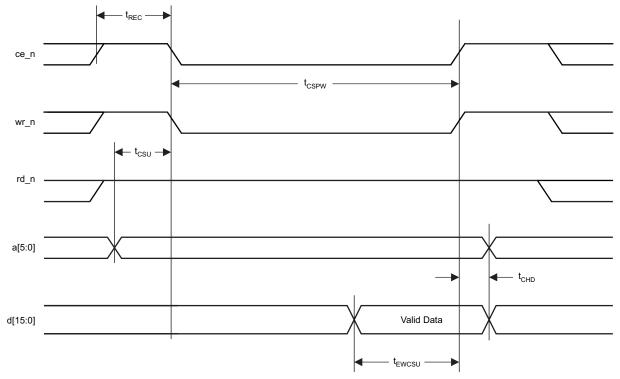

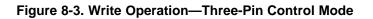

| t <sub>CSU</sub>   | Control setup during reads or writes<br>3 pin mode: <b>a[5:0]</b> valid before <b>rd_n, wr_n or ce_n</b> falling edge<br>2 pin mode: <b>a[5:0]</b> and <b>wr_n</b> valid before <b>ce_n</b> falling edge <sup>(2)</sup>    | 6   |       |    | ns   |

| t <sub>EWCSU</sub> | Control setup during writes<br>3 pin mode: <b>d[15:0]</b> valid before <b>wr_n</b> and <b>ce_n</b> rising edge<br>2 pin mode: <b>d[15:0]</b> valid before <b>ce_n</b> rising edge <sup>(2)</sup>                           | 10  |       |    | ns   |

| t <sub>CHD</sub>   | Control hold during writes.<br>3 pin mode: <b>a[5:0]</b> and <b>d[15:0]</b> valid after <b>wr_n</b> and <b>ce_n</b> rise<br>2 pin mode: <b>a[5:0], d[15:0]</b> and <b>wr_n</b> valid after <b>ce_n</b> rise <sup>(2)</sup> | 6   |       |    | ns   |

| t <sub>CSPW</sub>  | Control strobe (ce_n and wr_n low) pulse duration during write. <sup>(2)</sup>                                                                                                                                             | 25  |       |    | ns   |

| t <sub>CDLY</sub>  | Control output delay ce_n and rd_n low and a[5:0] stable to d[15:0] during read. <sup>(2)</sup>                                                                                                                            |     |       | 25 | ns   |

| t <sub>REC</sub>   | Control recovery time between reads or writes. (2)                                                                                                                                                                         |     |       | 6  | ns   |

| t <sub>HIZ</sub>   | Control end of read to Hi-Z. rd_n and ce_n rise to d[15:0] 3-state <sup>(4)</sup>                                                                                                                                          |     |       | 10 | ns   |

| t <sub>COH</sub>   | Control read d[15:0] output hold time                                                                                                                                                                                      | 1   |       |    | ns   |

Timing is measured from the respective clock at VDDS/2 to input or output at VDDS/2. Output loading is a 50-Ω transmission line whose delay is calibrated out.

(2) Each part is tested at 90°C case temperature for the given specification. Lots are sample tested at -40°C.

(3) Recommended practice

(4) Controlled by design and process and not directly tested.

SLWS212A-OCTOBER 2008-REVISED JANUARY 2009

## 4 AFE8405 PINS

## 4.1 Analog Section Signals

| Signal Name   | Ball | Туре   | Description                                                           |

|---------------|------|--------|-----------------------------------------------------------------------|

| inpa          | F3   | Input  | ADCA analog positive input                                            |

| inma          | F4   | Input  | ADCA analog negative input                                            |

| NC            | V4   | _      |                                                                       |

| NC            | V3   | —      |                                                                       |

| clkpa         | H1   | Input  | ADCA clock positive input                                             |

| clkma         | J1   | Input  | ADCA clock negative input                                             |

| NC            | R1   | —      |                                                                       |

| NC            | T1   | —      |                                                                       |

| refpa         | L3   | Input  | ADCA positive reference input. connect 0.1 µF to AVSS.                |

| refma         | K3   | Input  | ADCA negative reference input; connect 0.1 µF to AVSS.                |

| NC            | P3   | _      |                                                                       |

| NC            | N3   | —      |                                                                       |

| cma           | H3   | Output | ADCA common-mode output reference                                     |

| NC            | Т3   | _      |                                                                       |

| iref          | M3   | Input  | Current set; connect 56 k $\Omega$ to AVSS                            |

| clkouta       | n/a  | Output | ADCA output clock; internally connected to adcclka                    |

| da(13:0)      | n/a  | Output | ADCA output data; internally connected to rxin_a_15:2                 |

| fuse_sel      | H5   | Input  | Connect to AVSS; factory use only                                     |

| pwdn          | L9   | Input  | Connect to AVDD, ADCA output enable; AVDD = enabled, AVSS = disabled  |

| GND           | N9   | Input  |                                                                       |

| ovra          | G6   | Output | ADCA over range indicator bit                                         |

| NC            | N8   | _      |                                                                       |

| pin_configure | T5   | Input  | Connect to AVDD, factory use only                                     |

| dll_disable   | N10  | Input  | Connect to AVDD, factory use only                                     |

| AVDD          | M9   | Input  |                                                                       |

| ext_ref       | M10  | Input  | Connect to AVSS, AVDD = external reference, AVSS = internal reference |

# AFE8405 14-BIT, 85-MSPS, SINGLE-ADC, 8-CHANNEL WIDEBAND RECEIVER SLWS212A-OCTOBER 2008-REVISED JANUARY 2009

www.ti.com

# 4.2 Digital Receive Section Signals

| Signal Name | Ball | Туре         | Description                                               |  |

|-------------|------|--------------|-----------------------------------------------------------|--|

| rxclk       | R22  | Input        | Receive digital section clock input                       |  |

|             |      | •            |                                                           |  |

| adcclk_a    | n/a  | Input        | rxin_a_x input clock; connected to ADCA output clock      |  |

| adcclk_b    | n/a  | Input        | Not used, not connected internally                        |  |

| adcclk_c    | AA11 | Input        | rxin_c_x input clock                                      |  |

| adcclk_d    | AB11 | Input        | rxin_d_x input clock                                      |  |

| rxin_c_ovr  | AB6  | Input        | ADC overflow/overrange bit for rxin_c                     |  |

| rxin_d_ovr  | V12  | Input        | ADC overflow/overrange bit for rxin_d                     |  |

| dvga_a_5    | D7   | Output       | Digital VGA control output for ADC0 MSB                   |  |

| dvga_a_4    | D8   | Output       | Digital VGA control output for ADC0                       |  |

| dvga_a_3    | C7   | Output       | Digital VGA control output for ADC0                       |  |

| dvga_a_2    | B7   | Output       | Digital VGA control output for ADC0                       |  |

| dvga_a_1    | A7   | Output       | Digital VGA control output for ADC0                       |  |

| dvga_a_0    | C8   | Output       | Digital VGA control output for ADC0 LSB                   |  |

| dvga_b_5    | B8   | Output       | Not used                                                  |  |

| dvga_b_4    | A8   | Output       | Not used                                                  |  |

| dvga_b_3    | D9   | Output       | Not used                                                  |  |

| dvga_b_2    | D10  | Output       | Not used                                                  |  |

| dvga_b_1    | C9   | Output       | Not used                                                  |  |

| dvga_b_0    | B9   | Output       | Not used                                                  |  |

| dvga_c_5    | AA15 | Output       | Digital VGA control output for rxin_c MSB, test bus bit 1 |  |

| dvga_c_4    | AB15 | Output       | Digital VGA control output for rxin_c, test bus bit 0     |  |

| dvga_c_3    | V16  | Output       | Digital VGA control output for rxin_c, test bus bit 19    |  |

| dvga_c_2    | W16  | Output       | Digital VGA control output for rxin_c, test bus bit 18    |  |

| dvga_c_1    | Y16  | Output       | Digital VGA control output for rxin_c, test bus CLK       |  |

| dvga_c_0    | AA16 | Output       | Digital VGA control output for rxin_c LSB, test bus SYNC  |  |

| dvga_d_5    | AB16 | Output       | Digital VGA control output for rxin_d MSB, test bus AFLAG |  |

| dvga_d_4    | V17  | Output       | Digital VGA control output for rxin_d                     |  |

| dvga_d_3    | W17  | Output       | Digital VGA control output for rxin_d                     |  |

| dvga_d_2    | AA17 | Output       | Digital VGA control output for rxin_d                     |  |

| dvga_d_1    | AB17 | Output       | Digital VGA control output for rxin_d                     |  |

| dvga_d_0    | V18  | Output       | Digital VGA control Output for rxin_d LSB                 |  |

| rxin_c_15   | Y7   | Input/output | Receive input data bus c bit 15 (MSB), test bus bit 17    |  |

| rxin_c_14   | AA7  | Input/output | Receive input data bus c bit 14, test bus bit 16          |  |

| rxin_c_13   | AB7  | Input/output | Receive input data bus c bit 13, test bus bit 15          |  |

| rxin_c_12   | Y8   | Input/output | Receive input data bus c bit 12, test bus bit 14          |  |

| rxin_c_11   | V10  | Input/output | Receive input data bus c bit 11, test bus bit 13          |  |

| rxin_c_10   | AA8  | Input/output | Receive input data bus c bit 10, test bus bit 12          |  |

| rxin_c_9    | AB8  | Input/output | Receive input data bus c bit 9, test bus bit 11           |  |

| rxin_c_8    | W9   | Input/output | Receive input data bus c bit 8, test bus bit 10           |  |

| rxin_c_7    | Y9   | Input/output | Receive input data bus c bit 7, test bus bit 9            |  |

| rxin_c_6    | AA9  | Input/output | Receive input data bus c bit 6, test bus bit 8            |  |

| rxin_c_5    | AB9  | Input/output | Receive input data bus c bit 5, test bus bit 7            |  |

| rxin_c_4    | W10  | Input/output | Receive input data bus c bit 4, test bus bit 6            |  |

| rxin_c_3    | Y10  | Input/output | Receive input data bus c bit 3, test bus bit 5            |  |

# AFE8405 14-BIT, 85-MSPS, SINGLE-ADC, 8-CHANNEL WIDEBAND RECEIVER SLWS212A-OCTOBER 2008-REVISED JANUARY 2009

| Signal Name   | Ball | Туре         | Description                                                                                                   |  |

|---------------|------|--------------|---------------------------------------------------------------------------------------------------------------|--|

| rxin_c_2      | AA10 | Input/output | Receive input data bus c bit 2, test bus bit 4                                                                |  |

| rxin_c_1      | AB10 | Input/output | Receive input data bus c bit 1, test bus bit 3                                                                |  |

| rxin_c_0      | W11  | Input/output | Receive input data bus c bit 0 (LSB), test bus bit 2                                                          |  |

| rxin_d_15     | W12  | Input/output | Receive input data bus d bit 15 (MSB), test bus bit 35                                                        |  |

| rxin_d_14     | Y12  | Input/output | Receive input data bus d bit 14, test bus bit 34                                                              |  |

| rxin_d_13     | AA12 | Input/output | Receive input data bus d bit 13, test bus bit 33                                                              |  |

| rxin_d_12     | AB12 | Input/output | Receive input data bus d bit 12, test bus bit 32                                                              |  |

| rxin_d_11     | V13  | Input/output | Receive input data bus d bit 11, test bus bit 31                                                              |  |

| rxin_d_10     | W13  | Input/output | Receive input data bus d bit 10, test bus bit 30                                                              |  |

| rxin_d_9      | Y13  | Input/output | Receive input data bus d bit 9, test bus bit 29                                                               |  |

| rxin_d_8      | AA13 | Input/output | Receive input data bus d bit 8, test bus bit 28                                                               |  |

| rxin_d_7      | AB13 | Input/output | Receive input data bus d bit 7, test bus bit 27                                                               |  |

| rxin_d_6      | V14  | Input/output | Receive input data bus d bit 6, test bus bit 26                                                               |  |

| rxin_d_5      | W14  | Input/output | Receive input data bus d bit 5, test bus bit 25                                                               |  |

| rxin_d_4      | AA14 | Input/output | Receive input data bus d bit 4, test bus bit 24                                                               |  |

| rxin_d_3      | AB14 | Input/output | Receive input data bus d bit 3, test bus bit 23                                                               |  |

| rxin_d_2      | V15  | Input/output | Receive input data bus d bit 2, test bus bit 22                                                               |  |

| rxin_d_1      | W15  | Input/output | Receive input data bus d bit 1, test bus bit 21                                                               |  |

| rxin_d_0      | Y15  | Input/output | Receive input data bus d bit 0 (LSB), test bus bit 20                                                         |  |

| rx_synca      | P21  | Input        | Receive sync input                                                                                            |  |

| rx_syncb      | P22  | Input        | Receive sync input                                                                                            |  |

| rx_syncc      | N20  | Input        | Receive sync input                                                                                            |  |

| rx_syncd      | N21  | Input        | Receive sync input                                                                                            |  |

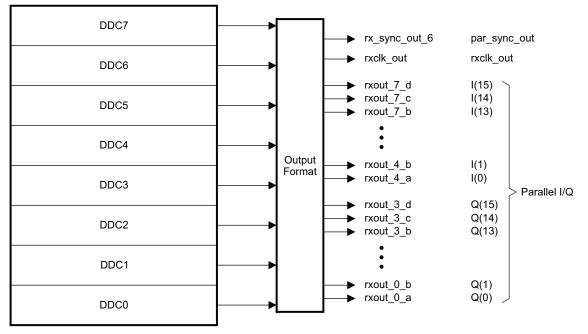

| rx_sync_out   | E22  | Output       | Receive general purpose output sync                                                                           |  |

| rxclk_out     | E21  | Output       | Receive clock output                                                                                          |  |

| rx_sync_out_7 | A20  | Output       | Receive serial interface frame strobe for rxout_7_x                                                           |  |

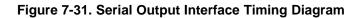

| rx_sync_out_6 | C19  | Output       | Receive serial interface frame strobe for rxout_6_x, frame strobe (rx_sync_out signal) for parallel interface |  |

| rx_sync_out_5 | C17  | Output       | Receive serial interface frame strobe for rxout_5_x                                                           |  |

| rx_sync_out_4 | C16  | Output       | Receive serial interface frame strobe for rxout_4_x                                                           |  |

| rx_sync_out_3 | D15  | Output       | Receive serial interface frame strobe for rxout_3_x                                                           |  |

| rx_sync_out_2 | B13  | Output       | Receive serial interface frame strobe for rxout_2_x                                                           |  |

| rx_sync_out_1 | C12  | Output       | Receive serial interface frame strobe for rxout_1_x                                                           |  |

| rx_sync_out_0 | A10  | Output       | Receive serial interface frame strobe for rxout_0_x                                                           |  |

| rxout_7_a     | D20  | Output       | DDC 7 serial out data. CDMA A: I data UMTS: Imsb DDC parallel interface I(12)                                 |  |

| rxout_7_b     | C21  | Output       | DDC 7 serial out data. CDMA B: I data UMTS: Imsb – 1 DDC parallel interface I(13)                             |  |

| rxout_7_c     | B20  | Output       | DDC 7 serial out data. CDMA A: Q data UMTS: Qmsb DDC parallel interface I(14)                                 |  |

| rxout_7_d     | C20  | Output       | DDC 7 serial out data. CDMA B: Q data UMTS: Qmsb – 1 DDC parallel interface I(15)                             |  |

| rxout_6_a     | A19  | Output       | DDC 6 serial out data. CDMA A: I data UMTS: Imsb DDC parallel interface I(8)                                  |  |

| rxout_6_b     | B19  | Output       | DDC 6 serial out data. CDMA B: I data UMTS: Imsb – 1 DDC parallel interface I(9)                              |  |

| rxout_6_c     | A18  | Output       | DDC 6 serial out data. CDMA A: Q data UMTS: Qmsb DDC parallel interface I(10)                                 |  |

| rxout_6_d     | B18  | Output       | DDC 6 serial out data. CDMA B: Q data UMTS: Qmsb – 1 DDC parallel interface I(11)                             |  |

| rxout_5_a     | D18  | Output       | DDC 5 serial out data. CDMA A: I data UMTS: Imsbparallel interface I(4)                                       |  |

| rxout_5_b     | B17  | Output       | DDC 5 serial out data. CDMA B: I data UMTS: Imsb – 1 parallel interface I(5)                                  |  |

| rxout_5_c     | D17  | Output       | DDC 5 serial out data. CDMA A: Q data UMTS: Qmsb parallel interface I(6)                                      |  |

| rxout_5_d     | A17  | Output       | DDC 5 serial out data. CDMA B: Q data UMTS: Qmsb – 1parallel interface I(7)                                   |  |

# AFE8405 14-BIT, 85-MSPS, SINGLE-ADC, 8-CHANNEL WIDEBAND RECEIVER SLWS212A-OCTOBER 2008-REVISED JANUARY 2009

| Signal Name | Ball | Туре   | Description                                                                   |  |

|-------------|------|--------|-------------------------------------------------------------------------------|--|

| rxout_4_a   | A16  | Output | DDC 4 serial out data. CDMA A: I data UMTS: Imsb parallel interface I(0)      |  |

| rxout_4_b   | B16  | Output | DDC 4 serial out data. CDMA B: I data UMTS: Imsb – 1 parallel interface I(1)  |  |

| rxout_4_c   | D16  | Output | DDC 4 serial out data. CDMA A: Q data UMTS: Qmsb parallel interface I(2)      |  |

| rxout_4_d   | A15  | Output | DDC 4 serial out data. CDMA B: Q data UMTS: Qmsb – 1 parallel interface I(3)  |  |

| rxout_3_a   | B15  | Output | DDC 3 serial out data. CDMA A: I data UMTS: Imsb parallel interface Q(12)     |  |

| rxout_3_b   | C15  | Output | DDC 3 serial out data. CDMA B: I data UMTS: Imsb – 1 parallel interface Q(13) |  |

| rxout_3_c   | A14  | Output | DDC 3 serial out data. CDMA A: Q data UMTS: Qmsb parallel interface Q(14)     |  |

| rxout_3_d   | B14  | Output | DDC 3 serial out data. CDMA B: Q data UMTS: Qmsb – 1 parallel interface Q(15) |  |

| rxout_2_a   | D14  | Output | DDC 2 serial out data. CDMA A: I data UMTS: Imsb parallel interface Q(8)      |  |

| rxout_2_b   | A13  | Output | DDC 2 serial out data. CDMA B: I data UMTS: Imsb – 1 parallel interface Q(9)  |  |

| rxout_2_c   | C13  | Output | DDC 2 serial out data. CDMA A: Q data UMTS: Qmsb parallel interface Q(10)     |  |

| rxout_2_d   | D13  | Output | DDC 2 serial out data. CDMA B: Q data UMTS: Qmsb – 1 parallel interface Q(11) |  |

| rxout_1_a   | A12  | Output | DDC 1 serial out data. CDMA A: I data UMTS: Imsb parallel interface Q(4)      |  |

| rxout_1_b   | B12  | Output | DDC 1 serial out data. CDMA B: I data UMTS: Imsb – 1 parallel interface Q(5)  |  |

| rxout_1_c   | D12  | Output | DDC 1 serial out data. CDMA A: Q data UMTS: Qmsb parallel interface Q(6)      |  |

| rxout_1_d   | A11  | Output | DDC 1 serial out data. CDMA B: Q data UMTS: Qmsb – 1 parallel interface Q(7)  |  |

| rxout_0_a   | B11  | Output | DDC 0 serial out data. CDMA A: I data UMTS: Imsb parallel interface Q(0)      |  |

| rxout_0_b   | C11  | Output | DDC 0 serial out data. CDMA B: I data UMTS: Imsb – 1 parallel interface Q(1)  |  |

| rxout_0_c   | B10  | Output | DDC 0 serial out data. CDMA A: Q data UMTS: Qmsb parallel interface Q(2)      |  |

| rxout_0_d   | A9   | Output | DDC 0 serial out data. CDMA B: Q data UMTS: Qmsb – 1 parallel interface Q(3)  |  |

# AFE8405 14-BIT, 85-MSPS, SINGLE-ADC, 8-CHANNEL WIDEBAND RECEIVER SLWS212A-OCTOBER 2008-REVISED JANUARY 2009

## 4.3 Microprocessor Signals

| Signal Name | Ball | Туре         | Description                                     |  |

|-------------|------|--------------|-------------------------------------------------|--|

| d0          | Y22  | Input/output | MPU register interface data bus bit 0 (LSB)     |  |

| d1          | Y21  | Input/output | MPU register interface data bus                 |  |

| d2          | AB20 | Input/output | MPU register interface data bus                 |  |

| d3          | AA20 | Input/output | MPU register interface data bus                 |  |

| d4          | Y20  | Input/output | MPU register interface data bus                 |  |

| d5          | W20  | Input/output | MPU register interface data bus                 |  |

| d6          | V20  | Input/output | MPU register interface data bus                 |  |

| d7          | AB19 | Input/output | MPU register interface data bus                 |  |

| d8          | AA19 | Input/output | MPU register interface data bus                 |  |

| d9          | Y19  | Input/output | MPU register interface data bus                 |  |

| d10         | W19  | Input/output | MPU register interface data bus                 |  |

| d11         | V19  | Input/output | MPU register interface data bus                 |  |

| d12         | AB18 | Input/output | MPU register interface data bus                 |  |

| d13         | AA18 | Input/output | MPU register interface data bus                 |  |

| d14         | Y18  | Input/output | MPU register interface data bus                 |  |

| d15         | W18  | Input/output | MPU register interface data bus bit 15 (MSB)    |  |

| a0          | T20  | Input        | MPU register interface address bus bit 0 (LSB)  |  |

| a1          | U22  | Input        | MPU register interface address bus              |  |

| a2          | U21  | Input        | MPU register interface address bus              |  |

| a3          | W22  | Input        | MPU register interface address bus              |  |

| a4          | V21  | Input        | MPU register interface address bus              |  |

| а5          | W21  | Input        | MPU register interface address bus bit 5 (MSB)  |  |

| rd_n        | T22  | Input        | MPU register interface read – active low        |  |

| wr_n        | R20  | Input        | MPU register interface write – active low       |  |

| ce_n        | T21  | Input        | MPU register interface chip enable – active low |  |

| reset_n     | R21  | Input        | Chip reset – active low                         |  |

| interrupt   | M21  | Output       | Chip interrupt                                  |  |

SLWS212A-OCTOBER 2008-REVISED JANUARY 2009

# 4.4 JTAG Signals

| Signal Name | Ball | Туре   | Description                                                                                                  |  |

|-------------|------|--------|--------------------------------------------------------------------------------------------------------------|--|

| tdi         | K22  | Input  | JTAG test data in                                                                                            |  |

| tms         | K21  | Input  | JTAG test mode select                                                                                        |  |

| trst_n      | J22  | Input  | JTAG test reset                                                                                              |  |

|             |      |        | Note: the trst_n pin should be asserted low after power up to insure the JTAG logic is properly initialized. |  |

| tck         | L20  | Input  | JTAG test clock                                                                                              |  |

| tdo         | L21  | Output | JTAG test data out                                                                                           |  |

# 4.5 Factory Test and No-Connect Signals

| Signal Name | Ball | Туре   | Description                       |  |

|-------------|------|--------|-----------------------------------|--|

| testmode0   | G21  | Input  | Do not connect; internal pulldown |  |

| testmode1   | G22  | Input  | Do not connect; internal pulldown |  |

| scanen      | H21  | Input  | Do not connect; internal pulldown |  |

| fa002_scan  | J20  | Input  | Do not connect; internal pulldown |  |

| fa002_clk   | H22  | Input  | Do not connect; internal pulldown |  |

| fa002_out   | J21  | Output | Do not connect                    |  |

| zero        | H20  | Input  | Do not connect; internal pulldown |  |

| fuse_out    | F20  | Output | Do not connect                    |  |

| fuse_ena    | D21  | Input  | Do not connect; internal pulldown |  |

| fuse_bias   | F21  | Input  | Do not connect; internal pulldown |  |

# 4.6 Power and Ground Signals

| Signal Name | Ball                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Description                                   |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--|

| AVDD        | H4, J3, L1, L2, M1, M2, M9, N1, N2, R3, T4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Analog power (3.3 V)                          |  |

| DRVDD       | H6, H7, J8, K8, L8, P8, R8, T6, T7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Analog I/O power (3.3 V)                      |  |

| AVSS        | A1, A2, A3, A4, A5, B1, B2, B3, B4, B5, C1, C2,<br>C3, C4, C5, D1, D2, D3, D4, D5, E1, E2, E3, E4,<br>E5, F1, F2, F5, F6, F7, F8, F9, G1, G2, G3, G4,<br>G5, G7, G8, G9, H2, J2, J4, J5, J6, K1, K2, K4, K5,<br>K6, L4, L5, L6, L7, M4, M5, M6, M7, N4, N5, N6,<br>N7, N9, P1, P2, P4, P5, P6, R2, R4, R5, R6, T2,<br>U1, U2, U3, U4, U5, U6, U7, U8, U9, V1, V2, V5,<br>V6, V7, V8, W1, W2, W3, W4, W5, Y1, Y2, Y3, Y4,<br>AA1, AA2, AA3, AA4, AB1, AB2, AB3, AB4                                                                                                                                                                                                |                                               |  |

| DRVSS       | H8, H9, J7, J9, K7, K9, M8, P7, P9, R7, R9, T8, T9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Analog I/O ground                             |  |

| VDDS        | B6, B21, D6, D11, D19, D22, E10, E11, E12, E13,<br>E14, E15, E16, E17, E18, E19, K20, M20, P20,<br>U11, U12, U13, U14, U15, U16, U17, U18, U19,<br>V11, W7, AA6, AA21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Digital I/O power (3.3 V), also called Vpad   |  |

| DVDD        | F22, G10, G19, H10, H19, J10, J19, K10, K19, L10, L19, M19, N19, P10, P19, R10, R19, V22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Digital core power (1.5 V), also called Vcore |  |

| DVSS        | A6, A21, A22, B22, C6, C10, C14, C18, C22, E6,<br>E7, E8, E9, E20, F10, F11, F12, F13, F14, F15,<br>F16, F17, F18, F19, G11, G12, G13, G14, G15,<br>G16, G17, G18, G20, H11, H12, H13, H14, H15,<br>H16, H17, H18, J11, J12, J13, J14, J15, J16, J17,<br>J18, K11, K12, K13, K14, K15, K16, K17, K18, L11,<br>L12, L13, L14, L15, L16, L17, L18, M11, M12, M13,<br>M14, M15, M16, M17, M18, N11, N12, N13, N14,<br>N15, N16, N17, N18, N22, P11, P12, P13, P14,<br>P15, P16, P17, P18, R11, R12, R13, R14, R15,<br>R16, R17, R18, T10, T11, T12, T13, T14, T15, T16,<br>T17, T18, T19, U10, U20, V9, W6, W8, Y5, Y6,<br>Y11, Y14, Y17, AA5, AA22, AB5, AB21, AB22 | Digital ground                                |  |

SLWS212A-OCTOBER 2008-REVISED JANUARY 2009

#### IEXAS INSTRUMENTS

www.ti.com

#### 4.7 Digital Supply Monitoring

| Signal Name | Ball | Description                                                                                        |  |

|-------------|------|----------------------------------------------------------------------------------------------------|--|

| dvddmon     | L22  | It is recommended that this pin be brought to a probe point for monitoring and debugging purposes. |  |

| dvssmon     | M22  | It is recommended that this pin be brought to a probe point for monitoring and debugging purposes. |  |

# 4.8 JTAG

The JTAG standard for boundary scan testing is implemented for board testing purposes. Internal scan test is not supported. Five device pins are dedicated for JTAG support: tdi, tdo, tms, tck, and trst\_n. The JTAG bsdl configuration file is available at www.ti.com.

#### NOTE

The trst\_n pin should be asserted after power up to insure the JTAG logic is properly initialized.

# 4.9 AFE8405 and AFE8406 PCB Design Compatibility

The AFE8406 is 14-bit, 85-MSPS, dual-ADC, 8-channel wideband receiver. AFE8405 has a pin- and software-compatible upgrade to AFE8406 for diversity applications. Attention must be paid to the configuration of pins L9, M9, and N9 for PCB design to support AFE8405 and AFE8406 compatibility.

The ADC power-management system is configured by pins L9, M9, and N9. AFE8405/8406 signal names of pin L9, M9 and N9 are shown in the following table.

| BALL NO. | AFE8405 SIGNAL NAME | AFE8406 SIGNAL NAME | COMMENT                                                   |

|----------|---------------------|---------------------|-----------------------------------------------------------|

| L9       | pwdn                | oea                 | AFE8405 ADCA output enable: AVDD = enable; AVSS = disable |

| M9       | AVDD                | pwdn                |                                                           |

| N9       | GND                 | oeb                 |                                                           |

The AFE8406 has two ADCs (ADCA and ADCB). Their ADC output and power on/off states are configured by pins L9, M9, and N9 as shown in following table.

|    |    |    | AFE8406 |       |       |       |

|----|----|----|---------|-------|-------|-------|

| M9 | L9 | N9 | Out A   | Out B | ADC A | ADC B |

| 0  | 0  | 0  | Off     | Off   | On    | On    |

| 0  | 0  | 1  | Off     | On    | On    | On    |

| 0  | 1  | 0  | On      | Off   | On    | On    |

| 0  | 1  | 1  | On      | On    | On    | On    |

| 1  | 0  | 0  | Off     | Off   | Off   | Off   |

| 1  | 0  | 1  | Off     | On    | Off   | On    |

| 1  | 1  | 0  | On      | Off   | On    | Off   |

| 1  | 1  | 1  | On      | On    | On    | On    |

The AFE8405 has one ADC (ADCA). Its output and power on/off states are configured by pin L9. When the ADC is enabled, the configuration corresponds to the AFE8406 configuration with (M9, L9, N9) = (1, 1, 0), which is ADCA on and ADCB off.

The AFE8405 L9, M9, and N9 configuration is recommended for new designs using AFE8405. For current AFE8406 users who would like to use AFE8405 on an AFE8406 PCB for single-ADC applications, if L9, M9, and N9 are in a state where ADCB is is not powered down, device functionality and performance is not affected, but this state results in higher power dissipation.

# **5** Typical Characteristics

8192

**Digital Output Codes**

Figure 5-2.

10240

12288

14336

16384

G002

2048

4096

6144

-2.5 -3.0

0

SLWS212A-OCTOBER 2008-REVISED JANUARY 2009

Figure 5-5.

Figure 5-6.

Submit Documentation Feedback

TEXAS INSTRUMENTS

# AFE8405 14-BIT, 85-MSPS, SINGLE-ADC, 8-CHANNEL WIDEBAND RECEIVER

SLWS212A-OCTOBER 2008-REVISED JANUARY 2009

SLWS212A-OCTOBER 2008-REVISED JANUARY 2009

Instruments

Texas

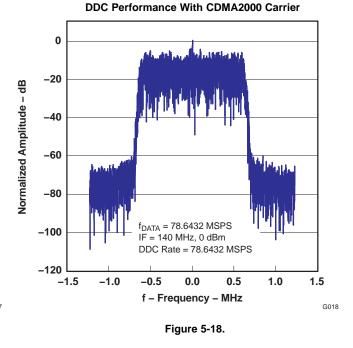

DDC Performance With CDMA2000 Carrier

Figure 5-17.

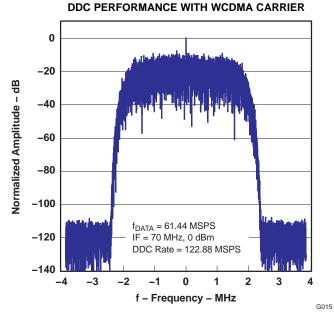

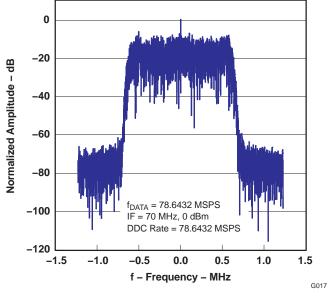

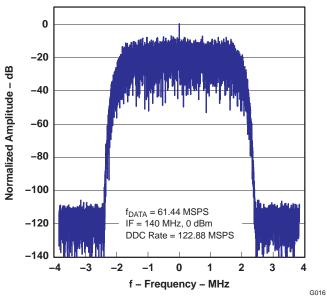

DDC PERFORMANCE WITH WCDMA CARRIER

TEXAS INSTRUMENTS

www.ti.com

SLWS212A-OCTOBER 2008-REVISED JANUARY 2009

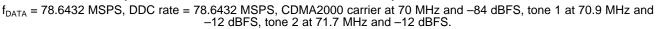

# DDC Performance (WCDMA Carrier With Tone Blocker)

f<sub>DATA</sub> = 61.44 MSPS, DDC rate = 122.88 MSPS, WCDMA carrier at 70 MHz and -71 dBFS, tone blocker at 73 MHz and -1 dBFS.

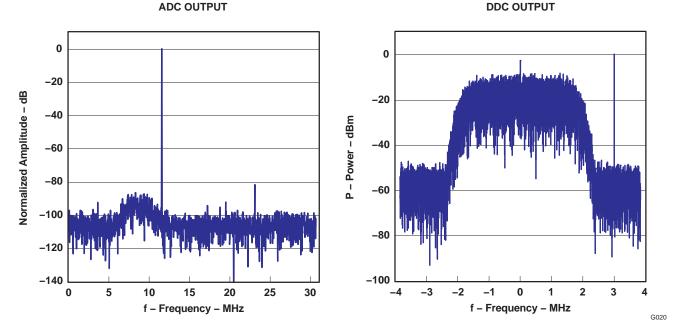

## DDC Performance (CDMA Carrier With Two-Tone Blocker)

Figure 5-21.

Figure 5-22.

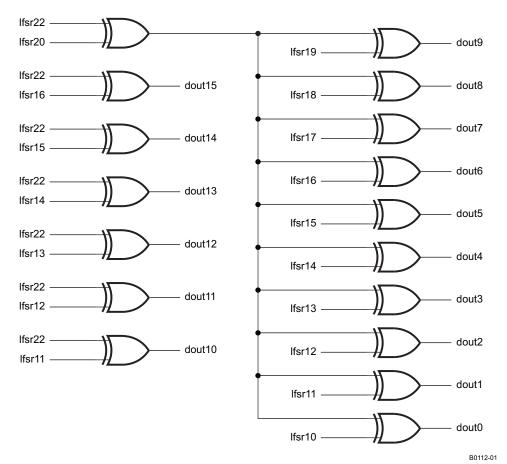

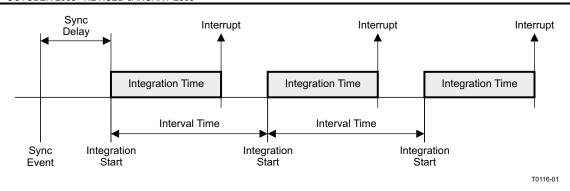

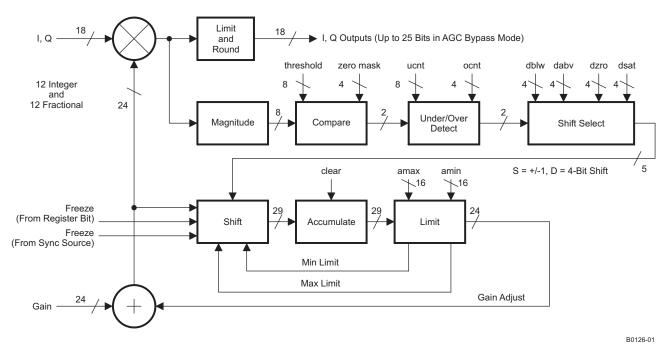

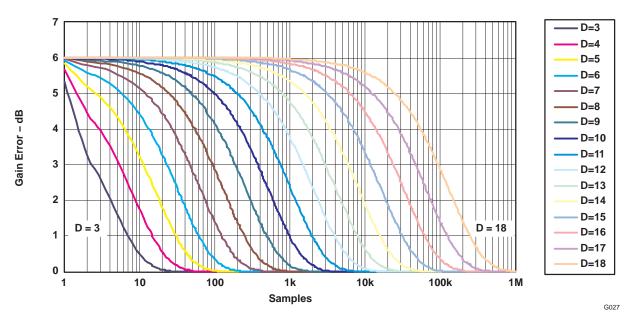

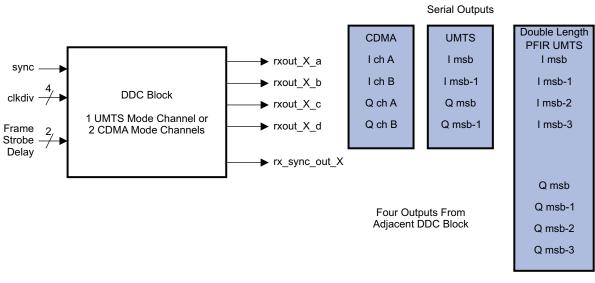

# 6 ANALOG-TO-DIGITAL CONVERTERS