AIC-010

AIC-010-10 AIC-010-5

- Controls ST506/412, ESDI, ST412HP, SA1000 and SMD, Interface Hard Disk Drives

- \* Controls QIC-36 Interface Tape Drives

- \* User Modifiable RAM Based Control Store

- \* User Programmable Internal 32-bit ECC Polynomial

- \* 5 Mbits/sec and 10 Mbits/sec Transfer Rate Versions

- \* Soft or Hard Sector Drives

- \*- Multiple Sector Transfer

- \* Sector Level Defect Handling

- \* Non-interleaved Operation

- \* User Programmable Sector Length upto a Full Track

- \* High Speed Search Capability

- \* Single +5V Power

#### DESCRIPTION

The Adaptec AIC-OlO Programmable Mass Storage Controller is a LSI component that provides the major portion of hardware necessary to build a Winchester disk controller. The chip is capable of supporting most drive interfaces including, but not limited to, ST506/412, ESDI, ST412-HP, SA1000, and SMD. In addition, the chip can also be setup to control QIC-36 interface tape drives, and other such peripherals.

The Adaptec AIC-OlO is a fully user programmable RAM based sequencer which can be loaded, in order to change its control store. The sequencer RAM can be easily modified to achieve full compatibility with a variety of drive interfaces. In addition, this allows the user to define specialized track formats. The chip also has a user programmable 32-bit ECC polynomial, thus offerring full flexibility in implenting error detection and correction.

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

|-------------------------------------------------------|

|                                                       |

|                                                       |

The AIC-OlO forms the nucleus of a three chip set comprised of the AIC-OlO, AIC-250 (or AIC-270) and the AIC-300. These chips along with a data seperator, driver/receivers, and a microprocessor chip provide all that is required to implement a full-featured, high performance disk controller. Typically, most implementations are able to read or write a full track in one revolution, run commonly available drives at their performance limits and, in fact, tend to put the performance bottleneck within the limitations of the system, as opposed to those of the controller.

The AIC-OlO performs basic read/write functions for a mass storage device. For this purpose, the chip provides the necessary serialization/deserialization, formatting, ECC generation and correction functions. In addition, the AIC-OlO also has search and verify capabilities.

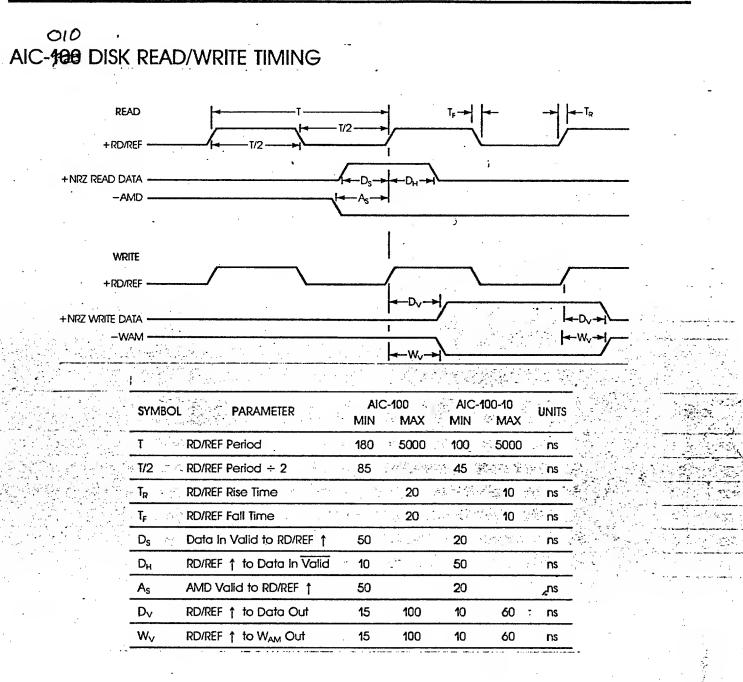

The AIC-250 provides the write precompensation, write address mark/address mark detect and NRZ to MFM conversion functions required in ST506/412 type of drive interface applications. The AIC-270 has the ability to convert NRZ format data to/from 2/7 RLL code. This method of encoding can increase the effective capacity on a drive by upto 50%.

The AIC-300 provides a dual-ported buffer controller function in systems whose available bus bandwidth requires the use of a buffer between the host bus and the controller.

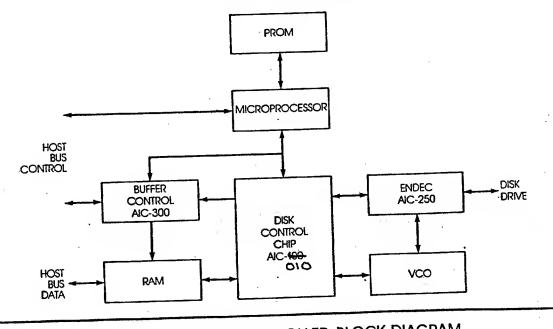

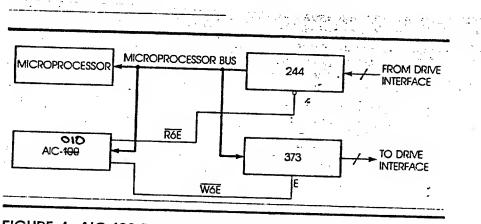

Figure 1 shows a simplified block diagram of an ST412/506 controller using the three chip set.

The AIC-OlO is designed to work with either a local processor or the host processor. This choice is up to the designer and is a function of the host system's available bus bandwidth and board space design considerations. Accordingly the microcode for the control of the AIC-OlO will be present in the system ram or a local (ep)rom.

FIGURE 1. SIMPLIFIED WINCHESTER DISK CONTROLLER BLOCK DIAGRAM

### AIC-OLO PIN DESCRIPTION

•

| SYMBOL       | PIN | TYPE   | NAME AND FUNCTION                                                                                                                                                                                                                                                                     |

|--------------|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ALE          | 1   | IN     | ADDRESS LATCH ENABLE: Signal<br>used to latch the address from<br>the multiplexed address/data<br>bus.                                                                                                                                                                                |

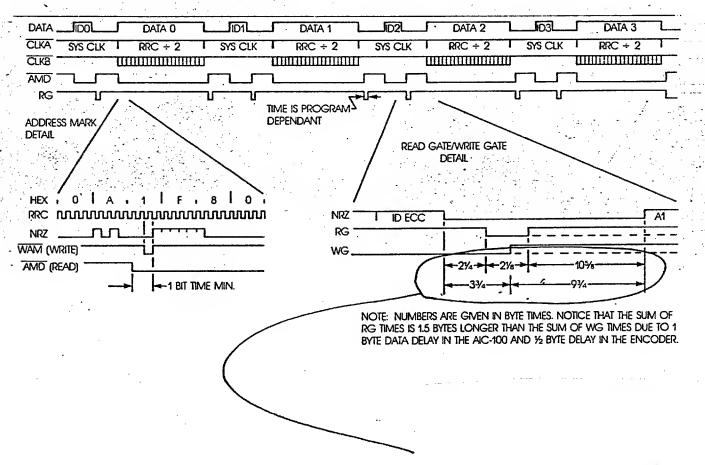

| CLKA         | . 2 | OUT    | CLOCK A: During a read or<br>write operation, the output of<br>this signal is derived from<br>the input RD/REF CLK.<br>Otherwise, it is derived from<br>the input SYSCLK. The<br>relationship between the input<br>clock and CLKA is controlled<br>by the contents of Register<br>7F. |

| CLKB         | 3   | OUT    | CLOCK B: A pulse which<br>overlaps the negative edge of<br>Clock A, and occurs whenever a<br>byte is transferred to/from<br>Data Bus pins DO-D7.                                                                                                                                      |

| GPIOO or W6E | 4   | IN/OUT | GENERAL PURPOSE I/O LINE O:<br>An user programmable I/O line<br>for use as an input or an<br>output. This pin can also be<br>programmed as a decoded output<br>for a write to address 6E.                                                                                             |

| GPIOl or R6E | 5   | IN/OUT | GENERAL PURPOSE I/O LINE 1:<br>An user programmable I/O line<br>for use as an input or an<br>output. This pin can also be<br>programmed as a decoded output<br>for a read from address 6E.                                                                                            |

| GPIO2 or W6F | 6   | IN/OUT | GENERAL PURPOSE I/O LINE 2:<br>An user programmable I/O line<br>for use as an input or an<br>output. This pin can also be<br>programmed as a decoded output<br>for a write to address 6F.                                                                                             |

| GPIO3 or R6F | 7  | · IN/OUT | GENERAL PURPOSE I/O LINE 3:<br>An user programmable I/O line<br>for use as an input or an<br>output. This pin can also be<br>programmed as a decoded output<br>for a read from address 6F. |

|--------------|----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INPUT        | 8  | IN       | INPUT PIN: The state of this<br>pin is sampled by reading<br>Register 7E, bit 4.                                                                                                           |

| Ουτρυτ       | 9  | OUT      | OUTPUT PIN: Controlled by the<br>bit 2 of the control block (AO<br>thru B7) of the sequencer ram.                                                                                          |

| INDEX        | 10 | IN       | INDEX: Input for the index<br>pulse received from the disk<br>drive. Must be a minimum of<br>one byte time.                                                                                |

| SECTOR       | 11 | IN       | SECTOR: Input for the sector<br>pulse received from drives<br>that are hard-sectored. Must<br>be a minimum of one byte time.                                                               |

| RST          | 12 | IN       | RESET: A low input sets an<br>internal reset latch that<br>stops all operations within<br>the chip and drops RG, WG, WAM<br>& NRZ outputs. Registers 71<br>through 7E are reset.           |

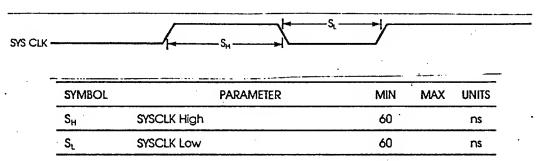

| SYSCLK       | 13 | IN       | SYSCLK: A 1.5 to 3.0 MHz<br>clock input which is used to<br>derive the Clock A output when<br>not reading or writing data.                                                                 |

| RG           | 14 | OUT      | READ GATE: Enables the<br>external phaselock loop to<br>lock onto the read data stream<br>coming from the storage device                                                                   |

| WG           | 15 | OUT      | WRITE GATE: Is used to enable<br>or gate the writing of NRZ<br>data out to the storage<br>device.                                                                                          |

| DO-D7      | 16-19<br>22-25 | IN/OUT | DATA BUS: Byte parallel data<br>lines to/from the buffer.                                                                                                                                                                                |

|------------|----------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND        | 20-21          |        | GROUND                                                                                                                                                                                                                                   |

| RD/REF CLK | 26             | . IN   | READ REFERENCE CLOCK: A<br>multiplexed input sourced from<br>the VFO oscillator during read<br>gate, otherwise from the write<br>oscillator. This is the<br>primary clock for the AIC-OlO.                                               |

| NRZ        | 27             | IN/OUT | NRZ: Read data input from the<br>device when RG is active; writ<br>data to the device when WG is<br>active.                                                                                                                              |

| WAM/AMD    | 28             | IN/OUT | WRITE ADDRESS MARK/ADDRESS<br>MARK DETECT: A one bit wide<br>pulse is output when write<br>gate is active and an address<br>mark is to be written. When<br>read gate is active, a low<br>level input to indicate<br>address mark detect. |

| CS         | 29             | IN     | CHIP SELECT: Active during<br>processor bus cycles to/from<br>the chip.                                                                                                                                                                  |

| WR         | 30             | IN     | WRITE: Signal from the<br>microprocessor to latch data<br>into a specified register.                                                                                                                                                     |

| RD         | 31             | IN     | READ: Signal from the<br>microprocessor to enable data<br>from a specified register out<br>onto the bus.                                                                                                                                 |

| ADO-AD7    | 32-39          | IN/OUT | Multiplexed address/data lines<br>interfacing to the control<br>processor.                                                                                                                                                               |

| VCC        | 40             | ······ | +5 Volts.                                                                                                                                                                                                                                |

.

#### FUNCTIONAL DESCRIPTION

Internal to the controller chip are three functional blocks:

- \* Microprocessor Interface Decoder

- \* Sector Format Sequencer

- \* Dataflow

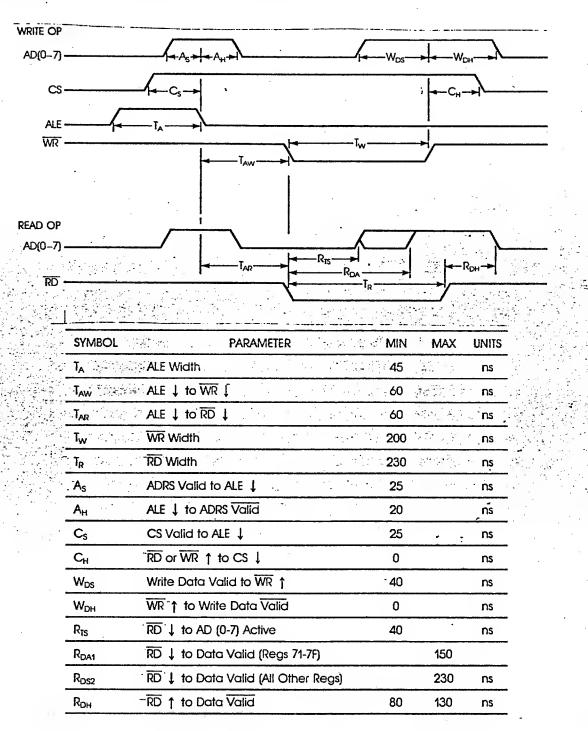

MICROPROCESSOR INTERFACE DECODER: The microprocessor interface is an eight-bit multiplexed bus such as is found on the Intel 8085 family of processors. Other microprocessors such as the Z80 can be utilized by multiplexing their address and data lines, and generating the necessary control lines.

•

The controller chip decodes addresses from 6EH to FFH, and addresses 50H and 51H. While all addresses are not used, to prevent erroneous operation, addresses from 6EH to FFH must not be decoded elsewhere on the controller board. The device architecture is structured to allow the firmware of an processor to determine what functions are to be incorporated in the control unit design.

SECTOR FORMAT SEQUENCER: The sector format sequencer performs the basic sequencing function for a mass storage device which include:

- \* Read ID

- \* Read ID and Read Data

- \* Read ID and Write Data

- \* Write ID and Write Data

These functions can be modified to perform the search data and verify data functions.

The sequencer consists of 96 bytes of RAM, organised as a 24 x 4 matrix. These locations have to be set up at initialization time, for the proper operation of the chip. Under firmware control, the AIC-OlO can be made to sequence through different types of operations. The user can control the timing relationships between various ouput signals, and can monitor the different input lines to branch to various sequencer locations.

The controller chip also has other registers which can be used to control the definition of the track format. Using these registers, such things like gap lengths, sync characters, ECC length can be controlled. The track layout (sector size and sector data fill character) can also be flexibly defined.

The Winchester controller chip interfaces with the bidirectional data bus which is connected to an external RAM buffer. The CS, WE, and address increment signals required for the sector buffer are derived from the Clock A and Clock B outputs.

DATA FLOW: The dataflow portion of the controller chip is composed of a 32 bit ECC and a serializer/deserializer. Data to be written to the disk enters the device in 8-bit parallel format. It is serialized, and run through a 32-bit ECC generator. The controller chip outputs NRZ serial data followed by 4bytes of ECC check burst.

The user has the ability to select the ECC polynomial that is optimum for the media and the encoding scheme that is being used. The ECC length can also be controlled, and in fact can be fully suppressed in the case of a tape controller. In this case, 2 bytes of CRC would have to be supplied externally.

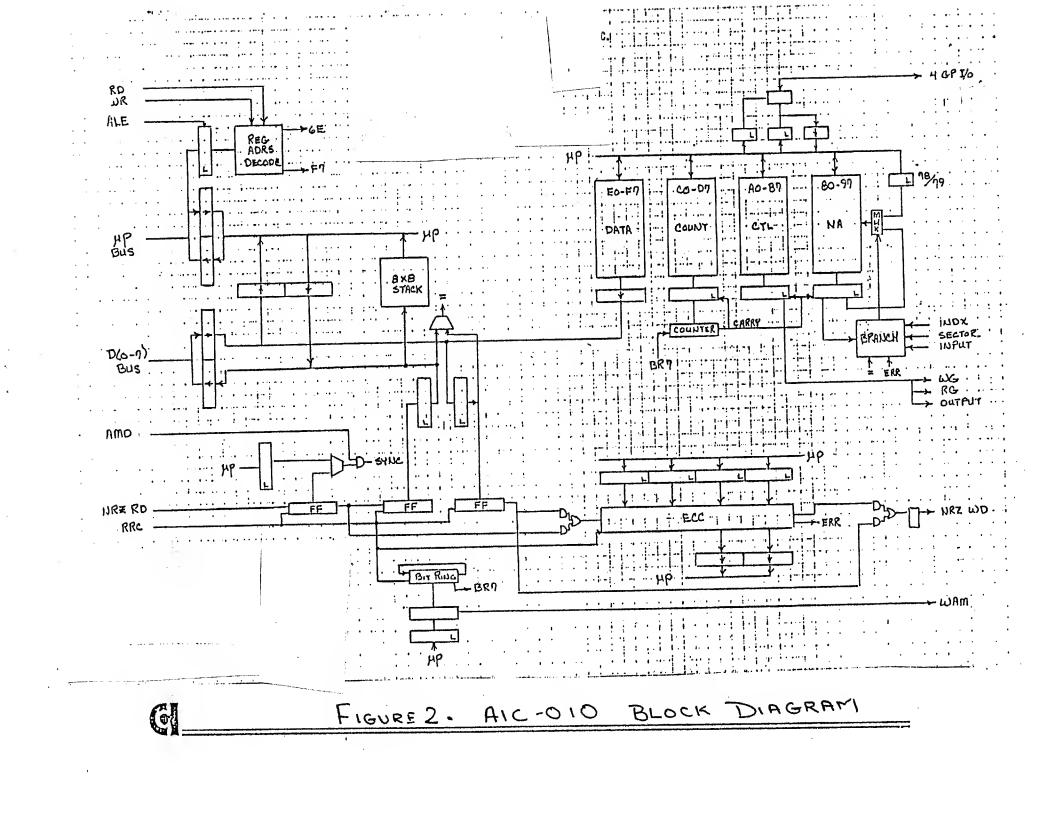

Figure 2 is a block diagram of the AIC-010 controller chip, and identifies the different blocks.

#### FUNCTIONAL OPERATION

The Programmable Mass Storage controller chip is designed to be used with a low-cost micro processor rather than the high-speed-bit slice designs required for controllers in the past. This processor is used to maintain "loose" synchronization with the real time on the device. The Winchester controller chip in return maintains the "close" synchronization of data to and from the disk and provides the signals necessary to control this path. With this device, a lower total part count can be achieved with the same or greater performance than that of a bit slice processor design.

Because the controller chip controls primarily the high speed signals associated with the Winchester disk, the designer is free to choose which type of drive to interface, e.g., ST506, SMD, etc. Each of these interfaces can be accommodated with the 4 general purpose I/O lines. These lines can be defined as input, output or external register decode signals. The AIC-OlO chip simplifies the external logic needed, by internally decoding addresses 6EH and 6FH, and providing signals to read and write ports at these locations.

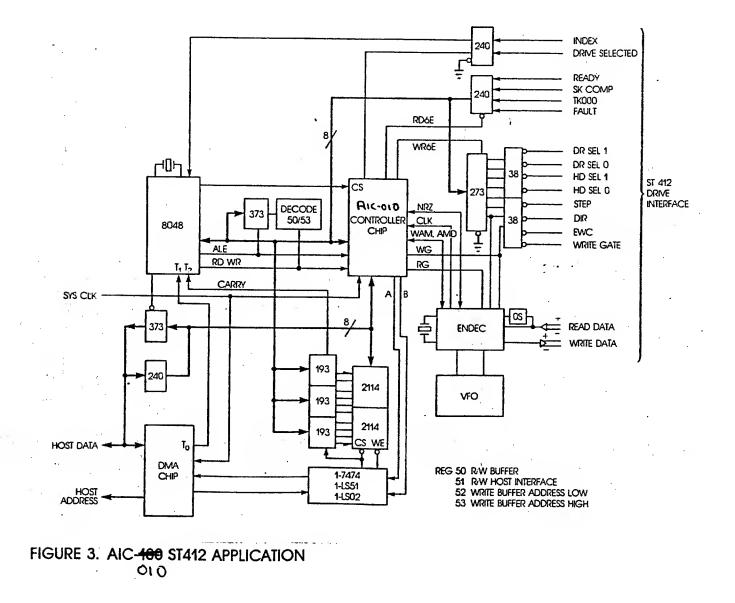

An example of an ST412 application is shown in Figure 3. These 4 signals are used to read device status or write device control lines.

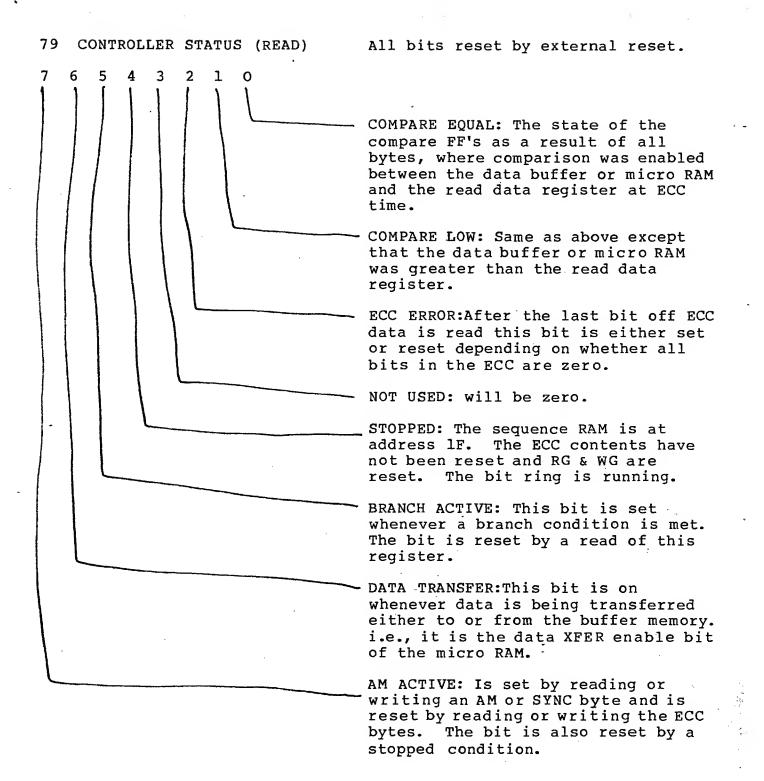

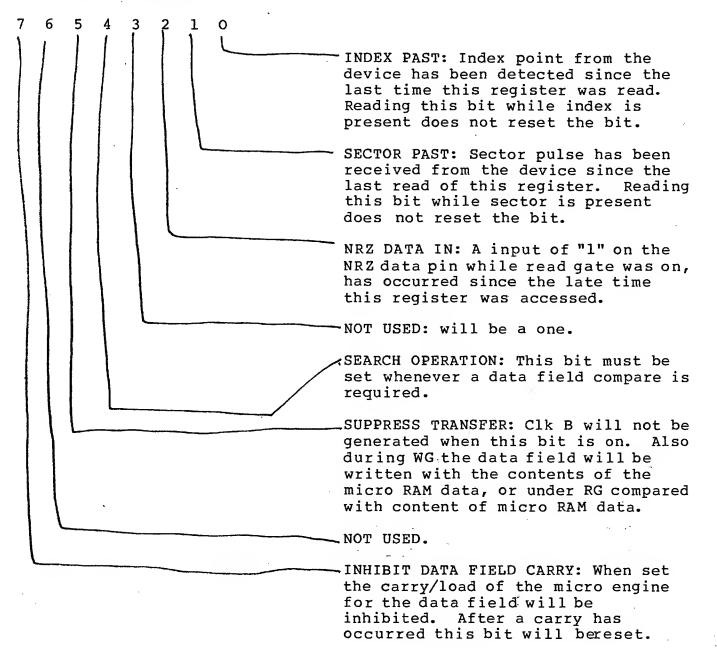

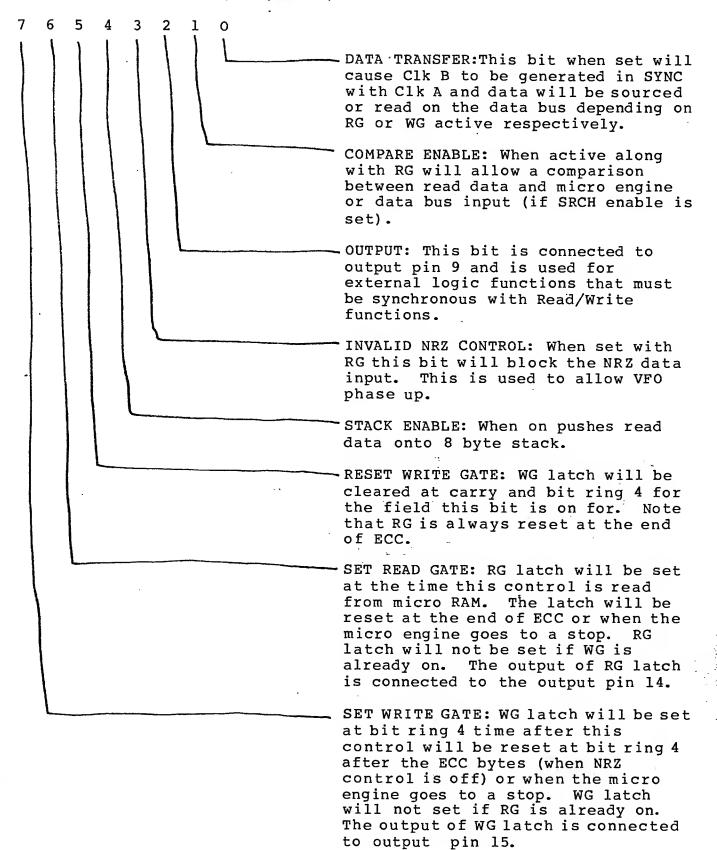

The basic operation of the controller chip are controlled by the contents of the sequencer ram. The sequencer ram consists of 96 bytes organized as 24 addresses which are 4 bytes wide. Each of these 4 bytes represent a field at that address, and is broken down as follows; Data, Count, Control and Next Address. The operation of the chip revolves around the branch register, Register 78; and the status/start register, Register 79. Register 79 is first loaded with the address where the sequencer is to begin execution. Thereafter, the chip sequences through the ram, and the next address executed is based on the contents of register 78 if a successful branch condition occurs. Otherwise it is based on the contents of the next address field at that address. Thus by setting up different conditions, which are based on external or internal events, the chip can be made to sequence through different operations. An example of the use of the AIC-010 as a ST-506 controller is shown in the Appendix.

The controller chip also has a stack which is 8 bytes deep. During a read process, by enabling the stack, information read from the drive such as the ID field, can be pushed on to the stack. These can then be popped, to look for any relevant information.

During a read process from the device, the chip also has the ability to compare the data being received, on a byte for byte basis with information found in other locations. The controller chip can be set up to compare with information found in the data field in the sequencer ram (such as when looking for the ID field), or with information stored in the external buffer (such as during a data field search operation). If an ECC error is detected after a read data operation, the syndrome is saved in the ECC register and will not be reset until a new read OP is started. By employing Registers 71, 72 and 73 the microprocessor can determine if the error is correctable, and if so, the error pattern and displacement from the beginning of the sector. The ECC polynomial is a computer selected code that will correct 8 bit single burst errors. After the error pattern is determined, it is EXOREd with the data byte (bytes) in the RAM buffer.

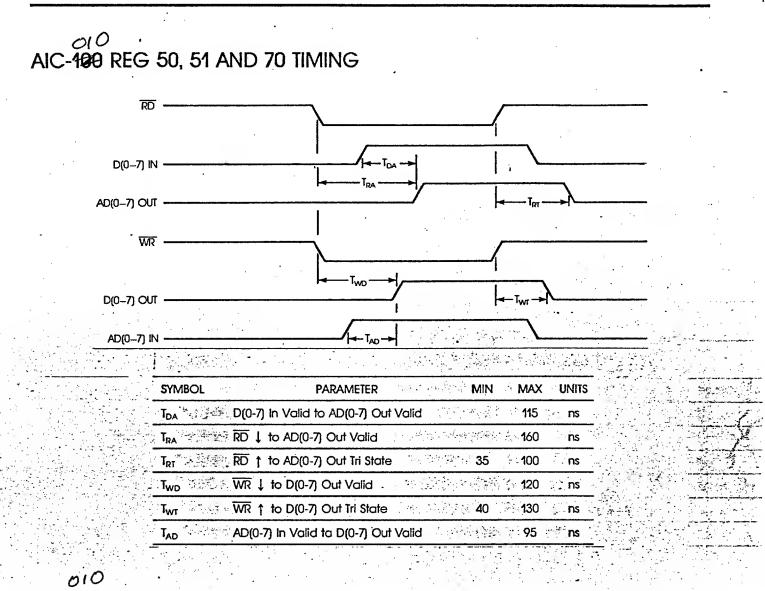

CLKA and CLKB outputs are used to control the external RAM buffer address counter. CLKB should be interpreted as the beginning of a controller chip memory access with a Clock A period equal to the RAM access time. The D(0-7) pins will contain valid data during that time of the cycle when CLKA is high. This is shown in the reference timing diagram.

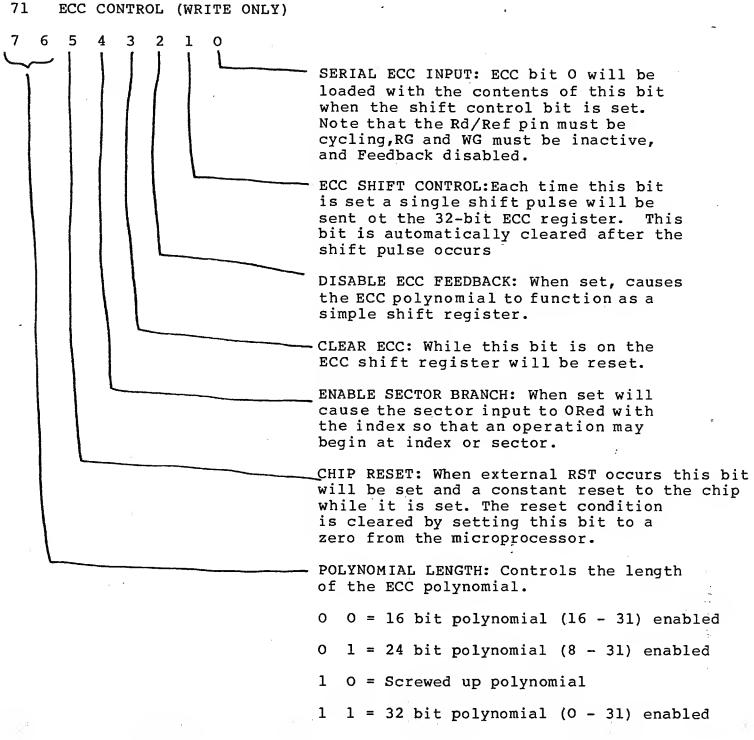

The table shows the register present in the AIC-OlO, which are used to control its operation. This is in addition to the sequencer ram which is located from address 80H to FFH. A more detailed graphical breakdown of the registers follows.

AIC-010

### SERDES REGISTER SUMMARY.

•

REV B 11/13/81

| Ø                               | BUFFER DATA                                                                                                                                                | 71                                   | ECC CTL                                                                                                                                                                                               | 72,                                   | ECC (16-23)                                                                                                                                                                        | 73 ECC (24-31)                                                                                                                                                                |  |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| M                               | 7<br>6<br>5<br>4 BUFFER<br>3<br>2<br>1<br>9                                                                                                                | W                                    | <ul> <li>7 DISABL 8-15</li> <li>6 DISABL Ø-7</li> <li>5 CHIP RESET</li> <li>4 EN SECTOR BRCH</li> <li>3 CLEAR ECC</li> <li>2 DISABL FEEDBACK</li> <li>1 SHIFT ECC</li> <li>Ø SERIAL ECC IN</li> </ul> | R                                     | 7 ECC 23<br>6 22<br>5 21<br>4 20<br>3 19<br>2 18<br>1 17<br>0 ECC 0-16                                                                                                             | R       7       ECC       31         6       3Ø         5       29         4       28         3       27         2       26         1       .25         Ø       ECC       .24 |  |

| '4                              | POLY (Ø-7)                                                                                                                                                 | 75                                   | POLY (8-15)                                                                                                                                                                                           | 76                                    | POLY (16-23)                                                                                                                                                                       | 77   POLY (24-31)                                                                                                                                                             |  |

| W                               | 7 POLY 8<br>6 7<br>5 6<br>4 5<br>3 4<br>2 3<br>1 2<br>Ø POLY 1                                                                                             | W                                    | 7 POLY 16<br>6 15<br>5 14<br>4 13<br>3 12<br>2 11<br>1 10<br>9 POLY 9                                                                                                                                 | W                                     | 7 FOLY 24<br>6 23<br>5 22<br>4 21<br>3 20<br>2 19<br>1 18<br>Ø FOLY 17                                                                                                             | W       7          6       FOLY       31         5       30         4       29         3       28         2       27         1       26         Ø       FOLY       25         |  |

| '8                              | BRANCH/MA                                                                                                                                                  | 79                                   | W START ADR/                                                                                                                                                                                          | 7a                                    | OP CIL                                                                                                                                                                             | 7B WAM CTL                                                                                                                                                                    |  |

| 1/R<br>1/R<br>1/R<br>1/R<br>1/R | <ul> <li>7TEST BR7</li> <li>6TEST ECC ERR</li> <li>5TEST CARRY</li> <li>4 BRCH/MA 4</li> <li>3 3</li> <li>2 2</li> <li>1 1</li> <li>Ø BRCH/MA Ø</li> </ul> | R<br>W/R<br>W/R<br>W/R<br>W/R<br>W/R | 6 DATA XFER<br>5 BRCH ACTIVE                                                                                                                                                                          | W/R<br>W/R<br>W/R<br>R<br>R<br>R<br>R | <ul> <li>7 INHIBIT</li> <li>6 CARRY</li> <li>6</li> <li>5 SUPRES XFER</li> <li>4 SRCH OP</li> <li>3</li> <li>3 NRZ DATA IN</li> <li>1 SECTOR PAST</li> <li>Ø INDEX PAST</li> </ul> | W 7 WAM AT BR7<br>6 6<br>5 5<br>4 4<br>3 3<br>2 2<br>1 1<br>9 WAM AT BR Ø                                                                                                     |  |

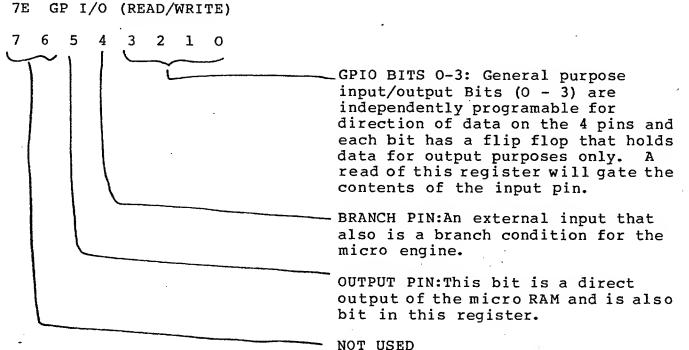

| 'C                              | AMD CTL                                                                                                                                                    | 7D                                   | GP I/O CTL                                                                                                                                                                                            | 7E                                    | GP I/O                                                                                                                                                                             | 7F   CLK CTL/POP                                                                                                                                                              |  |

| W                               | 7<br>6<br>5<br>4 AM<br>MATCH<br>3<br>2<br>1<br>Ø                                                                                                           | W                                    | 2 ENAB GP2 OUT<br>1 ENAB GP1 OUT                                                                                                                                                                      | R<br>R<br>R/W<br>R/W<br>R/W           | 7<br>6<br>5 OUT PUT<br>4 BRCH IN<br>3 GP I/O 3<br>2 2<br>1 1<br>0 GP I/O 0                                                                                                         | R/W 7 / ØØ = SC/4<br>}ØI = SC/2<br>6 / IØ = SC<br>5<br>4 / Ø = RRC/2 (5M<br>/I = RR4 4 (10MH<br>3 CLK A&B Hi Z<br>2 / NRZ SHIFT<br>1 } IN CODE<br>Ø /                         |  |

SEQUENCE MEHORY BIT MAP

C2 thru D7 AØ thru B7 80 thru 97 EØ thru E7 COMMENTS BRANCH CONT CONTROL NEXT ADRS. ADRS. DATA R78 R79 76543210 7654321976543218 76543210) g ø ÷ . . 1 1 • .: 2 • •• . 2 . -:---÷ • \* ~: 1 : 3 ۰. .3 • • . .... • . .: . • . ~ . . • 4 4 . 77-----. ••• ••• . . . . ÷ . 5 \_ 5 ٦, ٠., - - - - -- = . . . . . . 793 : ÷ : .. 6 7 6 . · •. •• .In. •: . ----Gi-i . •••• <u>\_\_\_\_</u> ÷:2 7 ي. 14 <u>نت رب</u>. • ..... ··· :·. ..... • :: • 8 8 • • prin 9 A B C ÷ ..... • • • • • • ÷. . 9 -. -. -. . -.... .. •••• • • • • • •. • • ŝ. ٠A · • • -: ' e. م<u>ي م</u>سرة · . · · . • . в --: ়. •••• ۰. • • . . ..... . . . . ÷ . . . •.•• C . • . D D . . . Е . Ε . E . Ē . 10 10 11 .. . . 11 . · . . . • ·. · .**.** : 12 • • • • • .12 : ' ÷, ·. . • • • • 13 13. . • • .• •••• . . 14 14 ... •• . . . ·15 15 • ٠ 16 16 . 17 17 . . . 765 219 765 3210 65 3210 3 7 3 210 65 4 4 4 7 4 STOP 1F IF STOP WG ON RG ON VG OFF STACK ENABL Invalid NR2 OUTPUT CONPARE EN DATA XFER . .. DATA DATA FIELD TYPE CVT . N.A. AM ECC Sebca RG - ECC = Ø RG - ECC = 1000 - No Branch 000 - No Branch 001 - ECC ERR Stop 001 - Stop on Input 010 - Stop on Index or Sector 010 - No Compare Stop 011 - Stop on Not Equal 911 - ERR or Comp. Stop 100 - Branch on Carry 199 - Good ECC & Comp. 101 - Branch on Input 110 - Branch on Index or Sector 101 - ECC ERR 110 - Not Equal 111 - ERR or Not Equal 111 - Branch on Not Equal

#### INTERNAL REGISTER DESCRIPTION

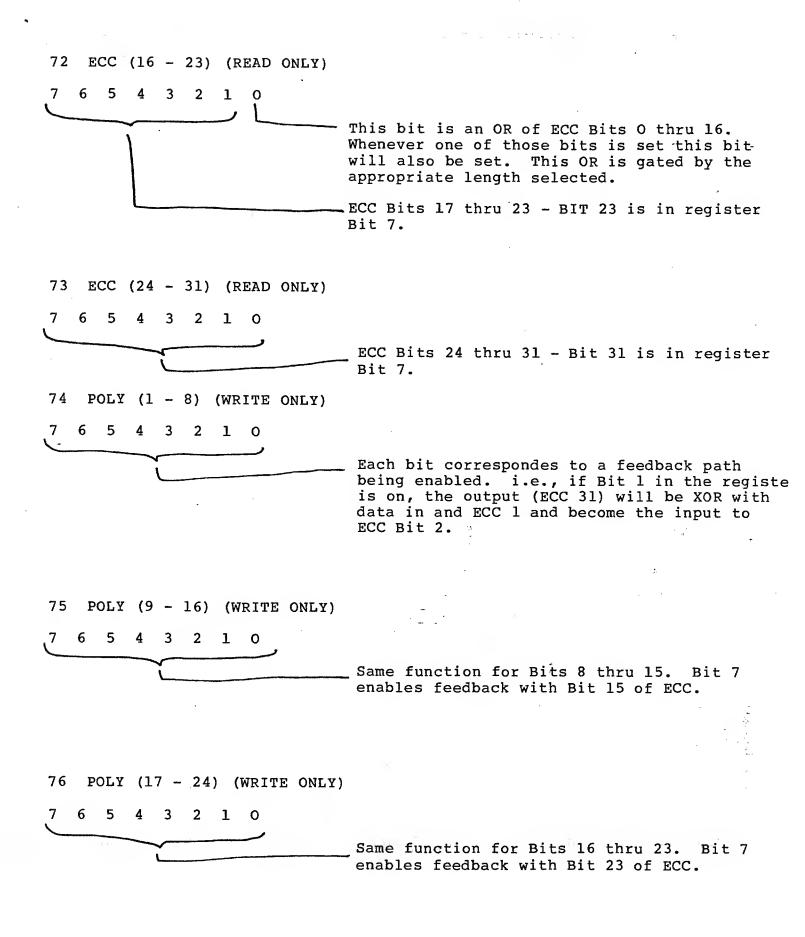

77 POLY (25 - 31) (WRITE ONLY)

7 6 5 4 3 2 1 0

Same function for Bits 24 thru 30. Bit 6 enables feedback with Bit 30 of ECC.

Not used.

Note: Registers 74 thru 77 can not be reset.

### 78 BRANCH CONTROL (READ/WRITE)

BRANCH ADDRESS: Writing Bits 0 - 4 will cause the sequence RAM to jump to this address when a branch condition is met.

A read off this reg Bits 0 - 4 are the next address field. Bits 5, 6 and 7 are test points.

79 SEQUENCER START (WRITE)

START ADDRESS: A write to bits 0-4 will start the sequencer at the appropriate address.

### 7A OPERATION CONTROL (READ/WRITE)

7.2

| 7B WAM CONTROL (WRITE ONLY)    |                                                                                                                                                                                                                                                                                                                  |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 6 5 4 3 2 1 0                |                                                                                                                                                                                                                                                                                                                  |

|                                | WRITE ADDRESS MARK CONTROL:The<br>WAM/AMD PIN will go active for each<br>bit cell time corresponding to the<br>bits set in this register during a<br>write address mark operation.                                                                                                                               |

| 7C AMD CONTROL (WRITE ONLY)    |                                                                                                                                                                                                                                                                                                                  |

| 7 6 5 4 3 2 1 0                |                                                                                                                                                                                                                                                                                                                  |

|                                | ADDRESS MARK DETECT CONTROL: A match<br>between this register and the serial<br>NRZ RD data input will cause a SYNC<br>detect (if AMD input is active), the<br>bit ring to start at zero, and data<br>to be gated into the ECC. Only<br>those bits enabled by reg 7F Bits O<br>thru 7 can be set for comparison. |

| 7D GP I/O CONTROL (WRITE ONLY) | · · ·                                                                                                                                                                                                                                                                                                            |

|                                | · ·                                                                                                                                                                                                                                                                                                              |

|                                | - GPIO DIRECTION CONTROL:When set<br>these bits enable the corresponding<br>bits of the GP I/O register to the<br>output pins. When these bits are<br>zero the pins are the source of the<br>GP I/O register.                                                                                                    |

|                                | i.e., inputs are simply gated to the bus when a read of GP I/O is done.                                                                                                                                                                                                                                          |

|                                | W6E CONTROL: When set along with Bit<br>O this bit will disable GP I/O reg<br>Bit O as an output and enable a set<br>register 6E output pulse. When zero<br>the GP I/O register is the output.                                                                                                                   |

|                                | - R6E CONTROL: Same function as above<br>except a read pulse for register 6E<br>will be output from pin 1.                                                                                                                                                                                                       |

|                                | W6F CONTROL: Same function as above<br>except a write pulse for register 6F<br>will be output from pin 2.                                                                                                                                                                                                        |

|                                | _ R6F CONTROL: Same function as above<br>except a read pulse for register 6F<br>will be output from pin 3.                                                                                                                                                                                                       |

|                                |                                                                                                                                                                                                                                                                                                                  |

•

•

NOT USED

| 7F         | CI     | LOC:  | K C | ON' | TROI | 5       | (W) | RIT | 'E)      |          |     |     |          |            |             |            |          |      |             |     |              |      |      |     |

|------------|--------|-------|-----|-----|------|---------|-----|-----|----------|----------|-----|-----|----------|------------|-------------|------------|----------|------|-------------|-----|--------------|------|------|-----|

| 7          | 6<br>~ | 5<br> | 4   | 3   | 2    | _       |     | 0   | ,        |          |     |     |          |            |             |            |          |      |             |     |              |      |      |     |

|            |        |       | (   | ·   |      |         | L   |     | -        | 0        | 0   | 0   | NRZ      | Sh         | ift         | Reg        | C        | ompa | ire         | Sta | arts         | Át   | Bit  | : 0 |

|            |        |       |     |     |      |         |     |     |          | 0        | 0   | 1   |          |            |             |            |          |      |             |     |              |      |      | 1   |

|            |        |       |     |     |      |         |     | -   |          | 0        | 1   | 0   |          |            |             |            |          |      |             |     |              |      |      | 2   |

|            |        |       |     |     |      | •       |     |     |          | 0        | 1   | 1   |          |            |             |            |          |      |             |     |              |      |      | 3   |

|            |        |       |     |     |      |         |     |     |          | 1        | 0   | 0   | *        |            |             |            |          |      |             |     |              |      |      | 4   |

|            |        |       |     |     |      |         |     |     |          | 1        | 0   | 1   |          |            |             |            |          |      |             |     |              |      |      | 5   |

|            |        |       |     |     |      |         |     |     |          | 1        | 1   | 0   |          |            |             |            |          | *    |             |     |              |      |      | 6   |

|            |        |       |     |     |      |         |     |     |          | 1        | 1   | 1   |          |            |             |            |          | -    |             |     |              |      |      | 7   |

|            |        |       |     | L   |      |         |     |     | <b>!</b> | Wh       | en  | set | Clk      | A          | & B         | out        | pu       | ts a | ire         | hiq | gh i         | mpeo | lenc | e.  |

| -          |        |       | L   |     |      | <u></u> |     |     |          | 0<br>1   |     |     | be<br>Cl | 2 (<br>k A | cyc:<br>dui | les<br>ing | pe<br>se | r by | rte.<br>nce | r č | lata<br>lata |      |      |     |

|            |        | ſ     |     |     |      |         |     |     |          | No       | t u | sed |          |            |             | -          |          |      |             |     |              |      | n ^  |     |

|            |        |       |     |     |      |         |     |     |          |          |     |     |          |            |             |            |          |      |             | •   |              | :    |      |     |

|            |        |       |     |     |      | •       |     |     | ~        | <b>0</b> | 0   |     |          |            |             |            |          |      |             |     | XFE          |      | 111  |     |

| -          |        |       |     |     |      |         |     |     |          | 0        | 1   |     |          |            |             |            |          |      |             |     | XFE<br>peri  |      | i11  |     |

|            |        |       |     |     |      |         |     |     |          | 1        | 0   |     |          |            |             |            |          |      |             |     | XFE<br>k pe  |      |      | 2   |

|            |        |       |     |     |      |         |     |     |          | 1        | 1   |     | Cli      | k A        | wil         | L1 b       | e 1      | ness | y.          |     |              |      | •    |     |

| 7 <b>두</b> | STA    | CK    | (RI | EAT | ))   |         |     |     |          |          |     |     |          |            |             |            |          |      |             |     |              |      |      |     |

STACK: A read of this reg will read the top of the 8 byte stack.

80 THRU 97 NEXT ADDRESS (READ/WRITE)

.

| 7 6 5 4 3 2 1 0 |                |                  |                 |                                                                                                                                                                             |

|-----------------|----------------|------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | mi<br>co<br>is | cro<br>unt<br>no | en<br>er<br>t t | RESS: This is the address the<br>gine will go to after the down –<br>has reached zero, if if a branch<br>aken. There are 24 possible next<br>locations locations.(00 to 17) |

|                 | EC             | Ca               | nđ              | ONDITIONS: Branch conditions when<br>read gate are is active. These<br>are taken at the end of ECC time.                                                                    |

|                 | 0              | 0                | 0               | Continue, next address used                                                                                                                                                 |

|                 | 0              | 0                | 1               | Go to address lF on ECC error                                                                                                                                               |

|                 | 0              | 1                | 0               | Go to address lF on not<br>compare equal                                                                                                                                    |

|                 | 0              | 1                | 1               | Go to address lF on not<br>compare equal or ECC error                                                                                                                       |

| -               | 1              | 0                | 0               | Branch on good ECC and<br>compare equal                                                                                                                                     |

|                 | 1              | 0                | 1               | Branch on ECC error                                                                                                                                                         |

|                 | 1              | 1                | 0               | Branch on not compare equal                                                                                                                                                 |

|                 | 1              | 1                | 1               | Branch on not compare equal<br>or ECC error                                                                                                                                 |

|                 |                |                  |                 | ondition at all other times.<br>anches are taken immediately.                                                                                                               |

| · · ·           | 0              | 0                | 0               | Continue, next address used                                                                                                                                                 |

|                 | 0              | 0                | 1               | Go to address 1F on external input active                                                                                                                                   |

|                 | 0              | 1                | 0               | Go to address 1F on index<br>or sector active                                                                                                                               |

|                 | 0              | 1                | 1               | Go to address lF on not .<br>compare equal                                                                                                                                  |

|                 | 1              | 0                | 0               | Branch on carry                                                                                                                                                             |

|                 | 1              | 0                | 1               | Branch on external input active                                                                                                                                             |

|                 | 1              | 1                | Õ               | Branch on index or sector active                                                                                                                                            |

|                 | 1              | 1                | 1               | Branch on not compare equal                                                                                                                                                 |

|                 |                |                  |                 |                                                                                                                                                                             |

#### AO THRU B7 CONTROL (READ/WRITE)

CO THRU D7 COUNT (READ/WRITE)

COUNT: These bits are the initial value of the micro engine counter when a new state is entered. Bits O thru 4 are set to bits O thru 4 of the counter respectively. The counter is down counted on bit ring 7 and when it reaches zero a new state will be accessed from thep micro RAM.

DATA TYPE: When data XFER bit of the micro RAM is off these bits are decoded for data type as indicated below:

- 0 0 0 Normal

- 0 0 1 AM

- 0 1 0 ECC

- 1 0 0 Set Enabl bit ring to Clk A (SEB (Reset at end of ECC)

Bits 5, 6 and 7 of the counter will be initialized to zero with data XFER B**it**off.

When the data XFER bit is set bits 5, 6 and 7 of the count will be initialized with bit 5, 6 and 7 respectively.

### EO THRU F7 DATA (READ/WRITE)

7 6 5 4 3 2 1 0

.

DATA: This register is the source for all overhead bytes of data used by the device during write operations. During Read operations it is one of the operands to the comparison logic.

When data XFER is on with the WG source for write data will be the external data bus. However when "surpress XFER" is on with WG this register will again be the source for write data.

#### EXTERNAL REGISTERS

The Winchester controller chip has three registers decoded that do not exist within the device. Their purpose is to provide versatile control unit design capability.

Registers 50, 51, and 70, when decoded, provide for a bidirectional connection of the microprocessor data bus with the buffer data bus through the Winchester controller chip on read or write.

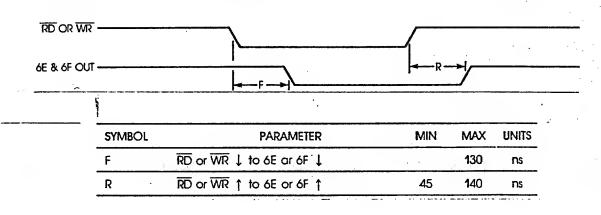

The general purposes I/O lines can also be set up as decodes for two external register addresses, at 6EH and 6FH. Internally, register 6E and 6F are decoded and a read or write to one of these addresses can be made to generate a negative pulse on one of four pins. These signals are then used to enable a 74LS244 onto the microprocessor bus or to latch the bus into a 74LS373. In this manner the drive interface to several types of drives can be accommodated.

An example of the usage of Registers 6E and 6F decode is shown below.

FIGURE 4. AIC-100 REGISTERS 6E AND 6F USAGE

### APPENDIX

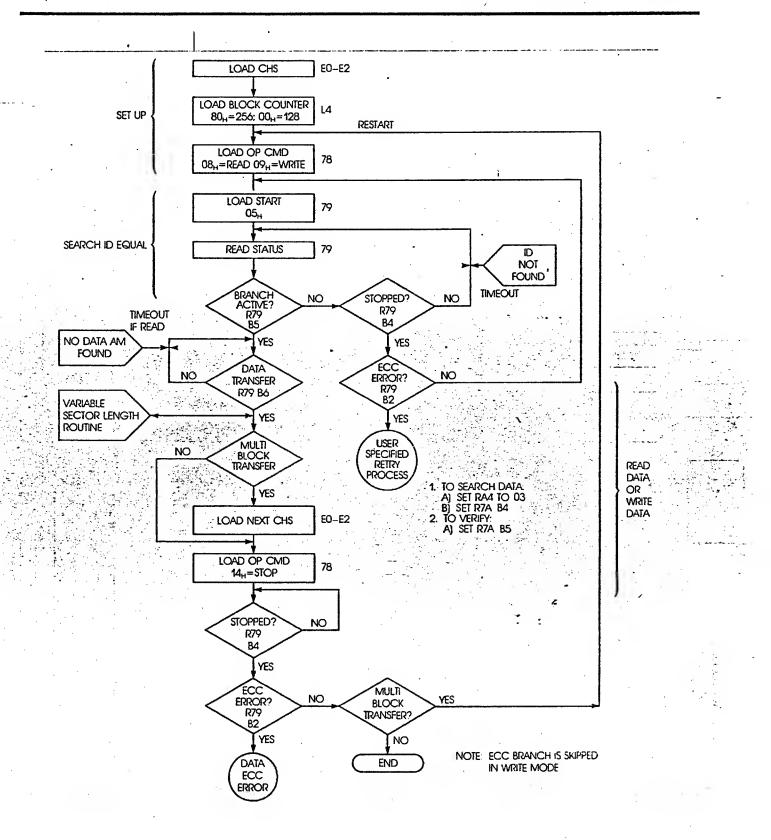

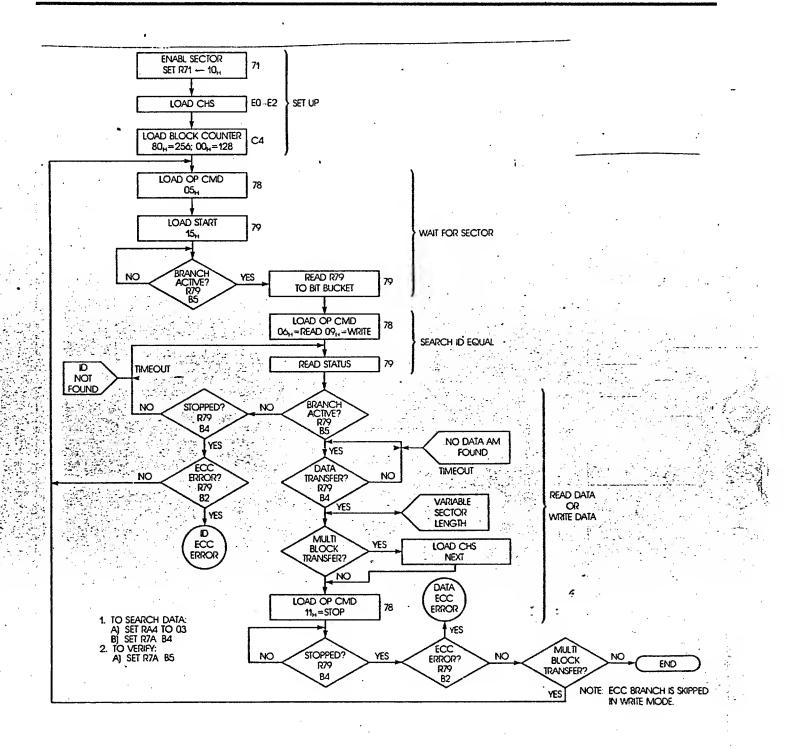

Fundamentally, any operation of the AIC-010 revolves around the following sequence of events:

\* Initialize the chip by loading up the sequencer ram with the appropriate values.

\* Setup the registers to handle the control of the data

\* Start sequencing the chip at the appropriate ram location, by loading register 79 with the starting address.

\* Monitor the status using register 79 and branching when appropriate, using the branch register, Register 78.

The following is a sequencer map of the AIC-OlO programmed as a ST-506 controller. The contents of the RAM are loaded up by the external microprocessor after power up. In addition, the ECC polynomial has to also be set up by the support processor.

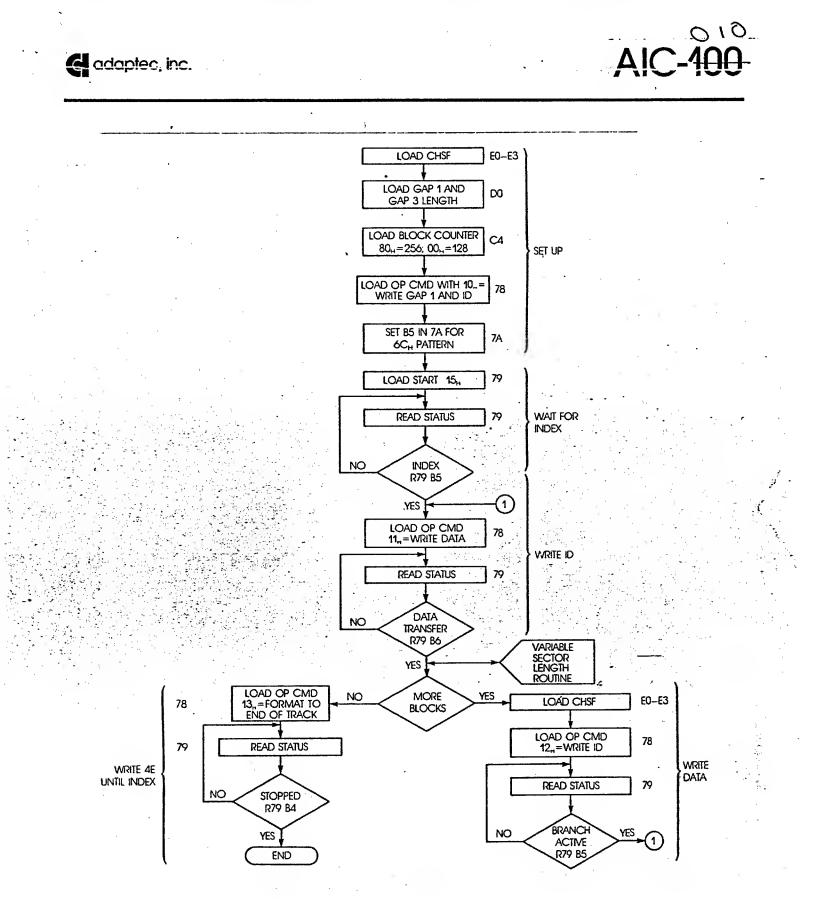

At this point, there are four fundamental operations that should be looked at. These are as follows:

\* Soft sector format

\* Soft sector read/write

\* Hard sector format

\* Hard sector read/write

The flow charts show the recommended steps to be followed in order to execute the above operations.

|              | -51      | EQUENCE MED                              | NORY DIT M            | PP FOR H    |                    | 57-5      | 06                    | CONTROLL                           | ER      |

|--------------|----------|------------------------------------------|-----------------------|-------------|--------------------|-----------|-----------------------|------------------------------------|---------|

|              |          |                                          | · · · · · ·           | אל דאנע אין |                    |           |                       | •                                  | •       |

|              | - 10     | כל דוגע בין                              |                       | NELT ADRS.  | en en              | SAVEJ     |                       | Comment                            | _       |

|              | DATA -   | COUNT                                    | CONTROL               | IVELI HUKS. |                    | (78       | *                     | •                                  | -       |

|              | 76543210 | 16543210                                 | 16343210              | 71.543210   |                    |           |                       |                                    | ••••    |

| 0            | ct       | 00                                       | 12                    | 01          | 6                  | C         | •                     |                                    | · • • • |

|              | но       |                                          | 12                    | - 02 .      |                    | <i>H</i>  |                       | -                                  | · • • • |

| z            | SEC      | 00 .                                     | 12                    | 03          | z                  | 5         | •                     |                                    |         |

| : (          | Fing     | -00                                      | 10                    | 0 C         | 3                  | F         |                       |                                    |         |

| 4            | 60       |                                          | 05                    | 00          | 4                  |           | ATA                   |                                    |         |

| 5            | 00       | 03                                       | SO                    | - 0 F       | -5                 |           | OID                   |                                    | •       |

| 6            | A 1      | 80                                       | <u> </u>              | .07         | G                  |           | AM                    |                                    |         |

| 7            | FE       | - <b>0</b> 0                             | 02                    | 00          | ?                  |           | SPN                   |                                    | • • •   |

| 8            | 00.      | 00                                       | 00                    | 17          | 8                  |           |                       | R DELA                             | ••••    |

| 9            | 00       | 08                                       | <u> </u>              | • • A • •   | 9                  |           |                       | r Data                             |         |

| A            | A        | AO                                       | · 0 Z                 | <u> </u>    | A                  |           | ATA A                 |                                    |         |

| 8            |          | 00                                       | - 02                  | * 04        | В                  |           | ATA S                 |                                    | n       |

| c            | 00       | 43                                       | · 00 · ·              | - 94        | Ċ                  |           |                       | BRCHONGOODI                        |         |

| D            | 00       | 43                                       | 00                    | 94          | . 0                |           |                       | BREH ON CARR                       |         |

| E            | · 00 ·   | OB                                       | 80                    | 06          | E                  |           |                       | EMT ID                             | · •     |

| F            | 00       | .01                                      | 4.0                   | 06          | F                  |           | G1 FO                 | • •                                | ••      |

| · · 10       | 4E       | 00-1F                                    | 80                    | <u> </u>    | 10                 |           |                       | AP 1 ¢4                            | 0       |

| $\mathbf{n}$ | . 00 _   | 05                                       | 00                    | <u> </u>    | 11.                | F         |                       | ATA FIELD.<br>TA FIELD FOR FI      | HT :    |

| 12           | 00       | . 01 .                                   | 0                     | 10          | 12                 | <i>E</i>  | 00 PA                 |                                    | ST SEC  |

| 13           | 00       | 01                                       | 00                    | 16.         | 13                 |           |                       | n n n LA:<br>n n Roj               | •       |

| . 14         | 00       | 03                                       | 00                    | 1 <u>F</u>  |                    |           | 2                     |                                    | WK.     |

| 15           | 00       | . 00                                     |                       | 705         | 15                 |           |                       | N JNDEX 1                          |         |

| 16           | HE_      | 00 -                                     | 00.                   | 56          | 16                 |           | -                     | ON INDEX ?                         |         |

| 17           | 96543210 | 01                                       | 40                    | 04          | 17 1               |           | GT FO                 | DATA                               |         |

| 570P=18      | 16515210 | en e | ,<br>                 | y           | 18=                | STOP      |                       |                                    |         |

|              | DATA     | TYPE (-1)                                | Solution and a second | N.A.        |                    |           | *                     |                                    |         |

|              |          | - 35<br>                                 | ACK OF                |             |                    | ,<br>,    |                       |                                    |         |

|              | • • • •  | A LAND                                   | 35323051              | · . 1 (coo- | ig - Ecc<br>No Bri | anch 🔭    |                       | RG BRANCH                          |         |

|              |          | 10                                       |                       | 001         | ECC ER             | PARE SE   | 0 L C                 | - STOP ON INPUT<br>- STOP ON INDER | e Sect  |

| •            | burn     | SOFFES                                   | $\sim$ .              | Vol1-       | COODE              | Comp. Sto | P 100                 | - BRANCH ON CAR                    | RY      |

|              |          |                                          |                       | 101-        | ELC E              | QUAL.     | 101<br>. 110<br>. 111 | - # # 1NCC                         | EQUAL   |

|              |          | • • •                                    | •                     | Urr-        | err o              | r not eq. | , 111<br>-            | 1001                               |         |

|              |          |                                          | · ·                   | • • • •     |                    |           |                       |                                    |         |

.

÷:

.

e

÷

÷ v

•

### Winchester Disk Controller

# Soft Sector Format

A stondord Winchester soft sector format employs 256 byte sectors and MFM encoding. This format yields 32 sectors per trock. Any sector size which is o multiple of 128 may be employed (discussed later).

The format trock commond sequence is os follows:

- Set Registers EO, E1, E2, and E3 with the first sector ID (cylinder, head, sector and flag respectively).

- 2. Set Register DO with Gop 1 and Gap 3 length.

- Set Register C4 with either 8O<sub>H</sub> (256 byte count) or OO<sub>H</sub> (128 byte count).

Set Register 78 (command register) with 10<sub>H</sub>. This will farmat Gap 1 ofter index.

- Set bit 5 in Register 7A for a 6C<sub>H</sub> doto pottern. Otherwise contents of the sector buffer will be used during write to the data field.

- Set Register 79 with 15<sub>H</sub>. This will start the formot operation. The Winchester controller chip waits for index, after which Gap 1 will be written.

- Reod stotus from Register 79. If BRANCH ACTIVE (bit 5 is set) it meons that index is past and Gap 1 is being written. After this the first ID will be written.

- Set Register 78 with 11<sub>H</sub>. This will cause the data to be written next.

- Read status from Register 79. If bit 6 is set, the dato field is now

being written.

- If there ore no more sectors ta be written, load Register 78 with 13<sub>H</sub>, check Register 79 and woit for the controller to stop (bit 4 is set).

- Otherwise set Register 78 with 12<sub>H</sub> ond update Register EO through E3 with the next ID field to be written.

- Woit for BRANCH ACTIVE by monitoring Register 79, bit 5. Gap 3 is being written.

Repeat steps 8, 9, 10, 11 and 12 for 31 times ar the number of sectors to be formatted.

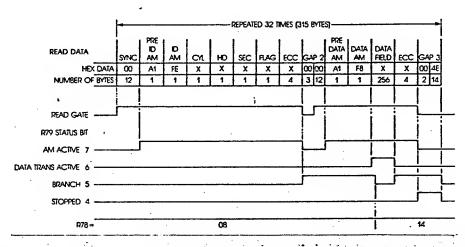

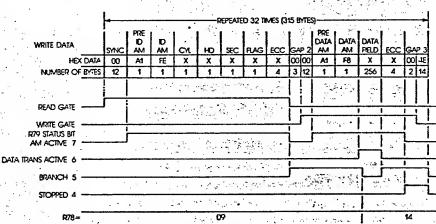

| INDEX               | L     |      | ·               | -        | -  | D  | EPEATE |    | AFS (31 |       |     |            |               | •          |          |          |        |               | - /- |

|---------------------|-------|------|-----------------|----------|----|----|--------|----|---------|-------|-----|------------|---------------|------------|----------|----------|--------|---------------|------|

|                     | GAP 1 | SYNC | PRE<br>ID<br>AM | ID<br>AM | СЦ | HD |        |    |         | GAP 2 | PRE | DATA<br>AM | data<br>Field | ECC        | GA       | >3       | GAP 4  |               |      |

| HEX DATA            | 4E    | 00   | A1              | FE       | X  | X  | X      | X  | X       | 00 00 | A1  | F8         | X             | X          | 00       | _        | 4E     |               |      |

| NUMBER OF BYTES     | _14   | 12   | 1               | 1        | 1  | 1  | 1      | .1 | •4      | 3 12  | 1   | 1          | 256           | 4          | 2        | 14       | 352 (N | IOM.)         |      |

|                     | ŝ     |      |                 |          |    |    |        | -  | 0       |       |     | ·· · *     |               | 1966.<br>1 |          | 1        | · 7%   | <u> </u>      |      |

| WRITE GATE          | •     |      |                 | ф. •     |    | •  | ·      | -  |         |       | ;   | -          |               | -          |          |          |        |               |      |

| R79 STATUS BIT      |       |      |                 |          |    |    |        |    | •       |       |     |            |               | 4          |          | ·.       |        | -             |      |

| AM ACTIVE 7         |       |      |                 | ÷        |    |    |        |    |         |       | ſ   |            | ·             |            | <u>ا</u> |          |        | 1             |      |

| DATA TRANS ACTIVE 6 |       |      |                 |          |    |    |        |    |         | 1     |     |            |               | L          | 1        |          |        | $\frac{1}{1}$ |      |

| BRANCH 5            |       |      |                 | •        |    |    |        |    |         | i     |     |            | 7_            |            |          | <u>ا</u> |        |               | ÷    |

| STOPPED 4           |       |      |                 |          |    |    |        |    |         |       |     |            | <u> </u>      |            |          | <u> </u> |        | 1             |      |

|                     | 1     | •    |                 |          |    |    |        |    |         |       |     |            | 1             |            |          | 1        |        |               |      |

| R78=10              |       |      |                 |          |    |    | 11     |    |         |       |     |            | 12<br>OR      | FOR LA     |          | •        |        | TE NEXT       | D    |

### Winchester Disk Controller

# Soft Sector Read/Write

In order to read or write data, the heads have to first be positioned aver the appropriate cylinder, and the relevant head must be selected. The follawing steps assume that the correct track has been reached.

The operation is performed as follows:

- 1. Set REO, E1 and E2 with the desired sector ID.

- Set C4 with either OO (128 byte caunter) ar 8O (256 byte counter).

- 3. Set OP command (R78) with O8, the read data command, or with O9, the write command.

- 4. Set Start Reg (R79) with O5. This will turn on Read Gate and enable the VFO to look for an address mark.

- 5. Wait for BRANCH ACTIVE (R79, bit 5). If the correct ID field was read, the Winchester controller chip will continue on to read the data field. If an ID ECC error ar incorrect sector was encountered, the stopped bit in R79 will be set. If so, go back to Step 4.

- 6. Wait for DATA TRANSFER (R79 bit

6). Read data is now being

transferred to the sector buffer,

or write data from the buffer,

- If this is a multiblock transfer, update EO-E2 with next sector ID while data is being transferred.

- Set OP command (R78) with 14. This will stop the Winchester controller chip at the end of the data field ECC.

- 9. Wait for STOPPED (R79 bit 4).

- 10. If it is a read command, test ECC ERROR (R79, bit 2). If it is set, ga to the error correction routine. If not, continue on ta read the next sector (Step 3) or end.

# AIC-400

### Winchester Disk Controller

## Hard Sector Format

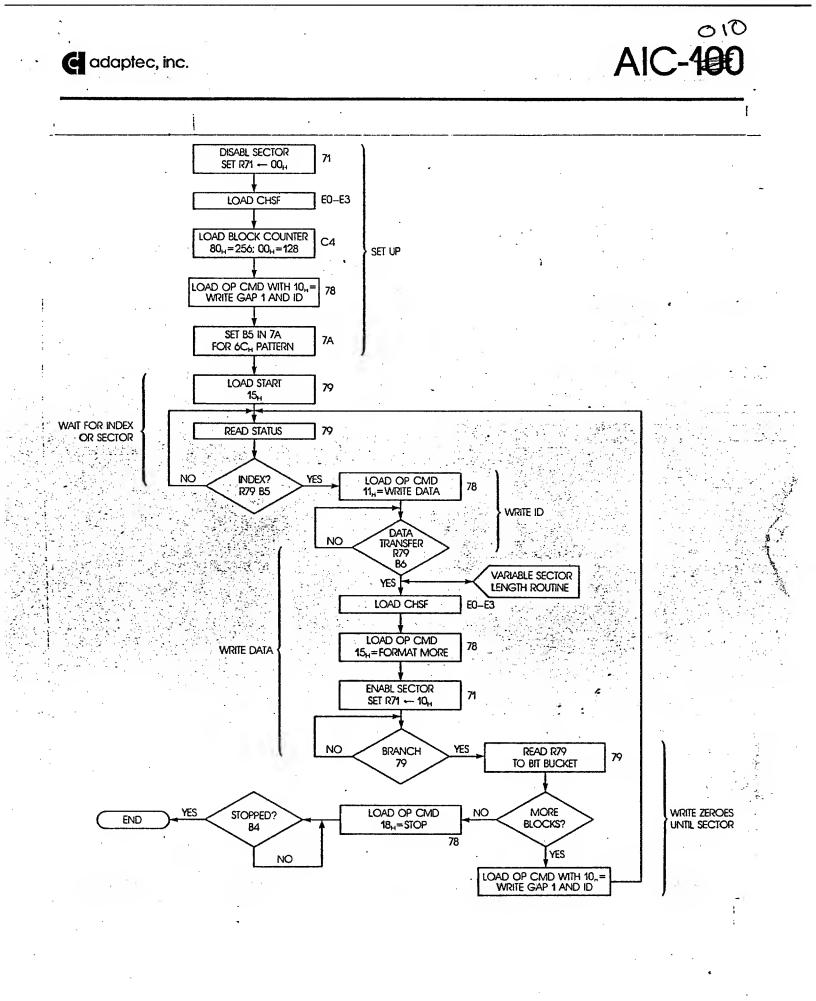

As mentioned eorlier, the AIC-100 controller chip is copable of supporting hard sectored drives. Hord sector drives differ from soft sector drives in thot, between every adjocent sector on a track, there is a sector mark, and this is used to identify the beginning of a sector.

A hard sectored format operation is performed os follows:

- Disoble sector mark by setting Register 71 to OO<sub>H</sub>. Thus the controller chip will wait for the index mark before writing out Gap 1.

- Lood Registers EO-E3 with the sector ID (cylinder, head, sector and flog).

- 3. Lood Register C4 with the data

length ( $8O_{\rm H} = 256, OO_{\rm H} = 128$ ).

4. Load Register 78 with 10<sub>H</sub>. This will cause Gap 1 to be written after index.

Set bit 5 in Register 7A for 6C<sub>H</sub> data pattern. Otherwise sector buffer is used.

6. Load Register 79 with 15<sub>H</sub> to start formatting.

- 7. Read status from Register 79. If bit 5 is set, then Gap 1 is being

- written. After this the ID is written.

- Load Register 78 with 11<sub>H</sub>. This tells the controller to write the data

- next.9. Read status from Register 79. If bit 6 is set, then data is being

tronsferred.

- Update Registers EO-E3 with the next sector ID. This has to be done before even checking if there are more blocks, since, on a hard sector drive, the timing is more critical.

- Lood Register 78 with 15<sub>H</sub>. This tells the controller to write zeros until the next sector mork is encountered.

- 12. Enable sector branch by setting Register 71 to 10<sub>H</sub>.

- Read status from Register 79 and branch when active (bit 5 is set). This means that a sector mark was encountered.

- 14. Read status from Register 79 and discord contents. This guarantees

- 15. Check to see if any more blocks have to be written. If there is no more to be done, then lood Register 78 with 18<sub>H</sub>. This tells the controller to stop. Monitor Register 79 bit 4 (stop bit) before leaving the routine.

- If more blocks have to be written, then load Register 78 with 10<sub>H</sub> and repeat steps 7 through 15.

NOTE: It is suggested that Gap 1 length be kept to zero. Thus, during format, after the sector mark is encountered, the controller will write out the Sync for ID field. Inter record separation is provided by the cantroller writing OO from end of data field to next sector mark.

### Winchester Disk Controller

### Hard Sector Read/Write

As mentianed earlier, a hard sector<sup>1</sup> drive has a sectar mark between adjacent sectors. Thus the controller starts reading the ID field after the next sector mark is encountered.

The read and write operations differ In that offer a write operation, no ECC test is necessary. The read or write data operation is performed as follows:

- 1. Enable branch an sector mark by setting Register 71 to 10<sub>H</sub>.

- 2. Set Registers EO, E1 and E2 with the desired sector ID.

- 3. Set C4 with either OO (128 byte counter) or 8O (256 byte counter).

- Load Register 78 with O5<sub>H</sub>, the read ID command. The VFO will look for a SYNC af A1 after read gate is turned an.

- Load Register 79 with 15<sub>H</sub>. The controller will wait for index or the next sectar mark (since R71 wos set to 10<sub>H</sub>) and read the ID field.

- Wait for BRANCH ACTIVE (R79, bit 5). This means that the next sector mark or index has been encountered. The read gate will not be turned on.

- Read and discard Register 79 to ensure reset.

- 8. Load Register 78 with O8, the read command or a O9 for a write command.

- Wait for BRANCH ACTIVE (R79 bit

5). If the correct ID field was read, the Winchester controller chip will continue on to read the data field. If an ID ECC error or Incorrect sector was encountered, the stapped bit in Register 79 will be set. If sa, go back to Step 4.

- Wait for DATA TRANSFER (R79, bit 6). Read data is now being transferred to the sector buffer, or from the buffer in the case of a write.

- If this is a multi-block transfer, update EO-E2 with next sector ID while data is being transferred.

- 12. Set Register 78 with  $14_{H}$  (STOP command). This will stop the controller chip at the end of the data field ECC.

- Wait for STOPPED (R79, bit 4).

Test ECC ERROR (R79, bit 2). If it is set, go to the error correction routine. If not, continue on to the next sector (Step 4) or end.

AIC-100

#### AIC-010 SOFT SECTOR FORMAT SEQUENCING

The following example shows the operation of the AIC-OlO (programmed as a ST-506 controller) during a soft sector format operation. The example is presented using "Snapshots" of the AIC-OlO and system activity descriptions. The time references assigned to each snapshot or event represent the approximate times associated with a ST-506 disk drive. The drive is formatted for 256 byte sectors.

SYSTEM ACTIVITY (t = 0.0 to 0.5 ms)

Host initializes AIC-010 registers

Branch register = 10H RDOH = Gap 1 length (14 bytes) REOH = I.D. Cylinder Value RE1H = I.D. Head Value RE2H = I.D. Sector Value RE3H = I.D. Flag Value

Host writes 15H to AIC-010 sequencer start register (R79H) at t = .5ms

AIC-010 STATE (t = 0.5ms)

| Current Address: | 15H .                     |

|------------------|---------------------------|

| Next Address:    | 15H Loop until Branch     |

| Branch Control:  |                           |

| ÷ .              | Branch on Index or Sector |

| Branch Register: | 10H                       |

| Control:         | N.A.                      |

| Data Field:      | N.A.                      |

| Count:           | N.A.                      |

|                  |                           |

SYSTEM ACTIVITY (t = 0.5 to 10.0ms)

AIC-010 waits for Leading edge of Index to begin writing Gap 1. When Index is detected by the AIC-010 the Branch Active Flag is set.

#### AIC-010 STATE (t = 10.0ms)

| Current Address: | 10H                                      |

|------------------|------------------------------------------|

| Next Address:    | OEH                                      |

| Branch Control:  | 000                                      |

|                  | No Branch                                |

| Branch Register: | ІОН                                      |

| Control:         | 80H (WG on)                              |

| Data Field:      | 4 H Gap 1 Character                      |

| Count:           | Set by host at initialization (14 bytes) |

SYSTEM ACTIVITY (t = 10.0 to 10.022 ms)

AIC-010 has asserted write gate and the NRZ output is Gap 1 character. The host has detected the index pulse and has loaded the branch register with 11H (write I.D.)

## AIC-010 STATE (t = 10.022ms)

Current Address: OEH Next Address: O6H Branch Control: O00 No Branch Branch Register: 11H Control: 80H (WG on) Data Field: OOH Count: OCH (Write 12 bytes of 00 sync code)

SYSTEM ACTIVITY (t = 10.022 to 10.040ms)

AIC-010 NRZ output is 00H Sync characters. The host is waiting for data transfer.

AIC-OlO STATE (t = 10.040ms)

| Current Address: | Обн                                                                        |

|------------------|----------------------------------------------------------------------------|

| Next Address:    | 07н                                                                        |

| Branch Control:  | 000                                                                        |

|                  | No Branch                                                                  |

| Branch Register: | 11H                                                                        |

| Control:         | O2H (Not valid with RG =0)                                                 |

| Data Field:      | Alh                                                                        |

| Count:           | 1000 0000 (Strobe AM output bit as defined by<br>WAM Control register 7BH) |

SYSTEM ACTIVITY (t = 10.040 to 10.04lms)

AIC-010 NRZ output is A H Address mark character. The AM output will be strobed at the bit(s) time defined by the WAM control register.

AIC-010 STATE (t = 10.04 lms)

| •                |                                           |

|------------------|-------------------------------------------|

| Current Address: | 07H                                       |

| Next Address:    | ООН                                       |

| Branch Control:  |                                           |

|                  | No Branch                                 |

| Branch Register: | 11H                                       |

| Control:         | O2H (Not valid with RG = O)               |

| Data Field:      | FEH                                       |

| Count:           | OOH (Write 1 byte of I.D field sync byte) |

|                  |                                           |

SYSTEM ACTIVITY (t = 10.041 to 10.043ms)

AIC-010 NRZ output is FEH I.D. field sync character.

### AIC-OIO STATE (t = 10.043ms)

| Current Address: |                                    |

|------------------|------------------------------------|

| Next Address:    | Olh .                              |

| Branch Control:  | 000                                |

|                  | No Branch                          |

| Branch Register: | 11H                                |

| Control:         | O2H (Not valid with RG =O)         |

| Data Field:      | Cylinder value established by host |

| Count:           | OOH (Write 1 byte)                 |

SYSTEM ACTIVITY (t = 10.043 to 10.050ms)

AIC-OlO NRZ output is I.D. cylinder, head, sector, flag bytes as micro-sequencer executes locations OO, Ol, O2 and O3. The next location after O3H (Flag byte write) is OCH (I.D. ECC write).

AIC-010 STATE (t = 10.050ms)

| Current Address: | ОСН                              |  |

|------------------|----------------------------------|--|

| Next Address:    | 14H                              |  |

| Branch Control:  | 100                              |  |

|                  | Branch at end of ECC             |  |

| Branch Register: | 11H                              |  |

| Control:         | ООН                              |  |

| Data Field:      | N.A.                             |  |

| Count:           | OlOO OOll (Write 4 bytes of ECC) |  |

SYSTEM ACTIVITY (t = 10.050 to 10.056ms)

AIC-010 NRZ output is I.D. ECC characters (4 bytes)

AIC-010 STATE (t = 10.056ms)

| Current Address:<br>Next Address: | О9н                        |   |

|-----------------------------------|----------------------------|---|

| Branch Control:                   | 000                        | - |

|                                   | No Branch                  | í |

| Branch Register:                  | 11H                        |   |

| Control:                          | ООН                        |   |

| Data Field:                       | 00                         |   |

| Count:                            | O5H (Write 6 bytes of OOH) |   |

AIC-OlO STATE (t = 10.060ms)

| Current Address: | О9Н                        |

|------------------|----------------------------|

| Next Address:    | ОАН                        |

| Branch Control:  | 000                        |

|                  | No Branch                  |

| Branch Register: | 11H                        |

| Control:         | 80H                        |

| Data Field:      | 00                         |

| Count:           | O8H (Write 9 bytes of OOH) |

## SYSTEM ACTIVITY ( $t = 10.056 \ to \ 10.080 \ ms$ )

AIC-010 NRZ output is 15 bytes of OOH (Data field sync bytes)

AIC-010 STATE (t = 10.080ms)

Current Address: OAH Next Address: OBH Branch Control: 000 No Branch Branch Register: 11H Control: O2H (Not valid with RG = O) Data Field: AlH Count: 1010 0000 (Write 1 byte Data field AM AM output will be strobed as defined by WAM control register. CLKA and bit ring will be synchronized) AIC-OlO STATE (t = 10.080ms)Current Address: OBH Next Address: 04H Branch Control: 000 No Branch Branch Register: llH O2H (Not valid with RG = 0) Control: Data Field: F8H Count: OOH (Write 1 byte Data field syn) 1 SYSTEM ACTIVITY (t = 10.080 to 10.083ms) AIC-010 NRZ output is A (with AM output strobe) followed by FBH sync byte. AIC-010 STATE (t = 10.083 ms)Current Address: O4H Next Address: ODH Branch Control: 000 No Branch Branch Register: **1**1H Control: 05H (Output & Data Transfer bits set) Data Field: 6CH Count: FFH (256 byte multiples sent by host)

SYSTEM ACTIVITY (t = 10.083 to 10.492ms)

AIC-010 NRZ output is the sector data from the host buffer or a fill value of 6CH. Host buffer data will be transferred if the "Supress Transfer" bit (R7A bit 5) is off. If this bit is set then the 6CH fill byte will be output. At this point the Data Transfer flag (R79 bit 6) will be set and the host will load the branch register with 12H (end of data field format branch). Setting "Inhibit Data Field Carry" will allow a second 256 byte transfer (for 512 byte sectors).

#### AIC-OlO STATE (t = 10.492ms)

| Current Address: | ODH                       |

|------------------|---------------------------|

| Next Address:    | 14H                       |

| Branch Control:  | 100                       |

|                  | Branch after ECC complete |

| Branch Register: | 12H                       |

| Control:         | OOH                       |

| Data Field:      | ООН                       |

| Count:           | 43H (Write 4 ECC bytes )  |

SYSTEM ACTIVITY (t = 10.492 to 10.498ms)

AIC-010 NRZ output is Data Field ECC. At the end of the ECC, branch is active. The host has been waiting for branch active to set the branch register to 12H (Write I.D. for the next sector).

AIC-OlO STATE (t = 10.498 ms)

| Current Address: | 12H                       |        |

|------------------|---------------------------|--------|

| Next Address:    | 10H                       |        |

| Branch Control:  | 000                       |        |

|                  | No Branch                 |        |

| Branch Register: | 12H                       |        |

| Control:         | ООН                       |        |

| Data Field:      | ООН                       |        |

| Count:           | OlH (Write 2 bytes of OOH | bytes) |

SYSTEM ACTIVITY (t = 10.498 to 10.502ms)

AIC-010 NRZ output is 2 bytes of OOH. Host has sensed Branch Active and set Register 78 to 12H, setting up the next I.D. field write.

AIC-OlO STATE (t = 10.502ms)

| Current Address:<br>Next Address: | OEH               |               |            |

|-----------------------------------|-------------------|---------------|------------|

| Branch Control:                   | 000               | *             |            |

|                                   | No Branch         | •             |            |

| Branch Register:                  | 11H               |               |            |

| Control:                          | 80H (WG on)       |               |            |

| Data Field:                       | 4EH               |               |            |

| Count:                            | Set by host at in | nitialization | (14 bytes) |

|                                   |                   |               |            |

SYSTEM ACTIVITY (t = 10.502 to 10.524ms)

At this point the AIC-OlO is writing Gap 3, which is the same as when it was writing Gap 1. Following this, 12 bytes of OOH, the I.D. AM (Al FE) and the the I.D. field will be written. Then the Data AM and Data Field will be written. The sequence of writing I.D. and Data Fields will continue until the last sector is written. After the last sector, the host loads the Branch Register with 13H instead of 12H.

## AIC-010 STATE (t = ms)

| Current Address:                  | 13H                              |

|-----------------------------------|----------------------------------|

| Next Address:                     | 16H                              |

| Branch Control:                   | 000                              |

|                                   | No Branch                        |