## AIC1384

## **DDR Termination Regulator**

## **FEATURES**

- Source and Sink Current Capability

- Suspend To RAM Functionality

- Support DDR (1.25V<sub>TT</sub>) and DDR (0.9V<sub>TT</sub>) Requirements

- Low Output Voltage Offset, ±20mV

- High Accuracy Output Voltage at Full-Load

- Low External Component Count

- No external resistor required

- Current Limit protection

- Thermal Protection

- SOP-8 and SOP-8 Exposed Pad (Heat Sink) Package

#### **APPLICATIONS**

- Mother board

- Graphic cards

- DDR and DDR termination voltage

#### DESCRIPTION

The AIC1384 linear regulator is designed to deliver 1.5A continuous current and up to 3A peak transient currents for termination of DDR-SRAM. The AIC1384 contains a high-speed operational amplifier to supply superior load transient response. It also includes a  $V_{SENSE}$  to provide excellent load regulation and  $V_{REF}$  output as a reference for the chipset and DIMMs. The AIC1384 supply accurate  $V_{TT}$  and  $V_{REF}$  without external resistors that save PCB areas.

The AIC1384 also features an active low shutdown pin that provides Suspend To RAM (STR) functionality. The V<sub>TT</sub> will remain high impedance when in shutdown, but V<sub>REF</sub> will keep active. The advantage of power saving can be obtained through low 150 $\mu$ A (DDR ) quiescent current.

Built in current limiting in source and sink mode, with thermal shutdown provide maximal protection to the AIC1384 against fault conditions.

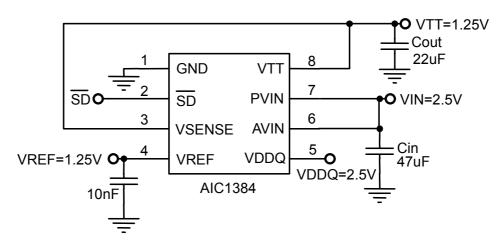

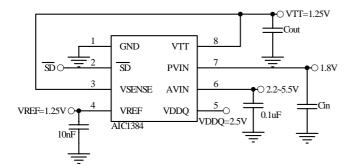

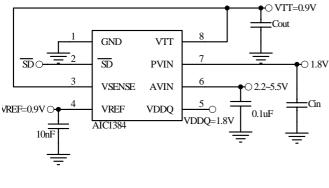

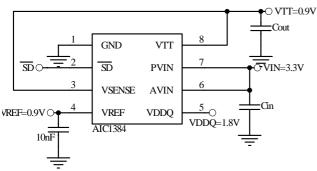

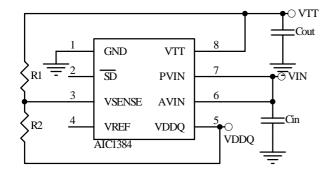

## **TYPICAL APPLICATION CIRCUIT**

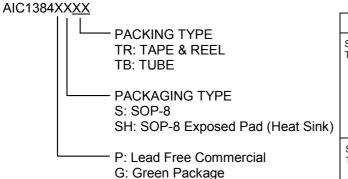

### ORDERING INFORMATION

→ In Lead Free SOP-8 Package & Taping & Reel Packing Type

## **ABSOLUTE MAXIMUM RATINGS**

| PVIN, AVIN, VDDQ, $\overline{SD}$ , V <sub>SENSE</sub> , V <sub>REF</sub> , V <sub>TT</sub> , to | GND                           | 6.0V         |  |  |

|--------------------------------------------------------------------------------------------------|-------------------------------|--------------|--|--|

| Operating Temperature Range                                                                      |                               | 40°C ∼ 85°C  |  |  |

| Junction Temperature                                                                             |                               | 125°C        |  |  |

| Storage Temperature Range                                                                        |                               | 65°C ~ 150°C |  |  |

| Lead Temperature (Soldering. 10 sec)                                                             |                               | 260°C        |  |  |

| Thermal Resistance Junction to Ambient, R $	heta_{JA}$ (Assume no ambient airflow, no heatsink)  |                               |              |  |  |

|                                                                                                  | SOP-8                         | 160°C /W     |  |  |

|                                                                                                  | SOP-8 Exposed Pad (Heat Sink) | 60°C /W      |  |  |

| Thermal Resistance Junction to Case, $\text{R}\theta_{\text{JC}}$                                | SOP-8                         | 40°C /W      |  |  |

|                                                                                                  | SOP-8 Exposed Pad (Heat Sink) | 16°C /W      |  |  |

Absolute Maximum Ratings are those values beyond which the life of a device may be Impaired.

### **TEST CIRCUIT**

Refer to TYPICAL APPLICATION CIRCUIT.

## **ELECTRICAL CHARACTERISTICS**

#### (AVIN=2.5V, PVIN=VDDQ=1.8V / 2.5V, T<sub>A</sub>=25°C, unless otherwise specified) (Note 1)

| PARAMETER                                   | CONDITIONS                                           | SYMBOL               | MIN   | ТҮР     | MAX   | UNITS |

|---------------------------------------------|------------------------------------------------------|----------------------|-------|---------|-------|-------|

| Input Voltage (DDD1/2)                      |                                                      | AVIN                 | 2.2   |         | 5.5   | V     |

| Input Voltage (DDR1/2)                      |                                                      | PVIN                 | 1.6   | 2.5/1.8 |       |       |

|                                             | VDDQ = 1.7V                                          |                      | 0.83  | 0.85    | 0.87  |       |

|                                             | VDDQ = 1.8V                                          | V <sub>REF</sub>     | 0.88  | 0.90    | 0.92  | V     |

|                                             | VDDQ = 1.9V                                          |                      | 0.93  | 0.95    | 0.97  |       |

| Reference Voltage                           | VDDQ = 2.3V                                          |                      | 1.127 | 1.15    | 1.177 | V     |

|                                             | VDDQ = 2.5V                                          | V <sub>REF</sub>     | 1.227 | 1.25    | 1.277 |       |

|                                             | VDDQ = 2.7V                                          |                      | 1.327 | 1.35    | 1.377 |       |

|                                             | I <sub>OUT</sub> = 0A, +0.9A, -0.9A                  |                      |       |         |       |       |

|                                             | VDDQ = 1.7V                                          | Ň                    | 0.81  | 0.85    | 0.89  | V     |

|                                             | VDDQ = 1.8V                                          | V <sub>TT</sub>      | 0.86  | 0.90    | 0.94  |       |

|                                             | VDDQ = 1.9V                                          |                      | 0.91  | 0.95    | 0.99  |       |

| V <sub>TT</sub> Output Voltage              | I <sub>OUT</sub> = 0A, +1.5A, -1.5A                  |                      |       |         |       |       |

|                                             | VDDQ = 2.3V                                          | Ň                    | 1.116 | 1.15    | 1.181 | V     |

|                                             | VDDQ = 2.5V                                          | V <sub>TT</sub>      | 1.216 | 1.25    | 1.281 |       |

|                                             | VDDQ = 2.7V                                          |                      | 1.316 | 1.35    | 1.381 |       |

| V <sub>TT</sub> Output Voltage Offset       | I <sub>OUT</sub> = 0A                                |                      | -20   |         | 20    |       |

| (for DDR I)                                 | I <sub>OUT</sub> =+1.5A/ -1.5A                       | V <sub>os</sub>      | -25   |         | 25    | mV    |

| V <sub>TT</sub> Output Voltage Offset       | I <sub>OUT</sub> = 0A                                |                      | -40   |         | 40    | mV    |

| (for DDR II)                                | I <sub>OUT</sub> =+0.9A/ -0.9A                       | V <sub>os</sub>      | -40   |         | 40    |       |

|                                             | VDDQ = 2.5V,                                         |                      |       | 0.5     |       | kΩ    |

|                                             | I <sub>REF</sub> = -30μA to +30μA                    | 7                    |       | 2.5     |       |       |

| V <sub>REF</sub> Output Impendence          | VDDQ = 1.8V,                                         | Z <sub>VREF</sub>    |       | 0.5     |       |       |

|                                             | I <sub>REF</sub> = -20μA to +20μA                    |                      |       | 2.5     |       |       |

| Current Limit                               | PVIN = 2.5V                                          |                      | 3.0   |         |       | A     |

|                                             | PVIN = 1.8V                                          | I <sub>IL</sub>      | 1.6   |         |       |       |

| Quiescent Current                           | I <sub>OUT</sub> = 0A                                | I <sub>Q-AVIN</sub>  |       | 320     | 500   | - μΑ  |

|                                             | SD = 0V                                              | I <sub>SD-AVIN</sub> |       |         | 150   |       |

| V <sub>SENSE</sub> Input Current            |                                                      | I <sub>SENSE</sub>   |       | 13      |       | nA    |

| V <sub>TT</sub> Leakage Current in Shutdown | $\overline{\text{SD}}$ = 0V, V <sub>TT</sub> = 1.25V | I <sub>LK-TT</sub>   |       |         | 10    | μA    |

## ELECTRICAL CHARACTERISTICS (Continued)

| PARAMETER                       | CONDITIONS | SYMBOL             | MIN | ТҮР | ΜΑΧ | UNITS |

|---------------------------------|------------|--------------------|-----|-----|-----|-------|

| Shutdown Leakage<br>Current     | SD = 0V    | I <sub>LK-SD</sub> |     | 2   | 5   | μA    |

| Shutdown Threshold              | Output ON  | V <sub>IH</sub>    | 1.9 |     |     | V     |

|                                 | Output OFF | V <sub>IL</sub>    |     |     | 0.8 |       |

| Thermal Shutdown<br>Temperature |            | T <sub>SD</sub>    |     | 165 |     | °C    |

| Thermal Shutdown<br>Hysteresis  |            |                    |     | 20  |     | °C    |

Note1: Specifications are production tested at T<sub>A</sub>=25°C. Specifications over the -40°C to 85°C operating temperature range are assured by design, characterization and correlation with Statistical Quality Controls (SQC).

Note 2:  $V_{\text{OS}}$  is the voltage measurement, which is defined as  $V_{\text{TT}}$  subtracted  $V_{\text{REF.}}$

Note 3: Load regulation and Current Limit are measured at constant junction temperature, by using pulse test with a short ON time.

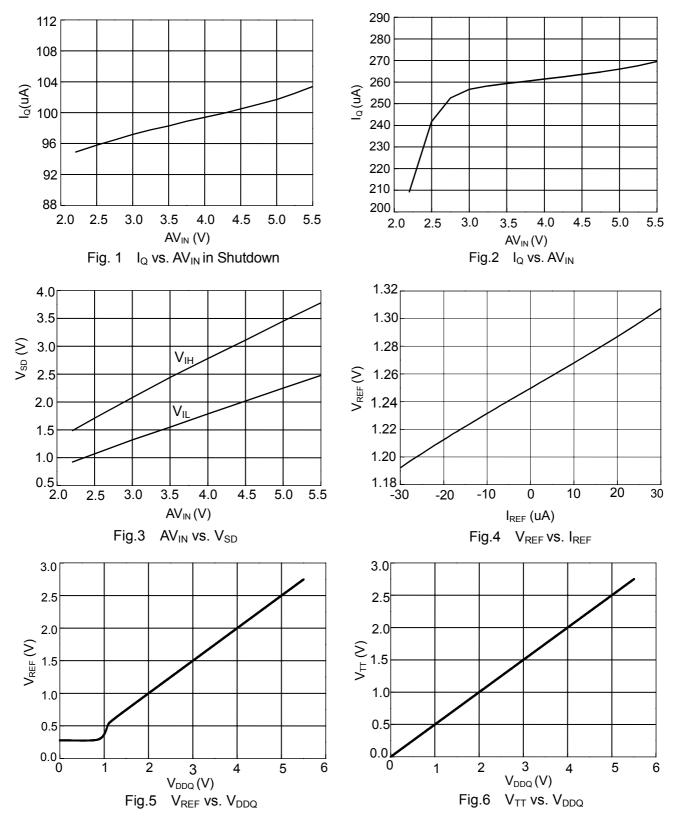

## **TYPICAL PERFORMANCE CHARACTERISTICS**

Daic\_

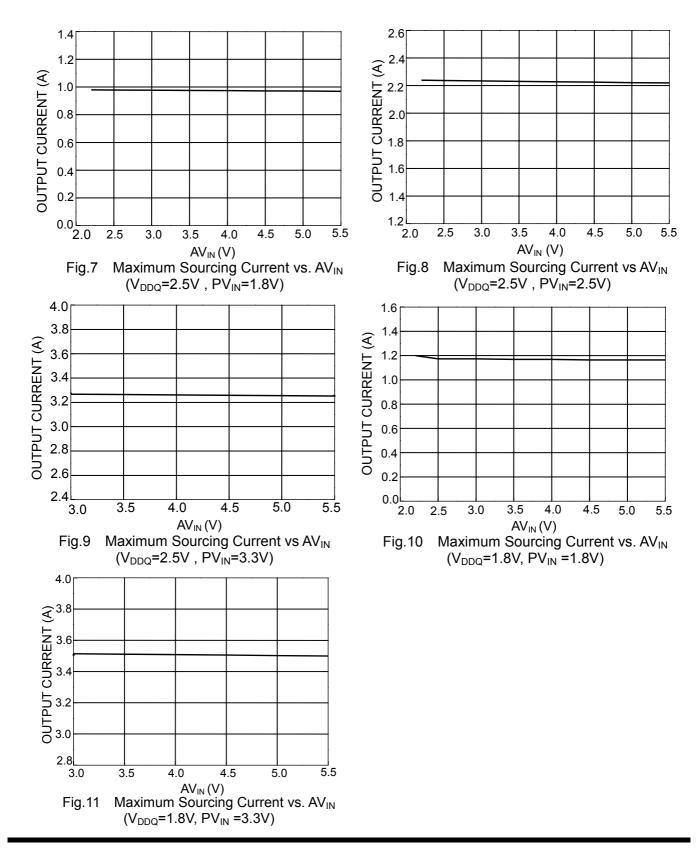

## **TYPICAL PERFORMANCE CHARACTERISTICS (Continued)**

) aic\_

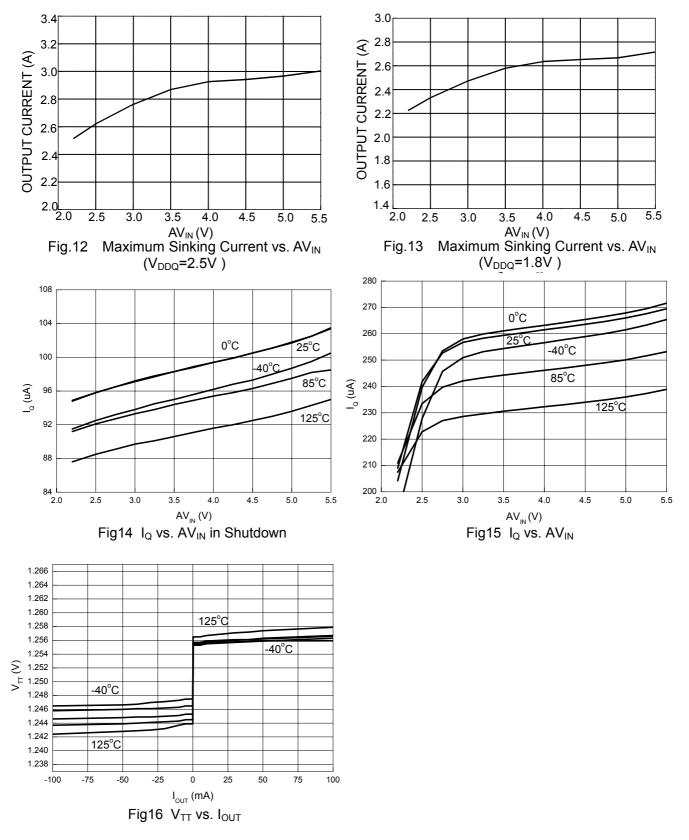

## **₫**Ŋ aic\_\_\_

## **TYPICAL PERFORMANCE CHARACTERISTICS (Continued)**

## **TYPICAL PERFORMANCE CHARACTERISTICS (Continued)**

) aic\_

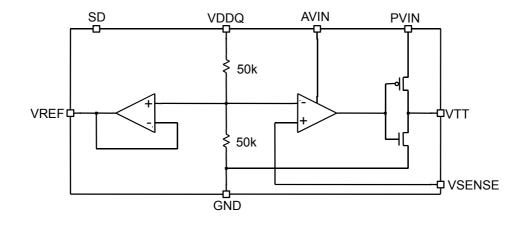

## BLOCK DIAGRAM

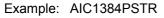

#### **PIN DESCRIPTION**

- Pin 1: GND Ground.

- Pin 2: SD Active low shutdown pin.

- Pin 3:  $V_{\text{SENSE}}$  Sense  $V_{\text{TT}}$  to improve load regulation.

- Pin 5: VDDQ Input voltage to internal reference voltage for regulating  $V_{TT}$ .

- Pin 6: AVIN Analog input voltage to supply internal control circuitry.

- Pin 8:  $V_{TT}$  Regulated output, equal to VDDQ/2.

- Heat Sink Recommended to Connect to GND.

## APPLICATION INFORMATION

aic

The AIC1384 linear termination regulator is designed to meet JEDEC requirements of DDR-SDRAM (DDR / ). The  $V_{TT}$  is able to deliver sinking and sourcing current while regulating the voltage equal to VDDQ/2. The output stage includes a sense function to maintain excellent load regulation to prevent shoot through. The power part has two distinct rails that split the internal analog circuitry from power output stage, which results in reducing internal power disspation.

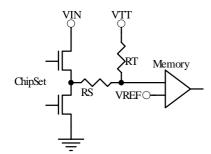

Series Stub Termination Logic (SSTL) was created to improve signal integrity of the data transmission across the memory bus. This termination scheme is necessary to prevent data error from signal reflections while transmitting at high frequencies encountered with DDR-SDRAM. The achievement of single parallel termination can be seen as below figure.

Between the chipset and memory are one RS series resistor and one RT termination resistor. Both RS and RT are 25 Ohms typically; they can be altered to scale the current requirements from the AIC1384.

#### AVIN and PVIN

AVIN and PVIN have the ability to work with separate supplies depending on the application. Higher PVIN will increase the maximum continuous output current resulting from output  $R_{DS-ON}$  limitations at voltages close to  $V_{TT}$ . Oppositely, the internal power dissipation will also

increase at high PVIN. Connect AVIN and PVIN together with 2.5V is a good compromise in SSTL-2 applications. This reduces the need for bypassing two supply pins separately. For the safe operation of the system; AVIN must always exceed or equal to PVIN.

#### VDDQ

VDDQ is used to make internal reference voltage for regulating V<sub>TT</sub>. And V<sub>TT</sub> will track VDDQ/2 precisely because of internal resistor divider. For SSTL-2 application, connect VDDQ to the 2.5V rail directly at the DIMM instead of AVIN and PVIN to achieve that reference voltage tracks the DDR memory rails accurately without a voltage drop from power lines.

#### V<sub>SENSE</sub>

The sense pin is used to improve remote load regulation. The termination resistors in most motherboards connect to  $V_{TT}$  with a long trace that will cause a significant voltage drop. The  $V_{SENSE}$  pin can improve that a lower termination voltage at one end of the bus than the other by connecting it to the middle of the bus. If a long  $V_{SENSE}$  trace is implemented close to the memory, noise pickup can be a problem in precise regulation of  $V_{TT}$ . A small  $0.1\mu$ F ceramic capacitor can be used for filtering noise.  $V_{SENSE}$  pin must still tie to  $V_{TT}$  if remote load regulation is not used.

#### V<sub>REF</sub>

$V_{REF}$  provides the buffered output of the internal VDDQ/2 reference voltage. It can be used to support the reference voltage for the Northbridge chipset and memory. The  $V_{REF}$  remains active during the shutdown state and thermal shutdown for the Suspend to RAM functionality. A bypass capacitor, located close to the  $V_{REF}$  pin, can be used to improve performance. Ranging from

# **⊘I**⊇ aic\_

$0.01 \mu F$  to  $0.1 \mu F$  of ceramic capacitor is recommended.

#### V<sub>TT</sub>

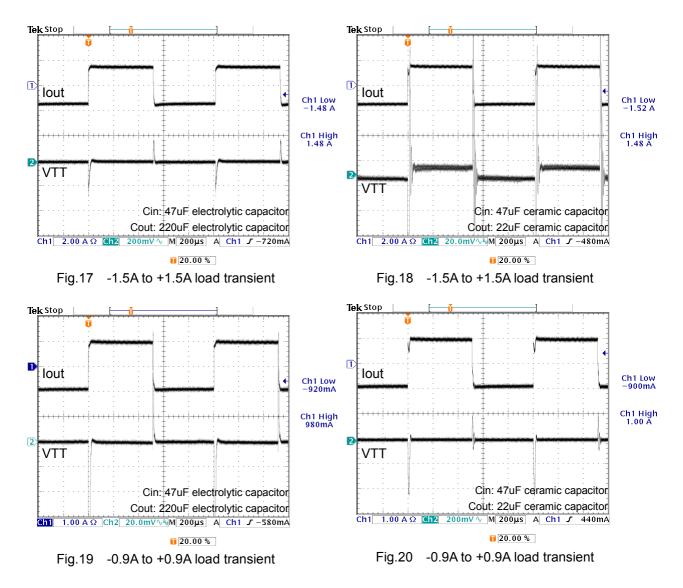

$V_{TT}$  is the regulated output that is used to terminate the bus resistor, which obtains the ability of sinking and sourcing current while regulating the output accurately to VDDQ/2. The AIC1384 is designed to deliver up to ±3A peak transient currents with excellent transient response. The output capacitor should be large enough to prevent an excessive voltage drop if a transient is expected to last above the maximum continuous current rating for a significant amount of time. AIC1384 is able to provide large transient output currents, yet it can't handle for long durations under all conditions that results from the standard packages are not able to dissipate the heat of the internal power loss. If large currents are required for longer durations, ensure that the maximum junction temperature is not exceeded.

#### **Capacitor Selection**

The input capacitor of AIC1384 is required for improved performance during large load transients to prevent the input rail from dropping.  $47\mu$ F aluminum electrolytic capacitors or ceramic capacitor is recommended. If AVIN and PVIN are separated, the  $47\mu$ F capacitor should be placed as close as possible to the PVIN. And AVIN can bypass a 0.1uF ceramic capacitor to prevent excessive noise.

220 $\mu$ F aluminum electrolytic capacitor is a recommendation for output capacitor to improve load transient response of V<sub>TT</sub>. And size above 22 $\mu$ F ceramic output capacitor is allowed to general used for obtain small profile. The value of ESR is determined by the acceptable maximum current spike and the output voltage droops.

#### Thermal Dissipation

The AIC1384 has a thermal-limiting circuitry, which is designed to protect the device against overload condition. For continuous load condition. maximum rating of junction temperature must not be exceeded. It is important to pay more attention in thermal resistance. It includes junction to case, junction to ambient. The maximum power dissipation of AIC1384 depends on the thermal resistance of its case and circuit board, the temperature difference between the die junction and ambient air, and the rate of airflow. The thermal resistance is greatly affected by the package used, the number of vias, the speed of airflow and the thickness of copper. When the IC mounting with good thermal conductivity is used, the junction temperature will be low even when large power dissipation applies. So the PCB mounting pad for GND pin of AIC1384 should provide maximum thermal conductivity to maintain low device temperature.

The power dissipation across the device is

$\mathsf{P} = \mathsf{I}_{\mathsf{OUT}} (\mathsf{V}_{\mathsf{IN}} - \mathsf{V}_{\mathsf{OUT}}).$

The maximum power dissipation is:

$$P_{MAX} = \frac{(T_{J-max} - T_A)}{R\theta_{JA}}$$

Where  $T_{J-max}$  is the maximum allowable junction temperature (125°C), and  $T_A$  is the ambient temperature suitable in application.

#### Layout Considerations

- Minimize high current ground loops. Place the ground of the device, the input capacitor, and the output capacitor together with short and wide connection.

- Connect the bottom-side pad (available in SOP-8 Exposed Pad) to a large ground plane. Use as much copper as possible to decrease the thermal resistance of the device.

- 3. A buried layer may be used as a heat spreader if the large copper around the

device is not available. Use vias to lead the heat into the buried layer.

- 4. The input capacitor should be placed as close as possible to the PVIN pin.

- 5. A bypass capacitor, located close to the  $V_{REF}$  pin, can be used to improve performance. Ranging from 0.01µF to 0.1µF

#### **APPLICATION EXAMPLES**

aic

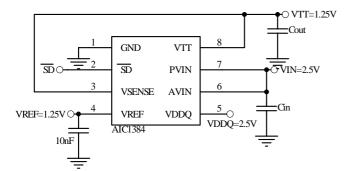

• DDR Application

of ceramic capacitor is recommended.

If long sense traces is used, the noise of V<sub>SENSE</sub> trace may occurs which from switching I/O signals. A 0.1uF ceramic capacitor connects to the V<sub>SENSE</sub> pin can be used to filter high frequency signal.

All the input rails connect to 2.5V rail is recommend for the SSTL-2 termination scheme application. The circuitry completes an optimal power dissipation and component count.

Connect the AIC1384 power rail to 3.3V to provide the maximum continuous output current if 1.8V and 2.5V rail are not available. Beware the junction temperature to exceed the maximum due to large current level. In this configuration AVIN will be limited to operation on the 3.3V or 5V rail results from PVIN can never exceed AVIN.

AVIN and PVIN have the ability to work with separate supplies. PVIN can be operated on a lower 1.8V rail and the AVIN can be connected to a higher rail. Although this circuitry can obtain better efficiency, but the maximum continuous current is reduced due to the lower rail voltage. Increasing the output capacitance can also help for large load transients.

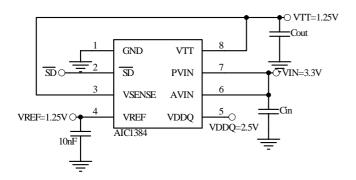

#### DDR Application

aic.

The circuit is recommended for DDR-II applications. The output stage is connected to the 1.8V rail and the AVIN pin can be connected to either a 3.3V or 5V rail.

Connect the power rail to 3.3V to provide a higher

continuous output current if 1.8V rail is not

available. Careful with the junction temperature

that may exceed the maximum due to the thermal

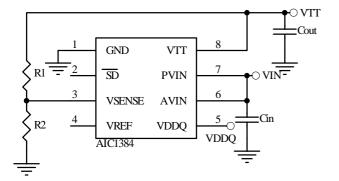

#### Level Shifting Application

dissipation increases with lower V<sub>TT</sub> output voltages. In this configuration PVIN will be limited to operation on the 3.3V rail. The AIC1384 is available to scale the output to any

voltage required. One method is to level shift the output above the internal reference voltage of VDDQ/2 by using two resistors from the  $V_{TT}$  to the  $V_{SENSE}$ . The correct voltage at VTT is

$V_{TT} = VDDQ/2 (1 + R1/R2)$

Another method is to level shift the output below the internal reference voltage of VDDQ/2 by using two resistors from the  $V_{SENSE}$  and VDDQ. The correct voltage at  $V_{TT}$  is

V<sub>TT</sub> = VDDQ/2 (1 - R1/R2)

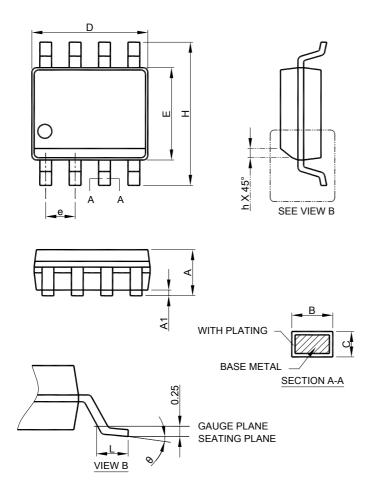

## PHYSICAL DIMENSIONS (unit: mm)

#### • SOP- 8

| S<br>Y      | SOP-8       |      |  |

|-------------|-------------|------|--|

| М           | MILLIMETERS |      |  |

| B<br>O<br>L | MIN.        | MAX. |  |

| А           | 1.35        | 1.75 |  |

| A1          | 0.10        | 0.25 |  |

| В           | 0.33        | 0.51 |  |

| С           | 0.19        | 0.25 |  |

| D           | 4.80        | 5.00 |  |

| E           | 3.80        | 4.00 |  |

| е           | 1.27 BSC    |      |  |

| Н           | 5.80        | 6.20 |  |

| h           | 0.25        | 0.50 |  |

| L           | 0.40        | 1.27 |  |

| θ           | 0°          | 8°   |  |

Note: 1. Refer to JEDEC MS-012AA.

- 2. Dimension "D" does not include mold flash, protrusions or gate burrs. Mold flash, protrusion or gate burrs shall not exceed 6 mil per side .

- 3. Dimension "E" does not include inter-lead flash or protrusions.

- 4. Controlling dimension is millimeter, converted inch dimensions are not necessarily exact.

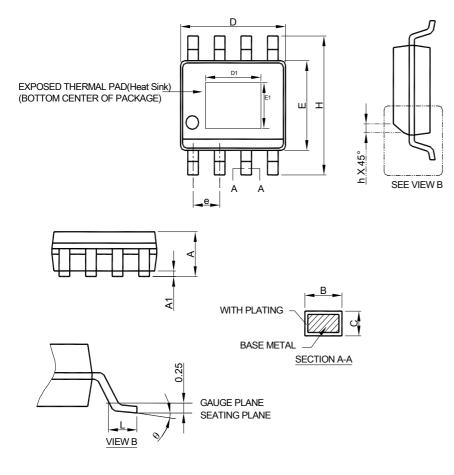

#### • SOP- 8 Exposed Pad (Heat Sink)

| S                     | SOP-8 Exposed Pad(Heat Sink) |      |  |  |  |

|-----------------------|------------------------------|------|--|--|--|

| S<br>Y<br>B<br>O<br>L | MILLIMETERS                  |      |  |  |  |

| 0<br>L                | MIN.                         | MAX. |  |  |  |

| А                     | 1.35                         | 1.75 |  |  |  |

| A1                    | 0.00                         | 0.15 |  |  |  |

| В                     | 0.31                         | 0.51 |  |  |  |

| С                     | 0.17                         | 0.25 |  |  |  |

| D                     | 4.80                         | 5.00 |  |  |  |

| Е                     | 3.80                         | 4.00 |  |  |  |

| е                     | 1.27 BSC                     |      |  |  |  |

| Н                     | 5.80                         | 6.20 |  |  |  |

| h                     | 0.25                         | 0.50 |  |  |  |

| L                     | 0.40                         | 1.27 |  |  |  |

| q                     | 0°                           | 8°   |  |  |  |

| D1                    | 1.5                          | 3.5  |  |  |  |

| E1                    | 1.0                          | 2.55 |  |  |  |

- Note : 1. Refer to JEDEC MS-012E.

- Dimension "D" does not include mold flash, protrusions or gate burrs. Mold flash, protrusion or gate burrs shall not exceed 6 mil per side.

- 3. Dimension "E" does not include inter-lead flash or protrusions.

- 4. Controlling dimension is millimeter, converted inch dimensions are not necessarily exact.

#### Note:

Information provided by AIC is believed to be accurate and reliable. However, we cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in an AIC product; nor for any infringement of patents or other rights of third parties that may result from its use. We reserve the right to change the circuitry and specifications without notice.

Life Support Policy: AIC does not authorize any AIC product for use in life support devices and/or systems. Life support devices or systems are devices or systems which, (I) are intended for surgical implant into the body or (ii) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.