# AK1573/AK1573B/AK1573C

# Frequency Synthesizer with Integrated VCO

#### 1. **General Description**

AK1573 is the Integer-N frequency synthesizer with integrated VCO (Voltage Controlled Oscillator). It is composed of programmable charge pump, reference divider, programmable divider, dual modulus prescaler (P / P + 1). With the feature of high-performance, low noise and small size, it can be used as a local signal source of a variety of frequency conversion.

By combining with an external loop filter, AK1573 form a complete Phase Locked Loop. Access to the register is controlled by the serial interface of the 3-wire and Power supply voltage is 2.7V to 3.3V.

#### 2. **Features**

Normalized Phase Noise -223dBc/Hz

Low Noise Integrated VCO -86dBc/Hz@10kHz -112dBc/Hz@100kHz

Operating Supply Voltage 2.7 to 3.3V

Low Current Comsumption@0dBm Output

> AK1573 43mA AK1573B 44mA AK1573C 46mA

Programmable to Divide by 1, 2, 4, 8, 16, 32, 64 -12dBm to +6dBm

Programmable Output Power

Fast Lock-up Function

Analog or Digital Lock Detect Function

**Output Mute Function**

Package 24pin QFN (0.5mm pitch 4x4mm)

**Operating Temperature Range** -40 °C to 85 °C

Frequency Coverage Options

|                     | AK1573       | AK1573B      | AK1573C           |

|---------------------|--------------|--------------|-------------------|

| VCO Frequency [MHz] | 1480 to 2240 | 1728 to 2600 | 2100 to 3000      |

| Divide by 1         | 1480 to 2240 | 1728 to 2600 | 2100 to 3000      |

| Divide by 2         | 740 to 1120  | 864 to 1300  | 1050 to 1500      |

| Divide by 4         | 370 to 560   | 432 to 650   | 525 to 750        |

| Divide by 8         | 185 to 280   | 216 to 325   | 262.5 to 375      |

| Divide by 16        | 92.5 to 140  | 108 to 162.5 | 131.25 to 187.5   |

| Divide by 32        | 46.25 to 70  | 54 to 81.25  | 65.625 to 93.75   |

| Divide by 64        | 30 to 35     | 30 to 40.625 | 32.8125 to 46.875 |

### 3. Ordering Guide

- AK1573

- AK1573B

- AK1573B

- AK1573C

- AKD1573

- AKD1573

- AKD1573B

- AKD1573B

- AKD1573B

- AKD1573B

- AKD1573B

- AK1573B

- AK1

- AKD1573B AK1573B Evaluation Board - AKD1573C AK1573C Evaluation Board

### 4. Applications

- □ Public safety and Community/Emergency Wireless System

- □ Wireless applications

- □ Cellular BTS

### 5. Table of Contents

| 1. G | General Description               | 1  |

|------|-----------------------------------|----|

| 2. F | eatures                           | 1  |

| 3. C | Ordering Guide                    | 2  |

| 4. A | pplications                       | 2  |

| 5. T | able of Contents                  | 3  |

| 6. B | Block Diagram and Functions       | 4  |

| 6.1. | Block Diagram                     | 4  |

| 6.2. | Functions                         | 4  |

| 7. P | Pin Configurations and Functions  | 5  |

| 8. A | bsolute Maximum Ratings           | 6  |

| 9. R | Recommended Operating Conditions  | 7  |

| 10.  | Electrical Characteristics        |    |

| 10.1 | 1. Digital DC Characteristics     | 7  |

| 10.2 | 2. Serial Interface Timing        | 7  |

| 10.3 | 3. Analog Circuit Characteristics | 8  |

| 10.4 | 4. Loop filter                    | 10 |

| 11.  | Typical Characteristics           | 11 |

| 12.  | Register Map                      | 21 |

| 13.  | Function Descriptions             | 28 |

| 13.1 | 1. Lock detect                    | 28 |

| 13.2 | 2. Frequency Setting              | 30 |

| 13.3 | 3. Fast Lock-up mode              | 32 |

| 13.4 | 4. VCO                            | 33 |

| 14.  | Power on sequence                 | 34 |

| 15.  | Recommended External Circuits     | 35 |

| 16.  | Application Note                  | 36 |

| 17.  | Interface circuit                 | 37 |

| 18.  | Package                           | 39 |

| 18.1 | 1. Outline Dimensions             | 39 |

| 18.2 | 2. Marking                        | 40 |

| 19   | Revision History                  | 41 |

### 6. Block Diagram and Functions

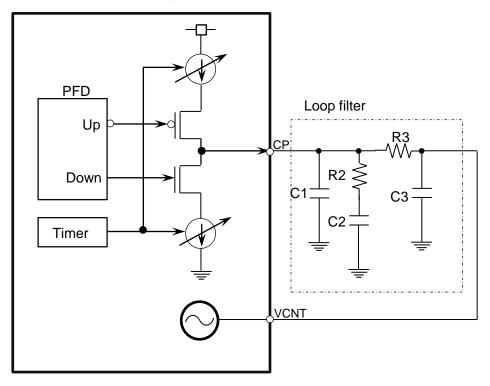

### 6.1. Block Diagram

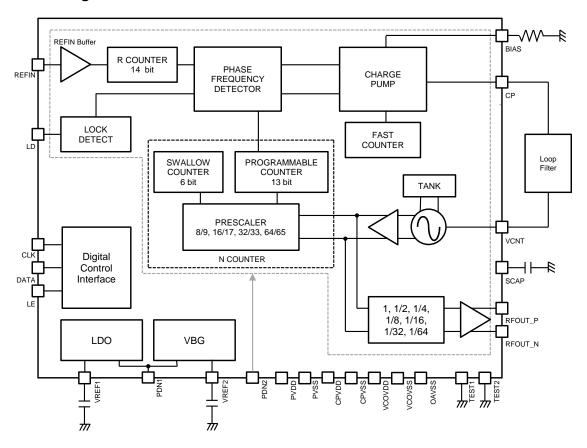

Figure.1 Block Diagram

#### 6.2. Functions

| Block                                  | Function                                                                                                                                               |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| N counter                              | It is composed of prescaler, Swallow Counter and Programmable Counter. VCO output signal is divided by N and passed to phase frequency detector (PFD). |

| VCO Divider                            | It divides VCO output signal and passes it to output buffer. Dividing ratio of 1, 2, 4, 8, 16, 32 and 64 can be selected.                              |

| R counter                              | It divides a reference signal by R and passes it to phase frequency detector (PFD).                                                                    |

| VCO<br>(Voltage Controlled Oscillator) | It generates a signal of the frequency corresponding to a voltage inputted to VCNT pin.                                                                |

| PFD(Phase Frequency Detector)          | It outputs a signal corresponding to phase difference between N counter and R counter.                                                                 |

| Charge Pump                            | Sweep or pull-in a current corresponding to a signal from PFD.                                                                                         |

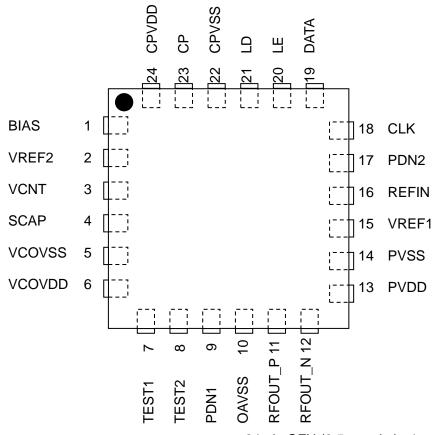

### 7. Pin Configurations and Functions

| No. | Pin Name | I/O | Pin function                                                                                                              | Power<br>Down | Description                              |

|-----|----------|-----|---------------------------------------------------------------------------------------------------------------------------|---------------|------------------------------------------|

| 1   | BIAS     | Al  | Charge pump current setting pin                                                                                           |               | Connect a 27kΩ resistor to the ground    |

| 2   | VREF2    | АО  | Internal reference voltage output pin                                                                                     | "L"           | Connect a 470nF capacitor to the ground  |

| 3   | VCNT     | Al  | VCO control voltage input pin                                                                                             |               |                                          |

| 4   | SCAP     | AO  | VCO Bias stabilizing connection pin                                                                                       | "L"           | Connect a 100pF capacitor to the ground  |

| 5   | VCOVSS   | G   | Ground of VCO block                                                                                                       |               |                                          |

| 6   | VCOVDD   | Р   | Power supply of VCO block                                                                                                 |               |                                          |

| 7   | TEST1    | DI  | TEST1 pin Connect to the ground                                                                                           |               | Pull Down<br>Schmitt trigger input       |

| 8   | TEST2    | DI  | TEST2 pin Connect to the ground                                                                                           |               | Pull Down<br>Schmitt trigger input       |

| 9   | PDN1     | DI  | Power down 1 pin. When PDN1 = "L", device is powered down and the registers are not retained.                             |               | Schmitt trigger input                    |

| 10  | OAVSS    | G   | Ground of Local buffer                                                                                                    |               |                                          |

| 11  | RFOUT_P  | AO  | Local signal output pin                                                                                                   |               | Open collector                           |

| 12  | RFOUT_N  | AO  | Local signal complementary output pin                                                                                     |               | Connect a inductor and a register to VDD |

| 13  | PVDD     | Р   | Power supply of Prescaler and LDO                                                                                         |               |                                          |

| 14  | PVSS     | G   | Ground of Prescaler and LDO                                                                                               |               |                                          |

| 15  | VREF1    | AO  | Output pin of LDO                                                                                                         | "L"           | Connect a 220nF capacitor to the ground  |

| 16  | REFIN    | DI  | Reference signal input pin                                                                                                |               |                                          |

| 17  | PDN2     | DI  | Power down 2 pin. When PDN2<br>= "L", all blocks except LDO and<br>VBG are powered down but the<br>registers are retained |               | Schmitt trigger input                    |

| 18  | CLK      | DI  | Serial clock input pin.                                                                                                   |               | Schmitt trigger input                    |

| 19  | DATA     | DI  | Serial data input pin.                                                                                                    |               | Schmitt trigger input                    |

| 20  | LE       | DI  | Load enable input pin.                                                                                                    |               |                                          |

| 21  | LD       | DO  | Lock detect output pin                                                                                                    | "L"           |                                          |

| 22  | CVPSS    | G   | Ground of Charge Pump                                                                                                     |               |                                          |

| 23  | CP       | AO  | CP signal output pin                                                                                                      | Tri-State     |                                          |

| 24  | CPVDD    | Р   | Power supply of Charge Pump                                                                                               |               |                                          |

AI: Analog input pin

AO: Analog output pin

AIO: Analog I/O pin

DI: Digital input pin DO: Digital output pin P: Power supply pin G: Ground pin

<sup>\* &</sup>quot;Power Down" means the state in which power supply is applied and PDN1 / PDN2 pins = "L".

<sup>\*</sup> The exposed pad at the center of the backside should be connected to the ground

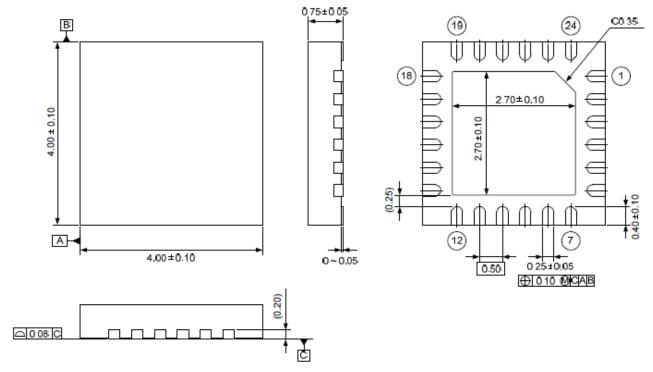

24-pin QFN (0.5mm pitch, 4mm × 4mm)

Figure 2 Package pin layout (Top view)

#### 8. Absolute Maximum Ratings

| Parameter             | Symbol | Min.    | Max.    | Unit | Description |

|-----------------------|--------|---------|---------|------|-------------|

| Supply Voltage        | VDD    | -0.3    | 3.6     | V    | * 1, 2      |

| Ground Level          | VSS    | 0       | 0       | V    | * 3         |

| Analog input voltage  | VAIN   | VSS-0.3 | VDD+0.3 | V    | * 1, 4, 6   |

| Digital input voltage | VDIN   | VSS-0.3 | VDD+0.3 | V    | * 1, 5, 6   |

| Input current         | IIN    | -10     | 10      | mA   |             |

| Storage Temperature   | Tstg   | -55     | 125     | °C   |             |

#### Note

- \* 1. All voltage reference ground level: 0V

- \* 2. Applied to the VCOVDD / PVDD / CPVDD pins

- \* 3. Applied to the CPVSS / PVSS / VCOVSS / OAVSS pins

- \* 4. Applied to the VCNT / REFIN pins

- \* 5. Applied to the CLK / DATA / LE / PDN1 / PDN2 / TEST1 / TEST2 pins

- \* 6. The maximum value must not exceed the absolute maximum rating of 3.6V.

Exceeding these maximum ratings may result in damage to the AK1573. Normal operation is not guaranteed at these extremes.

## 9. Recommended Operating Conditions

| Parameter                | Symbol | Min. | Тур. | Max. | Unit | Description                               |

|--------------------------|--------|------|------|------|------|-------------------------------------------|

| Operating<br>Temperature | Та     | -40  |      | 85   | °C   |                                           |

| Supply<br>Voltage        | VDD    | 2.7  | 3.0  | 3.3  | V    | Applied to the VCOVDD / PVDD / CPVDD pins |

#### 10. Electrical Characteristics

10.1. Digital DC Characteristics

| Parameter                  | Symbol | Conditions            | Min.    | Тур. | Max.    | Unit | Description |

|----------------------------|--------|-----------------------|---------|------|---------|------|-------------|

| High level input voltage   | Vih    |                       | 0.8×VDD |      |         | V    | * 1.        |

| Low level input voltage    | Vil    |                       |         |      | 0.2×VDD | V    | * 1.        |

| High level input current 1 | lih1   | Vih = VDD=3.3V        | -1      |      | 1       | μΑ   | * 2         |

| High level input current 2 | lih2   | Vih = VDD=3.3V        | 16.5    | 33   | 66      | μΑ   | * 3         |

| Low level input current    | lil    | Vil = 0V,<br>VDD=3.3V | -1      |      | 1       | μΑ   | * 1         |

| High level output voltage  | Voh    | Ioh = -500μA          | VDD-0.4 |      |         | V    | * 4         |

| Low level output voltage   | Vol    | IoI = 500μA           |         |      | 0.4     | V    | * 4         |

#### Note

- \* 1. Applied to the CLK / DATA / LE / PDN1 / PDN2 pins

- \* 2. Applied to the CLK / DATA / LE / PDN1 / PDN2 pins

- \* 3. Applied to the TEST1 / TEST2 pins

- \* 4. Applied to the LD pin

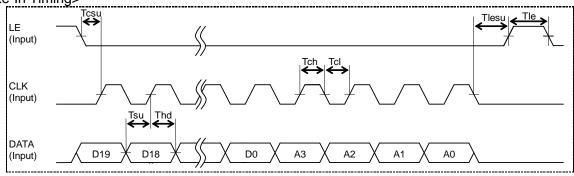

### 10.2. Serial Interface Timing

<Write-In Timing>

Figure.3 Serial Interface Timing

| Parameter               | Symbol | Min. | Тур. | Max. | Unit | Description |

|-------------------------|--------|------|------|------|------|-------------|

| Clock L level hold time | Tcl    | 25   |      |      | ns   |             |

| Clock H level hold time | Tch    | 25   |      |      | ns   |             |

| Clock setup time        | Tcsu   | 10   |      |      | ns   |             |

| Data setup time         | Tsu    | 10   |      |      | ns   |             |

| Data hold time          | Thd    | 10   |      |      | ns   |             |

| LE setup time           | Tlesu  | 10   |      |      | ns   |             |

| LE pulse width          | Tle    | 25   |      |      | ns   |             |

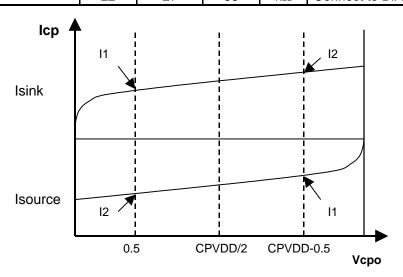

#### 10.3. Analog Circuit Characteristics

VDD=2.7 to 3.3V, -40°C<Ta<85°C, BIAS resistance =27k $\Omega$  unless otherwise specified.

The exposed pad at the center of the backside should be connected to the ground

| Paramete                                                       | er            | Min.     | Тур.         | Max.     | Unit                                               | Description                                        |

|----------------------------------------------------------------|---------------|----------|--------------|----------|----------------------------------------------------|----------------------------------------------------|

|                                                                |               |          | REFIN        |          |                                                    |                                                    |

| Input sensitivity                                              |               | 0.4      |              | VDD      | Vpp                                                | REFIN frequency < 200MHz                           |

|                                                                |               | 0.4      |              | 2        | Vpp                                                | REFIN frequency ≥ 200MHz                           |

| Input Frequency Ran                                            |               | 10       |              | 300      | MHz                                                |                                                    |

| Maximum available p                                            | rescaler      |          |              | 300      | MHz                                                | Design guarantee value                             |

| output Frequency                                               |               | Dhaca E  | requency De  | toctor/P | ED)                                                |                                                    |

| PFD Frequency                                                  |               | riiase r | requericy De | 104      | MHz                                                | Docian guarantos valus                             |

| PFD Flequency                                                  |               |          | Charge Pur   |          | IVIITZ                                             | Design guarantee value                             |

| Maximum Charga Du                                              | mp ourrent    |          | 2800         | пр       |                                                    |                                                    |

| Maximum Charge Pu                                              |               |          |              |          | μA                                                 |                                                    |

| Minimum Charge pur                                             | np current    |          | 350          |          | μA                                                 | To 0500 Vene VDD / 2                               |

| Icp TRI-STATE leak                                             |               |          | 1            |          | nA                                                 | Ta = 25°C, Vcpo = VDD / 2<br>Vcpo : CP pin voltage |

| Sink / Source current                                          |               | 1        | 10           | %        | Vcpo = VDD / 2, Ta = 25°C<br>Vcpo : CP pin voltage |                                                    |

| Icp vs. Vcpo * 2                                               |               | 3        | 15           | %        | 0.5 ≤ Vcpo ≤ VDD - 0.5<br>Ta = 25°C                |                                                    |

|                                                                |               |          | VCO          |          |                                                    |                                                    |

|                                                                |               | 1480     |              | 2240     | MHz                                                | AK1573                                             |

| Operating Frequency                                            | Range         | 1728     |              | 2600     | MHz                                                | AK1573B                                            |

|                                                                | _             | 2100     |              | 3000     | MHz                                                | AK1573C                                            |

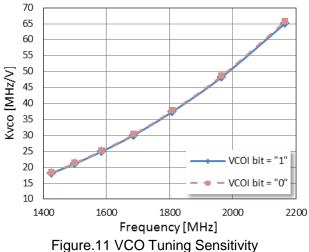

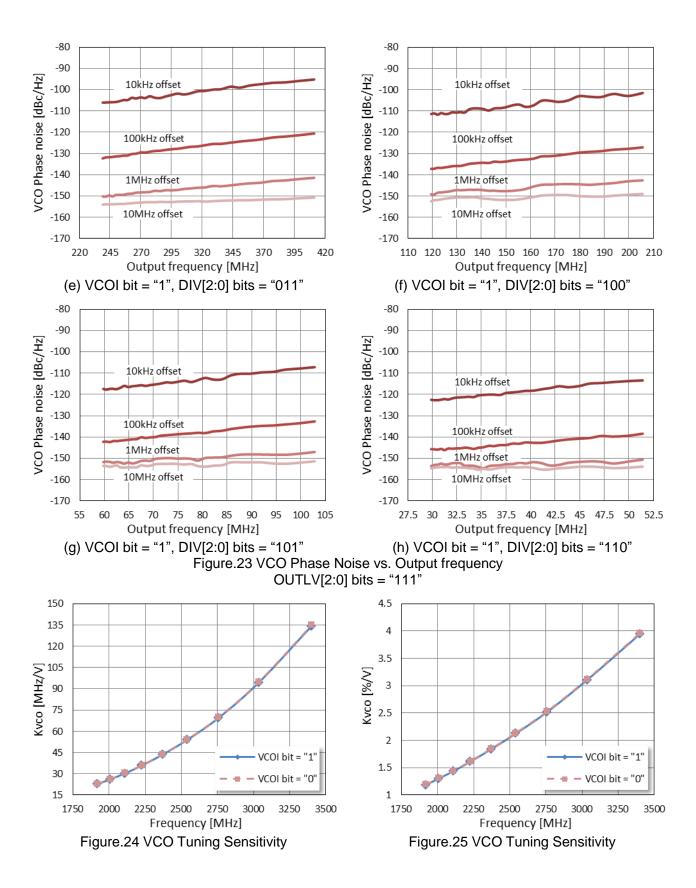

| VCO tuning Sensitivit                                          | :y            |          | fvco×0.02    |          | MHz/V                                              | fvco: Oscillation Frequency                        |

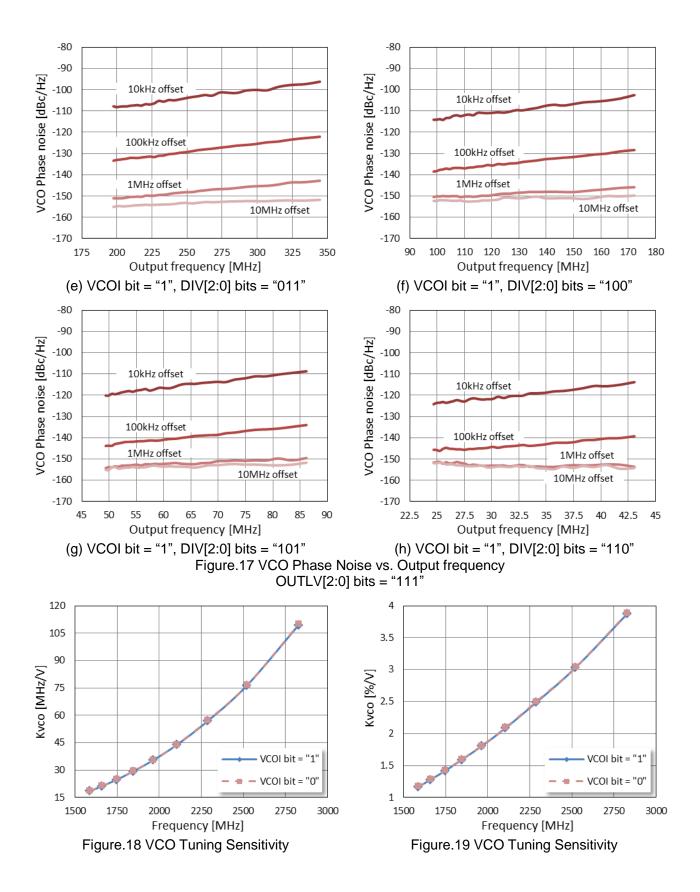

| Phase Noise                                                    | 10kHz offset  |          | -86          |          | dBc/Hz                                             | VCOI bit = "1"                                     |

| <ul><li>@ 1.6GHz (AK1573)</li><li>@ 1.8GHz (AK1573B)</li></ul> | 100kHz offset |          | -112         |          | dBc/Hz                                             | VCOI bit = "1"                                     |

| @ 2.1GHz (AK1573C)                                             | 1MHz offset   |          | -133         |          | dBc/Hz                                             | VCOI bit = "1"                                     |

| OUTLV[2:0] bits ≥ "011"                                        | 10MHz offset  |          | -151         |          | dBc/Hz                                             | VCOI bit = "1"                                     |

| Normalized Phase No                                            | oise          |          | -223         |          | dBc/Hz                                             | Note 3                                             |

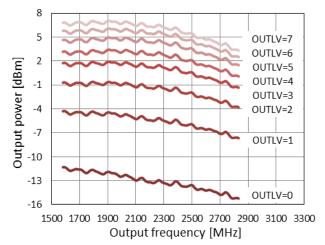

|                                                                |               |          | Output Buff  | er       |                                                    |                                                    |

|                                                                |               |          | 6            |          | dBm                                                | OUTLV[2:0] bits = "111"                            |

| OUTDUT Davier @40                                              | 21.1-         |          | 3            |          | dBm                                                | OUTLV[2:0] bits = "101"                            |

| OUTPUT Power @10                                               | <b>5</b> □∠   |          | 1            |          | dBm                                                | OUTLV[2:0] bits = "011"                            |

|                                                                |               |          | -5           |          | dBm                                                | OUTLV[2:0] bits = "001"                            |

| Output Frequency                                               |               | 30       |              |          | MHz                                                | Design guarantee value                             |

|                                                                |               |          | Regulator    | •        |                                                    |                                                    |

| VREF1 start-up time                                            |               |          |              | 10       | ms                                                 |                                                    |

#### Note

- \* 1. Sink/Source current mismatch :  $[(||sink|-||source|)/{(||sink|+||source|)/2}]$  \* 100 [%]

- \* 2. lcp v.s.Vcpo : [{1/2\*(|I1|-|I2|)}/{1/2\*(|I1|+|I2|)}]\*100 [%]

- \* 3. Measured in-band phase noise with the loop locked. Normalized Phase Noise is calculated from following equation. REFIN frequency = 120MHz, F<sub>PFD</sub> = 10MHz.

$(PN_{total} = PN_{synth} -10 \text{ Log } F_{PFD} - 20 \text{ Log } N)$  $PN_{total} : Normalized Phase Noise$

PN<sub>total</sub>: Normalized Phase Noise PN<sub>svnth</sub>: In-band Phase Noise

F<sub>PFD</sub>: PFD Frequency

| Parameter                                                  | Min. | Тур.         | Max.        | Unit  | Description                                                                |  |  |  |  |

|------------------------------------------------------------|------|--------------|-------------|-------|----------------------------------------------------------------------------|--|--|--|--|

|                                                            | C    | Current Co   | nsumptio    | n     |                                                                            |  |  |  |  |

| IDD1                                                       |      |              | 10          | μΑ    | PDN1 pin = PDN2 pin = "L"<br>(Full power down)                             |  |  |  |  |

| IDD2 @1.6GHz (AK1573)                                      | •    | •            | •           | •     |                                                                            |  |  |  |  |

| @ OUTLV[2:0] bits = "001"<br>VCOI bits = "0"               |      | 33           |             |       |                                                                            |  |  |  |  |

| @ OUTLV[2:0] bits = "011"<br>VCOI bits = "0"               |      | 43           |             | А     |                                                                            |  |  |  |  |

| @ OUTLV[2:0] bits = "111"<br>VCOI bits = "0"               |      | 62           |             | mA    |                                                                            |  |  |  |  |

| @ OUTLV[2:0] bits = "111"<br>VCOI bits = "1"               |      | 66           | 93          |       |                                                                            |  |  |  |  |

| IDD2 @1.8GHz (AK1573B)                                     |      |              |             |       |                                                                            |  |  |  |  |

| @ OUTLV[2:0] bits = "001"<br>VCOI bits = "0"               |      | 34           |             |       | DDN4 nin DDN2 nin "H"                                                      |  |  |  |  |

| @ OUTLV[2:0] bits = "011"<br>VCOI bits = "0"               |      | 44           |             | mA    | PDN1 pin = PDN2 pin = "H"<br>DIV[2:0] bits = "000"                         |  |  |  |  |

| @ OUTLV[2:0] bits = "111"<br>VCOI bits = "0"               |      | 62           |             | IIIA  | PRE[1:0] bits = "00"                                                       |  |  |  |  |

| @ OUTLV[2:0] bits = "111"<br>VCOI bits = "1"               |      | 66           | 93          |       |                                                                            |  |  |  |  |

| IDD2 @2.1GHz (AK1573C)                                     |      |              |             |       |                                                                            |  |  |  |  |

| @ OUTLV[2:0] bits = "001"<br>VCOI bits = "0"               |      | 37           |             |       |                                                                            |  |  |  |  |

| @ OUTLV[2:0] bits = "011"<br>VCOI bits = "0"               |      | 46           |             | Λ     |                                                                            |  |  |  |  |

| @ OUTLV[2:0] bits = "111"<br>VCOI bits = "0"               |      | 64           |             | mA    |                                                                            |  |  |  |  |

| @ OUTLV[2:0] bits = "111"<br>VCOI bits = "1"               |      | 68           | 93          |       |                                                                            |  |  |  |  |

| IDD3                                                       |      |              |             |       |                                                                            |  |  |  |  |

| @1.6GHz (AK1573)<br>@1.8GHz (AK1573B)<br>@2.1GHz (AK1573C) |      | 75           | 105         | mA    | PDN1 pin = PDN2 pin = "H"<br>DIV[2:0] bits ≠ "000"<br>PRE[1:0] bits = "00" |  |  |  |  |

| DIV[2:0} bits ≥ "100"                                      |      |              |             |       | [ 0 ] 5                                                                    |  |  |  |  |

| IDD4                                                       |      | 0.5          | 1           | mA    | PDN1 pin = "H", PDN2 pin = "L" (power down except VBG / LDO)               |  |  |  |  |

|                                                            | CP c | urrent adjus | sting resis | tance |                                                                            |  |  |  |  |

| BIAS resistance                                            | 22   | 27           | 33          | kΩ    | Connect to BIAS pin                                                        |  |  |  |  |

Figure.4 Charge Pump Characteristics – Voltage vs Current

### 10.4. Loop filter

Figure.5 shows loop filter topology used to evaluate AK1573, AK1573B and AK1573C.

Figure.5 Loop Filter Schematic

### 11. Typical Characteristics

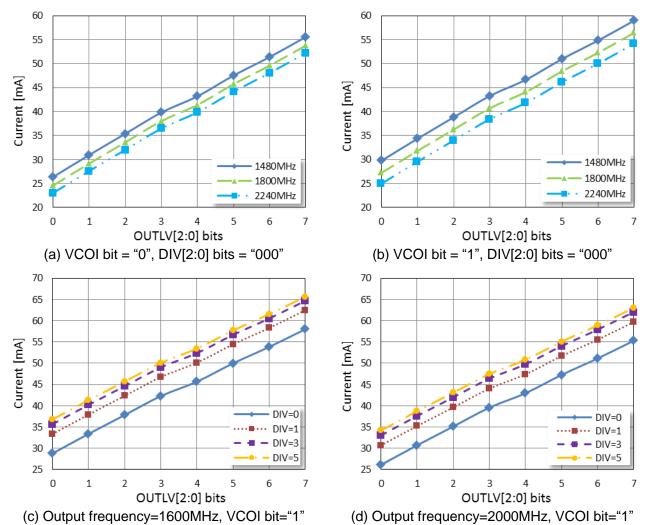

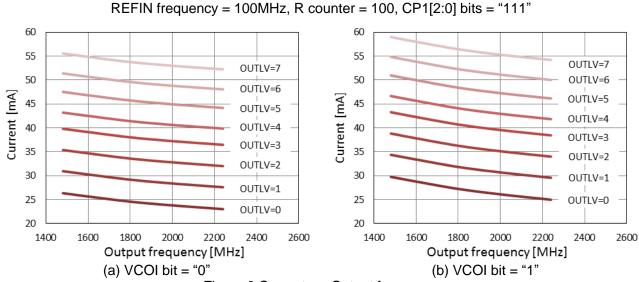

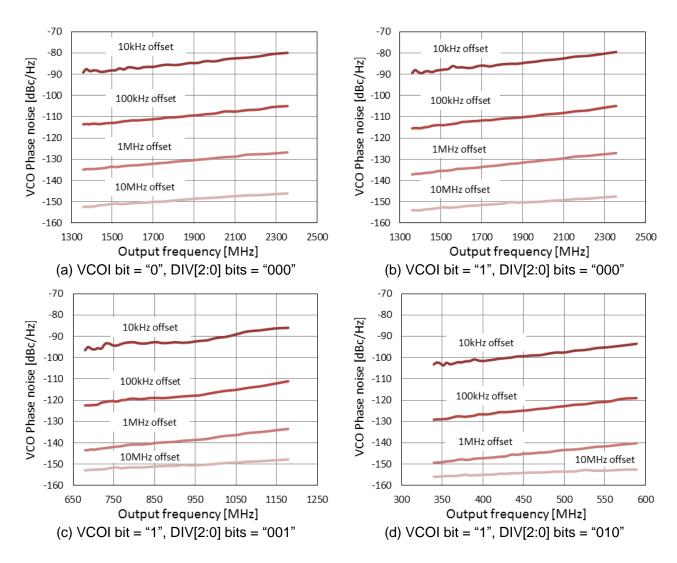

VDD=3.0V, Ta=25°C, BIAS resistance =27k $\Omega$ .

#### 1. Analog Characteristics

#### AK1573

Figure.6 Output power vs. Output frequency

Figure.7 Current vs. OUTLV[2:0] bits

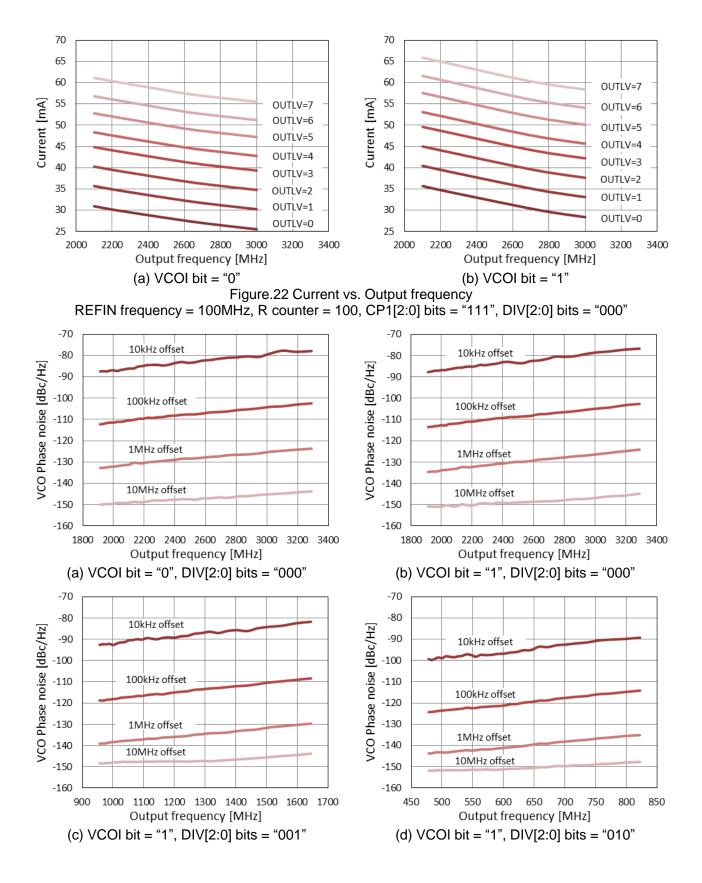

Figure.8 Current vs. Output frequency REFIN frequency = 100MHz, R counter = 100, CP1[2:0] bits = "111", DIV[2:0] bits = "000"

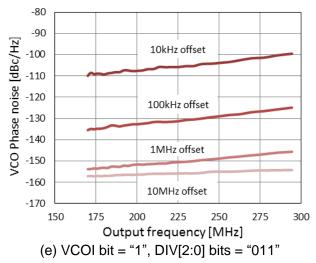

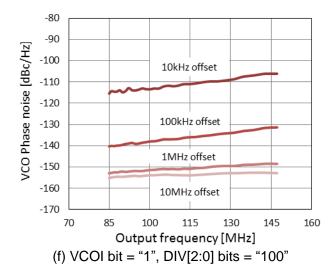

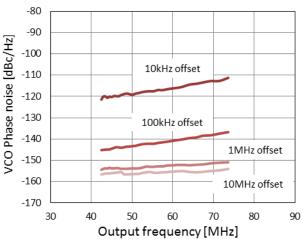

(g) VCOI bit = "1", DIV[2:0] bits = "101"

Figure.9 VCO Phase Noise vs. Output frequency

OUTLV[2:0] bits = "111"

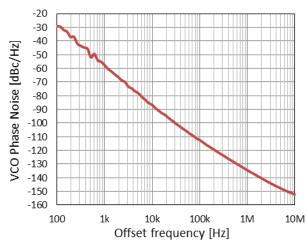

Figure.10 VCO Phase Noise vs. Offset frequency Output frequency = 1602.8MHz, VCOI bit = "1", OUTLV[2:0] bits = "111"

(a) Output frequency = 1500MHz

(c) Output frequency = 2100MHz

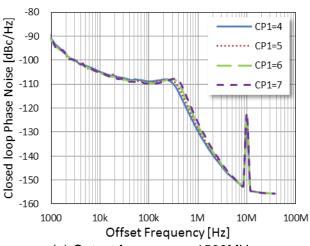

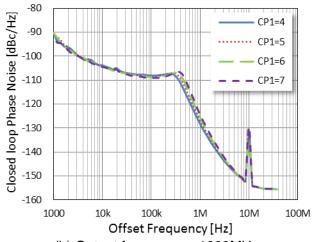

Figure.13 Closed loop Phase Noise REFIN frequency = 120MHz, R counter = 12, Prescaler = 8/9 Loop Filter : C1 = 33pF, C2 = 1500pF, C3 = N/A, R2 =  $10k\Omega$ , R3 =  $0\Omega$

Figure.12 VCO Tuning Sensitivity

(b) Output frequency = 1600MHz

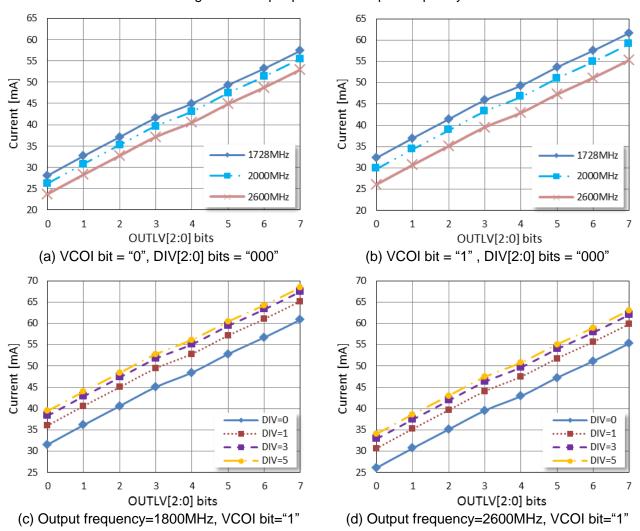

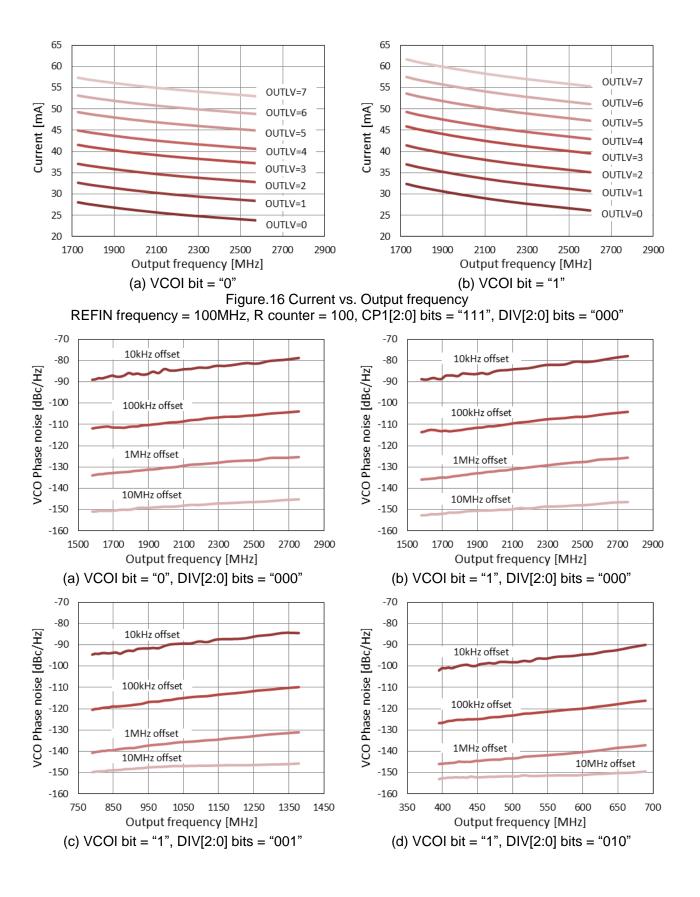

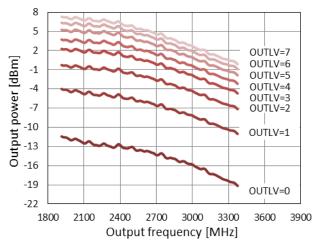

#### **AK1573B**

Figure.14 Output power vs. Output frequency

Figure.15 Current vs. OUTLV[2:0] bits

REFIN frequency = 100MHz, R counter = 100, CP1[2:0] bits = "111"

#### **AK1573C**

Figure.20 Output power vs. Output frequency

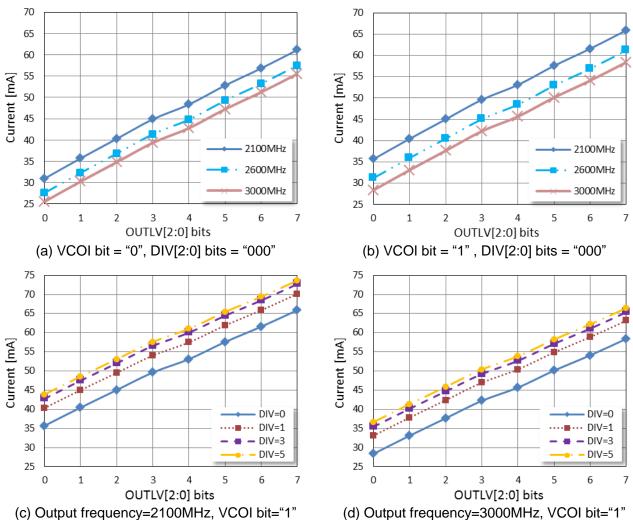

Figure.21 Current vs. OUTLV[2:0] bits

REFIN frequency = 100MHz, R counter = 100, CP1[2:0] bits = "111"

Asahi**KASEI** [AK1573/AK1573B/AK1573C]

## 12. Register Map

| Name     | Data       | Address |   |   |   |  |  |  |

|----------|------------|---------|---|---|---|--|--|--|

| A/B      |            | 0       | 0 | 0 | 1 |  |  |  |

| C/P      | D19 to D0  | 0       | 0 | 1 | 0 |  |  |  |

| Ref/Pres | D 19 t0 D0 | 0       | 0 | 1 | 1 |  |  |  |

| Function |            | 0       | 1 | 0 | 0 |  |  |  |

|                   | D19          | D18          | D17          | D16          | D15        | D14        | D13        | D12        | D11        | D10        | D9           | D8           | D7           | D6         | D5         | D4         | D3          | D2          | D1          | D0          | Address |

|-------------------|--------------|--------------|--------------|--------------|------------|------------|------------|------------|------------|------------|--------------|--------------|--------------|------------|------------|------------|-------------|-------------|-------------|-------------|---------|

| A/B               | Don't care   | B<br>[12]    | B<br>[11]    | B<br>[10]    | B<br>[9]   | B<br>[8]   | B<br>[7]   | B<br>[6]   | B<br>[5]   | B<br>[4]   | B<br>[3]     | B<br>[2]     | B<br>[1]     | B<br>[0]   | A<br>[5]   | A<br>[4]   | A<br>[3]    | A<br>[2]    | A<br>[1]    | A<br>[0]    | 0x01    |

| C/P               | Don't care   | Don't care   | Don't care   | Don't care   | Don't care | Don't care | Don't care | Don't care | Don't care | Don't care | Don't care   | CP2<br>[2]   | CP2<br>[1]   | CP2<br>[0] | Don't care | Don't care | Don't care  | CP1<br>[2]  | CP1<br>[1]  | CP1<br>[0]  | 0x02    |

| Ref/Pres          | CALTM<br>[3] | CALTM<br>[2] | CALTM<br>[1] | CALTM<br>[1] | PRE<br>[1] | PRE<br>[0] | R<br>[13]  | R<br>[12]  | R<br>[11]  | R<br>[10]  | R<br>[9]     | R<br>[8]     | R<br>[7]     | R<br>[6]   | R<br>[5]   | R<br>[4]   | R<br>[3]    | R<br>[2]    | R<br>[1]    | R<br>[0]    | 0x03    |

| Function          | Don't care   | Don't care   | LDCNT<br>SEL | FAST<br>EN   | CPHiZ      | LD         | DIV[2]     | DIV[1]     | DIV[0]     | MTLD       | OUTLV<br>[2] | OUTLV<br>[1] | OUTLV<br>[0] | Don't care | Don't care | VCOI       | FAST<br>[3] | FAST<br>[2] | FAST<br>[1] | FAST<br>[0] | 0x04    |

| Software<br>Reset |              |              |              |              |            |            |            |            |            |            |              | 0x05         |              |            |            |            |             |             |             |             |         |

- Notes on writing registers

- 1. When PDN1 pin = "H" and LDO (VREF1 pin) is active, access to the register is available

- 2. The setting of <Address0x02> and <Address0x03> will be reflected to the behavior of AK1573 when the register <Address0x01> is written

- 3. <Address0x04> can be written independently.

- 4. After PDN1 pin turns to "H", all of the register values are indefinite. It is needed to write the data to all the registers to confirm.

#### **Examples of the register setting**

#### Ex.1 Power on setting

- 1. Set PDN1 pin = "L" and PDN2 pin = "L"

- Power on VCOVDD, PVDD and CPVDD Note) All VDD should be powered on simultaneously

- 3. Set PDN1 pin = "H" and PDN2 pin = "L" (VBG / LDO are powered on)

- 4. Write the data to the register <Address0x04>

- 5. Set PDN1 pin = "H" and PDN2 pin = "H" (All blocks are powered on)

- 6. Write the data to the register <Address0x01> and <Address0x02>

- 7. Write the data to the register <Address0x01>

#### Ex.2 Change frequency settings

1. Write the data to the register <Address0x01>

#### **Ex.3 Change Charge Pump settings**

- 1. Write the data to the register <Address0x02>

- 2. Write the data to the register <Address0x01>

#### Ex.4 Change Reference dividing ratio

- 1. Write the data to the register <Address0x03>

- 2. Write the data to the register <Address0x01>

#### < Address0x01 : N counter >

#### D[18:6]

#### B[12:0]: B (Programmable) counter setting

Set the dividing ratio of B (Programmable) counter.

The setting range is shown in the following table.

| B[12:0] | Programmable counter dividing ratio | Remark     |

|---------|-------------------------------------|------------|

| 0       | -                                   | Prohibited |

| 1       | -                                   | Prohibited |

| 2       | -                                   | Prohibited |

| 3       | 3                                   |            |

| :       | :                                   |            |

| 8191    | 8191                                |            |

#### D[5:0]

#### A[5:0]: A (Swallow) counter setting

Set the dividing ratio of A (Swallow) counter.

The setting range is shown in the following table.

| A[5:0] | Swallow counter dividing ratio | Remark |

|--------|--------------------------------|--------|

| 0      | 0                              |        |

| 1      | 1                              |        |

| 2      | 2                              |        |

| :      | :                              |        |

| 63     | 63                             |        |

The data at A[5:0] bits and B[12:0] bits must meet the following requirements: B[12:0] bits  $\geq$  3, B[12:0] bits  $\geq$  A[5:0] bits

See "13. Frequency Setting" for details of the relationship between a frequency dividing ratio N and the data at A[5:0] bits and B[12:0] bits.

It is prohibited to set frequency once again until VCO calibration and Fast lock-up mode is completed.

< Address0x02 : C/P >

#### D[8: 6]

### CP2[2:0]: Charge pump current setting for Fast Lockup operation

#### D[2:0]

#### CP1[2:0]: Charge pump current setting for normal operation

AK1573 provides two settings for charge pump current. CP1[2:0] bits are for normal operation and CP2[2:0] bits are for Fast Lockup mode.

The following formula shows the relationship among the resistance value, the register setting and the electric current.

Charge pump current (Icp) [A] = Icp\_min [A] × [(CP1[2:0] bits or CP2[2:0] bits setting) + 1] Charge pump minimum current (Icp\_min) [A] = 9.45 / BIAS Resistance [ $\Omega$ ]

The following table shows the typical lcp for each status.

Icp (typ.) unit : μA

| CD4[3:0] CD3[3:0]  | BIAS   |      |      |  |  |

|--------------------|--------|------|------|--|--|

| CP1[2:0], CP2[2:0] | 33kΩ   | 27kΩ | 22kΩ |  |  |

| 0                  | 286    | 350  | 430  |  |  |

| 1                  | 573    | 700  | 859  |  |  |

| 2                  | 859    | 1050 | 1289 |  |  |

| 3                  | 1146   | 1400 | 1718 |  |  |

| 4                  | 1432   | 1750 | 2148 |  |  |

| 5                  | 1718   | 2100 | 2577 |  |  |

| 6 2005             |        | 2450 | 3007 |  |  |

| 7                  | 7 2291 |      | 3436 |  |  |

#### < Address0x03 : Ref/Pres >

#### D[19:16]

#### CALTM[3:0] Set the calibration precision of VCO

The register CALTM[3:0] bits set the calibration precision and time. The larger CALTM[3:0] bits are set, the higher calibration precision becomes, but the longer calibration time is required as trade-off. Set the value calculated by the following formula to get enough calibration precision. However, CALTM[3:0] bits should be set from 0 to 10. Over 11 are prohibited. See "15. VCO" for details of the VCO calibration.

CALTM[3:0] bits

$$\ge 10 - \log (B[12:0] \text{ bits}) / \log(2)$$

The calibration time can be estimated as following formula;

Calibration time =  $1 / F_{PFD} \times 11 \times 2 ^ CALTM[3:0]$  bits

#### D[15:14]

#### PRE[1:0]: Selects a dividing ratio for the prescaler

00: P=8

01: P=16

10: P=32

11: P=64

The prescaler value should be selected so that the prescaler output frequency is less than or equal to 300MHz.

### D[13:0]

#### R[13:0]: 14bit Reference Counter

The following settings can be selected for the reference clock division.

The allowed range is 1 (1/1 division) to 16383 (1/16383 division). 0 cannot be set.

The maximum PFD frequency is 104MHz.

| R[13:0] | Dividing Ratio |

|---------|----------------|

| 0       | Prohibited     |

| 1       | 1              |

| 2       | 2              |

| 3       | 3              |

| 4       | 4              |

| :       | •              |

| :       | •              |

| :       | •              |

| 16381   | 16381          |

| 16382   | 16382          |

| 16383   | 16383          |

#### < Address0x04 : Function >

#### D[17]

#### **LDCNTSEL: Lock Detect Precision**

Set the counter value for digital lock detect.

| LDCNTSEL | Function       |                    |

|----------|----------------|--------------------|

| 0        | 15 times Count | unlocked to locked |

| U        | 3 times Count  | locked to unlocked |

| 1        | 31 times Count | unlocked to locked |

| '        | 7 times Count  | locked to unlocked |

### D[16]

#### **FASTEN:** Enables the Fast Lock mode

See "14. Fast Lock-up mode" for details of the Fast Lock-up function.

0: Fast Lockup disable1: Fast Lockup enable

#### D[15]

#### **CPHIZ: TRI-STATE output setting for charge pump**

0: Charge pumps are activated

1: Tri-State

#### D[14]

### LD : Selects output from LD pin

See "12. Lock detect" for details of the Lock detect function.

0: Digital lock detect

1: Analog lock detect

#### D[13:11]

#### **DIV[2:0] : Selects Divide of Output**

Select the dividing ratio in accordance with the used frequency.

- 0: Divide by 1

- 1: Divide by 2

- 2: Divide by 4

- 3: Divide by 8

- 4: Divide by 16

- 5: Divide by 32

- 6: Divide by 64

- 7: Prohibited

#### D[10]

### MTLD: Local signal mute

0: Disable to mute local signal in unlock state.

1: Enable to Mute local signal in unlock state.

Set MTLD bit = "0" when LD bit = "1".

### D[9:7]

#### OUTLV[2:0]: Select output power level

Adjust bias current of output buffer

| OUTLV[2:0] | Bias current (mA) |

|------------|-------------------|

| 0          | 4                 |

| 1          | 8                 |

| 2          | 12                |

| 3          | 16                |

| 4          | 20                |

| 5          | 24                |

| 6          | 28                |

| 7          | 32                |

#### D[4]

### **VCOI: VCO core current setting**

0: Low current mode

1: Normal

D[3:0]

#### FAST[3:0]: FAST counter timer

Set the effective time of fast lock-up mode. Counter value = 3 + FAST[3:0] bits x 4

| FAST[3:0] | Counter value |

|-----------|---------------|

| 0         | 3             |

| 1         | 7             |

| 2         | 11            |

| 3         | 15            |

| 4         | 19            |

| 5         | 23            |

| 6         | 27            |

| 7         | 31            |

| 8         | 35            |

| 9         | 39            |

| 10        | 43            |

| 11        | 47            |

| 12        | 51            |

| 13        | 55            |

| 14        | 59            |

| 15        | 63            |

#### < Address0x05 : Software Reset >

When writing a <Address0x05>, all of the internal flip-flops, except for the register and calibration results, are initialized. Internal flip-flops except for the register and the calibration results is initialized in the state of PDN1 pin = PDN2 pin = "H". When standing up PDN1 pin and PDN2 pin at the same time or PDN1 pin and PDN2 pin are fixed to "H", internal flip-flops are not initialized. In this case, it is needed to initialize internal flip-flops using the Software Reset.

#### 13. Function Descriptions

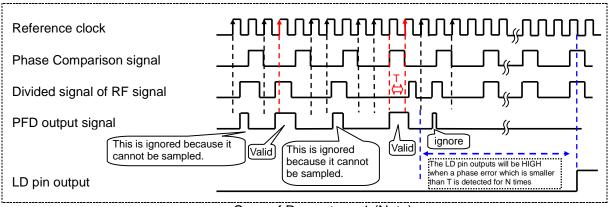

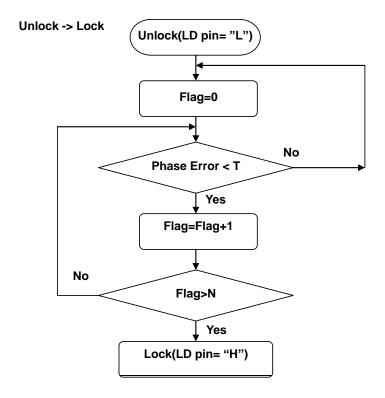

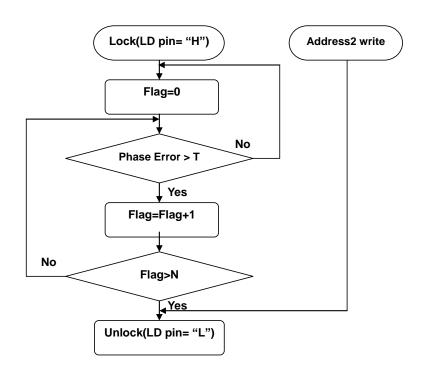

#### 13.1. Lock detect

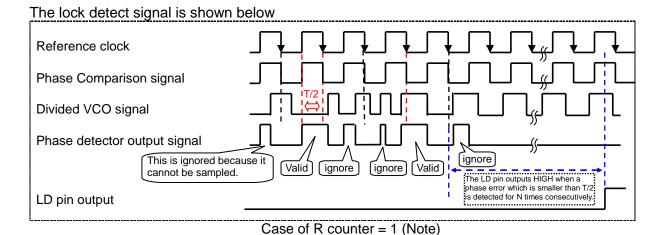

Lock detect output can be selected by LD bit in <Address0x04>. When LD bit = "1", LD pin outputs a phase comparison result which is from phase detector directly (This is called "analog lock detect"). When LD bit = "0", the output is the lock detect signal according to the on-chip logic (This is called "digital lock detect").

The digital lock detect can be done as following:

The LD pin is in unlocked state (which outputs "L") when a frequency setup is made.

In the digital lock detect, the LD pin outputs "H" (which means the locked state) when a phase error smaller than a cycle of [REFIN] clock (T) is detected for N times consecutively. When a phase error larger than T is detected for N times consecutively while the LD pin outputs "H", then the LD pin outputs "L" (which means the unlocked state). The counter value N can be set by LDCNTSEL bit in <Address0x04>. The N is different between "unlocked to locked" and "locked to unlocked".

| LDCNTSEL bit | unlocked to locked | locked to unlocked |

|--------------|--------------------|--------------------|

| 0            | N=15               | N=3                |

| 1            | N=31               | N=7                |

Case of R counter > 1 (Note)

Figure.26 Digital Lock Detect Operations

<sup>\*</sup> R counter can be set by R[13:0] bits in Address0x03

#### Lock -> Unlock

#### 13.2. Frequency Setting

The following formula is used to calculate the frequency setting for the AK1573.

#### Example

Set the AK1573 as follows to obtain Frequency setting =2100MHz with  $F_{PFD}$  = 200kHz

P = 8 (Address0x02 : Pre[1:0] bits = 0) B = 1312 (Address0x01 : B[12:0] bits = 1312) A = 4 (Address0x01 : A[5:0] bits = 4)

Frequency setting =  $200k \times (8 \times 1312 + 4) = 2100MHz$

#### Note) Lower limit for setting consecutive dividing numbers

For the AK1573, it is not possible to set consecutive dividing ratio below the lower limit (The lower limit is determined by a dividing ratio set for the prescaler).

The following table shows an example where consecutive dividing numbers below the lower limit cannot be set. The consecutive dividing ratio can be set when  $B \ge P-1$ .

\*P=8 (Dual modulus prescaler 8/9)

| Р | B[12:0] | A[5:0] | Dividing ratio |                                                                               |

|---|---------|--------|----------------|-------------------------------------------------------------------------------|

| 8 | 6       | 6      | 54             | 55 cannot be set as an N divider.                                             |

| 8 | 7       | 0      | 56             | This is the lower limit. 56 or over can consecutively be set as an N divider. |

| 8 | 7       | 1      | 57             |                                                                               |

| : | :       |        | :              |                                                                               |

| 8 | 7       | 7      | 63             |                                                                               |

| 8 | 8       | 0      | 64             |                                                                               |

| : | :       |        | :              |                                                                               |

\*P=16 (Dual modulus prescaler 16/17)

| Р  | В  | А  | N   |                                                                                      |

|----|----|----|-----|--------------------------------------------------------------------------------------|

| 16 | 14 | 14 | 238 | 239 cannot be set as an N divider.                                                   |

| 16 | 15 | 0  | 240 | This is the lower limit.<br>240 or over can consecutively<br>be set as an N divider. |

| 16 | 15 | 1  | 241 |                                                                                      |

| :  | :  | :  | :   |                                                                                      |

| 16 | 15 | 15 | 255 |                                                                                      |

| 16 | 16 | 0  | 256 |                                                                                      |

| :  | :  | :  | :   |                                                                                      |

\*P=32 (Dual modulus prescaler 32/33)

| Р  | В  | Α  | N    |                                                                                |

|----|----|----|------|--------------------------------------------------------------------------------|

| 32 | 30 | 30 | 990  | 991 cannot be set as an N divider.                                             |

| 32 | 31 | 0  | 992  | This is the lower limit. 992 or over can consecutively be set as an N divider. |

| 32 | 31 | 1  | 993  |                                                                                |

| :  | :  | :  | :    |                                                                                |

| 32 | 31 | 31 | 1023 |                                                                                |

| 32 | 32 | 0  | 1024 |                                                                                |

| :  | :  | :  | :    |                                                                                |

\*P=64 (Dual modulus prescaler 64/65)

| Р  | В  | А  | N    |                                                                                 |

|----|----|----|------|---------------------------------------------------------------------------------|

| 64 | 62 | 62 | 4030 | 4031 cannot be set as an N divider.                                             |

| 64 | 63 | 0  | 4032 | This is the lower limit. 4032 or over can consecutively be set as an N divider. |

| 64 | 63 | 1  | 4033 |                                                                                 |

| :  | :  | :  | :    |                                                                                 |

| 64 | 63 | 63 | 4095 |                                                                                 |

| 64 | 64 | 0  | 4096 |                                                                                 |

| :  | :  | :  | :    |                                                                                 |

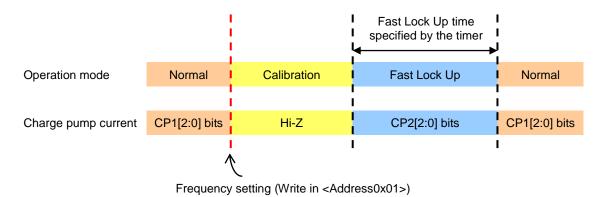

#### 13.3. Fast Lock-up mode

The AK1573 goes into Fast Lock Up mode by setting FASTEN bit in <Address0x04> to "1". When A and B counter setting is finished (writing in <Address0x01>), Fast Lock Up mode starts after calibration. The Fast Lock Up mode is enabled only during the time period set by the timer according to the counter value in FAST[3:0] bits in <Address0x04>. The charge pump current is set to the value specified by CP2[2:0] bits. When the specified time period elapses, the Fast Lock Up mode operation is switched to the normal operation, and the charge pump current returns to CP1[2:0] bits setting.

FAST[3:0] bits in <Address0x04> is used to set the time period for this mode. The following formula is used to calculate the time period :

Switchover time =  $1 / F_{PFD} \times Counter Value$ Counter Value =  $3 + 4 \times (FAST[3:0])$  bits setting)

Figure.27 Fast Lock-up Mode Timing Chart

#### 13.4. VCO

#### Calibration

The VCO core in AK1573 uses several overlapping bands to achieve low Phase Noise, low VCO sensitivity ( $K_{VCO}$ ) and wide frequency range. The correct band is chosen automatically at frequency setting by VCO calibration. The calibration starts when A counter and B counter in <Address0x01> are set. During the calibration, VCO  $V_{CNT}$  is disconnected from the external loop filter and connected to an internal reference voltage. The charge pump output is Tri-State.

The internal reference voltage must be stable so that the calibration is done correctly. Therefore, it is necessary to wait  $10\mu$ sec at least until <Address0x01> is set after PDN2 pin rises up to "1" (when 100pF is connected to SCAP pin).

The register CALTM[3:0] bits set the calibration precision and time. The larger CALTM[3:0] bits are set, the higher calibration precision becomes, but the longer calibration time is required as trade-off. Set the value calculated by the following formula to get enough calibration precision. However, CALTM[3:0] bits should be set from 0 to 10. Over 11 are prohibited.

CALTM[3:0] bits  $\geq$  10 - log(B[12:0]) / log(2)

The calibration time can be estimated as following formula;

Calibration time =  $1 / F_{PFD} \times 11 \times 2 ^ CALTM[3:0]$  bits

It is prohibited to set frequency once again until VCO calibration and Fast lock-up mode is completed.

#### **Low Current Mode**

The AK1573 goes into low current mode by setting VCOI bit in <Address0x04> to "0". This mode decreases VCO core current but Phase Noise gets worse compared to normal mode.

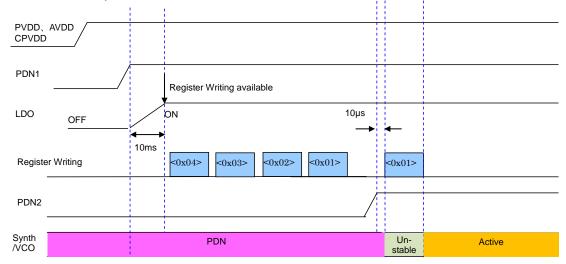

#### 14. Power on sequence

#### 1. Recommended sequence

### 2. The sequence when PDN1 pin and PDN2 pin are powered on simultaneously

Figure.28 Power on sequence

- \* After powering on AK1573, the initial register's values are not defined. It is required to write the data to all the registers.

- \* It takes about 10msec from PDN1 pin rise-up to LDO rise-up.

- \* If PDN1 pin and PDN2 pin are powered on simultaneously, the operation of AK1573 is not defined until the registers are set.

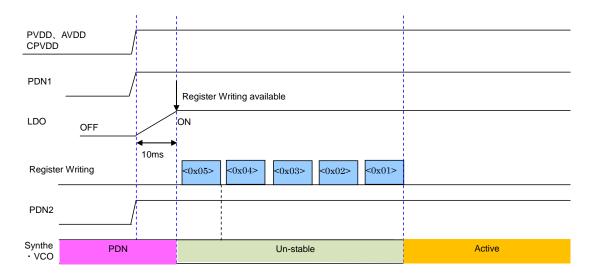

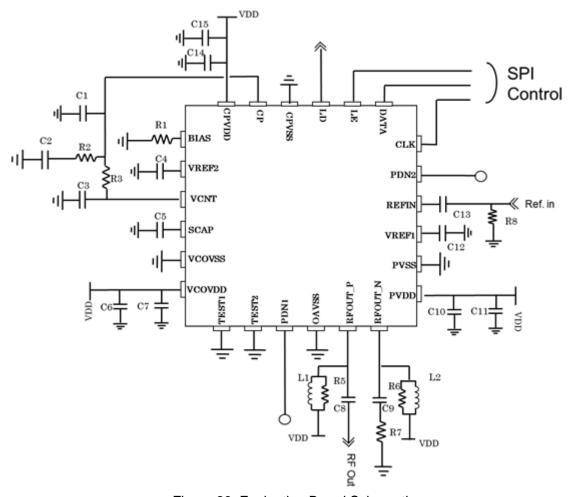

### 15. Recommended External Circuits

Figure.29. Evaluation Board Schematic

Table.1

| Ref. | Value       | Ref. | Value | Ref. | Value       | Ref. | Value       |

|------|-------------|------|-------|------|-------------|------|-------------|

| C1   | Loop Filter | C7   | 100pF | C13  | 100pF       | R3   | Loop Filter |

| C2   | Loop Filter | C8   | 100pF | C14  | 100pF       | R1   | 27kΩ        |

| C3   | Loop Filter | C9   | 100pF | C15  | 10nF        | R5   | 100Ω        |

| C4   | 470nF       | C10  | 100pF | L1   | 2.2μΗ       | R6   | 100Ω        |

| C5   | 100pF       | C11  | 10nF  | L2   | 2.2μΗ       | R7   | 51Ω         |

| C6   | 10nF        | C12  | 220nF | R2   | Loop Filter | R8   | 51Ω         |

- \* The exposed pad at the center of the backside should be connected to the ground.

- \* TEST1 / TEST2 pins should be connected to the ground.

- \* RFOUT\_P / RFOUT\_N pins must be connected an inductor and a register to VDD.

- \* In the case of single-ended output operation, unused output pin is terminated through  $50\Omega$  after 100pF capacitance.

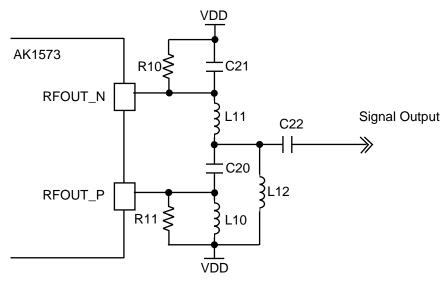

#### 16. Application Note

#### Differential to single-ended circuit

AK1573 has differential output ports. "15 Recommended External Circuits" shows single-ended output but users can convert differential output to single output using lumped element balun. By doing this, AK1573 outputs higher signal level compared to single-ended output with the same current consumption. Lumped element balun shows frequency dependence, so users need to populate optimized elements in order to obtain good matching characteristics. Table.2 shows the reference values of lumped element balun.

Figure 30 Lumped Element Balun Circuit

Table.2 Reference values of lumped element balun

| Frequency Range<br>[MHz] | C20<br>[pF] | C21<br>[pF] | C22<br>[pF] | L10<br>[nH] | L11<br>[nH] | L12<br>[nH] | R10<br>[Ω] | R11<br>[Ω] |

|--------------------------|-------------|-------------|-------------|-------------|-------------|-------------|------------|------------|

| 2150 to 2250             | 1           | 1           | 1000        | 1           | 1           | 330         | 100        | 100        |

| 2000 to 2150             | 1           | 1           | 1000        | 1.5         | 1.5         | 330         | 100        | 100        |

| 1900 to 2000             | 1           | 1           | 1000        | 2           | 2           | 330         | 100        | 100        |

| 1770 to 1900             | 1           | 1           | 1000        | 2.4         | 2.4         | 330         | 100        | 100        |

| 1600 to 1770             | 1           | 1           | 1000        | 3.3         | 3.3         | 330         | 100        | 100        |

| 1450 to 1600             | 1           | 1           | 1000        | 4.3         | 4.3         | 330         | 100        | 100        |

| 1280 to 1450             | 1           | 1           | 1000        | 5.1         | 5.1         | 330         | 100        | 100        |

| 1050 to 1280             | 1           | 1           | 1000        | 7.5         | 7.5         | 330         | 100        | 100        |

| 800 to 1050              | 1           | 1           | 1000        | 10          | 10          | 330         | 100        | 100        |

| 550 to 800               | 1           | 1           | 1000        | 15          | 15          | 330         | 100        | 100        |

| 350 to 550               | 1.6         | 1.6         | 1000        | 22          | 22          | 330         | 100        | 100        |

| 200 to 350               | 4.7         | 4.7         | 1000        | 47          | 47          | 330         | 100        | 100        |

| 100 to 200               | 8           | 8           | 1000        | 82          | 82          | 330         | 100        | 100        |

| 60 to 100                | 15          | 15          | 1000        | 150         | 150         | 330         | 100        | 100        |

| 40 to 60                 | 27          | 27          | 1000        | 270         | 270         | 330         | 100        | 100        |

| 30 to 40                 | 39          | 39          | 1000        | 390         | 390         | 330         | 100        | 100        |

### 17. Interface circuit

| Pin<br>No. | Pin name | I/O | R0<br>(Ω) | Current<br>(μA) | Function                  |

|------------|----------|-----|-----------|-----------------|---------------------------|

| 9          | PDN1     | ı   | 300       |                 |                           |

| 17         | PDN2     | I   | 300       |                 | Digital input pin         |

| 18         | CLK      | I   | 300       |                 | <u> </u>                  |

| 19         | DATA     | -   | 300       |                 | ,                         |

| 20         | LE       | I   | 300       |                 |                           |

|            |          |     |           |                 |                           |

| 7          | TEST1    | I   | 300       |                 | Digital input (Pull-Down) |

| 8          | TEST2    |     | 300       |                 | <del> </del>              |

|            |          |     |           |                 | R0   W   100k             |

| 21         | LD       | 0   |           |                 | Digital output pin        |

|            |          |     |           |                 |                           |

| 3          | VCNT     | I   | 100       |                 | Analog input pin          |

| 16         | REFIN    | I   | 300       |                 | <u> </u>                  |

|            |          |     |           |                 | RO                        |

| Pin<br>No. | Pin Name | I/O | R0<br>(Ω) | Current<br>(µA) | Function                  |

|------------|----------|-----|-----------|-----------------|---------------------------|

| 1          | BIAS     | Ю   | 300       |                 | Analog input/output pin   |

| 2          | VREF2    | Ю   | 300       |                 |                           |

| 4          | SCAP     | 10  | 100       |                 | R0                        |

| 15         | VREF1    | 0   | 300       |                 | ]                         |

|            |          |     |           |                 |                           |

| 23         | CP       | 0   |           |                 | Analog output pin         |

|            |          |     |           |                 |                           |

| 11         | RFOUT_P  | 0   |           |                 | Open-collector output pin |

| 12         | RFOUT_N  | 0   |           |                 | <u> </u>                  |

|            |          |     |           |                 |                           |

### 18. Package

### 18.1. Outline Dimensions

<sup>\*</sup> The exposed pad at the center of the backside should be connected to ground.

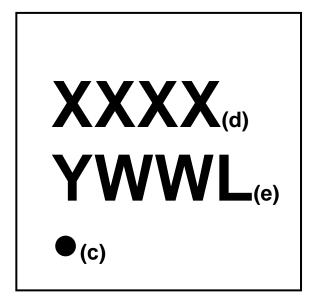

#### 18.2. Marking

(a) Style : QFN (b) Number of pins : 24-pin (c) 1 pin marking : ○

(d) Product number : XXXX (4 or 5 digits)

AK1573 : AK1573 AK1573B : AK1573B AK1573C : AK1573C

(e) Date code : YWWL (4 digits)

Y: Lower 1 digit of calendar year (Year 2015  $\rightarrow$  5, 2016  $\rightarrow$  6 ...)

WW: Week

L: Lot identification, given to each product lot which is

made in a week

→ LOT ID is given in alphabetical order (A, B, C...)

## 19. Revision History

| Date (Y/M/D) | Revision | Reason        | Page | Contents |

|--------------|----------|---------------|------|----------|

| 15/08/03     | 00       | First Edition |      |          |

#### IMPORTANT NOTICE

Asahi Kasei Microdevices Corporation ("AKM") reserves the right to make changes to the information contained in this document without notice. When you consider any use or application of AKM product stipulated in this document ("Product"), please make inquiries the sales office of AKM or authorized distributors as to current status of the Products.

All information included in this document are provided only to illustrate the operation and application examples of AKM Products. AKM neither makes warranties or representations with respect to the accuracy or completeness of the information contained in this document nor grants any license to any intellectual property rights or any other rights of AKM or any third party with respect to the information in this document. You are fully responsible for use of such information contained in this document in your product design or applications. AKM ASSUMES NO LIABILITY FOR ANY LOSSES INCURRED BY YOU OR THIRD PARTIES ARISING FROM THE USE OF SUCH INFORMATION IN YOUR PRODUCT DESIGN OR APPLICATIONS.

The Product is neither intended nor warranted for use in equipment or systems that require extraordinarily high levels of quality and/or reliability and/or a malfunction or failure of which may cause loss of human life, bodily injury, serious property damage or serious public impact, including but not limited to, equipment used in nuclear facilities, equipment used in the aerospace industry, medical equipment, equipment used for automobiles, trains, ships and other transportation, traffic signaling equipment, equipment used to control combustions or explosions, safety devices, elevators and escalators, devices related to electric power, and equipment used in finance-related fields. Do not use Product for the above use unless specifically agreed by AKM in writing.

Though AKM works continually to improve the Product's quality and reliability, you are responsible for complying with safety standards and for providing adequate designs a

data loss or corruption.

4. Do not use or otherwise make available the Product or related technology or any information contained in this document for any military purposes, including without limitation, for the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile technology products (mass destruction weapons). When exporting the Products or related technology or any information contained in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. The Products and related technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

Please contact AKM sales representative for details as to environmental matters such as the RoHS compatibility of the Product. Please use the Product in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. AKM assumes no liability for damages or losses occurring as a result of noncompliance with applicable laws and regulations.

Resale of the Product with provisions different from the statement and/or technical features set forth in this document shall immediately void any warranty granted by AKM for the Product and shall not create or extend in any manner whatsoever, any liability of AKM.

This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of AKM.