## AK1574

## 46.875-1682.5MHz Fractional-N PLL

with integrated VCO and FM/FSK modulator

## 1. General Description

The AK1574 is a fractional-N PLL synthesizer with a VCO (Voltage Controlled Oscillator) that has frequency modulation function. It integrates an output divider for VCO signal that operates by 3365MHz frequency at maximum realizing wide range output frequency from 46.875MHz to 1682.5MHz. The AK1574 reduces the power consumption while realizing low normalized phase noise of -221dBc/Hz. It achieves 90mW(3V/Single output) operation when outputting -6dBm. It is capable of replacing VCOs, that use to consist of variable capacitance diode and etc., in various wireless applications especially suitable for hand portable wireless devices. The fast lock-up, that completes in only less than 1ms, suites for intermittent operation of PLL/VCO. It contributes to reducing the system power consumption.

Two set of mode settings that include frequency setting and On/Off settings of RF output pins are available.

Output Mode A: Frequency setting  $f_{Rx}$ , RFOUT\_A On, RFOUT\_B Off (Single output)

Output Mode B: Frequency setting  $f_{Tx}$ , RFOUT\_A Off, RFOUT\_B On (Single output)

By setting as above, the RFOUT\_A pin can be used as receiving output and the RFOUT\_B pin can be used as transmitting output.

Output Mode A: Frequency  $f_{Rx}$ , RFOUT\_A On, RFOUT\_B On (Differential Output) By setting as above, two lines of common-frequency can be output. It is able to use for diversity receivers. When both RFOUT\_A and B are On, the signal is output as differential signal so that it is capable of being used as single differential output.

Data input format for frequency modulation corresponds to both analog and digital data inputs. Digital I/F data format can be selected from I<sup>2</sup>S (Inter-IC Sound), Left-justified and SPI. The AK1574 has a frequency shift compensation function for TCXO that is used when shipping user's product. Therefore, it is able to use TCXO instead of VCTCXO.

| 2. Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| □ Output Frequency: 46.875MHz ~ 1682.5MHz □ Current Consumption: 30mA at 3V, 520.1MHz, -6dBm Output (Single Output) □ Supply Voltage/Temperature Range: 2.7 ~ 3.45V (IOVDD: 1.7V~ ) / -40 ~ +85°C □ Frequency Modulation Supporting Analog Voice Data Input (FM/FSK) □ Various Digital I/F for Frequency Modulation Function (FM/FSK): I²S, Left-Justified, SPI □ Normalized Phase Noise: -221dBc/Hz (during fractional operation) □ In-band Phase Noise: -125dBc/Hz at 12.5kHz Offset, 420MHz Output, PFD □ Frequency=50.4MHz □ Frequency Resolution Under 10Hz by a 23-bit ΔΣ Modulator □ Driver amplifier with variable output power: -12 ~ +6dBm Output (Single Output) □ Two Output Ports for various application □ Faster Lock-up Time: <1ms □ Divided Reference Clock Output Function for Common System Clock □ REFCKIN Frequency: 10MHz ~ 60MHz □ Package: 36-pin QFN (5mm×5mm×0.75 mm, 0.4mm pitch) |  |

| 3. Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| <ul><li>□ Professional Mobile Radio (DMR, NXDN, dPMR, TIA-603, STD-T98/102, etc.)</li><li>□ FM/FSK transmitter</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|                | 4. Table of Contents                              |      |

|----------------|---------------------------------------------------|------|

|                | al Description                                    |      |

|                | es                                                |      |

|                | ations                                            |      |

|                | of Contents                                       |      |

|                | Diagram and Functions                             |      |

|                | ock Diagram                                       |      |

|                | nfigurations and Functionsn Layout                |      |

|                | n Functions                                       |      |

|                | andling of Unused Pin                             |      |

|                | ute Maximum Ratings                               |      |

|                | nmended Operating Conditions                      |      |

|                | Characteristics                                   |      |

|                | C Characteristics                                 |      |

|                | ystem Reset                                       |      |

|                | erial Interface Timing for Register Accessing     |      |

|                | erial Interface Timing of Modulation Signal Input |      |

|                | log Characteristics                               |      |

|                | cal Performance                                   |      |

|                | Output Power                                      |      |

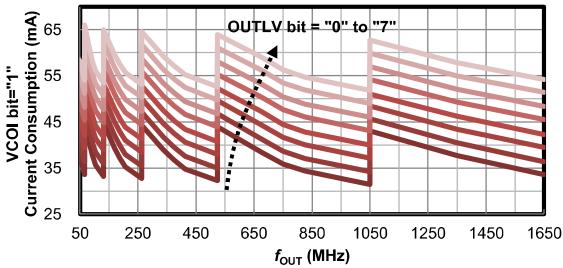

|                | Current Consumption                               |      |

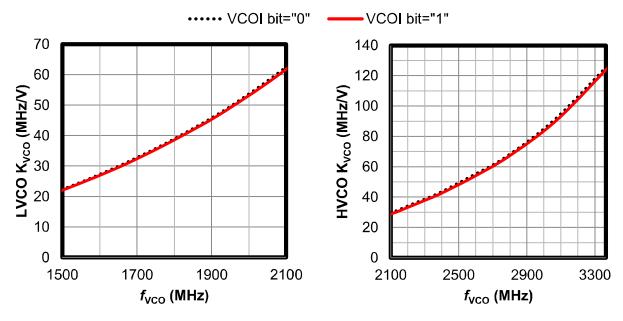

|                | Tuning Sensitivity(K <sub>VCO</sub> )             |      |

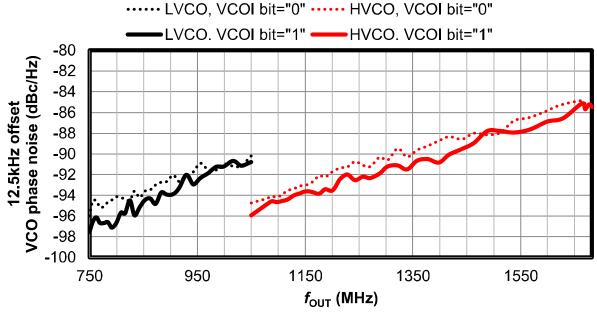

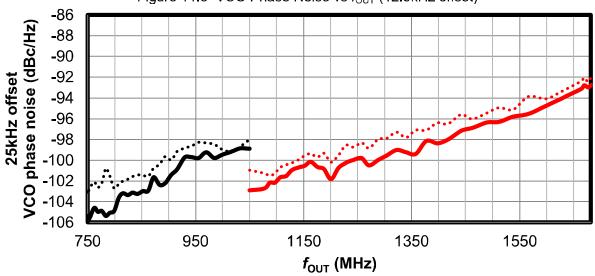

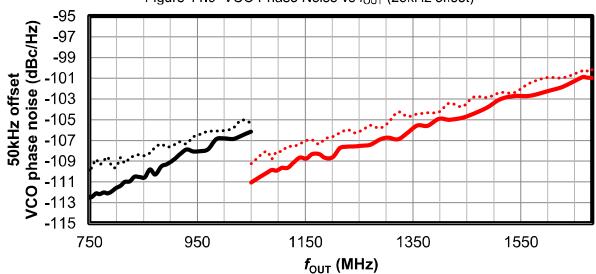

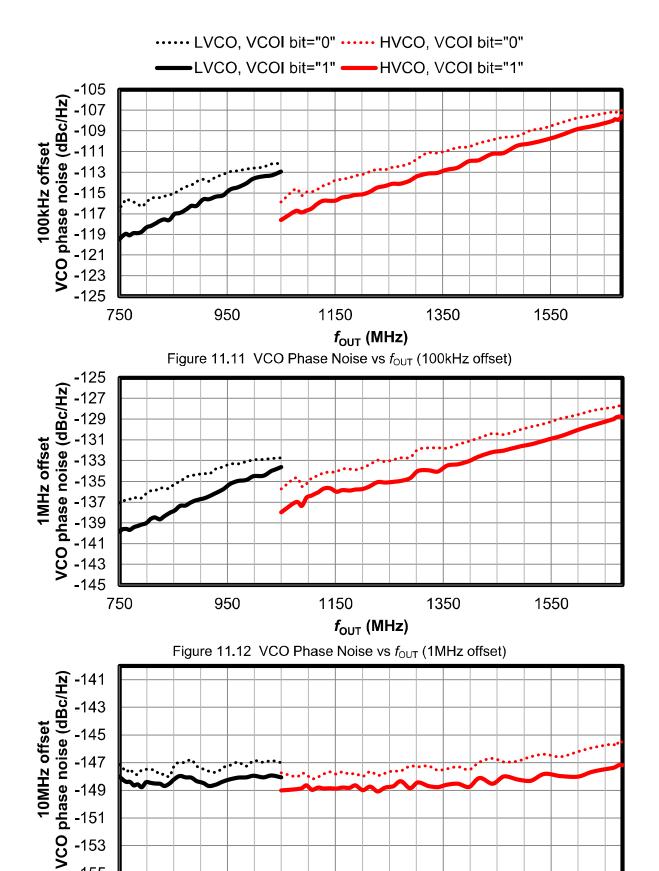

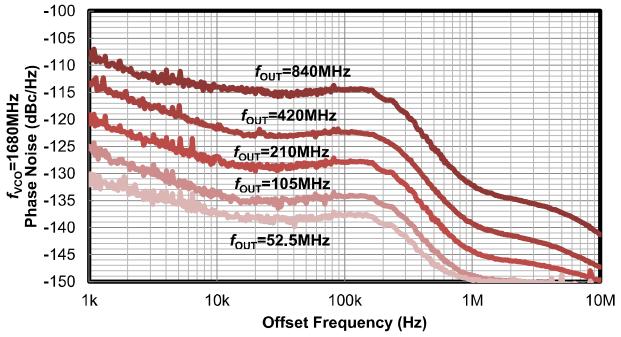

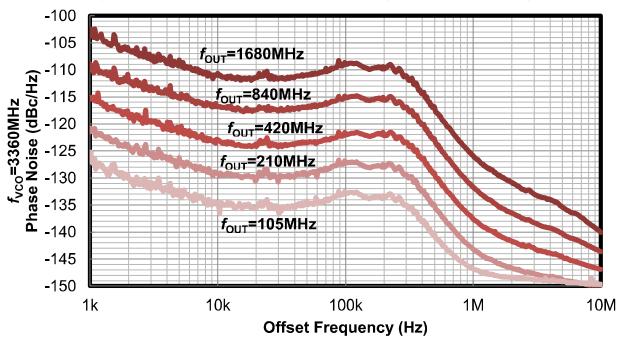

|                | VCO Phase Noise                                   |      |

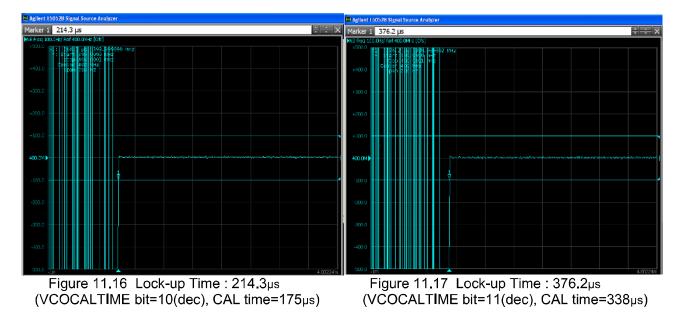

|                | Lock-up Time                                      |      |

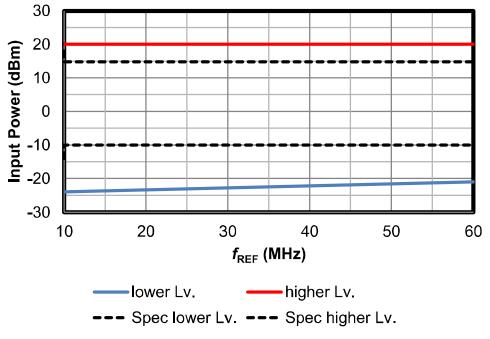

| 11.7.          | REFCK BUFFER                                      |      |

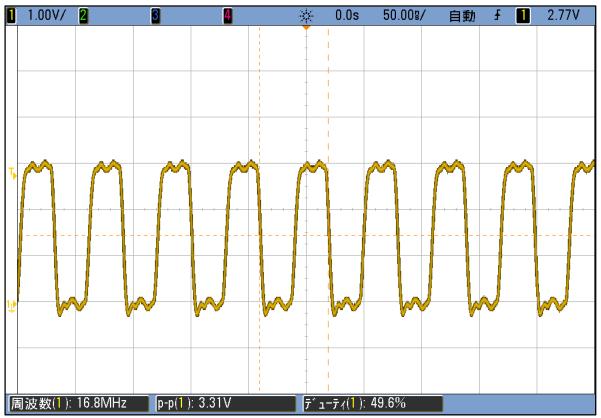

| 11.8           | REFCK DIVIDER                                     |      |

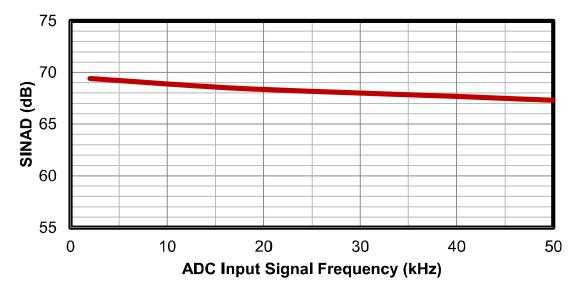

|                | ADC                                               |      |

|                | Modulation Characteristics                        |      |

|                | Wide-band Spurious(WBS)                           |      |

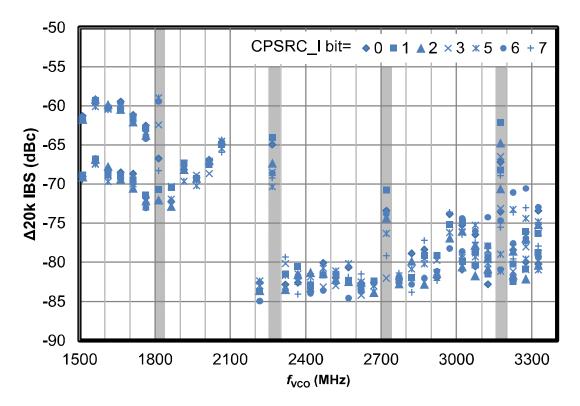

| 11.12.         | Integer Boundary Spurious(IBS)                    | 27   |

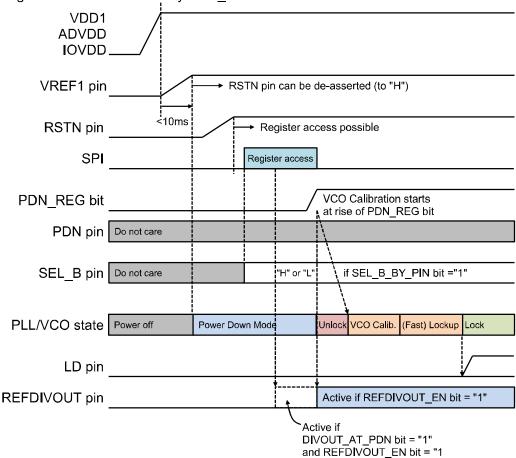

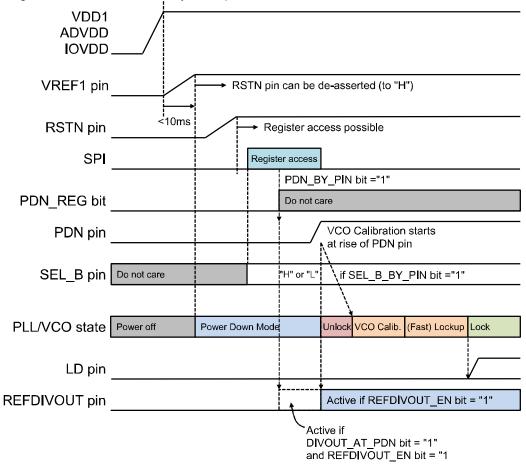

|                | er-Up Sequence                                    |      |

|                | Power-up Sequence                                 |      |

|                | ctional Description                               |      |

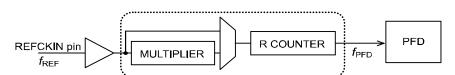

|                | MULTIPLIER / R COUNTER                            |      |

|                | Frequency Stetting                                |      |

|                | Re-lock up event                                  | 3/   |

| 13.4.<br>13.5. | Fast Lock-Up ModeVCO                              |      |

| 13.6.          | LOOP FILTER                                       | 30   |

|                | LOCK DETECTOR.                                    |      |

|                | Single/Differential Output                        |      |

|                | ADC                                               |      |

|                | Modulation                                        |      |

|                | REFDIVOUT Reference Frequency Divided Output      |      |

|                | ister Map                                         |      |

| 14.1.          | Register Map                                      | 47   |

|                | Special Register Access                           |      |

| 14.3.          | Register Definitions                              |      |

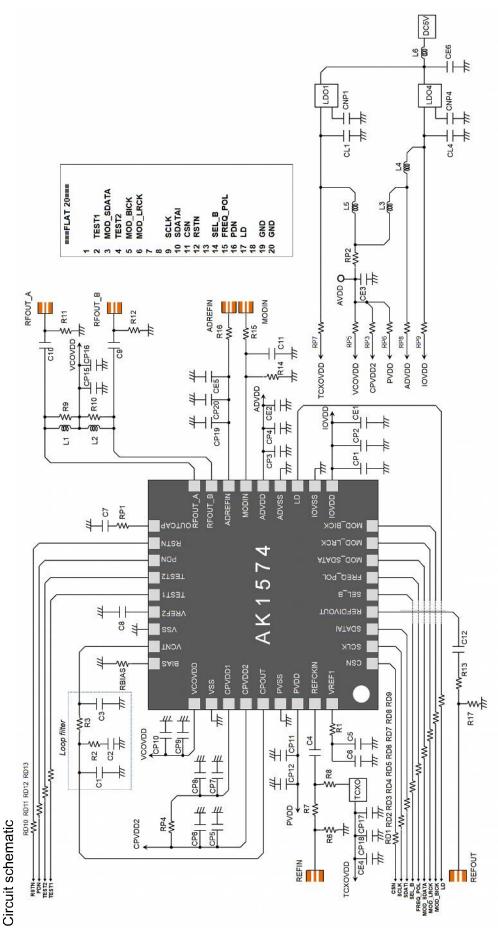

|                | ernal Circuits                                    |      |

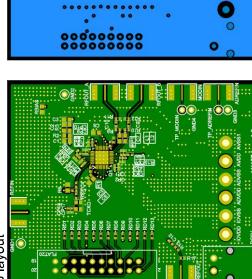

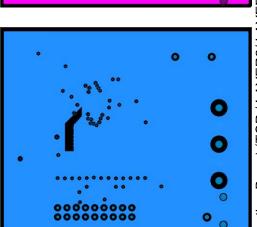

| 15.1.          | Reference Evaluation Board                        |      |

|                | PCB Design                                        |      |

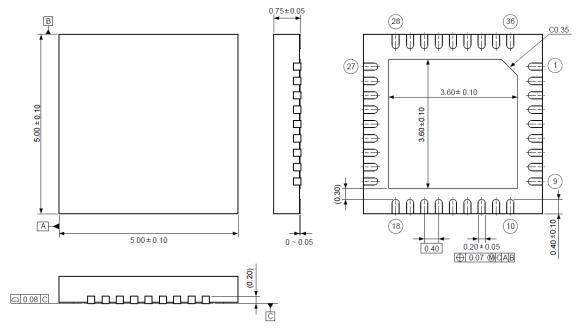

|                | kage                                              |      |

|                | Outline Dimensions                                |      |

|                | Markingering Guide                                | 65   |

|                |                                                   | . 1. |

| 18. Revision History | Asah | hi <b>KASEI</b>  | [AK1574] |

|----------------------|------|------------------|----------|

|                      | 18.  | Povision History | 65       |

## 5. Block Diagram and Functions

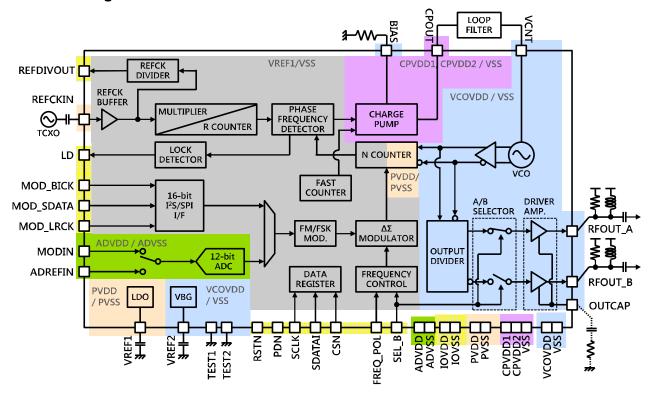

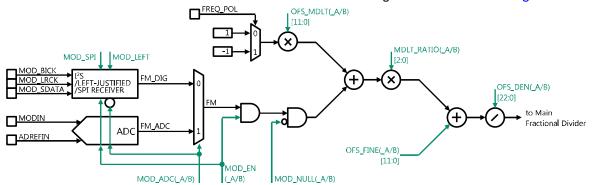

## 5.1. Block Diagram

Figure 5.1 AK1574 Block Diagram

## **Functions**

| Block                                    | Function                                                                                                                                                                                                                                                                                               |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REFCK BUFFER                             | Input signal of the REFCKIN pin is buffered and output                                                                                                                                                                                                                                                 |

| REFCK DIVIDER                            | Divide the output signal of the REFCK BUFFER. It is able to divide a signal into $4 \sim 1$ . The output clock of this block can be used as PLL synchronous system clock.                                                                                                                              |

| MULTIPLIER / R COUNTER                   | Multiplies M times the signal output from REFCK BUFFER and divides it by R, and outputs a signal to PHASE FREQUENCY DETECTOR (PFD).                                                                                                                                                                    |

| PHASE FREQUENCY DETECTOR (PFD)           | Output a signal according to the phase difference of two input signals.                                                                                                                                                                                                                                |

| CHARGE PUMP (CP)                         | Sink or Source a current according to the signal from the PFD.                                                                                                                                                                                                                                         |

| LOOP FILTER                              | External Loop Filter for PLL Stabilization AKM provides a PLL design tool for loop filter constant calculation. https://www.akm.com/akm/en/product/detail/0038/                                                                                                                                        |

| Voltage Controlled Oscillator (VCO)      | Oscillate in the corresponding frequency of the input voltage of the VCNT pin.                                                                                                                                                                                                                         |

| N COUNTER                                | Divide output signal from VCO by N and output it to PFD.                                                                                                                                                                                                                                               |

| ΔΣ MODULATOR                             | Control N COUNTER modulus and realize fractional dividing.                                                                                                                                                                                                                                             |

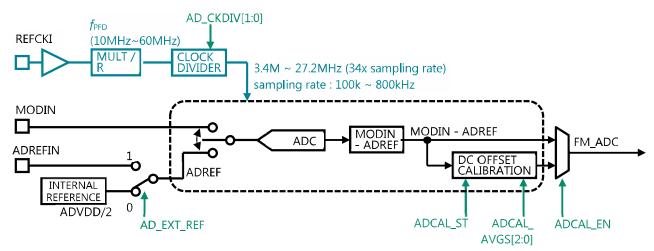

| 12-bit ADC (Analog to Digital Converter) | 12-bit ADC to receive analog sound data as modulated signal. Either this ADC or the digital I/F is available at one time.                                                                                                                                                                              |

| 16-bit I <sup>2</sup> S/SPI I/F          | Digital I/F to receive modulation data.  Either this digital I/F or the ADC is available at one time.                                                                                                                                                                                                  |

| FM/FSK MOD.                              | Control $\Delta\Sigma$ MODULATOR by inputting modulation data and modulate the output signal.                                                                                                                                                                                                          |

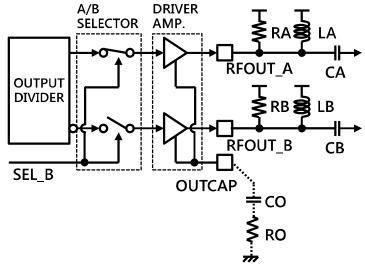

| OUTPUT DIVIDER                           | Divide VCO signal and output the signal to DRIVER AMP. It can divide the signal by 2, 4, 8, 16 and 32.                                                                                                                                                                                                 |

| A/B SELECTOR                             | Select an RF Output pin by selecting active DRIVER AMP.                                                                                                                                                                                                                                                |

| DRIVER AMP(A/B)                          | Buffer the signal from output divider and output. The output power can be changed by register setting. There are two output lines and output power can be selected independently for both lines. However, if the power is output from both lines, output power setting of both lines will be the same. |

| Low Dropout (LDO)                        | Built-in regulator outputs 1.9V. It cannot supply current externally.                                                                                                                                                                                                                                  |

| Voltage Bandgap (VBG)                    | Internal reference voltage is output. It cannot supply current externally.                                                                                                                                                                                                                             |

## 6. Pin Configurations and Functions

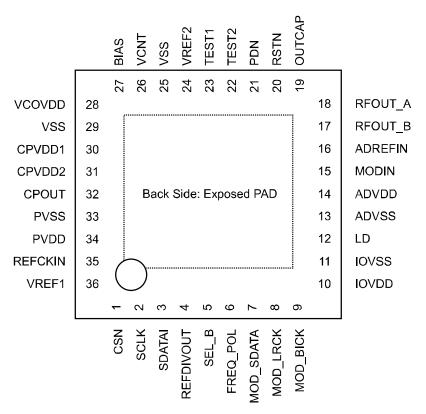

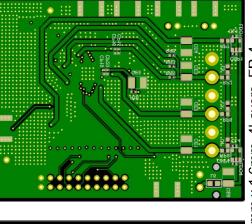

## 6.1. Pin Layout

Figure 6.1 Pin Layout (Top view)

#### 6.2. Pin Functions

Al: Analog Input Pin, AO: Analog Output Pin, DI: Digital Input Pin, DO: Digital Output Pin, P: Power Supply Pin, G: Ground Pin

All digital input pins must not be allowed to float.

Refer to 15.1 Reference Evaluation Board for the external element constant.

Table 6.1 Pin Functions

| Pin# | Pin Name  | I/O | Pin State<br>when PDN<br>pin="L"* 1 | Pin State<br>when RSTN<br>pin="L"* 2 | Function                                                                                                                                                                                             |  |

|------|-----------|-----|-------------------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1    | CSN       | DI  | Hi-Z                                | Hi-Z                                 | Chip Select Input for Serial Data                                                                                                                                                                    |  |

| 2    | SCLK      | DI  | Hi-Z                                | Hi-Z                                 | Clock Input for Serial Data                                                                                                                                                                          |  |

| 3    | SDATAI    | DI  | Hi-Z                                | Hi-Z                                 | Serial Data Input                                                                                                                                                                                    |  |

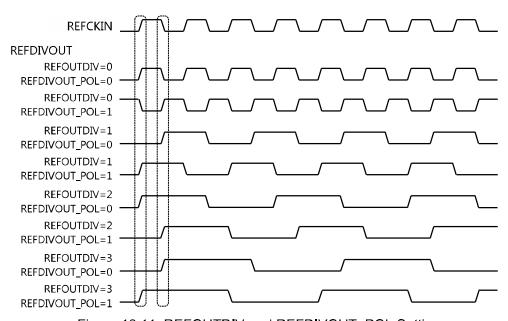

| 4    | REFDIVOUT | DO  | Low                                 | Low                                  | Divided Reference Clock Output                                                                                                                                                                       |  |

| 5    | SEL_B     | DI  | Hi-Z                                | Hi-Z                                 | Mode Switching Signal Input Valid only when SEL_B_BY_PIN bit = "1" "L": Operate in "Output Mode A". "H": Operate in "Output Mode B".                                                                 |  |

| 6    | FREQ_POL  | DI  | Hi-Z                                | Hi-Z                                 | Offset Frequency Polarity Switching Signal Input  "L": Frequency is set with normal polarity of  OFS_MDLT(_A/B) bit value  "H": Frequency is set with inverted polarity of  OFS_MDLT(_A/B) bit value |  |

| 7    | MOD_SDATA | D   | Hi-Z                                | Hi-Z                                 | I <sup>2</sup> S Input for Modulation Data                                                                                                                                                           |  |

| 8    | MOD_LRCK  | DI  | Hi-Z                                | Hi-Z                                 | I <sup>2</sup> S LR Clock Input for Modulation Data                                                                                                                                                  |  |

| 9    | MOD_BICK  | DI  | Hi-Z                                | Hi-Z                                 | I <sup>2</sup> S Bit Clock Input for Modulation Data                                                                                                                                                 |  |

| 10 | IOVDD   | Р  | -                          | -                          | Power Supply for Interface Circuit                                                                                                                                                                             |

|----|---------|----|----------------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11 | IOVSS   | G  | _                          | _                          | Interface Circuit Ground                                                                                                                                                                                       |

| 12 | LD      | DO | Low                        | Low                        | Lock Detection Flag Output  "L": Unlock  "H": Lock                                                                                                                                                             |

| 13 | ADVSS   | G  | -                          | -                          | ADC Ground                                                                                                                                                                                                     |

| 14 | ADVDD   | Р  | -                          | -                          | Power Supply for ADC                                                                                                                                                                                           |

| 15 | MODIN   | Al | Hi-Z                       | Hi-Z                       | Modulation Signal Input The pin capacitance is 7.7pF.                                                                                                                                                          |

| 16 | ADREFIN | Al | Hi-Z                       | Hi-Z                       | ADC Reference Voltage Input                                                                                                                                                                                    |

| 17 | RFOUT_B | AO | Hi-Z                       | Hi-Z                       | RF Signal Output B Open collector pin. Connect this pin to VDD1 via a resistor and an inductor.                                                                                                                |

| 18 | RFOUT_A | AO | Hi-Z                       | Hi-Z                       | RF Signal Output A Open collector pin. Connect this pin to VDD1 via a resistor and an inductor.                                                                                                                |

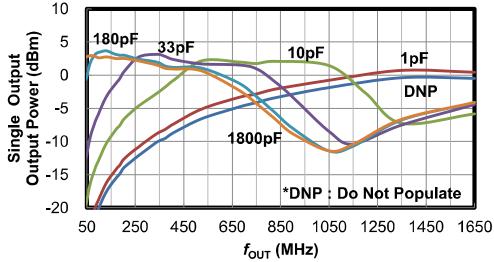

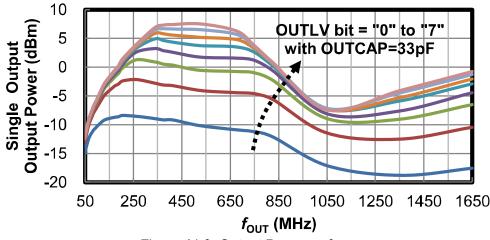

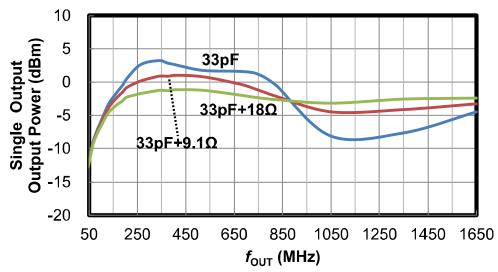

| 19 | OUTCAP  | AO | Hi-Z                       | Hi-Z                       | Stabilization Capacitor Connecting Pin for Driver Amplifier For Differential Output, leave this pin open. For Single Output, this pin should be connected to VSS via a capacitor according to RFOUT frequency. |

| 20 | RSTN    | DI | Hi <b>-</b> Z              | Hi-Z                       | Hardware Reset Signal Input The AK1574 is reset by "L" input of 1µs or more.                                                                                                                                   |

| 21 | PDN     | DI | Hi-Z                       | Hi-Z                       | Power Down Pin Valid only when PDN_BY_PIN bit = "1" "L": Power down blocks except LDO and VBG blocks. Register values will be kept. "H": Normal Operation                                                      |

| 22 | TEST2   | DI | 100kΩ<br>Pull down         | 100kΩ<br>Pull down         | TEST Mode Setting Pin Connect to VSS.                                                                                                                                                                          |

| 23 | TEST1   | DI | 100kΩ<br>Pu <b>ll</b> down | 100kΩ<br>Pu <b>ll</b> down | TEST Mode Setting Pin Connect to VSS.                                                                                                                                                                          |

| 24 | VREF2   | АО | Normal<br>Operation        | Normal<br>Operation        | Capacitor Connecting Pin for Noise Attenuation of Reference Voltage (VBG) Connect this pin to VSS via a 0.47µF capacitor.                                                                                      |

| 25 | VSS     | G  | * 3                        | * 3                        | Analog Ground                                                                                                                                                                                                  |

| 26 | VCNT    | Al | Hi-Z                       | Hi-Z                       | Voltage Input for Internal VCO Frequency Control                                                                                                                                                               |

| 27 | BIAS    | Al | Hi-Z                       | Hi-Z                       | Resistor Connecting Pin for Charge Pump Current Setting Connect this pin to VSS via an $18 \sim 33 \text{k}\Omega$ resistor.                                                                                   |

| 28 | VCOVDD  | Р  | -                          | -                          | Power Supply for Internal VCO                                                                                                                                                                                  |

| 29 | VSS     | G  | * 3                        | * 3                        | Analog Ground                                                                                                                                                                                                  |

| 30 | CPVDD1  | Р  | -                          | -                          | Power Supply for Charge Pump                                                                                                                                                                                   |

| 31 | CPVDD2  | Р  | -                          | -                          | Power Supply for Charge Pump                                                                                                                                                                                   |

| 32 | CPOUT   | AO | Hi-Z                       | Hi-Z                       | Charge Pump Output                                                                                                                                                                                             |

| 33 | PVSS    | G  | * 3                        | * 3                        | Digital Circuit Ground                                                                                                                                                                                         |

| 34 | PVDD    | Р  | -                          | -                          | Power Supply for Digital Circuit                                                                                                                                                                               |

| 35 | REFCKIN | Al | 25kΩ<br>Pull down          | 25kΩ<br>Pull down          | Reference Clock Input Connect a 1000pF capacitor to this pin. The pin capacitance is 2.2pF.                                                                                                                    |

| 36 | VREF1   | АО | Normal<br>Operation        | Normal<br>Operation        | Stabilization Capacitor Connecting Pin for LDO Connect this pin to VSS via 10µF capacitor.                                                                                                                     |

| -  | TAB     | G  | -                          | -                          | Exposed pad on the bottom surface of the package must be connected to VSS.                                                                                                                                     |

<sup>\* 1.</sup> This also applies to Power Down by register control. It corresponds to the Power Down Mode described in Table 14.1.

<sup>\* 2.</sup> Software reset by register control is also the same. For the reset operation, refer to 9.2 System Reset. \* 3. It is connected to the TAB internally.

## 6.3. Handling of Unused Pin

Unused I/O pins must be connected appropriately.

■ When Not Using Digital I/F for Modulation Signal Input

Table 6.2 Pin Connection when not Using Digital I/F for Modulation Signal Input

| No. | Pin Name  | I/O | Pin Connection   | Note |

|-----|-----------|-----|------------------|------|

| 7   | MOD_SDATA | DI  | Connect to IOVSS |      |

| 8   | MOD_LRCK  | DI  | Connect to IOVSS |      |

| 9   | MOD_BICK  | DI  | Connect to IOVSS |      |

■ When Not Using Analog Input for Modulation Signal Input

Table 6.3 Pin Connection when not Using Analog Input for Modulation Signal Input

| No. | Pin Name | I/O | Pin Connection   | Note                                     |

|-----|----------|-----|------------------|------------------------------------------|

| 13  | ADVSS    | G   | Connect to ADVSS |                                          |

| 14  | ADVDD    | Р   | Connect to ADVSS |                                          |

| 15  | MODIN    | Αl  | Open             |                                          |

| 16  | ADREFIN  | ΑI  | Open             | Including the case of AD_EXT_REF bit="0" |

■ When Not Using Each Function

Table 6.4 Pin Connection when not Using Functions Below

| No. | Pin Name  | I/O | Pin Connection                                           | Note                                                              |

|-----|-----------|-----|----------------------------------------------------------|-------------------------------------------------------------------|

| 4   | REFDIVOUT | DO  | Open                                                     | Not using the Reference Clock Dividing Output function            |

| 5   | SEL_B     | DI  | Connect to IOVSS                                         | Not using the Output Mode Switching Function by Pin               |

| 6   | FREQ_POL  | DI  | Connect to IOVSS                                         | Not using the Polarity Switching Function of the Offset Frequency |

| 12  | LD        | DO  | Open                                                     | Not using Lock Detection Function                                 |

| 17  | RFOUT_B   | АО  | Connect this pin to VDD1 via a resistor and an inductor. | Only Using RFOUT_A pin                                            |

| 18  | RFOUT_A   | АО  | Connect this pin to VDD1 via a resistor and an inductor. | Only Using RFOUT_B pin                                            |

| 21  | PDN       | DI  | Connect to IOVDD                                         | Not using the Power Down Function by Pin                          |

## 7. Absolute Maximum Ratings

Table 7.1 Absolute Maximum Ratings

(PVSS=ADVSS=IOVSS=VSS=0V; \* 4)

| Parameter                                      |                                                                                                             | Symbol            | Min. | Max.                 | Unit |

|------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------------------|------|----------------------|------|

| Power Supply                                   | VCOVDD pin<br>CPVDD1 pin<br>CPVDD2 pin<br>PVDD pin                                                          | VDD1              | -0.3 | 3.8                  | V    |

|                                                | ADVDD pin                                                                                                   | ADVDD             | -0.3 | 4.3                  | ٧    |

|                                                | IOVDD pin                                                                                                   | IOVDD             | -0.3 | 4.3                  | V    |

|                                                | REFCKIN pin                                                                                                 | V <sub>AIN1</sub> | -0.3 | VDD1+0.3<br>(≤ 3.8)  |      |

| Analog Input Voltage                           | MODIN pin<br>ADREFIN pin                                                                                    | V <sub>AIN2</sub> | -0.3 | ADVDD+0.3<br>(≤ 4.3) | V    |

|                                                | VCNT pin                                                                                                    | V <sub>AIN3</sub> | -0.3 | 2.5                  |      |

|                                                | TEST1 pin<br>TEST2 pin                                                                                      | V <sub>DIN1</sub> | -0.3 | VDD1+0.3<br>(≤3.8)   | V    |

| Digital Input Voltage                          | RSTN pin PDN pin SCLK pin SDATAI pin CSN pin MOD_BICK pin MOD_SDATA pin MOD_LRCK pin SEL_B pin FREQ_POL pin | V <sub>DIN2</sub> | -0.3 | IO∨DD+0.3<br>(≤4.3)  | V    |

| Input Current (Input pins except power supply) |                                                                                                             | I <sub>IN</sub>   | -10  | +10                  | mA   |

| Storage Temperature                            |                                                                                                             | T <sub>STG</sub>  | -55  | 125                  | °C   |

### Note:

WARNING: Operation at or beyond these limits may result in permanent damage to the device. Normal operation is not guaranteed at these extremes.

<sup>\* 4.</sup> All voltages are with respect to ground. PVSS, ADVSS, IOVSS and VSSs must be connected to the same ground.

## 8. Recommended Operating Conditions

Table 8.1 Recommended Operating Conditions

(PVSS=ADVSS=IOVSS=VSS=0V; \* 5)

| Parameter           | symbol | Min. | Тур. | Max. | Unit |

|---------------------|--------|------|------|------|------|

| Ambient Temperature | Та     | -40  |      | +85  | °C   |

|                     | VDD1   | 2.7  | 3.0  | 3.45 | V    |

| Power Supply        | ADVDD  | 2.7  | 3.0  | 3.6  | V    |

|                     | IOVDD  | 1.7  |      | 3.6  | V    |

#### Note:

WARNING: AKM assumes no responsibility for the usage beyond the conditions in the datasheet.

## 9. Digital Characteristics

## 9.1. DC Characteristics

Table 9.1 Digital DC Characteristics

| Parameter            |                                              | Symbol           | Min.       | Тур. | Max.       | Unit |  |  |

|----------------------|----------------------------------------------|------------------|------------|------|------------|------|--|--|

| High Input Voltage   | * 6                                          | V <sub>IH</sub>  | 0.8×IOVDD  |      |            | V    |  |  |

| Low Input Voltage    | * 6                                          | V <sub>IL</sub>  |            |      | 0.2×IOVDD  | V    |  |  |

| High Input Current 1 | V <sub>IH</sub> =IOVDD=3.6V, * 6             | I <sub>IH1</sub> | -1         |      | +1         | μΑ   |  |  |

| High Input Current 2 | V <sub>IH</sub> =IOVDD=3.6V, * 7             | I <sub>IH2</sub> | +18        | +36  | +72        | μΑ   |  |  |

| Low Input Current    | V <sub>IL</sub> =0V, <b>I</b> OVDD=3.6V, * 6 | I <sub>IL</sub>  | -1         |      | +1         | μΑ   |  |  |

| High Output Voltage  | I <sub>OH</sub> =+500μA, * 8                 | V <sub>OH</sub>  | 0.85×IOVDD |      |            | V    |  |  |

| Low Output Voltage   | <b>I</b> <sub>OL</sub> =-500μA, * 8          | $V_{OL}$         |            |      | 0.15×IOVDD | V    |  |  |

Regarding the input current, the direction in which the current flows into the IC is defined as + and the direction in which the current flows out from the IC is defined as -.

#### Notes

- \* 6. RSTN, PDN, SCLK, SDATAI, CSN, MOD\_BICK, MOD\_SDATA, MOD\_LRCK, SEL\_B and FREQ\_POL pins

- \* 7. TEST1 and TEST2 pins

- \* 8. LD and REFDIVOUT pins

<sup>\* 5.</sup> All voltages are with respect to ground. PVSS, ADVSS, IOVSS and VSSs must be connected to the same ground.

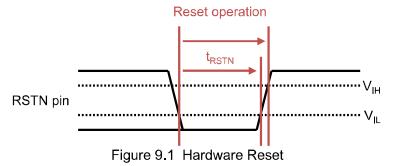

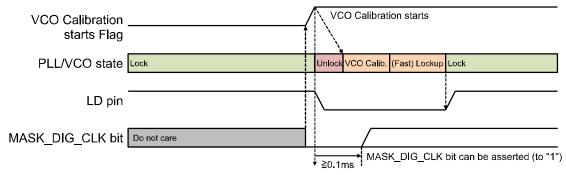

## 9.2. System Reset

#### Hardware Reset

| Parameter                         | Symbol   | Min.              | Тур. | Max. | Unit |    |

|-----------------------------------|----------|-------------------|------|------|------|----|

| Hardware Reset Signal Input Width | RSTN pin | t <sub>RSTN</sub> | 1    |      |      | μs |

Hardware reset is executed by inputting "L" for 1µs or longer to the RSTN pin. All internal statuses including VCO calibration and ADC DC offset calibration are initialized by the hardware reset and the registers are set to their initial value. Therefore all operational settings should be made after this reset. Refer to 14.1 Register Map for the initial value of the register.

For a certain reset of the device, inputs of the SCLK, the SDATAI and the CSN pins should be fixed to "L" or "H" during reset and reset release timings.

#### Software Reset

Software reset is executed by writing Address 0x2B bit[7:0]: SW\_RST bit="0100 1010". All internal statuses including VCO calibration and ADC DC offset calibration are initialized by this reset and the registers are set to their initial value. Therefore all operational settings should be made after this reset. Software reset operation is the same as hardware reset operation.

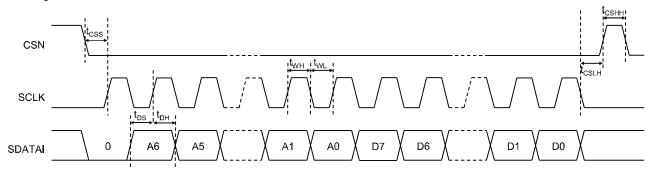

## 9.3. Serial Interface Timing for Register Accessing

Register data is written to the AK1574 via 3-wire serial interface (SCLK, SDATAI and CSN pins). Register read function is for test purpose only. So it is not described in this document. Input data of the SDATAI pin consists of MSB "0" data, 7 bits register address (MSB first, A6 to A0) and 8 bits register data (MSB first, D7 to D0) in total 16 bits (Figure 9.2).

## ■ Register Write

MSB : Set to "0"

A6~A0 : Register address to access

D7~D0: Written data

Figure 9.2 Register Access Timing

- 1. Set the CSN pin to "H" when there is no register access. Input clock and data are ignored when the CSN pin = "H". Serial interface is activated by setting the CSN pin = "L".

- 2. When the CSN pin = "L", the input address and data of the SDATAI pin is stored in this order by synchronizing to a rising edge of 16 clocks of the SCLK pin. The input data is fixed on a rising edge of the 16th clock. The CSN pin should be set back to "H" every time SDATAI data is written.

- 3. Input data is invalid if the CSN pin is turned to "H" before the clock count reaches 16. If the clock input is kept after 16 cycles while the CSN pin = "L", input clock and data after the 16th clock are also ignored.

Table 9.2 Register Access AC Timing

| Parameter          | Symbol            | Min. | Тур. | Max. | Unit |

|--------------------|-------------------|------|------|------|------|

| SCLK Frequency     | f <sub>SCLK</sub> |      |      | 12.5 | MHz  |

| CSN setup time     | t <sub>CSS</sub>  | 40   |      |      | ns   |

| SDATAI setup time  | t <sub>DS</sub>   | 20   |      |      | ns   |

| SDATAI hold time   | t <sub>DH</sub>   | 20   |      |      | ns   |

| SCLK high time     | t <sub>WH</sub>   | 40   |      |      | ns   |

| SCLK low time      | t <sub>WL</sub>   | 40   |      |      | ns   |

| CSN low hold time  | t <sub>CSLH</sub> | 20   |      |      | ns   |

| CSN high hold time | t <sub>CSHH</sub> | 40   |      |      | ns   |

<sup>\*</sup> Digital input timing refers 0.5×IOVDD of rising/falling edge of the SCLK clock.

## 9.4. Serial Interface Timing of Modulation Signal Input

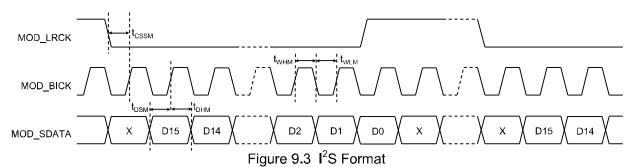

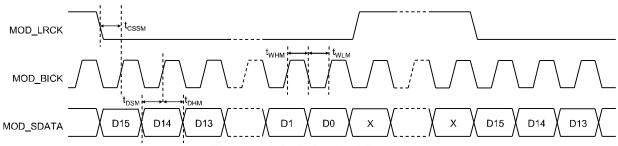

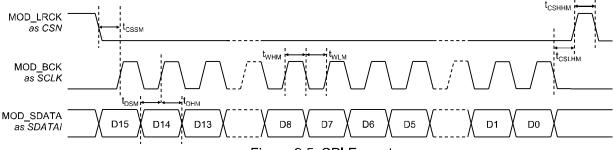

Modulation signal is input to the AK1574 via 3-wire serial interface (MOD\_BICK, MOD\_SDATA and MOD\_LRCK pins). Input data format can be selected from Left-Justified, I<sup>2</sup>S or SPI by setting MOD\_SPI bit and MOD\_LEFT bit. MOD\_LRCK frequency equals to the sampling range of a modulation signal. Refer to 13.10 Modulation for the selection of the writing format of the digital modulation signal.

Input data of the MOD\_SDATA pin consists of 16 bits (2's complement, MSB first, D15-D0) and it is written in synchronization of a rising edge of a bit clock from the MOD\_BICK pin. After the MOD\_LRCK pin status is changed to "L" from "H", MSB data is written on the first rising edge of the bit clock if the data is in Left-Justified and SPI formats, and MSB data is written on the second rising edge of the bit clock if the data is in I<sup>2</sup>S format as shown in Figure 9.3 ~ Figure 9.5. Input data is fixed on the 15th rising edge of the bit clock after writing MSB data (when LSB is written).

Input data is invalid if the "L" period of the MOD\_LRCK pin is shorter than 16 cycles of the bit clock. When "L" period of the MOD\_LRCK is longer than 16 cycles, input data is valid for first 16 bits including MSB. Necessary "H" period of MOD\_LRCK in Left-Justified or I<sup>2</sup>S format is only 1 cycle of the bit clock.

## I<sup>2</sup>S After a falling edge of LR clock, MSB is written in second bit. (delays one bit as Left-justified)

## Left-Justified MSB is written as soon as LR clock falls.

## Figure 9.4 Left-Justified Format SPI

# MOD\_BICK is stopped when Left-Justified MOD\_LRCK = "H". Even if MOD\_BICK is input when MOD\_LRCK = "H", operation is not affected.

Figure 9.5 SPI Format

Table 9.3 Modulation Signal AC Timing

| Parameter                       | Symbol             | Min. | Тур. | Max. | Unit |

|---------------------------------|--------------------|------|------|------|------|

| MOD BICK Frequency              | f <sub>BICK</sub>  |      |      | 12.5 | MHz  |

| MOD_SDATA / MOD_LRCK setup time | t <sub>DSM</sub>   | 20   |      |      | ns   |

| MOD_SDATA / MOD_LRCK hold time  | $t_{DHM}$          | 20   |      |      | ns   |

| MOD_BICK high time              | t <sub>WHM</sub>   | 40   |      |      | ns   |

| MOD_BICK low time               | $t_{WLM}$          | 40   |      |      | ns   |

| CSN low hold time               | t <sub>CSLHM</sub> | 20   |      |      | ns   |

| CSN high hold time              | t <sub>CSHHM</sub> | 20   |      |      | ns   |

| CSN setup time                  | t <sub>CSSM</sub>  | 20   |      |      | ns   |

## 10. Analog Characteristics

(Ta= -40  $\sim$  +85°C; VDD1= 2.7  $\sim$  3.45V, ADVDD=2.7  $\sim$  3.6V, IOVDD=1.7  $\sim$  3.6V; Connect the BIAS pin to VSS via a 27k $\Omega$  resistor; Test circuit is shown in 15.1 Reference Evaluation Board, unless otherwise specified)

Table 10.1 Analog Characteristics

|                             |                | Table 10.1                | Analog Char                    | acteristics              | ı      |                                                                                                                 |  |  |

|-----------------------------|----------------|---------------------------|--------------------------------|--------------------------|--------|-----------------------------------------------------------------------------------------------------------------|--|--|

| Par                         | ameter         | Min.                      | Тур.                           | Max.                     | Unit   | Description                                                                                                     |  |  |

|                             | REFCK BUFFER   |                           |                                |                          |        |                                                                                                                 |  |  |

| Input Sensitivity           |                | 0.2                       |                                | VDD1                     | Vp-p   | REFCKIN pin                                                                                                     |  |  |

| Operating Fre               | quency Range   | 10                        |                                | 60                       | MHz    | $f_{REF}$                                                                                                       |  |  |

|                             |                |                           | MULTIPLIER                     |                          |        |                                                                                                                 |  |  |

| Operating Fre               | quency Range   | 350                       |                                | 505                      | MHz    | f <sub>MULTI</sub> : f <sub>REF</sub> * MULT                                                                    |  |  |

|                             |                |                           | PFD                            |                          |        |                                                                                                                 |  |  |

| Operating Fre               | quency Range   | 10                        |                                | 60                       | MHz    | $f_{PFD}$ :<br>PFD Frequency                                                                                    |  |  |

|                             |                | CI                        | HARGE PUMI                     | )                        |        |                                                                                                                 |  |  |

| CP External For Current Ac  |                | 18                        | 27                             | 33                       | kΩ     | Connected to BIAS pin                                                                                           |  |  |

|                             | •              |                           | 1200                           |                          | μA     | ·                                                                                                               |  |  |

| OD 0                        |                |                           | 900                            |                          | μA     | 4 levels by                                                                                                     |  |  |

| CP Current                  |                |                           | 600                            |                          | μΑ     | ICP_FAST bit ICP_NORM bit                                                                                       |  |  |

|                             |                |                           | 300                            |                          | μA     | TOT _IVOTAWI BIL                                                                                                |  |  |

|                             |                |                           | VCO                            |                          |        |                                                                                                                 |  |  |

| Operating Fre               |                |                           |                                | 2100                     | MHz    | LVCO                                                                                                            |  |  |

| Operating Fre               | quency Range   | 2100                      |                                | 3365                     | MHz    | HVCO                                                                                                            |  |  |

| VCO Tuning S                | Sensitivity    |                           | 0.02 × f <sub>VCO</sub>        |                          | MHz/V  | f <sub>VCO</sub> :<br>Oscillation Frequency                                                                     |  |  |

| Acquisition Fr              | equency Range  | -0.001 × f <sub>VCO</sub> |                                | 0.001 × f <sub>VCO</sub> | MHz    |                                                                                                                 |  |  |

|                             |                |                           | put Characte<br>ferential Outp | ristics                  |        |                                                                                                                 |  |  |

|                             |                |                           | e A) / (mod<br>" / Ol          |                          |        |                                                                                                                 |  |  |

|                             | 6.25kHz Offset | LO_A bit- 1               | -124                           | <u> </u>                 |        |                                                                                                                 |  |  |

|                             | 12.5kHz Offset |                           | -125                           |                          |        |                                                                                                                 |  |  |

| Phase Noise                 | 25kHz Offset   |                           | -125                           |                          |        |                                                                                                                 |  |  |

| at 420MHz                   | 50kHz Offset   |                           | -125                           |                          | dBc/Hz |                                                                                                                 |  |  |

| * 11                        | 100kHz Offset  |                           | -124                           |                          |        |                                                                                                                 |  |  |

|                             | 225kHz Offset  |                           | -124                           |                          |        |                                                                                                                 |  |  |

|                             | 1MHz Offset    |                           | -139                           |                          |        |                                                                                                                 |  |  |

| Normalized Phase Noise * 11 |                |                           | -221                           |                          | dBc/Hz | FoM= -20×log <sub>10</sub> (f <sub>OUT</sub> /f <sub>PFD</sub> ) -10×log <sub>10</sub> (f <sub>PFD</sub> ) + CN |  |  |

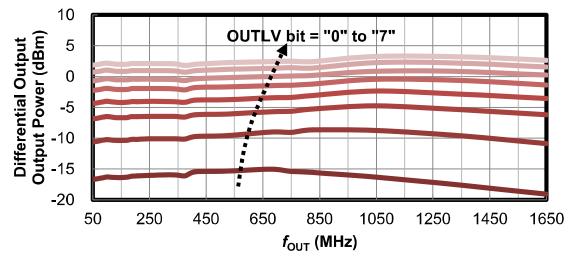

|                             |                |                           | 3                              |                          | dBm    | OUTLV(_A/B) bit<br>="111"                                                                                       |  |  |

| Output Power                |                | _                         | -3                             |                          | dBm    | ="011"                                                                                                          |  |  |

| at 520.1MHz                 |                |                           | <b>-</b> 9                     |                          | dBm    | ="001"                                                                                                          |  |  |

|                             |                |                           | -15                            |                          | dBm    | ="000"                                                                                                          |  |  |

|                                              | 1050         |              | 1682.5    | MHz | HVCO, DIV2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------------------|--------------|--------------|-----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                              | 750          |              | 1050      | MHz | LVCO, DIV2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                              | 525          |              | 841.25    | MHz | HVCO, DIV4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                              | 375          |              | 525       | MHz | LVCO, DIV4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Output Frequency Range                       | 262.5        |              | 420.625   | MHz | HVCO, DIV8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| * 12                                         | 187.5        |              | 262.5     | MHz | LVCO, DIV8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                              | 131.25       |              | 210.312   | MHz | HVCO, D <b>I</b> V16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                              | 93.75        |              | 131.25    | MHz | LVCO, DIV16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                              | 65.625       |              | 105.156   | MHz | HVCO, DIV32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

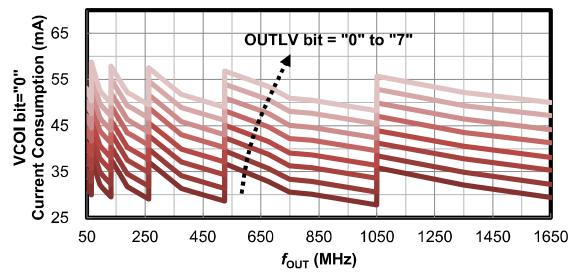

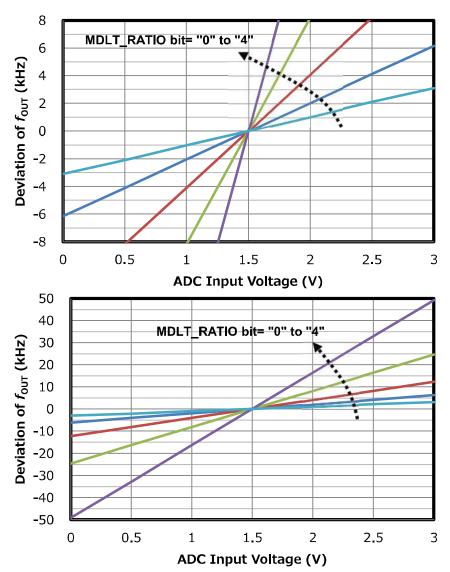

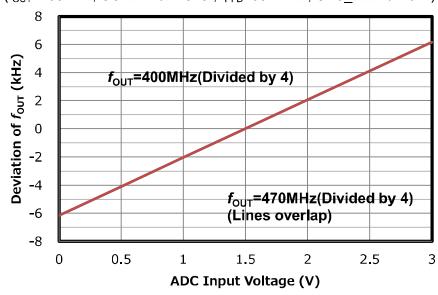

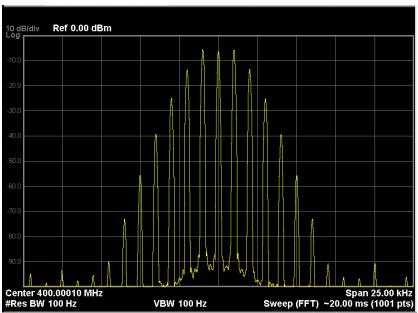

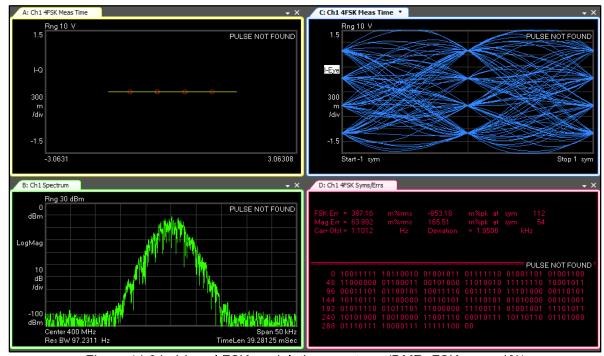

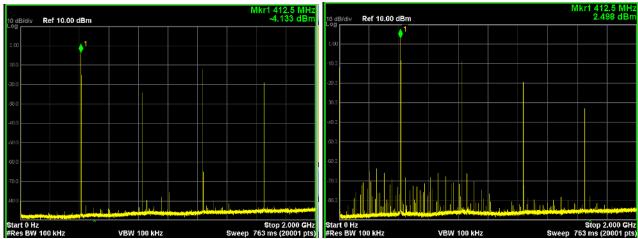

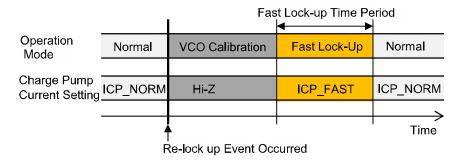

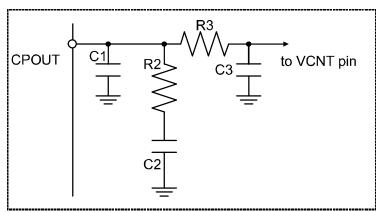

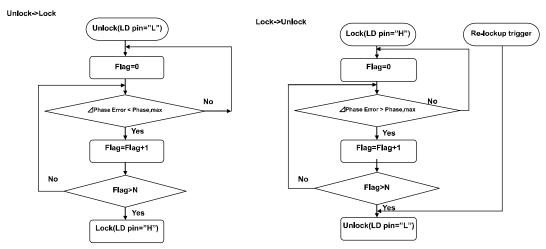

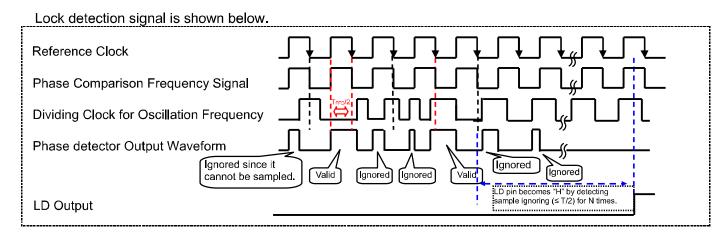

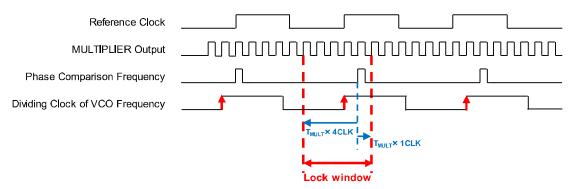

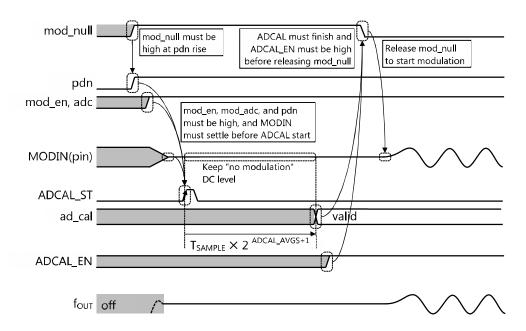

|                                              | 46.875       |              | 65.625    | MHz | LVCO, DIV32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |