## **AK4161**

## 6-channel Capacitive Touch Sensor IC

#### GENERAL DESCRIPTION

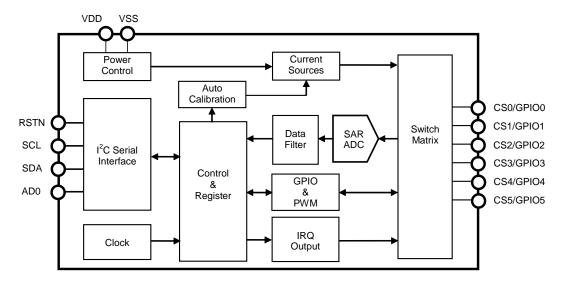

The AK4161 is a low operating voltage and low power consumption 6-channel capacitive touch sensor. Maximum 6 input channels can be configured to LED drive or GPIO. 2 channels out of 6-channel can also be configured to interrupt output. The AK4161 has a channel independent automatic correct function of environmental drifts for each sense input. It reduces false detection by continuous calibration of the internal reference value in the situation when the input capacitance of the touch switch is changed by the external factors such as hydrothermal conditions. The automatic initial setting function sets the charge current and charge time according to the size and the shape of a touch switch. Even more, a noise filter and a false protection filter are integrated. The AK4161 can be configured via serial interfaces, it is suitable for mobile phones, PCs and home electric applications.

#### **FEATURE**

- Up to 6 capacitive sensor inputs

- Up to 6 general purpose inputs/outputs with PWM control for LED

- Selectable 2 interrupt outputs

- Automatic initial setting function for the charge current and time

- Independent automatic environmental drifts correct function for each sense terminal

- Independent threshold configuration for each sense terminal

- Selectable multi touch feature

- Integrated Median Averaging Filter

- Data Update Stop Function for Noisy Environment

- Reset Input pin

- I<sup>2</sup>C Serial Interface

- 10 bit SAR A/D Converter with S/H circuit

- Integrated Regulator

- Low Power Consumption:

Typ. 4.1uA (Sampling rate=512ms, 6ch Sensor input, VDD=3.3V, N1S=20)

Typ. 177uA (Sampling rate=1ms, 6ch Sensor input, VDD=3.3V, N1S=6)

- Power Down Current: Typ. 1.2uA

- Low Power Operation: VDD = 1.6V ~ 3.6V

- Operating Temperature: Ta = -40 ~ 85 °C

- Package: 16pin QFN (3mm x 3mm, pitch 0.5mm)

I<sup>2</sup>C-bus is a trademark of NXP B.V.

Figure 1. Block Diagram

#### **■** Ordering Guide

AK4161EN  $-40 \sim +85$ °C 16pin QFN (3mm x 3mm, 0.5mm pitch) AKD4161 AK4161EN Evaluation Board

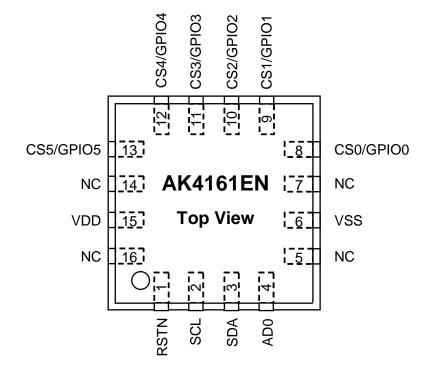

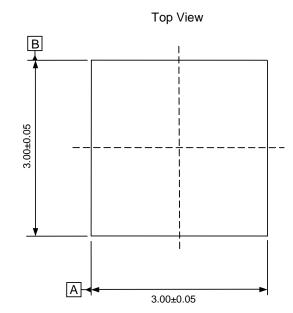

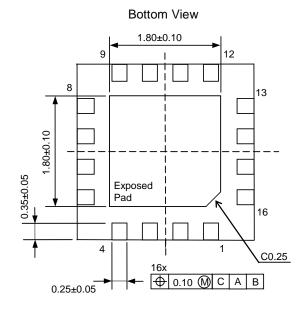

## **■** Pin Layout

## PIN/FUNCTION

| Pin No. | Pin Name    | Type (Note 1) | I/O<br>(Note 2) | Function                                   | Reset State<br>RSTN = "L" |

|---------|-------------|---------------|-----------------|--------------------------------------------|---------------------------|

| 1       | RSTN        | D             | I               | Reset Pin (Active Low)                     | -                         |

| 2       | SCL         | D             | I               | I <sup>2</sup> C Serial Clock Input        | -                         |

| 3       | SDA         | D             | I/O             | I <sup>2</sup> C Serial Data Input/ Output | Hi-z                      |

| 4       | AD0         | D             | I               | I <sup>2</sup> C Slave Address Bit 0       | -                         |

| 6       | VSS         | GND           | -               | Ground                                     | -                         |

| 8       | CS0 / GPIO0 | A/D           | I/O             | Cap Sense / GPIO Pin0                      | Hi-z                      |

| 9       | CS1 / GPIO1 | A/D           | I/O             | Cap Sense / GPIO Pin1                      | Hi-z                      |

| 10      | CS2 / GPIO2 | A/D           | I/O             | Cap Sense / GPIO Pin2                      | Hi-z                      |

| 11      | CS3 / GPIO3 | A/D           | I/O             | Cap Sense / GPIO Pin3                      | Hi-z                      |

| 12      | CS4 / GPIO4 | A/D           | I/O             | Cap Sense / GPIO Pin4 with IRQN            | Hi-z                      |

| 13      | CS5 / GPIO5 | A/D           | I/O             | Cap Sense / GPIO Pin5 with IRQN            | Hi-z                      |

| 15      | VDD         | PWR           | -               | Power Supply: 1.6V ~ 3.6V                  | -                         |

| 5       | NC          | -             | -               | No Connection                              | -                         |

| 7       |             |               |                 | No internal bonding. This pin must be      |                           |

| 14      |             |               |                 | connected to VSS.                          |                           |

| 16      |             |               |                 |                                            |                           |

Note 1. A (Analog terminal), D (Digital terminal), GND (Ground), PWR (Power)

## ■ Handling of Unused Pins

The unused I/O pins must be connected appropriately.

|   | Classification | Pin Name                            | Setting                                            |

|---|----------------|-------------------------------------|----------------------------------------------------|

| Λ | Analog/Digital | og/Digital CS0 / GPIO0 ~ CS5/ GPIO5 | Pin Connection: Connect to VSS.                    |

|   | Analog/Digital |                                     | Register Setting: FUNC (Addr: $0x1F-0x20$ ) = "00" |

Note 2. I (Input terminal), O (Output terminal)

Note 3. All digital input pins (SCL, SDA, AD0, RSTN) must not be allowed to float.

#### **ABSOLUTE MAXIMUM RATINGS**

(VSS = 0V (Note 4))

| Parameter                                | Symbol  | min  | max            | Unit |

|------------------------------------------|---------|------|----------------|------|

| Power Supply                             | VDD     | -0.3 | 4.3            | V    |

| Input Current Any Pins except for supply | IIN     | -    | ±10            | mA   |

| GPIO Source Current per Pin              | Isource | -    | 12             | mA   |

| GPIO Sink Current per Pin                | Isink   | -    | 1.2            | mA   |

| Input Voltage (Note 5)                   | VIN     | -0.3 | VDD+0.3 or 4.3 | V    |

| Ambient Temperature (power applied)      | Ta      | -40  | 85             | °C   |

| Storage Temperature                      | Tstg    | -65  | 150            | °C   |

Note 4. All voltages with respect to ground.

Note 5. For SDA, SCL, AD0, RSTN, CS0/GPIO0 ~ CS5/GPIO5 pins. The maximum value is smaller value between (VDD+0.3)V and 4.3V.

WARNING: Operation at or beyond these limits may result in permanent damage to the device. Normal operation is not guaranteed at these extremes.

| RECOMMEND OPERATING CONDITIONS   |  |  |  |

|----------------------------------|--|--|--|

| DECOMMEND ODED A LING COMMINIONS |  |  |  |

|                                  |  |  |  |

|                                  |  |  |  |

(VSS = 0V (Note 4))

| Parameter    | Symbol | min | typ | max | Unit |

|--------------|--------|-----|-----|-----|------|

| Power Supply | VDD    | 1.6 | 3.3 | 3.6 | V    |

Note 4. All voltages with respect to ground.

WARNING: AKM assumes no responsibility for the usage beyond the conditions in this datasheet.

#### **ANALOG CHARACTERISTICS**

$(Ta = -40^{\circ}C \sim 85^{\circ}C, VDD = 3.3V; unless otherwise specified)$

| Parameter                                               | Symbol | min | typ   | max | Unit |

|---------------------------------------------------------|--------|-----|-------|-----|------|

| A/D Converter                                           |        |     |       |     |      |

| Resolution                                              | RESO   | -   | 10    | -   | Bits |

| Touch Sensor                                            |        |     |       |     |      |

| Charge Current Variation Against Nominal Value (Note 6) | ICHG   | -30 | -     | 30  | %    |

| Power Supply Current                                    | •      |     | •     |     | •    |

| Measurement Current (All function in active)            | IMEAS  | -   | 0.765 | -   | mA   |

| Idle Current                                            | IIDLE  | -   | 3.15  | -   | uA   |

| Average Supply Current (Note 7)                         | IDD    |     |       |     |      |

| TSR = 0.25 ms                                           |        | -   | 687   | -   | uA   |

| TSR= 0.5ms                                              |        | -   | 351   | -   | uA   |

| TSR= 1ms                                                |        | -   | 177   | -   | uA   |

| TSR= 2ms                                                |        | -   | 90    | -   | uA   |

| TSR = 4ms                                               |        | -   | 47    | -   | uA   |

| TSR=8ms                                                 |        | -   | 25    | -   | uA   |

| TSR=16ms                                                |        | -   | 14    | -   | uA   |

| TSR=32ms                                                |        | -   | 9     | -   | uA   |

| TSR=2ms, 20 samplings at 1st order Filter               |        | -   | 489   | -   | uA   |

| TSR=32ms, 20 samplings at 1st order Filter              |        | -   | 18    | -   | uA   |

| TSR=512ms, 20 samplings at 1st order Filter             |        | -   | 4.1   | -   | uA   |

| Shutdown Current, ACT= "0" (Shutdown Mode)              | ISHUT  | -   | 1.2   | 8.0 | uA   |

Note 6. Sense terminal voltage condition: The AD conversion value should be less or equal to VDD-0.2[V]. (It should be less or equal to VDD-0.3[V] when CC2Xn bit="1") The charge current is dependent on the operating voltage, and is configured by register settings in the range of "0.556 x VDD [uA]" to "70.056 x VDD [uA]".

Note 7. Measurement Condition: 6 active sense terminals, 2us charge period, 6 samplings at 1st order filter for noise cancelling, using sense terminal with 22pF capacitance.

## DC CHARACTERISTICS (Logic I/O)

$(Ta = -40^{\circ}C \sim 85^{\circ}C, VDD = 1.6V \sim 3.6V; unless otherwise specified)$

| Parameter                                        | Symbol | min              | typ | max     | Unit |

|--------------------------------------------------|--------|------------------|-----|---------|------|

| Input Leakage Current (Note 8)                   | IILH   | -5               | -   | 5       | uA   |

| Tri-state Leakage Current (Note 9)               | IOLK   | -5               | -   | 5       | uA   |

| Input High Voltage (Note 10)                     | VIH    | $0.7 \times VDD$ | ı   | -       | V    |

| Input Low Voltage (Note 10)                      | VIL    | =                | -   | 0.3×VDD | V    |

| Output High Voltage (Note 11) (Note 12) Io=-10mA | VOHF   | VDD-0.5          | -   | -       | V    |

| Output High Voltage (Note 11) (Note 13) Io=-1mA  | VOH    | VDD-0.3          | -   | -       | V    |

| Output Low Voltage (Note 10) (Note 13) Io=1mA    | VOL    | -                | -   | 0.3     | V    |

| Output Low Voltage (Note 14) Io=3mA              | VOLI2C | =                | -   | 0.3     | V    |

Note 8. RSTN pin

Note 9. AD0, SCL, SDA, GPIO0~GPIO5 pins

Note 10. GPIO0 ~ GPIO5 pins (FUNCn 1-0 bits = "01", GPIO input setting) Note 11. GPIO0 ~ GPIO5 pins (FUNCn 1-0 bits = "10", GPIO output setting) Note 12. Full Drive Operation (Output Driver Setting: DRVn1-0 bits = "11")

Note 13. Normal Drive Operation (Output Driver Setting: DRVn1-0 bits = "00", "01", "10")

Note 14. SDA pin

#### **SWITCHING CHARACTERISTICS**

$(Ta = -40^{\circ}C \sim 85^{\circ}C, VDD = 1.6V \sim 3.6V; unless otherwise specified)$

| Parameter                                                                    | Symbol    | min | typ | max | Unit |

|------------------------------------------------------------------------------|-----------|-----|-----|-----|------|

| Internal Oscillator                                                          |           |     |     |     |      |

| Fast Oscillator Period                                                       | FPRD      | 75  | 125 | 175 | ns   |

| Slow Oscillator Period                                                       | SPRD      | 21  | 32  | 43  | us   |

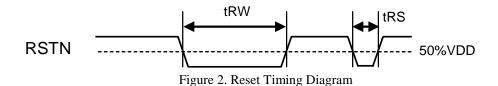

| Reset Timing                                                                 |           |     |     |     |      |

| Reset Pulse Width (Note 15)                                                  | tRW       | 10  | -   | -   | us   |

| Reset Pin Pulse Width of Spike Noise<br>Suppressed by Input Filter (Note 16) | tRS       | 0.5 | -   | -   | us   |

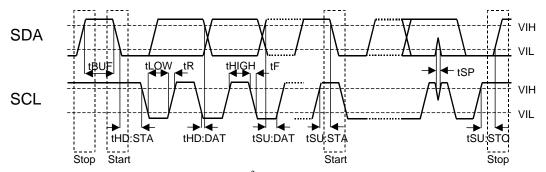

| 12C                                                                          |           | •   |     | •   |      |

| SCL clock frequency                                                          | $f_{SCL}$ | -   | -   | 400 | kHz  |

| Bus Free Time Between Transmissions                                          | tBUF      | 1.3 | -   | -   | us   |

| Start Condition Hold Time (prior to first Clock pulse)                       | tHD:STA   | 0.6 | -   | -   | us   |

| Clock Low Time                                                               | tLOW      | 1.3 | -   | -   | us   |

| Clock High Time                                                              | tHIGH     | 0.6 | -   | -   | us   |

| Setup Time for Repeated Start Condition                                      | tSU:STA   | 0.6 | -   | -   | us   |

| SDA Hold Time from SCL Falling (Note 17)                                     | tHD:DAT   | 0   | -   | =   | us   |

| SDA Setup Time from SCL Rising                                               | tSU:DAT   | 0.1 | -   | -   | us   |

| Rise Time of Both SDA and SCL Lines                                          | tR        | -   | -   | 0.3 | us   |

| Fall Time of Both SDA and SCL Lines                                          | tF        | -   | -   | 0.3 | us   |

| Setup Time for Stop Condition                                                | tSU:STO   | 0.6 | -   | -   | us   |

| Pulse Width of Spike Noise Suppressed By Input Filter                        | tSP       | 50  | -   | -   | ns   |

| Capacitive load on bus                                                       | Cb        | -   | -   | 400 | pF   |

Note 15. The AK4161 can be reset by the RSTN pin = "L". Keep "L" period for 10us or more for a certain reset.

Note 16. Pulse width of spike noise suppressed by input filter of the RSTN pin.

Note 17. Data must be held for sufficient time to bridge the 300ns transition time of SCL.

Figure 3. I<sup>2</sup>C Interface Timing Diagram

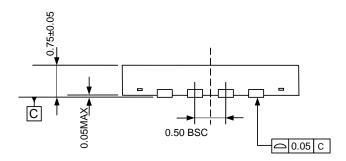

## **PACKAGE**

# 16pin QFN (Unit: mm)

Note: The thermal die pad must be connected to open node.

#### ■ Package & Lead frame material

Package molding compound: Epoxy Resin, Halogen (Br, Cl) Free

Lead frame material: Cu Alloy

Lead frame surface treatment: Solder (Pb free) Plate

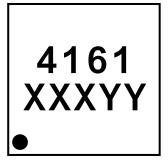

## MARKING

Contents of XXXYY XXX: Date Code

YY: Internal Control Code

Pin #1 indication

#### **IMPORTANT NOTICE**

- These products and their specifications are subject to change without notice.

When you consider any use or application of these products, please make inquiries the sales office of Asahi Kasei Microdevices Corporation (AKM) or authorized distributors as to current status of the products.

- Descriptions of external circuits, application circuits, software and other related information contained in this document are provided only to illustrate the operation and application examples of the semiconductor products. You are fully responsible for the incorporation of these external circuits, application circuits, software and other related information in the design of your equipments. AKM assumes no responsibility for any losses incurred by you or third parties arising from the use of these information herein. AKM assumes no liability for infringement of any patent, intellectual property, or other rights in the application or use of such information contained herein.

- Any export of these products, or devices or systems containing them, may require an export license or other official

approval under the law and regulations of the country of export pertaining to customs and tariffs, currency exchange,

or strategic materials.

- AKM products are neither intended nor authorized for use as critical components<sub>Note1)</sub> in any safety, life support, or

other hazard related device or system<sub>Note2)</sub>, and AKM assumes no responsibility for such use, except for the use

approved with the express written consent by Representative Director of AKM. As used here:

- Note1) A critical component is one whose failure to function or perform may reasonably be expected to result, whether directly or indirectly, in the loss of the safety or effectiveness of the device or system containing it, and which must therefore meet very high standards of performance and reliability.

- Note2) A hazard related device or system is one designed or intended for life support or maintenance of safety or for applications in medicine, aerospace, nuclear energy, or other fields, in which its failure to function or perform may reasonably be expected to result in loss of life or in significant injury or damage to person or property.

- It is the responsibility of the buyer or distributor of AKM products, who distributes, disposes of, or otherwise places the product with a third party, to notify such third party in advance of the above content and conditions, and the buyer or distributor agrees to assume any and all responsibility and liability for and hold AKM harmless from any and all claims arising from the use of said product in the absence of such notification.

Thank you for your access to AKM product information.

More detail product information is available, please contact our sales office or authorized distributors.