**AK4642**

## AKM

# 16-Bit $\Delta\Sigma$ Stereo CODEC with MIC/HP/SPK-AMP

### **GENERAL DESCRIPTION**

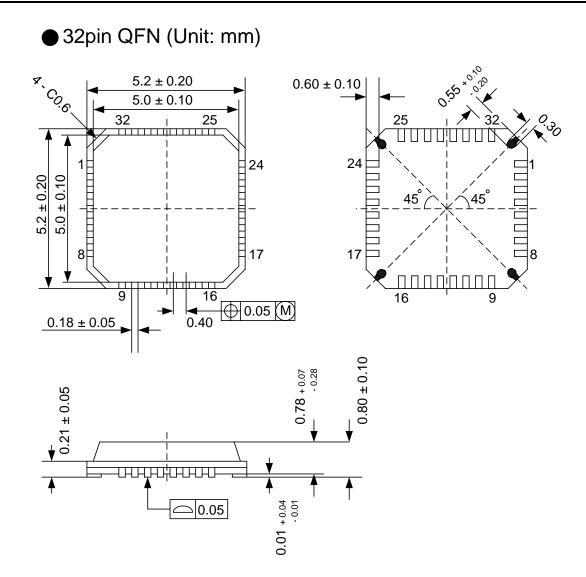

The AK4642 features a 16-bit stereo CODEC with a built-in Microphone-Amplifier, Headphone-Amplifier and Speaker-Amplifier. Input circuits include a Microphone-Amplifier and an ALC (Auto Level Control) circuit that is suitable for portable application with recording/playback function. The AK4642 is available in a 32pin QFN, utilizing less board space than competitive offerings.

### FEATURES

### 1. Resolution: 16bits

- 2. Recording Function

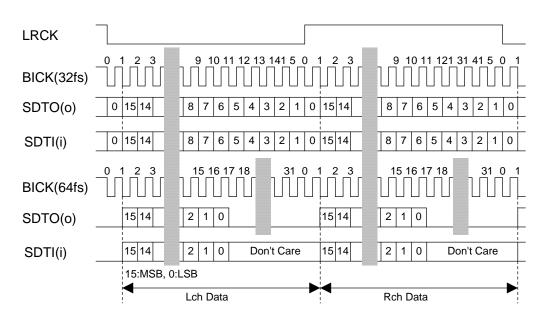

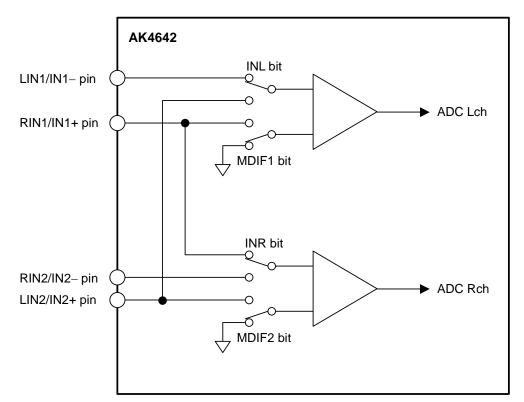

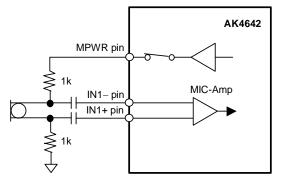

- Stereo Mic Input (Full-differential or Single-ended)

- Stereo Line Input

- MIC Amplifier (+32dB/+26dB/+20dB or 0dB)

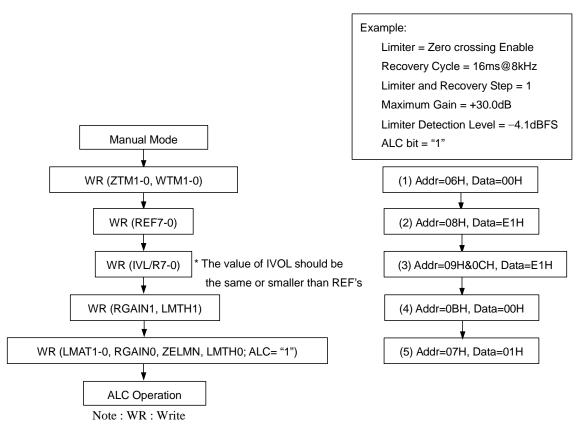

- Digital ALC (Automatic Level Control)

- (+36dB ~ -54dB, 0.375dB Step, Mute)

- ADC Performance: S/(N+D): 83dB, DR, S/N: 86dB (MIC-Amp=+20dB) S/(N+D): 88dB, DR, S/N: 95dB (MIC-Amp=0dB)

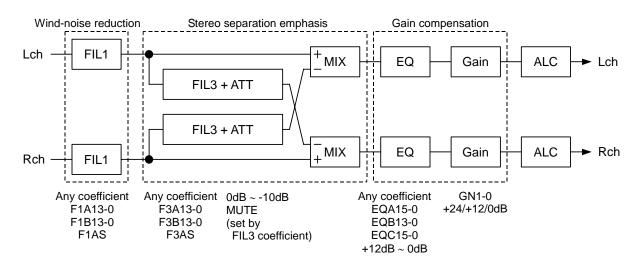

- Wind-noise Reduction Filter

- Stereo Separation Emphasis

- 3. Playback Function

- Digital De-emphasis Filter (tc=50/15µs, fs=32kHz, 44.1kHz, 48kHz)

- Digital Volume (+12dB ~ -115.0dB, 0.5dB Step, Mute)

- Digital ALC (Automatic Level Control)

- (+36dB ~ -54dB, 0.375dB Step, Mute)

- Stereo Separation Emphasis

- Stereo Line Output

- Performance: S/(N+D): 88dB, S/N: 92dB

- Stereo Headphone-Amp

- S/(N+D): 70dB, S/N: 90dB

- Output Power:  $15mW@16\Omega$  (HVDD=3.3V)

- Pop Noise Free at Power ON/OFF

- Mono Speaker-Amp

- S/(N+D): 50dB@240mW, S/N: 90dB

- BTL Output

- Availbable for both Dynamic and Piezo Speaker

- Output Power: 400m $\hat{W}$ @8 $\Omega$  (HVDD=3.3V)

- 3.0Vrms@50Ω (HVDD=5V)

- Beep Input

- 4. Power Management

- 5. Master Clock:

- (1) PLL Mode

- Frequencies:

- 11.2896MHz, 12MHz, 12.288MHz, 13.5MHz, 24MHz, 27MHz (MCKI pin) 1fs (LRCK pin)

- 32fs or 64fs (BICK pin)

- (2) External Clock Mode

- Frequencies: 256fs, 512fs or 1024fs (MCKI pin)

- 6. Output Master Clock Frequencies: 32fs/64fs/128fs/256fs

7. Sampling Rate:

- PLL Slave Mode (LRCK pin): 7.35kHz ~ 48kHz

- PLL Slave Mode (BICK pin): 7.35kHz ~ 48kHz

- PLL Slave Mode (MCKI pin):

- 8kHz, 11.025kHz, 12kHz, 16kHz, 22.05kHz, 24kHz, 32kHz, 44.1kHz, 48kHz • PLL Master Mode:

- 8kHz, 11.025kHz, 12kHz, 16kHz, 22.05kHz, 24kHz, 32kHz, 44.1kHz, 48kHz

- EXT Slave Mode:

- 7.35kHz  $\sim$  48kHz (256fs), 7.35kHz  $\sim$  26kHz (512fs), 7.35kHz  $\sim$  13kHz (1024fs) 8.  $\mu\text{P}$  I/F: 3-wire Serial, I^2C Bus

- 9. Master/Slave mode

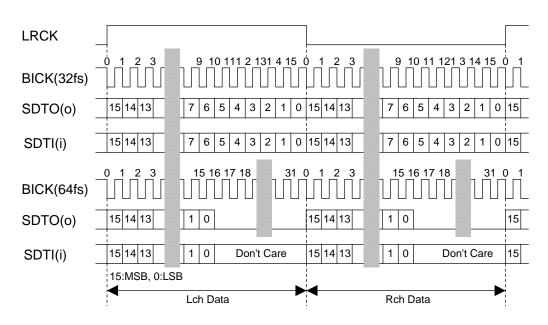

- 10. Audio Interface Format: MSB First, 2's compliment

- ADC : 16bit MSB justified, I<sup>2</sup>S

- DAC : 16bit MSB justified, 16bit LSB justified, I2S

- 11. Ta = -40 ~ 85°C (SPK-Amp=OFF)

- –40 ∼ 70°C (SPK-Amp=ON)

- 12. Power Supply:

- $\bullet$  AVDD, DVDD: 2.6  $\sim$  3.6V (typ. 3.3V)

- HVDD: 2.6 ~ 5.25V (typ. 3.3V/5.0V)

- 13. Package: 32pin QFN (5.2mm x 5.2mm)

- 14. Register Upper-Compatible with Mono CODEC (AK4536/4630/4631)

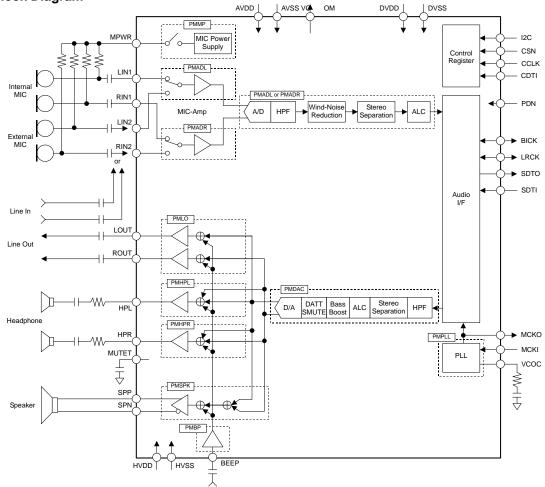

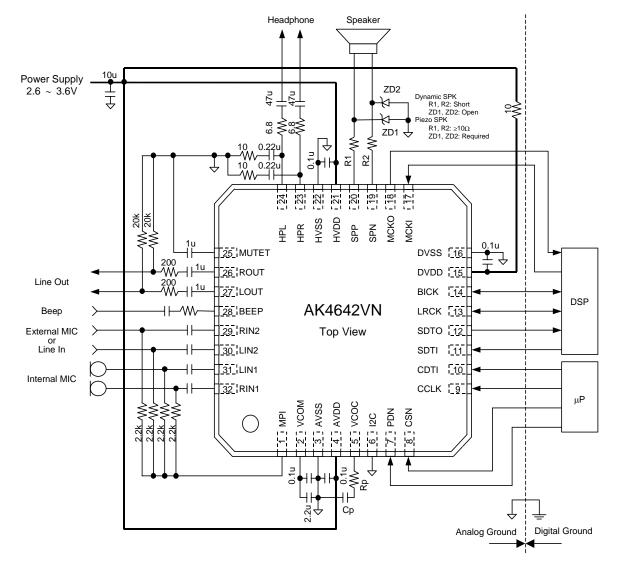

- Block Diagram

Figure 1. Block Diagram

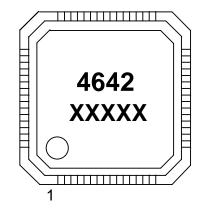

### Ordering Guide

| AK4642VN |     | $-40 \sim +85^{\circ}C$ | 32pi       | n QFN (0.4mm pitch) |

|----------|-----|-------------------------|------------|---------------------|

| AKD4642  | Eva | luation board           | for AK4642 | _                   |

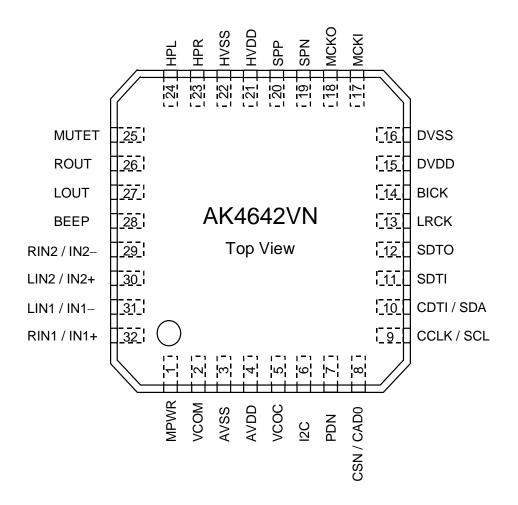

### Pin Layout

### ■ Comparison with AK4537

| Function AK4537             |                                      | AK4642                               |

|-----------------------------|--------------------------------------|--------------------------------------|

| Mic Input                   | Single-ended                         | Single-ended / Full-differential     |

| Stereo Mic Input            | 1-Input                              | 2-Input selectable                   |

| MIC-Power                   | 2-Output, $R_L=2k\Omega$ (min)       | 1-Output, $R_L=0.5k\Omega$ (min)     |

| MIC-Amp                     | +20dB or 0dB                         | +32dB/+26dB/+20dB or 0dB             |

| MIC ALC                     | +27.5dB to -8dB, 0.5dB step          | +36dB to -54dB, 0.375dB step, Mute   |

| Wind-noise Reduction Filter | N/A                                  | Available                            |

| Stereo Separation Emphasis  | N/A                                  | Available                            |

| Mono Mic Mode               | N/A                                  | Available                            |

| ALC for Playback            | SP only, +18dB to -8dB               | Line/HP/SP, +36dB to -54dB           |

| DATT                        | 0 to -127dB, Mute                    | +12 to -115dB, Mute                  |

| Bass Boost                  | +5.74dB/+5.94dB/+16.04dB@20Hz        | +5.76dB/+10.80dB/+16.06dB@20Hz       |

| DAC Digital Filter          | 43dB                                 | 59dB                                 |

| Stopband Attenuation        | 430B                                 | 590B                                 |

| Line Output Level           | 1.98Vpp                              | 1.98Vpp/2.50Vpp                      |

| Usage for Piezo Speaker     | N/A                                  | Available                            |

| PLL Input Frequency         | 11.2896MHz, 12MHz, 12.288MHz         | 11.2896MHz, 12MHz, 12.288MHz,        |

| T LL Input I requency       |                                      | 13.5MHz, 24MHz, 27MHz                |

| μP I/F                      | 4-wire/I <sup>2</sup> C(100kHz mode) | 3-wire/I <sup>2</sup> C(400kHz mode) |

| X'tal                       | Available                            | N/A                                  |

| MCKI AC Input               | Available                            | N/A                                  |

| MCKI Pull-down              | Available                            | N/A                                  |

| Analog Loopback             | Available                            | N/A                                  |

| Mono Line Output            | Available                            | N/A                                  |

| Stereo Beep Input           | Available                            | N/A                                  |

| Power Supply (HVDD)         | 2.4 ~ 3.6V                           | 2.6 ~ 5.25V                          |

| Package                     | 52pin QFN (7.2mm x 7.2mm)            | 32pin QFN (5.2mm x 5.2mm)            |

| Register Map                |                                      | No Compatibility                     |

### ■ Comparison with AK4631

| Function AK4631             |                             | AK4642                                                                                 |

|-----------------------------|-----------------------------|----------------------------------------------------------------------------------------|

| Mic Input                   | Single-ended                | Single-ended / Full-differential                                                       |

| Stereo Mic Input            | N/A                         | Available                                                                              |

| ADC                         | Mono                        | Stereo                                                                                 |

| MIC ALC                     | +27.5dB to -8dB, 0.5dB step | +36dB to -54dB, 0.375dB step, Mute                                                     |

| Wind-noise Reduction Filter | N/A                         | Available                                                                              |

| Stereo Separation Emphasis  | N/A                         | Available                                                                              |

| ALC for Playback            | SP only, +18dB to -8dB      | Line/HP/SP, +36dB to -54dB                                                             |

| Soft Mute                   | N/A                         | Available                                                                              |

| Bass Boost                  | N/A                         | Available                                                                              |

| De-emphasis                 | N/A                         | Available                                                                              |

| DAC                         | Mono                        | Stereo                                                                                 |

| HP-Amp                      | N/A                         | Available                                                                              |

| Line Output                 | Mono                        | Stereo                                                                                 |

| Line Output Level           | 1.98Vpp                     | 1.98Vpp/2.50Vpp                                                                        |

| μP I/F                      | 3-wire                      | 3-wire/I <sup>2</sup> C                                                                |

| MCKI Pull-down              | Available                   | N/A                                                                                    |

| Analog Loopback             | Available                   | N/A                                                                                    |

| DSP Mode                    | Available                   | N/A                                                                                    |

| Package                     | 28pin QFN (5.2mm x 5.2mm)   | 32pin QFN (5.2mm x 5.2mm)                                                              |

| Regester Map                |                             | Upper-compatible (Difference: ALC<br>parameter, Analog Loopback & DSP<br>Mode Removed) |

### Register Compatibility with AK4631

### AK4631

| Addr | Register Name          | D7 D6 |       | D5     | D4 D  | 3     | D2 D1 |       | D0     |

|------|------------------------|-------|-------|--------|-------|-------|-------|-------|--------|

| 00H  | Power Management 1     | 0     | PMVCM | PMBP   | PMSPK | PMAO  | PMDAC | PMMIC | PMADC  |

| 01H  | Power Management 2     | 0     | 0     | 0      | 0     | M/S   | MCKPD | MCKO  | PMPLL  |

| 02H  | Signal Select 1        | SPPS  | BEEPS | ALC2S  | DACA  | DACM  | MPWR  | MICAD | MGAIN0 |

| 03H  | Signal Select 2        | 0     | AOPSN | MGAIN1 | SPKG1 | SPKG0 | BEEPA | ALC1M | ALC1A  |

| 04H  | Mode Control 1         | PLL3  | PLL2  | PLL1   | PLL0  | BCKO1 | BCKO0 | DIF1  | DIF0   |

| 05H  | Mode Control 2         | 0     | 0     | FS3    | MSBS  | BCKP  | FS2   | FS1   | FS0    |

| 06H  | Timer Select           | DVTM  | ROTM  | ZTM1   | ZTM0  | WTM1  | WTM0  | LTM1  | LTM0   |

| 07H  | ALC Mode Control 1     | 0     | ALC2  | ALC1   | ZELM  | LMAT1 | LMAT0 | RATT  | LMTH   |

| 08H  | ALC Mode Control 2     | 0     | REF6  | REF5   | REF4  | REF3  | REF2  | REF1  | REF0   |

| 09H  | Input PGA Control      | 0     | IPGA6 | IPGA5  | IPGA4 | IPGA3 | IPGA2 | IPGA1 | IPGA0  |

| 0AH  | Digital Volume Control | DVOL7 | DVOL6 | DVOL5  | DVOL4 | DVOL3 | DVOL2 | DVOL1 | DVOL0  |

| 0BH  | ALC2 Mode Control      | 0     | 0     | RFS5   | RFS4  | RFS3  | RFS2  | RFS1  | RFS0   |

### AK4642

| Addr | Register Name              | D7                                  | D6 D5                               |        | D4 D3 | D2    |       | D1 D0  |        |

|------|----------------------------|-------------------------------------|-------------------------------------|--------|-------|-------|-------|--------|--------|

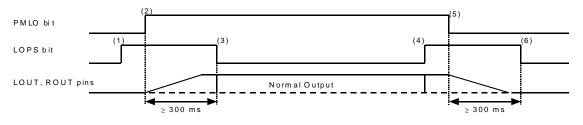

| 00H  | Power Management 1         | 0                                   | PMVCM                               | PMBP   | PMSPK | PMLO  | PMDAC | 0      | PMADL  |

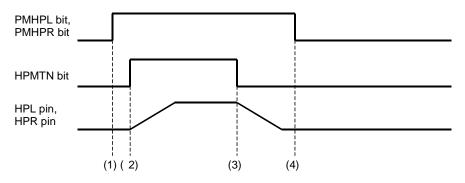

| 01H  | Power Management 2         | 0                                   | HPMTN                               | PMHPL  | PMHPR | M/S   | 0     | МСКО   | PMPLL  |

| 02H  | Signal Select 1            | SPPSN                               | BEEPS                               | DACS   | DACL  | 0     | PMMP  | 0      | MGAIN0 |

| 03H  | Signal Select 2            | LOVL                                | LOPS                                | MGAIN1 | SPKG1 | SPKG0 | BEEPL | 0      | 0      |

| 04H  | Mode Control 1             | PLL3                                | PLL2                                | PLL1   | PLL0  | BCKO  | 0     | DIF1   | DIF0   |

| 05H  | Mode Control 2             | PS1                                 | PS0                                 | FS3    | 0     | 0     | FS2   | FS1    | FS0    |

| 06H  | Timer Select               | DVTM                                | 0                                   | ZTM1   | ZTM0  | WTM1  | WTM0  | 0      | 0      |

| 07H  | ALC Mode Control 1         | 0                                   | 0                                   | ALC    | ZELMN | LMAT1 | LMAT0 | RGAIN0 | LMTH0  |

| 08H  | ALC Mode Control 2         | REF7                                | REF6                                | REF5   | REF4  | REF3  | REF2  | REF1   | REF0   |

| 09H  | Lch Input Volume Control   | IVL7                                | IVL6                                | IVL5   | IVL4  | IVL3  | IVL2  | IVL1   | IVL0   |

| 0AH  | Lch Digital Volume Control | DVL7                                | DVL6                                | DVL5   | DVL4  | DVL3  | DVL2  | DVL1   | DVL0   |

| 0BH  | ALC Mode Control 3         | RGAIN1                              | LMTH1                               | 0      | 0     | 0     | 0     | 0      | 0      |

| 0CH  |                            |                                     |                                     |        |       |       |       |        |        |

| to   |                            | Additional Function for AK4642 only |                                     |        |       |       |       |        |        |

| 1FH  |                            |                                     |                                     |        |       |       |       |        |        |

| • •  |                            |                                     | Additional Function for AK4642 only |        |       |       |       |        |        |

Bits which are not needed for AK4642

| PIN/FUNCTION                                                    |         |                                                                                 |  |  |  |  |  |  |

|-----------------------------------------------------------------|---------|---------------------------------------------------------------------------------|--|--|--|--|--|--|

|                                                                 |         |                                                                                 |  |  |  |  |  |  |

| No. P in Na                                                     | ime I/O | Function                                                                        |  |  |  |  |  |  |

| 1 MPWI                                                          | R 0     | MIC Power Supply Pin                                                            |  |  |  |  |  |  |

| 2 V COM                                                         | 1 0     | Common Voltage Output Pin, 0.45 x AVDD                                          |  |  |  |  |  |  |

| 2 V CON                                                         | 0       | Bias voltage of ADC inputs and DAC outputs.                                     |  |  |  |  |  |  |

| 3 AVSS                                                          | -       | Analog Ground Pin                                                               |  |  |  |  |  |  |

| 4 AVDE                                                          | ) -     | Analog Power Supply Pin                                                         |  |  |  |  |  |  |

| 5 V COC                                                         |         | Output Pin for Loop Filter of PLL Circuit                                       |  |  |  |  |  |  |

| 5 0 000                                                         | . 0     | This pin should be connected to AVSS with one resistor and capacitor in series. |  |  |  |  |  |  |

| 6 I2C                                                           | I       | Control Mode Select Pin                                                         |  |  |  |  |  |  |

| 012C                                                            | 1       | "H": I <sup>2</sup> C Bus, "L": 3-wire Serial                                   |  |  |  |  |  |  |

| 7 P DN                                                          | I       | Power-Down Mode Pin                                                             |  |  |  |  |  |  |

|                                                                 | 1       | "H": Power-up, "L": Power-down, reset and initializes the control register.     |  |  |  |  |  |  |

| 8 CSN                                                           | I       | Chip Select Pin (I2C pin = "L")                                                 |  |  |  |  |  |  |

| CAD0                                                            | Ι       | Chip Address 1 Select Pin (I2C pin = "H")                                       |  |  |  |  |  |  |

| 9 CCLK                                                          | I       | Control Data Clock Pin (I2C pin = "L")                                          |  |  |  |  |  |  |

| 9 SCL                                                           | Ι       | Control Data Clock Pin (I2C pin = "H")                                          |  |  |  |  |  |  |

| 10 CDTI                                                         | Ι       | Control Data Input Pin (I2C pin = "L")                                          |  |  |  |  |  |  |

| <sup>10</sup> SDA                                               | I/O     | Control Data Input Pin (I2C pin = "H")                                          |  |  |  |  |  |  |

| 11 SDTI                                                         | Ι       | Audio Serial Data Input Pin                                                     |  |  |  |  |  |  |

| 12 SDTO                                                         | 0       | Audio Serial Data Output Pin                                                    |  |  |  |  |  |  |

| 13 LRCK                                                         |         | Input / Output Channel Clock Pin                                                |  |  |  |  |  |  |

| 14 BICK                                                         | I/O     | Audio Serial Data Clock Pin                                                     |  |  |  |  |  |  |

| 15 DVDD                                                         | ) -     | Digital Power Supply Pin                                                        |  |  |  |  |  |  |

| 16 DVSS                                                         | -       | Digital Ground Pin                                                              |  |  |  |  |  |  |

| 17 MCKI                                                         | Ι       | External Master Clock Input Pin                                                 |  |  |  |  |  |  |

| 18 MCK0                                                         |         | Master Clock Output Pin                                                         |  |  |  |  |  |  |

| 19 SPN                                                          | 0       | Speaker Amp Negative Output Pin                                                 |  |  |  |  |  |  |

| 20 SPP                                                          | 0       | Speaker Amp Positive Output Pin                                                 |  |  |  |  |  |  |

| 21 HVDD                                                         | ) -     | Headphone & Speaker Amp Power Supply Pin                                        |  |  |  |  |  |  |

| 22 HVSS                                                         | -       | Headphone & Speaker Amp Ground Pin                                              |  |  |  |  |  |  |

| 23 HPR                                                          | 0       | Rch Headphone-Amp Output Pin                                                    |  |  |  |  |  |  |

| 24 HPL                                                          | 0       | Lch Headphone-Amp Output Pin                                                    |  |  |  |  |  |  |

|                                                                 |         | Mute Time Constant Control Pin                                                  |  |  |  |  |  |  |

| 25 MUTET                                                        | 0       | Connected to HVSS pin with a capacitor for mute time constant.                  |  |  |  |  |  |  |

| 26 ROUT                                                         | 0       | Rch Stereo Line Output Pin                                                      |  |  |  |  |  |  |

| 27 LOUT                                                         | 0       | Lch Stereo Line Output Pin                                                      |  |  |  |  |  |  |

| 28 BEEP                                                         | Ι       | Mono Beep Signal Input Pin                                                      |  |  |  |  |  |  |

| 20 RIN2                                                         | Ι       | Rch Analog Input 2 Pin (MDIF2 bit = "0")                                        |  |  |  |  |  |  |

| 29 IN2-                                                         | Ι       | Microphone Negative Input 2 Pin (MDIF2 bit = "1")                               |  |  |  |  |  |  |

| L IN2                                                           | Ι       | Lch Analog Input 2 Pin (MDIF2 bit = "0")                                        |  |  |  |  |  |  |

| $\begin{array}{c c} 30 & \underline{III12} \\ IN2+ \end{array}$ | Ι       | Microphone Positive Input 2 Pin (MDIF2 bit = "1")                               |  |  |  |  |  |  |

| L IN1                                                           | Ι       | Lch Analog Input 1 Pin (MDIF1 bit = "0")                                        |  |  |  |  |  |  |

| 31 <u>IN1–</u>                                                  | Ī       | Microphone Negative Input 1 Pin (MDIF1 bit = "1")                               |  |  |  |  |  |  |

| RIN1                                                            | I       | Rch Analog Input 1 Pin     (MDIF1 bit = "0")                                    |  |  |  |  |  |  |

| 32 IN1+                                                         | I       | Microphone Positive Input 1 Pin (MDIF1 bit = "1")                               |  |  |  |  |  |  |

| 11 11                                                           | 1       |                                                                                 |  |  |  |  |  |  |

Note 1. All input pins except analog input pins (BEEP, LIN1, RIN1, LIN2, RIN2) should not be left floating. Note 2. AVDD or AVSS voltage should be input to I2C pin.

### Handling of Unused Pin

The unused I/O pins should be processed appropriately as below.

| Classification P | in Name                                                                                                   | Setting                                                           |

|------------------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| Analog           | MPWR, VCOC, SPN, SPP, HPR, HPL, MUTET,<br>ROUT, LOUT, BEEP, RIN2/IN2–, LIN2/IN2+,<br>LIN1/IN1–, RIN1/IN1+ | These pins should be open.                                        |

| Digital          | MCKO<br>MCKI                                                                                              | This pin should be open.<br>This pin should be connected to DVSS. |

|                     |                | ABSOLUTE N        | AXIMUM F      | RATINGS |          |       |

|---------------------|----------------|-------------------|---------------|---------|----------|-------|

| (AVSS, DVSS, H      | VSS=0V; Note   | 23)               |               |         |          |       |

| Parameter S         |                |                   | ymbol         | min     | max      | Units |

| Power Supplies:     | Analog         |                   | AVDD          | -0.3    | 6.0 V    |       |

| Digi                | tal            |                   | DVDD          | -0.3    | 6.0 V    |       |

|                     | Headphone-     | Amp / Speaker-Amp | HVDD          | -0.3    | 6.0 V    |       |

|                     | AVSS – DV      | VSS  (Note 4)     | $\Delta GND1$ | - 0.3   |          | V     |

|                     | AVSS – HV      | VSS (Note 4)      | $\Delta GND2$ | - 0.3   |          | V     |

| Input Current, An   | y Pin Except S | upplies           | IIN           | -       | $\pm 10$ | mA    |

| Analog Input Volt   | age (Note 5)   |                   | VINA          | -0.3    | AVDD+0.3 | V     |

| Digital Input Volta | age (Note 6)   |                   | VIND          | -0.3    | DVDD+0.3 | V     |

| Ambient Tempera     | ture (powered  | applied)          | Та            | -40     | 85       | °C    |

| Storage Temperature |                |                   | Tstg          | -65     | 150      | °C    |

| Maximum Power       | Dissipation    | Ta=85°C (Note 8)  | Pd1 -         |         | 400      | mW    |

|                     | (Note 7)       | Ta=70°C (Note 9)  | Pd2 -         |         | 550      | mW    |

Note 3. All voltages with respect to ground.

Note 4. AVSS, DVSS and HVSS must be connected to the same analog ground plane.

Note 5. I2C, BEEP, RIN2/IN2-, LIN2/IN2+, LIN1/IN1-, RIN1/IN1+ pins

Note 6. PDN, CSN/CAD0, CCLK/SCL, CDTI/SDA, SDTI, LRCK, BICK, MCKI pins

Note 7. In case that PCB wiring density is 100%. This power is the AK4642 internal dissipation that does not include power of externally connected speaker and headphone.

Note 8. Speaker-Amp is not available.

Note 9. Speaker-Amp is available.

WARNING: Operation at or beyond these limits may result in permanent damage to the device. Normal operation is not guaranteed at these extremes.

|                  | RECOMMENDED OPERATING CONDITIONS |           |         |           |      |       |  |  |  |  |

|------------------|----------------------------------|-----------|---------|-----------|------|-------|--|--|--|--|

| (AVSS, DVSS, H   | (AVSS, DVSS, HVSS=0V; Note 3)    |           |         |           |      |       |  |  |  |  |

| Parameter Symbol |                                  |           | min typ |           | Max  | Units |  |  |  |  |

| Power Supplies   | Analog                           | AVDD      | 2.6     | 3.3       | 3.6  | V     |  |  |  |  |

| (Note 10)        | Digital                          | DVDD      | 2.6     | 3.3       | 3.6  | V     |  |  |  |  |

|                  | HP / SPK-Amp (Note 11)           | HVDD      | 2.6     | 3.3 / 5.0 | 5.25 | V     |  |  |  |  |

|                  | Difference                       | AVDD-DVDD | -0.3    | 0 +0.3    |      | V     |  |  |  |  |

Note 3. All voltages with respect to ground.

Note 10. The power-up sequence between AVDD, DVDD and HVDD is not critical. When the power supplies are partially powered OFF, the AK4642 must be reset by bringing PDN pin "L" after these power supplies are powered ON again.

Note 11. HVDD =  $2.6 \sim 3.6V$  when  $8\Omega$  dynamic speaker is connected to the AK4642.

\* AKM assumes no responsibility for the usage beyond the conditions in this datasheet.

Г

|                             |                             | ANALUG                 | CHARACIERIS                  | 51163                                  |                 |          |

|-----------------------------|-----------------------------|------------------------|------------------------------|----------------------------------------|-----------------|----------|

| (Ta=25°C; A                 | AVDD, DVDD, HVDD=3.3        | V; AVSS=DV             | /SS=HVSS=0V; f               | s=44.1kHz, BICK=                       | 64fs;           |          |

| Signal Freq                 | uency=1kHz; 16bit Data; N   | leasurement fr         | requency=20Hz ~              | 20kHz; unless other                    | wise specified) |          |

| Parameter                   |                             |                        | min ty                       | р                                      | max             | Units    |

| MIC Ampli                   | ifier: LIN1, RIN1, LIN2, R  | IN2 pins; MD           | IF1 = MDIF2 bits             | = "0" (Single-ended                    | l inputs)       |          |

| Input                       | MGAIN1-0 bits = " $00$ "    |                        | 40                           | 60                                     | 80              | kΩ       |

| Resistance                  | MGAIN1-0 bits = "01", "     | 10"or "11"             | 20                           | 30                                     | 40              | kΩ       |

|                             | MGAIN1-0 bits = "00"        |                        | -                            | 0                                      | -               | dB       |

| Calin                       | MGAIN1-0 bits = "01"        |                        | -                            | +20                                    | -               | dB       |

| Gain                        | MGAIN1-0 bits = "10"        |                        |                              | +26                                    | -               | dB       |

|                             | MGAIN1-0 bits = "11"        |                        | -                            | +32                                    | -               | dB       |

| MIC Ampli                   | ifier: IN1+, IN1–, IN2+, IN | 2- pins; MDI           | F1 = MDIF2 bits =            | = "1" (Full-different                  | ial input)      |          |

|                             | nput Voltage (Note 12)      | <b>^</b>               |                              | `````````````````````````````````````` | <b>A</b> '      |          |

|                             | MGAIN1-0 bits = "01"        |                        | -                            | -                                      | 0.228           | Vpp      |

|                             | MGAIN1-0 bits = "10"        |                        |                              | -                                      | 0.114           | Vpp      |

|                             | MGAIN1-0 bits = "11"        |                        |                              | -                                      | 0.057           | Vpp      |

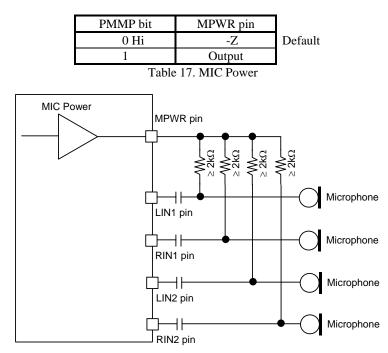

| <b>MIC Power</b>            | Supply: MPWR pin            |                        |                              |                                        |                 | - ^ ^ ·  |

|                             | age (Note 13)               |                        | 2.22                         | 2.47                                   | 2.72            | V        |

| Load Resista                | ance                        |                        | 0.5                          | -                                      | -               | kΩ       |

| Load Capac                  | itance                      |                        | -                            | -                                      | 30              | pF       |

| ADC Analo                   | g Input Characteristics: L  | .IN1/RIN1/LI           | N2/RIN2 pins $\rightarrow 1$ | ADC $\rightarrow$ IVOL, IVC            | L=0dB, ALC=0    | )FF      |

| Resolution -                |                             |                        |                              | -                                      | 16              | Bits     |

| Input Voltag                | $(\mathbf{N}_{oto} 1_{4})$  | (Note 15)              | 0.168                        | 0.198                                  | 0.228           | Vpp      |

| mput vonag                  | ge (Note 14)                | (Note 16)              | 1.68                         | 1.98                                   | 2.28            | Vpp      |

| S/(N+D)                     | (-1dBFS)                    | (Note 15)              | 71                           | 83                                     | -               | dBFS     |

| 5/(I <b>\</b> +D)           | (-10015)                    | (Note 16)              | -                            | 88                                     | -               | dBFS     |

| D-Range                     | (-60dBFS, A-weighted)       | (Note 15)              | 76                           | 86                                     |                 | dB       |

| Dittange                    | ( oodbi 5, 11 weighted)     | (Note 16)              | -                            | 95                                     | -               | dB       |

| S/N (A -weighted) (Note 15) |                             | 76                     | 86                           |                                        | dB              |          |

| `                           | υ,                          | (Note 16)              | -                            | 95                                     | -               | dB       |

| Interchannel                | l Isolation                 | (Note 15)              | 75                           | 90                                     | -               | dB       |

|                             |                             | (Note 16)              | -                            | 100<br>0.1                             | - 0.8           | dB<br>dB |

| Interchannel                | l Gain Mismatch             | (Note 15)<br>(Note 16) | -                            | 0.1                                    | 0.8             | dB<br>dB |

|                             |                             | (11010-10)             | -                            | 0.1                                    | 0.0             | uD       |

ANALOG CHARACTERISTICS

Note 12. The voltage difference between IN1/2+ and IN1/2- pins. AC coupling capacitor should be inserted in series at each input pin. Full-differential mic input is not available at MGAIN1-0 bits = "00". Maximum input voltage of IN1+, IN1-, IN2+ and IN2- pins is proportional to AVDD voltage, respectively.

Vin = 0.069 x AVDD (max)@MGAIN1-0 bits = "01", 0.035 x AVDD (max)@MGAIN1-0 bits = "10", 0.017 x AVDD (max)@MGAIN1-0 bits = "11".

When the signal larger than above value is input to IN1+, IN1-, IN2+ or IN2- pin, ADC does not operate normally.

Note 13. Output voltage is proportional to AVDD voltage. Vout = 0.75 x AVDD (typ)

Note 14. Input voltage is proportional to AVDD voltage. Vin = 0.06 x AVDD (typ)@MGAIN1-0 bits = "01" (+20dB), Vin = 0.6 x AVDD(typ)@MGAIN1-0 bits = "00" (0dB)

Note 15. MGAIN1-0 bits = "01" (+20dB)

Note 16. MGAIN1-0 bits = "00" (0dB)

| Parameter                  |                                  | min typ         |                  | max          | Units      |

|----------------------------|----------------------------------|-----------------|------------------|--------------|------------|

| DAC Characteristics:       |                                  |                 |                  |              |            |

| Resolution                 |                                  | -               | -                | 16           | Bits       |

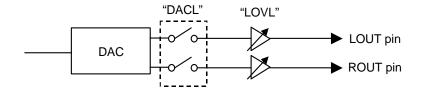

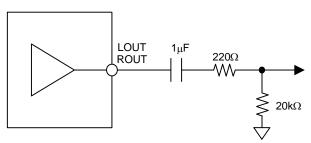

| Stereo Line Output Charact | eristics: DAC $\rightarrow$ LOUT | , ROUT pins, AL | C=OFF, IVOL=0dl  | B, DVOL=0dB, | LOVL bit = |

| -                          | "0", R <sub>L</sub> =10kΩ        | · • •           |                  |              |            |

| Output Voltage (Note 17)   | LOVL bit = "0"                   | 1.78            | 1.98             | 2.18         | Vpp        |

|                            | LOVL bit = "1"                   | 2.25            | 2.50             | 2.75         | Vpp        |

| S/(N+D) (-3dBFS)           |                                  | 78 88           |                  | -            | dBFS       |

| S/N (A -weighted)          |                                  | 82              | 92               | -            | dB         |

| Interchannel Isolation     |                                  | 80              | 100              | -            | dB         |

| Interchannel Gain Mismatch |                                  | -               | 0.1              | 0.5          | dB         |

| Load Resistance            |                                  | 10              | -                | -            | kΩ         |

| Load Capacitance           |                                  | -               | -                | 30           | pF         |

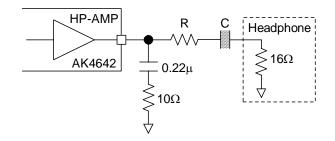

| Headphone-Amp Character    | istics: DAC $\rightarrow$ HPL/HP | R pins, ALC=OF  | F, IVOL=0dB, DVO | DL=0dB       |            |

| Output Valtaga (Nota 18)   | (Note 19)                        | 1.58            | 1.98             | 2.38         | Vpp        |

| Output Voltage (Note 18)   | (Note 20)                        | 2.40 3.00 3     | 60               |              | Vpp        |

| S/(N+D) (-3dBFS)           | (Note 19)                        | 60              | 70               | -            | dBFS       |

| S/(N+D) (-30BFS)           | (Note 20)                        | - 80 -          |                  |              | dBFS       |

| S/N (A- weighted)          | (Note 19)                        | 80              | 90               | -            | dB         |

| S/IV (A- weighted)         | (Note 20)                        | -               | 90               | -            | dB         |

| Interchannel Isolation     | (Note 19)                        | 65              | 75               |              | dB         |

| Interenamier Isolation     | (Note 20)                        | -               | 80               | -            | dB         |

| Interchannel Gain Mismatch | (Note 19)                        |                 | 0.1              | 0.8          | dB         |

| Interenamer Gum Wilshuten  | (Note 20)                        | -               | 0.1              | 0.8          | dB         |

| Load Resistance            | (Note 19)                        | 20              |                  | -            | Ω          |

|                            | (Note 20)                        | 100             | -                | -            | Ω          |

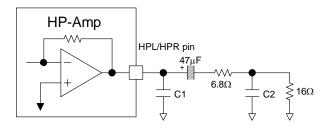

| Load Capacitance           | C1 in Figure 2                   |                 |                  | 30           | pF         |

| Louis Supuriunee           | C2 in Figure 2                   | -               | -                | 300          | pF         |

Note 17. Output voltage is proportional to AVDD voltage. Vout =  $0.6 \times \text{AVDD} (\text{typ})@LOVL \text{ bit} = "0"$ . Note 18. Output voltage is proportional to AVDD voltage.

Vout = 0.6 x AVDD(typ)@HPG bit = "0", 0.91 x AVDD(typ)@HPG bit = "1".

Note 19. HPG bit = "0", HVDD=3.3V, RL=22.8Ω.

Note 20. HPG bit = "1", HVDD=5V, RL= $100\Omega$ .

Figure 2. Headphone-Amp output circuit

| Parameter                          |                                    |                                | min typ          |               | max                                     | Units                   |

|------------------------------------|------------------------------------|--------------------------------|------------------|---------------|-----------------------------------------|-------------------------|

| Speaker-Amp Cha                    | racteristics                       | : DAC $\rightarrow$ SPP/SPN p  | ins, ALC=OFF, IV | OL=0dB, DVOL= | $=0$ dB, R <sub>L</sub> $=8\Omega$ , BT | L,                      |

|                                    |                                    | HVDD=3.3V                      |                  |               |                                         |                         |

| Output Voltage (No                 |                                    |                                |                  |               |                                         |                         |

| SPKG1-0 bits =                     | "00", -0.50                        | lBFS (Po=150mW)                | 2.49 3.11 3      | .73           |                                         | Vpp                     |

| SPKG1-0 bits =                     | "01", -0.50                        | lBFS (Po=240mW)                | - 3.92 -         |               |                                         | Vpp                     |

| SPKG1-0 bits =                     | "10", -2.50                        | lBFS (Po=400mW)                | - 1.79 -         |               |                                         | Vrms                    |

| S/(N+D)                            |                                    |                                |                  |               |                                         |                         |

| SPKG1-0 bits =                     | "00", -0.50                        | lBFS (Po=150mW)                | - 60 -           |               |                                         | dB                      |

| SPKG1-0 bits =                     | "01", -0.50                        | lBFS (Po=240mW)                | 20 50            |               | -                                       | dB                      |

| SPKG1-0 bits =                     | "10", -2.50                        | lBFS (Po=400mW)                | - 20 -           |               |                                         | dB                      |

| S/N (A                             | A-weighted                         | )                              | 80               | 90            | -                                       | dB                      |

| Load Resistance                    |                                    |                                | 8                | -             | -                                       | Ω                       |

| Load Capacitance                   |                                    |                                | -                | -             | 30                                      | pF                      |

| Speaker-Amp Cha                    | racteristics                       | : DAC $\rightarrow$ SPP/SPN pi | ns, ALC=OFF, IVC | DL=0dB, DVOL= | $DdB, C_L = 3\mu F, R_{ser}$            | <sub>ial</sub> =10Ω x 2 |

|                                    |                                    | $R_L=50\Omega$ , BTL, HVI      | DD=5.0V          |               |                                         |                         |

| Output Voltage S                   | PKG1-0 bit                         | s = "10", 0dBFS                | -                | 6.75          | -                                       | Vpp                     |

| (Note 21) S                        | PKG1-0 bit                         | s = "11", 0dBFS                | 6.80             | 8.50          | 10.20                                   | Vpp                     |

| S/(N+D) S                          | PKG1-0 bit                         | s = "10", 0dBFS                | -                | 60            | -                                       | dB                      |

| (Note 22) S                        | PKG1-0 bit                         | s = "11", 0dBFS                | 40               | 50            | -                                       | dB                      |

| S/N (4                             | A-weighted                         | )                              | 80               | 90            | -                                       | dB                      |

| Load Resistance (Ne                | ote 23)                            |                                | 50               | -             | -                                       | Ω                       |

| Load Capacitance (I                | Note 23)                           |                                | -                | -             | 3                                       | μF                      |

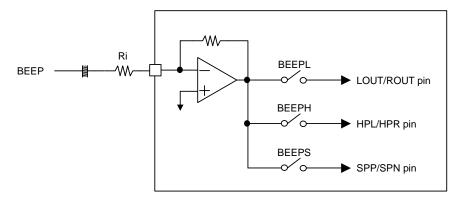

| <b>BEEP Input:</b> BEEF            | P pin (Exter                       | nal Input Resistance=2         | 20kΩ)            |               |                                         |                         |

| Maximum Input Vo                   | ltage (Note                        | 24)                            | -                | 1.98          | -                                       | Vpp                     |

| Gain (Note 25)                     |                                    |                                |                  |               |                                         |                         |

| BEEP $\rightarrow$ LOU'            | T/ROUT                             | LOVL bit = " $0$ "             | -4.5             | 0+4.5         |                                         | dB                      |

|                                    |                                    | LOVL bit = "1"                 | -                | +2            | -                                       | dB                      |

| BEEP $\rightarrow$ HPL/            | HPR                                | HPG bit = " $0$ "              | -24.5            | -20           | -15.5                                   | dB                      |

|                                    |                                    | HPG bit = "1"                  | -                | -16.4         | - dB                                    |                         |

| BEEP $\rightarrow$ SPP/S           | SPN                                | •                              |                  |               |                                         |                         |

| ALC b                              | oit = "0", SH                      | PKG1-0 bits = "00"             | -0.57            | +4.43 +       | 8.93                                    | dB                      |

| ALC b                              | ALC bit = "0", SPKG1-0 bits = "01" |                                |                  | +6.43         | -                                       | dB                      |

| ALC bit = "0", SPKG1-0 bits = "10" |                                    |                                | -                | +10.65        | -                                       | dB                      |

|                                    |                                    | PKG1-0 bits = "11"             | -                | +12.65        | -                                       | dB                      |

| ALC t                              | oit = "1", SF                      | PKG1-0 bits = "00"             |                  | +6.43         |                                         | dB                      |

| ALC b                              | oit = "1", SF                      | PKG1-0 bits = "01"             |                  | +8.43         |                                         | dB                      |

| ALC t                              | oit = "1", SF                      | PKG1-0 bits = "10"             |                  | +12.65        |                                         | dB                      |

| ALC t                              | oit = "1", SH                      | PKG1-0 bits = "11"             | -                | +14.65        | -                                       | dB                      |

Note 21. Output voltage is proportional to AVDD voltage.

Vout = 0.94 x AVDD(typ)@SPKG1-0 bits = "00", 1.19 x AVDD(typ)@SPKG1-0 bits = "01", 2.05 x

AVDD(typ)@SPKG1-0 bits = "10", 2.58 x AVDD(typ)@SPKG1-0 bits = "11" at Full-differential output.

Note 22. In case of measuring at SPP and SPN pins.

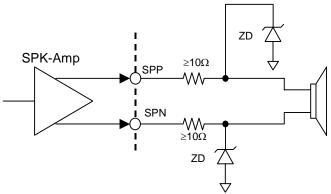

Note 23. Load impedance is total impedance of series resistance and piezo speaker impedance at 1kHz in Figure 33. Load capacitance is capacitance of piezo speaker. When piezo speaker is used,  $10\Omega$  or more series resistors should be connected at both SPP and SPN pins, respectively.

Note 24. Maximum voltage is in proportion to both AVDD and external input resistance (Rin). Vin = 0.6 x AVDD x Rin /  $20k\Omega$  (typ).

Note 25. The gain is in inverse proportion to external input resistance.

| Para | meter                            | min typ |    | max | Units |

|------|----------------------------------|---------|----|-----|-------|

| Powe | r Supplies:                      |         |    |     |       |

| Powe | r-Up (PDN pin = "H")             |         |    |     |       |

|      | All Circuit Power-up:            |         |    |     |       |

|      | AVDD+DVDD (Note 26)              | -       | 15 | 23  | mA    |

|      | HVDD: HP-Amp Normal Operation    | - 5     |    | 8   | mA    |

|      | No Output (Note 27)              | - 5     |    | 0   | IIIA  |

|      | HVDD: SPK-Amp Normal Operation   | - 8     |    | 24  | mA    |

|      | No Output (Note 28)              | - 0     |    | 24  | IIIA  |

| Powe | r-Down (PDN pin = "L") (Note 29) |         |    |     |       |

| AV   | DD+ DVDD+HVDD                    | -       | 10 | 100 | μA    |

Note 26. PLL Master Mode (MCKI=12.288MHz) and PMADL = PMADR = PMDAC = PMLO = PMHPL = PMHPR = PMSPK = PMVCM = PMPLL = MCKO = PMBP = PMMP = M/S bits = "1". MPWR pin outputs 0mA. AVDD=11mA(typ), DVDD=4mA(typ).

EXT Slave Mode (PMPLL = M/S = MCKO bits = "0"): AVDD=10mA(typ), DVDD=3mA(typ).

Note 27. PMADL = PMADR = PMDAC = PMLO = PMHPL = PMHPR = PMVCM = PMPLL = PMBP bits = "1" and PMSPK bit = "0".

Note 28. PMADL = PMADR = PMDAC = PMLO = PMSPK = PMVCM = PMPLL = PMBP bits = "1" and PMHPL = PMHPR bits = "0".

Note 29. All digital input pins are fixed to DVDD or DVSS.

|                        |                 | FIL         | TER CHAR          | ACTERISTIC     | S           |             |       |

|------------------------|-----------------|-------------|-------------------|----------------|-------------|-------------|-------|

| (Ta=25°C; AVDD, DV     | DD=2.6          | ~ 3.6V; HVD | $D=2.6 \sim 5.25$ | /; fs=44.1kHz; | DEM=OFF; FI | L1=FIL3=EQ= | OFF)  |

| Parameter Symbol       |                 |             |                   | min            | typ         | max         | Units |

| ADC Digital Filter (De | ecimatio        | n LPF):     |                   |                |             |             |       |

| Passband (Note 30)     |                 | ±0.16dB     | PB                | 0              | -           | 17.3        | kHz   |

|                        |                 | -0.66dB     | -                 |                | 19.4        | -           | kHz   |

|                        |                 | -1.1dB      | -                 |                | 19.9        | -           | kHz   |

|                        |                 | -6.9dB      | -                 |                | 22.1        | -           | kHz   |

| Stopband SB            |                 |             |                   | 26.1           | -           | -           | kHz   |

| Passband Ripple        |                 |             | PR                | -              | -           | ±0.1        | dB    |

| Stopband Attenuation   |                 |             | SA                | 73             | -           | -           | dB    |

| Group Delay (Note 31)  |                 |             | GD                | -              | 19          | -           | 1/fs  |

| Group Delay Distortion | l               |             | $\Delta GD$       | -              | 0           | -           | μs    |

| ADC Digital Filter (H  | <b>PF):</b> (No | te 32)      |                   |                |             |             |       |

| Frequency Response (N  | lote 30)        | -3.0dB      | FR                | -              | 0.9         | -           | Hz    |

|                        |                 | -0.5dB      | -                 |                | 2.7         | -           | Hz    |

|                        |                 | -0.1dB      | -                 |                | 6.0         | -           | Hz    |

| DAC Digital Filter (Ll | PF):            |             |                   |                |             |             |       |

| Passband (Note 30)     |                 | ±0.1dB      | PB                | 0              | -           | 19.6        | kHz   |

| × ,                    |                 | -0.7dB      | -                 |                | 20.0        | -           | kHz   |

|                        |                 | -6.0dB      | -                 |                | 22.05       | -           | kHz   |

| Stopband SB            |                 | 1           |                   | 25.2           | -           | -           | kHz   |

| Passband Ripple        |                 |             | PR                | -              | -           | ±0.01       | dB    |

| Stopband Attenuation   |                 |             | SA                | 59             | -           | -           | dB    |

| Group Delay (Note 31)  |                 |             | GD                | -              | 22          | -           | 1/fs  |

| DAC Digital Filter (Ll | PF) + SC        | <b>F:</b>   |                   |                |             |             |       |

| Frequency Response: 0  |                 |             | FR                | -              | ±1.0        | -           | dB    |

| DAC Digital Filter (H  |                 |             | 1                 |                | 1           | 1           |       |

| Frequency Response (N  |                 | -3.0dB      | FR                | -              | 0.9         | _           | Hz    |

|                        |                 | -0.5dB      | _                 |                | 2.7         | -           | Hz    |

|                        |                 | -0.1dB      | -                 |                | 6.0         | -           | Hz    |

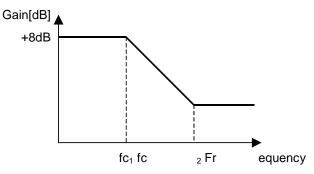

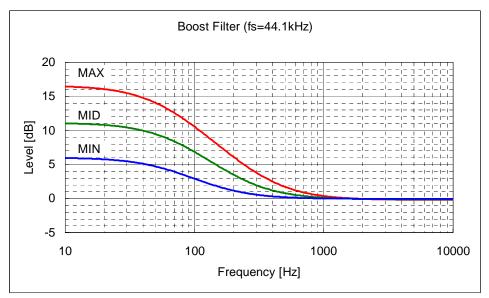

| BOOST Filter: (Note 3  | 33)             |             |                   |                |             |             |       |

| Frequency Response     | MIN             | 20Hz        | FR                | -              | 5.76        | -           | dB    |

| quency response        |                 | 100Hz       |                   | _              | 2.92        | - dB        |       |

|                        |                 | 1kHz        |                   | _              | 0.02        | - dB        |       |

|                        | MID             | 20Hz        | FR                | -              | 10.80       | -           | dB    |

|                        |                 | 100Hz       |                   | _              | 6.84        | - dB        |       |

|                        |                 | 1kHz        |                   | _              | 0.13        | - dB        |       |

|                        | MAX             | 20Hz        | FR                | -              | 16.06       | -           | dB    |

|                        |                 | 100Hz       |                   | _              | 10.54       | - dB        |       |

|                        |                 | 1kHz        |                   | _              | 0.37        | - dB        |       |

Note 30. The passband and stopband frequencies scale with fs (system sampling rate).

For example, ADC is PB=0.454\*fs (@-1.0dB). Each response refers to that of 1kHz.

- Note 31. The calculated delay time caused by digital filtering. This time is from the input of analog signal to setting of the 16-bit data of both channels from the input register to the output register of the ADC. This time includes the group delay of the HPF. For the DAC, this time is from setting the 16-bit data of both channels from the input register to the output of analog signal.

- Note 32. When PMADL bit = "1" or PMADR bit = "1", the HPF of ADC is enabled but the HPF of DAC is disabled. When PMADL=PMADR bits = "0", PMDAC bit = "1", the HPF of DAC is enabled but the HPF of ADC is disabled.

Note 33. These frequency responses scale with fs. If a high-level and low frequency signal is input, the analog output clips to the full-scale.

| DC CHARACTERISTICS                                 |         |          |     |         |       |  |  |  |  |  |

|----------------------------------------------------|---------|----------|-----|---------|-------|--|--|--|--|--|

| (Ta=25°C; AVDD, DVDD=2.6 ~ 3.6V; HVDD=2.6 ~ 5.25V) |         |          |     |         |       |  |  |  |  |  |

| Parameter Symbol                                   |         | min      | typ | Max     | Units |  |  |  |  |  |

| High-Level Input Voltage                           | VIH     | 70%DVDD  | -   | -       | V     |  |  |  |  |  |

| Low-Level Input Voltage                            | VIL     | -        | -   | 30%DVDD | V     |  |  |  |  |  |

| High-Level Output Voltage (Iout=-200µA             | ) VOH   | DVDD-0.2 | -   | -       | V     |  |  |  |  |  |

| Low-Level Output Voltage                           |         |          |     |         |       |  |  |  |  |  |

| (Except SDA pin: Iout=200µA                        | ) VOL - |          | -   | 0.2     | V     |  |  |  |  |  |

| (SDA pin: Iout=3mA                                 | ) VOL   | -        | -   | 0.4     | V     |  |  |  |  |  |

| Input Leakage Current                              | Iin     | -        | -   | ±10     | μΑ    |  |  |  |  |  |

|    | SWITCHIN                                 | G CHARA                 | CTERISTICS |          |          |       |

|----|------------------------------------------|-------------------------|------------|----------|----------|-------|

| (T | a=25°C; AVDD, DVDD=2.6 ~ 3.6V; HVDD=2.6  | ~ 5.25V; C <sub>I</sub> | _=20pF)    |          |          |       |

| Pa | rameter Symbol                           |                         | min        | typ      | max      | Units |

| PI | L Master Mode (PLL Reference Clock = MCK | I pin)                  |            |          |          |       |

|    | MCKI Input Timing                        |                         |            |          |          |       |

|    | F requency                               | fCLK                    | 11.2896    | -        | 27       | MHz   |

|    | Pulse Width Low                          | tCLKL                   | 0.4/fCLK   | -        | -        | ns    |

|    | Pulse Width High                         | tCLKH                   | 0.4/fCLK   | -        | -        | ns    |

|    | MCKO Output Timing                       |                         |            |          |          | 1     |

|    | F requency                               | fMCK                    | 0.2352     | -        | 12.288   | MHz   |

|    | Dut <u>y Cycle</u>                       |                         |            |          |          |       |

|    | Except 256fs at fs=32kHz, 29.4kHz        | dMCK                    | 40         | 50       | 60       | %     |

|    | 256fs at fs=32kHz, 29.4kHz               | dMCK                    | -          | 33       | -        | %     |

|    | LRCK Output Timing                       |                         |            |          |          |       |

|    | F requency                               | fs                      | 7.35       | -        | 48       | kHz   |

|    | Dut y Cycle                              | Duty                    | -          | 50       | -        | %     |

|    | BICK Output Timing                       |                         |            |          |          |       |

|    | Period BCKO bit = "0"                    | tBCK                    | -          | 1/(32fs) | -        | ns    |

|    | BCKO bit = "1"                           | tBCK                    | -          | 1/(64fs) | -        | ns    |

|    | Dut y Cycle                              | dBCK                    | -          | 50       | -        | %     |

| PI | L Slave Mode (PLL Reference Clock = MCKI | pin)                    |            |          |          |       |

|    | MCKI Input Timing                        |                         |            |          |          |       |

|    | F requency                               | fCLK                    | 11.2896    | -        | 27       | MHz   |

|    | Pulse Width Low                          | tCLKL                   | 0.4/fCLK   | -        | -        | ns    |

|    | Pulse Width High                         | tCLKH                   | 0.4/fCLK   | -        | -        | ns    |

|    | MCKO Output Timing                       |                         |            |          |          |       |

|    | F requency                               | fMCK                    | 0.2352     | -        | 12.288   | MHz   |

|    | Dut y Cycle                              |                         |            |          |          |       |

|    | Except 256fs at fs=32kHz, 29.4kHz        | dMCK                    | 40         | 50       | 60       | %     |

|    | 256fs at fs=32kHz, 29.4kHz               | dMCK                    | -          | 33       | -        | %     |

|    | LRCK Input Timing                        |                         |            |          | -        |       |

|    | F requency                               | fs                      | 7.35       | -        | 48       | kHz   |

|    | Dut y                                    | Duty                    | 45         | -        | 55       | %     |

|    | BICK Input Timing                        |                         |            |          |          |       |

|    | P eriod                                  | tBCK                    | 1/(64fs)   | -        | 1/(32fs) | ns    |

|    | Pulse Width Low                          | tBCKL                   | 0.4 x tBCK | -        | -        | ns    |

|    | Pulse Width High                         | tBCKH                   | 0.4 x tBCK |          | -        | ns    |

| Para | ameter Symbol   |                                    |            | min        | typ       | max      | Units |

|------|-----------------|------------------------------------|------------|------------|-----------|----------|-------|

|      | -               | PLL Reference Clock = LRC          | CK pin)    |            |           |          |       |

|      | LRCK Input T    |                                    | <b>F</b> ) |            |           |          |       |

|      | F requency      | 8                                  | fs         | 7.35       | -         | 48       | kHz   |

|      | Dut y           |                                    | Duty       | 45         | -         | 55       | %     |

|      | BICK Input Ti   | ming                               | Duty       | 10         |           | 55       | 70    |

|      | P eriod         |                                    | tBCK       | 1/(64fs)   | _         | 1/(32fs) | ns    |

|      | Pulse Width     | Low                                | tBCKL      | 240        |           | 17(3213) | ns    |

|      | Pulse Width     |                                    | tBCKE      | 240        |           |          | ns    |

| DII  |                 |                                    |            | 240        | _         | -        | 115   |

|      |                 | PLL Reference Clock = BIC          | K pin)     |            |           |          |       |

|      | LRCK Input Ti   | iming                              | C          | 7.25       |           | 40       | 1.11  |

|      | F requency      |                                    | fs         | 7.35       | -         | 48       | kHz   |

|      | Dut y           | •                                  | Duty       | 45         | -         | 55       | %     |

| Ŀ    | BICK Input Ti   |                                    | D GV       |            | 1 ((226.) | T        |       |

|      | Period          | PLL3-0 bits = "0010"               | tBCK       | -          | 1/(32fs)  | -        | ns    |

|      |                 | PLL3-0 bits = "0011"               | tBCK       | -          | 1/(64fs)  | -        | ns    |

|      | Pulse Width     |                                    | tBCKL      | 0.4 x tBCK | -         | -        | ns    |

|      | Pulse Width     | High                               | tBCKH      | 0.4 x tBCK | -         | -        | ns    |

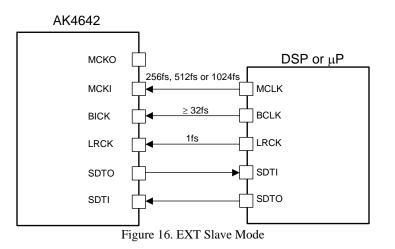

|      | ernal Slave Mo  |                                    |            |            |           |          |       |

| N    | MCKI Input Ti   | iming                              |            |            |           |          |       |

| ]    | F requency      | 256fs                              | fCLK       | 1.8816     | -         | 12.288   | MHz   |

|      |                 | 512fs                              | fCLK       | 3.7632     | -         | 13.312   | MHz   |

|      |                 | 1024fs                             | fCLK       | 7.5264     | -         | 13.312   | MHz   |

|      | Pulse Width     | Low                                | tCLKL      | 0.4/fCLK   | -         | -        | ns    |

|      | Pulse Width     | High                               | tCLKH      | 0.4/fCLK   | -         | -        | ns    |

| T    | RCK Input Ti    |                                    |            |            |           |          |       |

|      | Frequency       | 256fs                              | fs         | 7.35       | -         | 48       | kHz   |

|      | Trequency       | 512fs                              | fs         | 7.35       | -         | 26       | kHz   |

|      |                 | 1024fs                             | fs         | 7.35       | -         | 13       | kHz   |

|      | Duty            | 102115                             | Duty       | 45         | _         | 55       | %     |

| F    | BICK Input Til  | ming                               | Duty       | 15         |           | 55       | 70    |

| 1    | Period          | lining                             | tBCK       | 312.5      |           | _        | ns    |

|      | Pulse Width     | Low                                | tBCKL      | 130        | -         | _        |       |

|      | Pulse Width     |                                    | tBCKL      | 130        | -         | -        | ns    |

| . 1  |                 | 0                                  | IDCKH      | 130        | -         | -        | ns    |

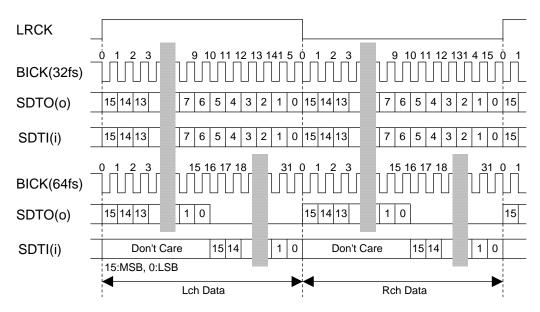

|      | io Interface Ti | ming                               |            |            |           |          |       |

| Mas  | s ter Mode      |                                    |            |            | 10        | T        |       |

|      |                 | LRCK Edge (Note 34)                | tMBLR      | -40        | - 40      |          | ns    |

|      |                 | to SDTO (MSB)                      | tLRD       | -70        | -         | 70       | ns    |

|      |                 | (Except I <sup>2</sup> S mode)     |            |            |           |          |       |

|      | BICK "↓" to     |                                    | tBSD       | -70        | - 70      |          | ns    |

|      | SDTI Hold 7     | Гime                               | tSDH       | 50         | -         | -        | ns    |

|      | SDTI Setup      | Time                               | tSDS       | 50         | -         | -        | ns    |

| S    | Slave Mode      |                                    |            |            |           |          |       |

|      |                 | to BICK " <sup>↑</sup> " (Note 34) | tLRB 50    |            | -         | -        | ns    |

|      |                 | LRCK Edge (Note 34)                | tBLR 50    |            | -         | -        | ns    |

|      |                 | to SDTO (MSB)                      | tLRD       | -          | -         | 80       | ns    |

|      | Liten Lugo      | (Except $I^2S$ mode)               |            |            |           |          |       |

|      | BICK "↓" to     |                                    | tBSD -     |            | _         | 80       | ns    |

|      | S DTI Hold      |                                    | tSDH       | 50         | _         | -        | ns    |

| ,    | SDTI Setup      |                                    | tSDN       | 50         | -         | -        |       |

|      | - som settip    |                                    | ເວບວ       | 50         | -         | -        | ns    |

Note 34. BICK rising edge must not occur at the same time as LRCK edge.

| Parameter Sym                                          | bol      | min | typ  | max | Units |

|--------------------------------------------------------|----------|-----|------|-----|-------|

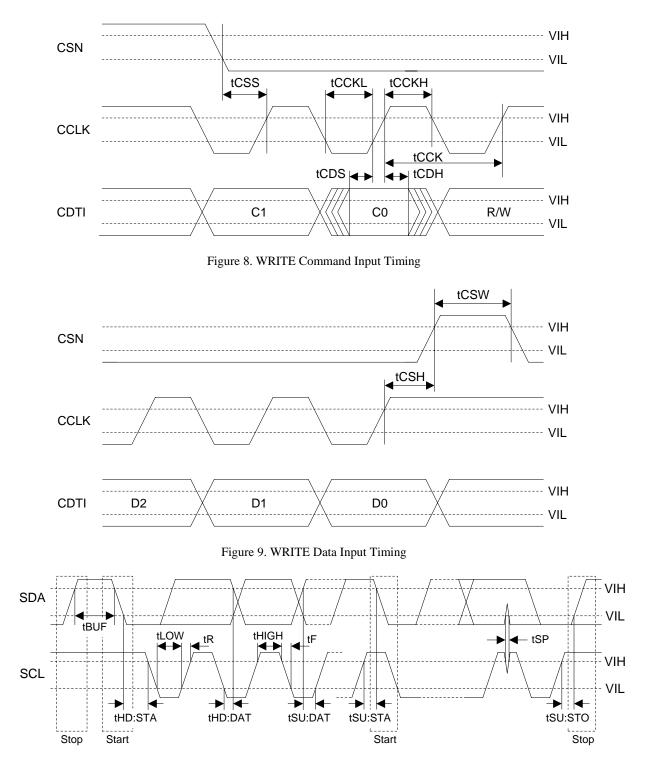

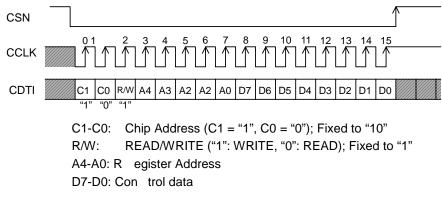

| Control Interface Timing (3-wire Serial mode)          |          |     |      |     |       |

| CCLK Period                                            | tCCK 200 | )   | -    | -   | ns    |

| CCLK Pulse Width Low                                   | tCCKL    | 80  | -    | -   | ns    |

| Pulse Width High                                       | tCCKH    | 80  | -    | -   | ns    |

| CDTI Setup Time                                        | tCDS     | 40  | -    | -   | ns    |

| CDTI Hold Time                                         | tCDH     | 40  | -    | -   | ns    |

| CSN "H" Time                                           | tCSW     | 150 | -    | -   | ns    |

| CSN "↓" to CCLK "↑"                                    | tCSS 50  |     | -    | -   | ns    |

| CCLK "↑" to CSN "↑"                                    | tCSH 50  |     | -    | -   | ns    |

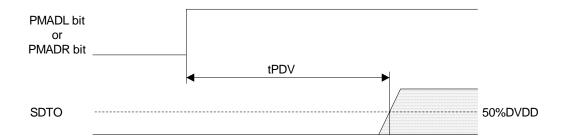

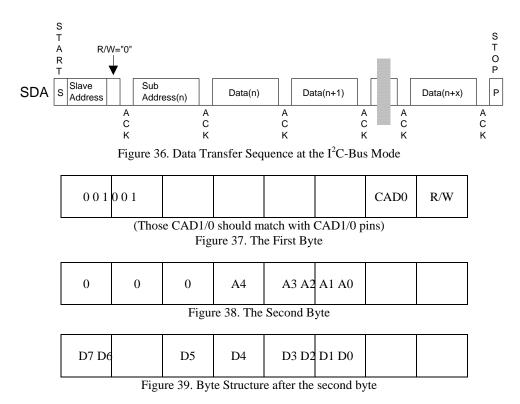

| Control Interface Timing (I <sup>2</sup> C Bus mode):  |          |     |      |     |       |

| SCL Clock Frequency                                    | fSCL -   |     | -    | 400 | kHz   |

| Bus Free Time Between Transmissions                    | tBUF 1.3 |     | -    | -   | μs    |

| Start Condition Hold Time (prior to first clock pulse) | tHD:STA  | 0.6 | -    | -   | μs    |

| Clock Low Time                                         | tLOW     | 1.3 | -    | -   | μs    |

| Clock High Time                                        | tHIGH    | 0.6 | -    | -   | μs    |

| Setup Time for Repeated Start Condition                | tSU:STA  | 0.6 | -    | _   | μs    |

| SDA Hold Time from SCL Falling (Note 35)               | tHD:DAT  | 0   | -    | -   | μs    |

| SDA Setup Time from SCL Rising                         | tSU:DAT  | 0.1 | -    | -   | μs    |

| Rise Time of Both SDA and SCL Lines                    | tR       | -   | -    | 0.3 | μs    |

| Fall Time of Both SDA and SCL Lines                    | tF       | -   | -    | 0.3 | μs    |

| Setup Time for Stop Condition                          | tSU:STO  | 0.6 | -    | -   | μs    |

| Pulse Width of Spike Noise Suppressed by Input Filter  | tSP      | 0   | -    | 50  | ns    |

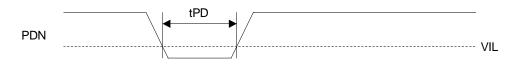

| Power-down & Reset Timing                              |          |     |      |     |       |

| PDN Pulse Width (Note 36)                              | tPD 150  |     | -    | -   | ns    |

| PMADL or PMADR "↑" to SDTO valid (Note 37)             | tPDV -   |     | 1059 | -   | 1/fs  |

Note 35. Data must be held long enough to bridge the 300ns-transition time of SCL.

Note 36. The AK4642 can be reset by the PDN pin = "L". Note 37. This is the count of LRCK " $\uparrow$ " from the PMADL or PMADR bit = "1".

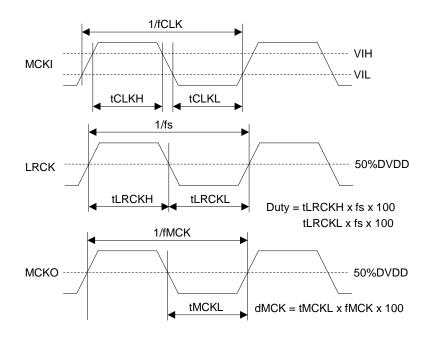

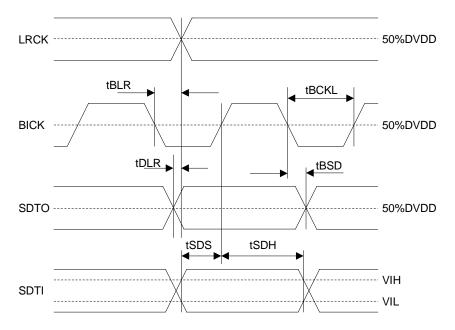

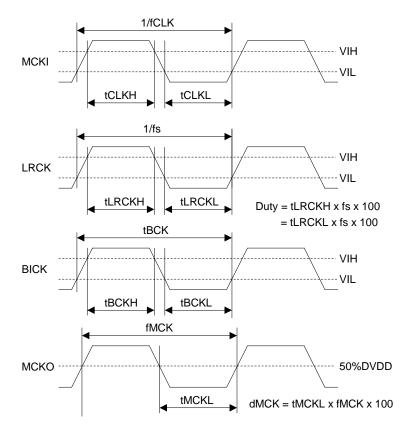

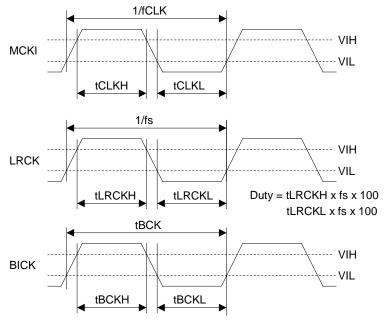

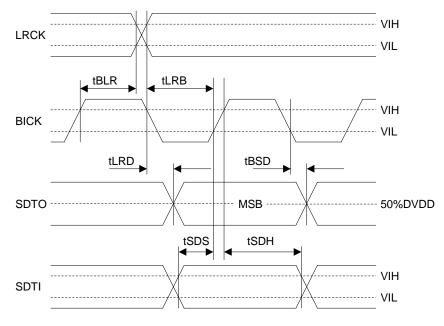

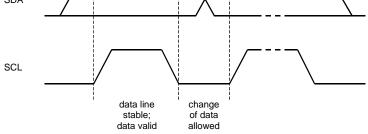

### Timing Diagram

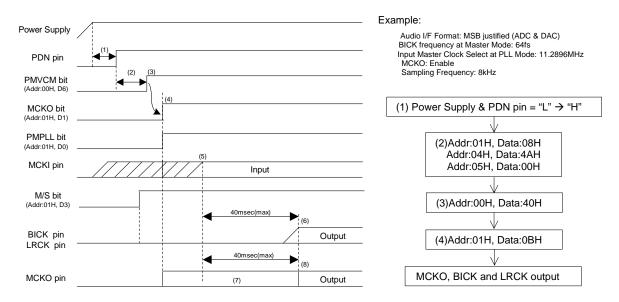

Figure 3. Clock Timing (PLL Master mode)

Figure 4. Audio Interface Timing (PLL Master mode)

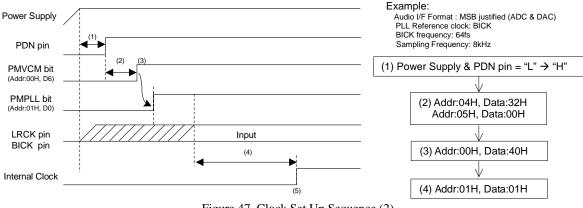

Figure 5. Clock Timing (PLL Slave mode; PLL Reference Clock = MCKI pin)

Figure 6. Clock Timing (EXT Slave mode)

Figure 7. Audio Interface Timing (PLL/EXT Slave mode)

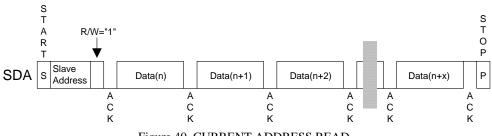

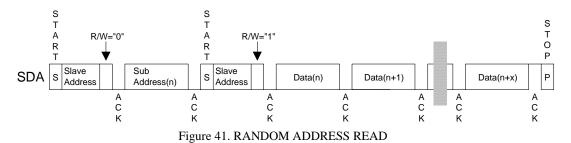

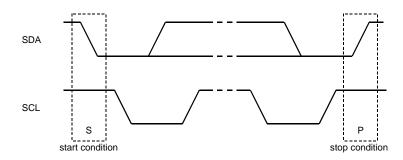

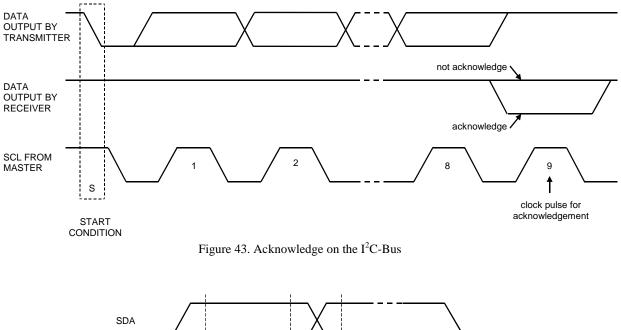

Figure 10. I<sup>2</sup>C Bus Mode Timing

Figure 11. Power Down & Reset Timing 1

Figure 12. Power Down & Reset Timing 2

### **OPERATION OVERVIEW**

### System Clock

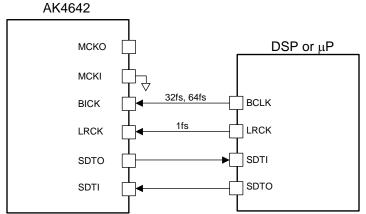

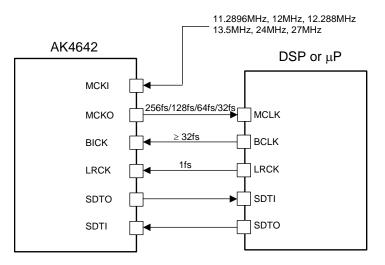

There are the following four clock modes to interface with external devices (see Table 1 and Table 2).

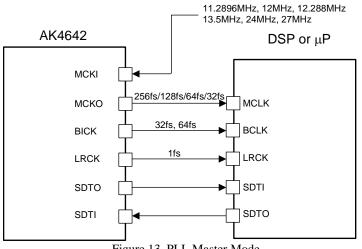

| Mode                                                        | PMPLL bit | M/S bit | PLL3-0 bits | Figure    |

|-------------------------------------------------------------|-----------|---------|-------------|-----------|

| PLL Master Mode                                             | 1         | 1       | See Table 4 | Figure 13 |

| PLL Slave Mode 1<br>(PLL Reference Clock: MCKI pin)         | 1         | 0       | See Table 4 | Figure 14 |

| PLL Slave Mode 2<br>(PLL Reference Clock: LRCK or BICK pin) | 1         | 0       | See Table 4 | Figure 15 |

| EXT Slave Mode                                              | 0         | 0       | Х           | Figure 16 |

| Don't Care (Note 38)                                        | 0         | 1       | Х           | -         |

Note 38. If this mode is selected, the invalid clocks are output from MCKO pin when MCKO bit is "1". Table 1. Clock Mode Setting (x: Don't care)

| Mode                                                      | MCKO bit | MCKO pin                  | MCKI pin               | BICK pin                           | LRCK pin       |  |

|-----------------------------------------------------------|----------|---------------------------|------------------------|------------------------------------|----------------|--|

|                                                           | 0        | "L"                       | Selected by            | Output                             | Output         |  |

| PLL Master Mode                                           | 1        | Selected by<br>PS1-0 bits | PLL3-0 bits            | (Selected by<br>BCKO bit)          | (1fs)          |  |

| PLL Slave Mode                                            | 0        | "L"                       | Selected by            | Input                              | Input          |  |

| (PLL Reference Clock: MCKI pin)                           | 1        | Selected by PS1-0 bits    | PLL3-0 bits            | (Selectet by<br>BCKO bit)          | (1fs)          |  |

| PLL Slave Mode<br>(PLL Reference Clock: LRCK or BICK pin) | 0 "L"    |                           | GND                    | Input<br>(Selected by<br>BCKO bit) | Input<br>(1fs) |  |

| EXT Slave Mode                                            | 0        | "L"                       | Selected by FS3-0 bits | Input<br>(≥ 32fs)                  | Input<br>(1fs) |  |

Table 2. Clock pins state in Clock Mode

### ■ Master Mode/Slave Mode

The M/S bit selects either master or slave mode. M/S bit = "1" selects master mode and "0" selects slave mode. When the AK4642 is power-down mode (PDN pin = "L") and exits reset state, the AK4642 is slave mode. After exiting reset state, the AK4642 goes to master mode by changing M/S bit = "1".

When the AK4642 is used by master mode, LRCK and BICK pins are a floating state until M/S bit becomes "1". LRCK and BICK pins of the AK4642 should be pulled-down or pulled-up by the resistor (about  $100k\Omega$ ) externally to avoid the floating state.

| M/S bit | Mode       |         |

|---------|------------|---------|

| 0 S     | lave Mode  | Default |

| 1 M     | aster Mode |         |

Table 3. Select Master/Salve Mode

### PLL Mode

When PMPLL bit is "1", a fully integrated analog phase locked loop (PLL) generates a clock that is selected by the PLL3-0 and FS3-0 bits. The PLL lock time is shown in Table 4, whenever the AK4642 is supplied to a stable clocks after PLL is powered-up (PMPLL bit = "0"  $\rightarrow$  "1") or sampling frequency changes.

| Mode   | PLL3<br>bit | PLL2<br>bit | PLL1<br>bit | PLL0<br>bit | PLL<br>Reference<br>Clock Input<br>Pin | Input<br>Frequency | R and<br>VCO<br>R[Ω] |      | PLL Lock<br>Time<br>(max) |         |

|--------|-------------|-------------|-------------|-------------|----------------------------------------|--------------------|----------------------|------|---------------------------|---------|

| 0      | 0           | 000         |             |             | LRCK pin                               | 1fs                | 6.8k                 | 220n | 160ms                     | Default |