#### AKM Preliminary

# **AK8851**

# **NTSC/PAL/SECAM** Digital Video Decoder

# **General Description**

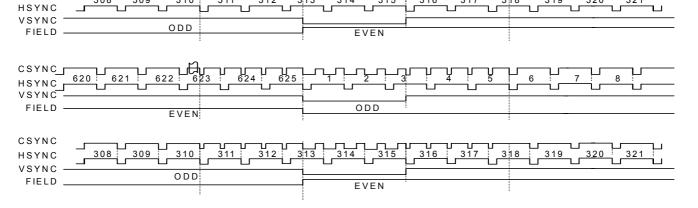

The AK8851 is an integrated chip that decodes NTSC, PAL, SECAM composite and S Video signals...

The digital output of the AK8851 is in Y, Cb, Cr signal format which compliances with ITU-R BT.601 and ITU-R BT.656\*

specifications.

An internally generated pixel clock is synchronized with an input signal. The clock rate is 27 MHz. When Closed Caption, VBID or WSS information are encoded on input Video signal, they are externally accessible.

# Features

- NTSC-M, NTSC-4.43/PAL-B, D, G, H, I, N, Nc, M, 60/SECAM Composite signals and S Video signal decoding function

- On-chip dual 10 Bit ADCs (27 MHz operation)

- Built-in PLLs for input-signal-synchronized clock generation (Line-locked PLL and Frame-locked PLL)

- On-chip Programmable Gain Amp (PGA), ranging from 0 dB to 12 dB

- Auto Color Control (ACC)

- Auto Gain Control (AGC)

- · Automatic input signal distinction function

- Adaptive 3-/5-line (NTSC/PAL) YC Separation

- · Phase compensation function for PAL signal decoding

- ITU-R BT.656 format output (4:2:2 8 Bit parallel output with EAV / SAV)/ 16-Bit output is also available

- NTSC Closed Caption signal decoding function

- VBID (CGM-A) Program condition decoding function (CRCC decode)

- · WSS Program condition decoding function

- VBI slicer function

- Macrovision Certification

- Power down function

- 6 channel Analog inputs

- I2C Control

- 3.3 V +/- 10 % CMOS

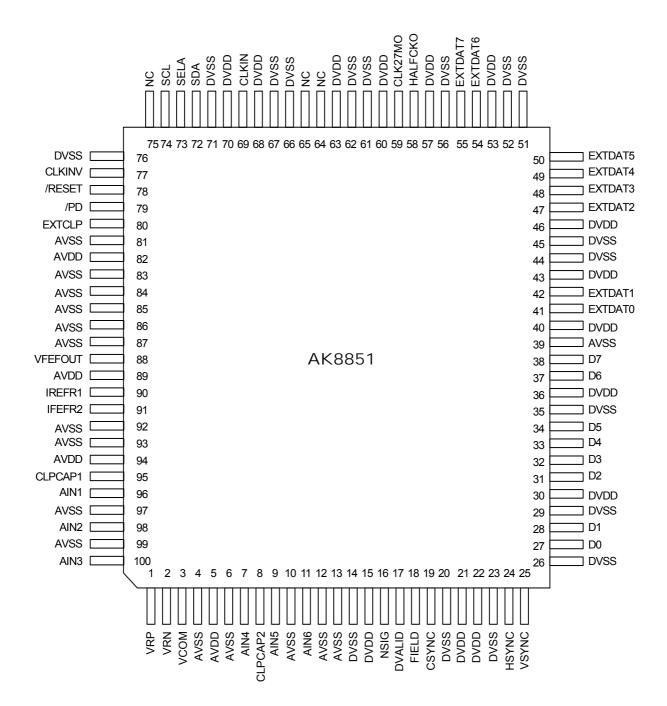

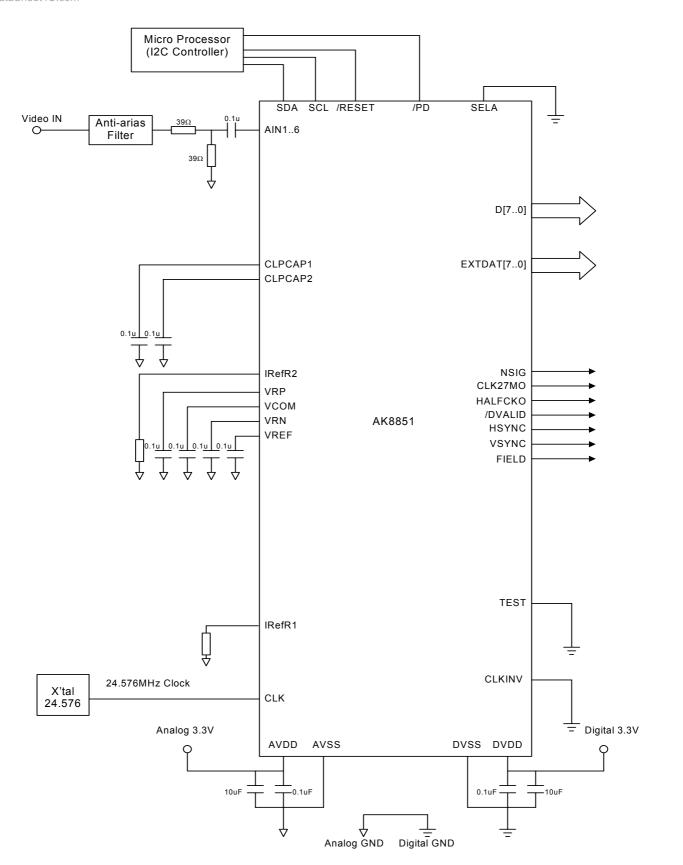

- 100 Pin LQFP package

Note: \* ITU-R BT.656 spec compatibility requires appropriate input signal quality.

2005/07

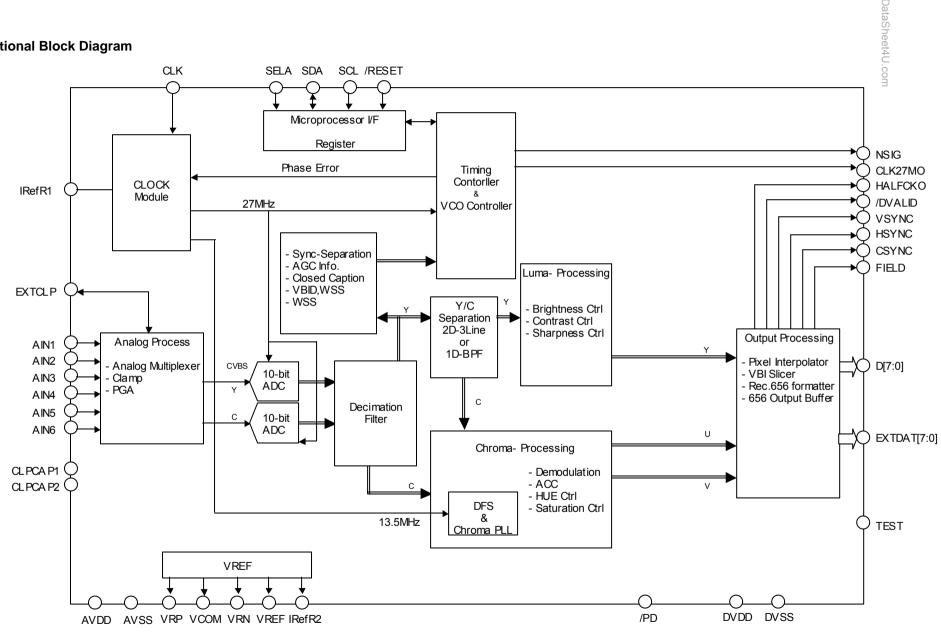

**1.Functional Block Diagram** CLK

| ataSpin#U. | Copm Symbol |   | Function                                                                            |

|------------|-------------|---|-------------------------------------------------------------------------------------|

|            | VRP         | 0 | Function                                                                            |

| 1          | VRP         | 0 | Internal reference positive Voltage for AD Converter                                |

| 2          | VRN<br>VCOM |   | Internal reference negative Voltage for AD Converter                                |

| 3          |             | 0 | Common voltage for AD Converter                                                     |

| 4          | AVSS        | G | Ground pin for Analog                                                               |

| 5          | AVDD        | P | Analog supply voltage (3.3V)                                                        |

| 6          | AVSS        | G | Ground pin for Analog                                                               |

| 7          | AIN4        | I | Analog Video Signal Input pin.                                                      |

|            |             |   | Input –6dB analog video signal via 0.1uF capacitor.                                 |

| 8          | CLPCAP2     | 0 | Capacitor for clamp.                                                                |

|            |             |   | Connect 0.1uF ceramic capacitor between AVSS                                        |

| 9          | AIN5        | I | Analog Video Signal Input pin.                                                      |

| 10         | A) (0.0     | - | Input –6dB analog video signal via 0.1uF capacitor.                                 |

| 10         | AVSS        | G | Ground pin for Analog                                                               |

| 11         | AIN6        | I | Analog Video Signal Input pin.                                                      |

| 10         | AV/00       | - | Input –6dB analog video signal via 0.1uF capacitor.                                 |

| 12         | AVSS        | G | Ground pin for Analog                                                               |

| 13         | AVSS        | G | Ground pin for Analog                                                               |

| 14         | DVSS        | G | Ground pin for Digital                                                              |

| 15         | DVDD        | Р | Digital supply voltage (3.3V)                                                       |

| 10         | NOID        | • | No-signal indicator.                                                                |

| 16         | NSIG        | 0 | H: No input video Signal                                                            |

|            |             |   | L: Video Signal Input                                                               |

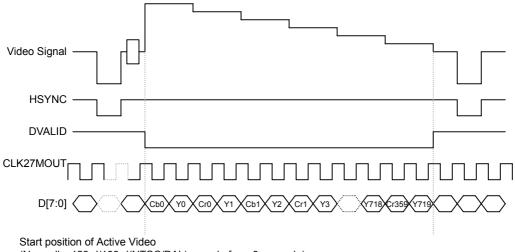

| 17         | DVALID      | 0 | Active video data (720pixel) indicator                                              |

| 18         | FIELD       | 0 | Timing signal for FIELD                                                             |

| 19         | CSYNC       | 0 | Timing signal for CSYNC                                                             |

| 20         | DVSS        | G | Ground pin for Digital                                                              |

| 21         | DVDD        | P | Digital supply voltage (3.3V)                                                       |

| 22         | DVDD        | P | Digital supply voltage (3.3V)                                                       |

| 23         | DVSS        | G | Ground pin for Digital                                                              |

| 24         | HSYNC       | 0 | Timing signal for HSYNC                                                             |

| 25         | VSYNC       | 0 | Timing signal for VSYNC                                                             |

| 26         | DVSS        | G | Ground pin for Digital                                                              |

| 27         | D0          | 0 | Decoded Data output pin (LSB)                                                       |

| 28         | D1          | 0 | Decoded Data output pin                                                             |

| 29         | DVSS        | G | Ground pin for Digital                                                              |

| 30         | DVDD        | Р | Digital supply voltage (3.3V)                                                       |

| 31         | D2          | 0 | Decoded Data output pin                                                             |

| 32         | D3          | 0 | Decoded Data output pin                                                             |

| 33         | D4          | 0 | Decoded Data output pin                                                             |

| 34         | D5          | 0 | Decoded Data output pin                                                             |

| 35         | DVSS        | G | Ground pin for Digital                                                              |

| 36         | DVDD        | Р | Digital supply voltage (3.3V)                                                       |

| 37         | D6          | 0 | Decoded Data output pin                                                             |

| 38         | D7          | 0 | Decoded Data output pin (MSB)                                                       |

| 39         | AVSS        | G | Ground pin for Analog                                                               |

| 40         | DVDD        | Р | Digital supply voltage (3.3V)                                                       |

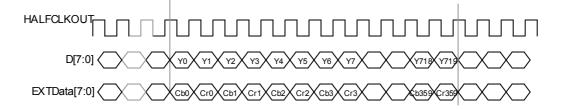

|            |             | 0 | Cb/Cr data output pin for 16-bit output mode (LSB)                                  |

| 41         | EXTDAT0     | 0 | Open this pin for 8-bit output mode                                                 |

| 40         |             | 0 | Cb/Cr data output pin for 16-bit output mode                                        |

| 42         | EXTDAT1     | 0 | Open this pin for 8-bit output mode                                                 |

| 43         | DVDD        | Р | Digital supply voltage (3.3V)                                                       |

| 44         | DVSS        | G | Ground pin for Digital                                                              |

| 45         | DVSS        | G | Ground pin for Digital                                                              |

| 46         | DVDD        | P | Digital supply voltage (3.3V)                                                       |

| 47         | EXTDAT2     | 0 |                                                                                     |

| 48         | EXTDAT3     | 0 | Cb/Cr data output pin for 16-bit output mode                                        |

| 49         | EXTDAT4     | 0 | Open this pin for 8-bit output mode                                                 |

| 50         | EXTDAT5     | 0 |                                                                                     |

| 51         | DVSS        | G | Ground pin for Digital                                                              |

| 52         | DVSS        | G | Ground pin for Digital                                                              |

|            |             | P | Digital supply voltage (3.3V)                                                       |

|            |             |   |                                                                                     |

| 53         | DVDD        |   | Cb/Cr data output pin for 16-bit output mode                                        |

|            | EXTDAT6     | 0 | Cb/Cr data output pin for 16-bit output mode                                        |

| 53<br>54   | EXTDAT6     | 0 | Cb/Cr data output pin for 16-bit output mode<br>Open this pin for 8-bit output mode |

| 53         |             |   | Cb/Cr data output pin for 16-bit output mode                                        |

| ASAHI KAS                 | EI      |     | [AK8851]                                                                             |

|---------------------------|---------|-----|--------------------------------------------------------------------------------------|

| 56                        | DVSS    | G   | Ground pin for Digital                                                               |

| ww.DataSh <b>59</b> t4U.c | DVDD    | Р   | Digital supply voltage (3.3V)                                                        |

| = 0                       |         | •   | Indicator for Y Data and Cb/Cr Data in 8-bit output mode                             |

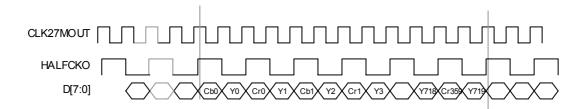

| 58                        | HALFCKO | 0   | (Indicator transition rate is 13.5MHz)                                               |

| 59                        | CLK27MO | 0   | 27MHz Clock output                                                                   |

| 60                        | DVDD    | P   | Digital supply voltage (3.3V)                                                        |

| 61                        | DVSS    | G   | Ground pin for Digital                                                               |

| 62                        | DVSS    | G   | Ground pin for Digital                                                               |

| 63                        | DVDD    | P   | Digital supply voltage (3.3V)                                                        |

|                           |         | Р   | Digital supply voltage (3.3V)                                                        |

| 64                        | NC      |     |                                                                                      |

| 65                        | NC      | -   |                                                                                      |

| 66                        | DVSS    | G   | Ground pin for Digital                                                               |

| 67                        | DVSS    | G   | Ground pin for Digital                                                               |

| 68                        | DVDD    | Р   | Digital supply voltage (3.3V)                                                        |

| 69                        | CLK     |     | Clock input pin (24.576MHz)                                                          |

| 70                        | DVDD    | Р   | Digital supply voltage (3.3V)                                                        |

| 71                        | DVSS    | G   | Ground pin for Digital                                                               |

| 72                        | SDA     | 1/0 | l <sup>2</sup> C bus Data                                                            |

| 73                        | SELA    | 1   | I <sup>2</sup> C bus address select                                                  |

| 74                        |         |     |                                                                                      |

|                           | SCL     |     | I <sup>2</sup> C bus clock                                                           |

| 75                        | NC      | -   |                                                                                      |

| 76                        | DVSS    | G   | Ground pin for Digital                                                               |

| 77                        | CLKINV  | I   | CLK27MO output polarization is determined by this pin                                |

| 78                        | /RESET  | 1   | Reset signal input pin (Low Active)                                                  |

| 70                        | /RESET  | '   | Reset sequence needs 24.576MHz Clock                                                 |

|                           |         |     | Power down control pin.                                                              |

|                           |         |     | L: Power down                                                                        |

| 79                        | /PD     | 1   | H: Active                                                                            |

|                           |         | -   | Reset sequence is necessary when Power Down signal after High                        |

|                           |         |     | All output pins become Low while Power down pin is Low.                              |

|                           |         |     | Monitor pin for internal clamp timing pulse.                                         |

| 80                        | EXTCLP  | I/O | External clamp timing pulse can be input on this pin by setting a register           |

| 00                        | EXICLE  | 1/0 |                                                                                      |

| 04                        | A) (0.0 | _   | Open this pin when not using                                                         |

| 81                        | AVSS    | G   | Ground pin for Analog                                                                |

| 82                        | AVDD    | Р   | Analog supply voltage (3.3V)                                                         |

| 83                        | AVSS    | G   | Ground pin for Analog                                                                |

| 84                        | AVSS    | G   | Ground pin for Analog                                                                |

| 85                        | AVSS    | G   | Ground pin for Analog                                                                |

| 86                        | AVSS    | G   | Ground pin for Analog                                                                |

| 87                        | AVSS    | G   | Ground pin for Analog                                                                |

|                           |         |     | Internal Vref Output pin                                                             |

| 88                        | VREFOUT | 0   | Connect ceramic capacitor (0.1uF -) between Analog Ground                            |

| 89                        | AVDD    | G   | Analog supply voltage (3.3V)                                                         |

|                           |         |     |                                                                                      |

| 90                        | IREFR1  | 0   | Connect 12kΩ(1%) Register between Analog ground                                      |

| 91                        | IREFR2  | 0   | Connect 4.7kΩ(1%) Register between Analog ground                                     |

| 92                        | AVSS    | G   | Ground pin for Analog                                                                |

| 93                        | AVSS    | G   | Ground pin for Analog                                                                |

| 94                        | AVDD    | Р   | Analog supply voltage (3.3V)                                                         |

| 95                        | CLPCAP1 | 0   | Capacitor for clamp.                                                                 |

| 95                        | CLPCAPT | 0   | Connect 0.1uF ceramic capacitor between AVSS                                         |

|                           |         |     | Analog Video Signal Input pin.                                                       |

| 96                        | AIN1    |     | Input –6dB analog video signal via 0.1uF capacitor.                                  |

| 97                        | AVSS    | G   | Ground pin for Analog                                                                |

| 51                        | 7300    | - 0 | Analog Video Signal Input pin.                                                       |

| 98                        | AIN2    |     |                                                                                      |

|                           | AV(CC   | ~   | Input –6dB analog video signal via 0.1uF capacitor.                                  |

| 99                        | AVSS    | G   | Ground pin for Analog                                                                |

| 100                       | AIN3    | 1   | Analog Video Signal Input pin.                                                       |

| 100                       | 7.1110  |     | Input –6dB analog video signal via 0.1uF capacitor                                   |

|                           |         |     |                                                                                      |

|                           | AVDD    | Р   | Analog supply voltage (3.3V)                                                         |

|                           | AVSS    | G   | Ground pin for Analog                                                                |

|                           | DVDD    | P   | Digital supply voltage (3.3V)                                                        |

|                           | DVSS    | G   | Ground pin for Digital                                                               |

| ± D                       |         |     | or on read? in the bight the device, as applying veltage to the AK9951 connet oncure |

\* Recommendation: Perform a "power on reset" prior to using the device, as applying voltage to the AK8851 cannot ensure proper device initialization. Only a reset sequence can ensure this.

#### ASAHI KASEI 4.Electrical Specifications www.DataSheet4U.com

(1) Absolute Maximum Ratings

| Parameter                           | Min. | Max.      | Units |

|-------------------------------------|------|-----------|-------|

| Supply Voltage* (VDD)<br>DVDD, AVDD | -0.3 | 4.5       | V     |

| Input Pin Voltage (Vin)             | -0.3 | VDD + 0.3 | V     |

| Input Pin Current (lin)             | -10  | 10        | mA    |

| Storage Temperature                 | -40  | 125       | °C    |

Note) power supply voltages are referenced to each ground pin (DVSS, AVSS) which is equal to 0 V (voltage reference).

(2) Recommended Operating Conditions

| Parame           | ter   | Min. | Тур. | Max | Units |

|------------------|-------|------|------|-----|-------|

| Supply Voltage * | AVDD  | 3.0  | 3.3  | 3.6 | V     |

|                  | DVDD  | 3.0  | 3.3  | 3.6 | V     |

| Operating Temper | ature | -20  |      | 85  | °C    |

Note) power supply voltages are referenced to each ground pin (DVSS, AVSS) which is equal to 0 V (voltage reference).

#### (3) DC Characteristics (DVDD=3.0 ~ 3.6 V at -20 ~+85 degree C)

| Parameter                                                          | Symbol | Min     | Тур. | Max.    | Units | Condition    |

|--------------------------------------------------------------------|--------|---------|------|---------|-------|--------------|

| Digital Input High Voltage                                         | VIH    | 0.7DVDD |      |         | V     |              |

| Digital Input Low Voltage                                          | VIL    |         |      | 0.3DVDD | V     |              |

| Digital Input Leak Current                                         | IIL    |         |      | +/- 10  | uA    |              |

| Digital Output High Voltage                                        | VOH    | 2.4     |      |         | V     | IOH = -400uA |

| Digital Output High Voltage                                        | VOL    |         |      | 0.4     | V     | IOL = 1.2mA  |

| I <sup>2</sup> C Input High Voltage<br>I <sup>2</sup> C (SDA, SCL) | VIHC   | 0.7VDD  |      |         | V     |              |

| I <sup>2</sup> C Input Low Voltage<br>I <sup>2</sup> C (SDA, SCL)  | VILC   |         |      | 0.3VDD  | V     |              |

| I <sup>2</sup> C (SDA) Output Low Voltage                          | VOLC   |         |      | 0.4     | V     | IOLC = 3mA   |

Note) The following are Digital Output pins:,

CLK27MO/D[7:0]/NSIG/DVALID/FIELD/CSYNC/HSYNC/VSYNC/HALFCKO/EXTDAT[7:0].

Digital output pins, excluding CLK27MO, are shown as Digital Data pins.

SDA pin is separated from Digital output pins and its characteristics are described in other terms.

(4) AC Characteristics

| Parameter                           | Symbol | Min. | Тур. | Max. | Units | Condition |

|-------------------------------------|--------|------|------|------|-------|-----------|

| Digital Maximum Load<br>Capacitance | CL     | 15   |      | 40   | pF    |           |

(5) Analog Characteristics and Power Dissipation (AVDD =3.3 V at room temperature) www.DataSheet4U.com

#### Selector Clamp

| Parameter                                   | Symbol | Min. | Тур.   | Max. | Units           | Condition    |

|---------------------------------------------|--------|------|--------|------|-----------------|--------------|

| Maximum Input Range                         | VIMX   |      |        | 1.20 | V <sub>PP</sub> | PGA Gain 0dB |

| Clamp Level<br>(Composite / Y Video Signal) | VYCP   |      | 0.65   |      | V               |              |

| C Signal Clamp Level                        | VCCP   |      | 1.29   |      | V               |              |

| Clamp Current                               | CLPI   |      | +/-150 |      | uA              |              |

| Isolation between Each Channels             |        |      | -60    |      | dB              | 5.5MHz       |

#### PGA

| Parameter    | Symbol | Min. | Тур.  | Max. | Units | Conditions                         |

|--------------|--------|------|-------|------|-------|------------------------------------|

| Resolutions  |        |      | 7     |      | bit   |                                    |

| Gain offset  | GOF    |      | 0.65  |      | dB    | Gain 0dB<br>(Reg0x0A, 0x0B = 0x00) |

| Minimum Gain | GMN    |      | 0     |      | dB    |                                    |

| Maximum Gain | GMX    |      | 12    |      | dB    |                                    |

| Gain Step    | GST    |      | 0.094 |      | dB    |                                    |

#### AD Converter

| Parameters                  | Symbol | Min. | Тур.   | Max.   | Units | Conditions                          |

|-----------------------------|--------|------|--------|--------|-------|-------------------------------------|

| Resolutions                 | RES    |      | 10     |        | bits  |                                     |

| Operation Clock             | FS     |      | 27     |        | MHz   |                                     |

| ADC Range                   | AIN    |      | 1.6    |        | Vpp   | (VRP-VRN) x 2                       |

| INL                         | INL    |      | +/-2.5 | +/-5.0 | LSB   | fs=27MHz (*1)                       |

| DNL                         | DNL    |      | +/-0.8 | +/-2.0 | LSB   | fs=27MHz (*1)                       |

| S/N                         | SN     |      | 54     |        | dB    | fin=1MHz Ain= -1dB<br>fs=27MHz (*2) |

| S/(N+D)                     | SND    |      | 51     |        | dB    | fin=1MHz Ain= -1dB<br>fs=27MHz (*2) |

| ADC Internal Common Voltage | VCOM   |      | 1.2    |        | V     |                                     |

| ADC Internal VREF+          | VRP    |      | 1.6    |        | V     |                                     |

| ADC Internal VREF-          | VRN    |      | 0.8    |        | V     |                                     |

(\*1) Full scale input range: VI=1.2Vpp, When PGA Gain Control Register 0x0A/0x0B is set to 0x0E. (\*2) VI=1.2Vpp PGA Gain Control Register 0x0A/0x0B = 0x06

#### Power Dissipation

| Power Dissipation<br>Parameter | Symbol | Min. | Тур.  | Max. | Units | Conditions                       |

|--------------------------------|--------|------|-------|------|-------|----------------------------------|

| Active Mode                    |        |      |       |      |       |                                  |

| Digital + Analog               |        |      | 142   | 185  | mA    | 2ch operation (YCmode)           |

| Analog                         |        |      | (129) |      | mA    | (1ch operation (CVBS))           |

|                                |        |      | 44    |      | mA    | 2ch operation (YC mode)          |

|                                |        |      | (30)  |      |       | (1ch operation (CVBS))           |

| Digital                        |        |      | 98    |      |       | 25pF Load                        |

|                                |        |      |       |      |       | 100% Color Bar Input             |

| Power Down Current             |        |      |       |      |       | Mode 1: AFE Control Register     |

| Mode 1                         |        |      |       |      |       | INSEL[2:0]=111                   |

| Digital + Analog               |        |      | 81    | 105  | mA    | Analog ADC Path Power Down       |

| Analog                         |        |      | 16    |      | mA    | (PLL block is not powered down.) |

| Digital                        |        |      | 85    |      | mA    |                                  |

| Mode 2                         |        |      |       |      |       | Mode 2: PD pin Low               |

|                                |        |      |       |      |       | When PD pin changes Low to       |

| Digital + Analog               |        |      | 10    | 200  | uA    | High, the AK8851 requires a      |

| Analog                         |        |      | 1     |      | uA    | Reset sequence.                  |

| Digital                        |        |      | 9     |      | uA    |                                  |

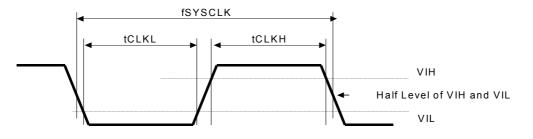

| Parameter           | Symbol  | Min. | Тур.   | Max.   | Units |

|---------------------|---------|------|--------|--------|-------|

| CLK                 | fSYSCLK |      | 24.576 |        | MHz   |

| CLK Pulse width H   | tCLKH   | 16   |        |        | nsec  |

| CLK Pulse width L   | tCLKL   | 16   |        |        | nsec  |

| Frequency stability |         |      |        | +/-100 | ppm   |

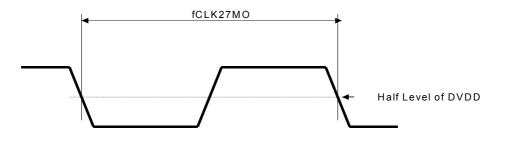

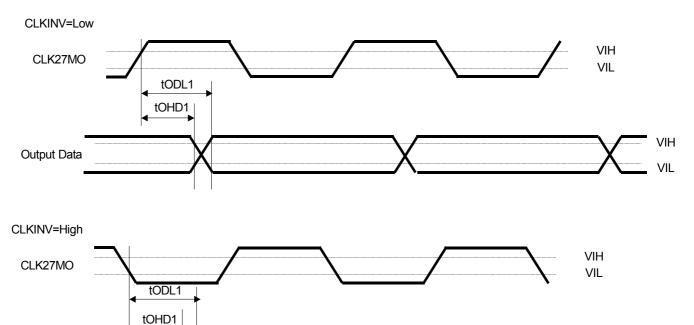

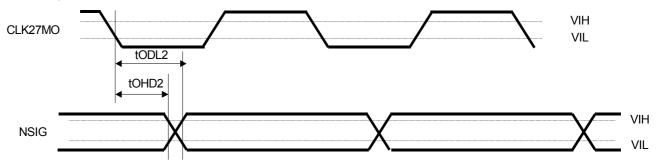

(2)CLK27MO output

| Parameter | Symbol   | Min. | Тур. | Max. | Units |

|-----------|----------|------|------|------|-------|

| CLK27MO   | fCLK27MO |      | 27   |      | MHz   |

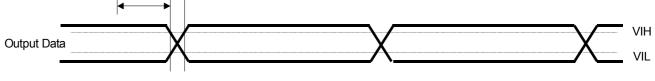

(3-1) Output Data Timing (except for D[7:0] and EXTDAT[7:0] in 16-Bit output mode and NSIG output)

| Parameter              | Symbol | Min. | Тур. | Max. | Units | Remark                  |

|------------------------|--------|------|------|------|-------|-------------------------|

| Output Data Delay Time | tODL1  |      |      | 25   | 2000  | CL <sub>Clk</sub> 25pF  |

| Output Data Hold Time  | tOHD1  | 3    |      |      | nsec  | CL <sub>Data</sub> 25pF |

#### CLKINV=High

| Parameter              | Symbol | Min. | Тур. | Max. | Units  | Remark                  |

|------------------------|--------|------|------|------|--------|-------------------------|

| Output Data Delay Time | tODL2  |      |      | 35   | - nsec | CL <sub>Clk</sub> 25pF  |

| Output Data Hold Time  | tOHD2  | 3    |      |      |        | CL <sub>Data</sub> 25pF |

ASAHI KASEI (3-2) 16-Bit Output Data Timing ([D7:D0] and [EXTDAT7:EXTDAT0]) www.DataSheet4U.com

VIH HALFCKO VIL tOSU3 tOHD3 [D7:0] VIH Cb/Cr Υ EXTDAT7:0] - -VIL

| Parameter              | Symbol | Min. | Тур. | Max. | Units | Remark                  |

|------------------------|--------|------|------|------|-------|-------------------------|

| Output Data Setup Time | tOSU3  | 10   |      |      | nsec  | CL <sub>Clk</sub> 25pF  |

| Output Data Hold Time  | tOHD3  | 20   |      |      | nsec  | CL <sub>Data</sub> 25pF |

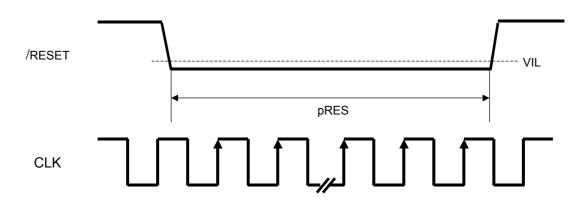

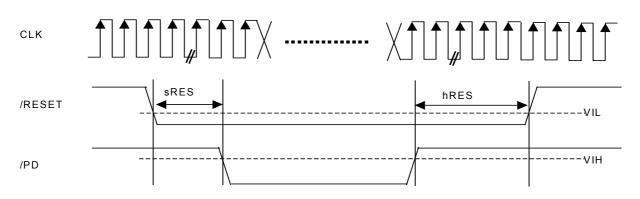

(4) Reset Timing

| Parameter          | Symbol | Min. | Тур. | Max. | Units | Remark            |

|--------------------|--------|------|------|------|-------|-------------------|

| /RESET Pulse width | pRES   | 10   |      |      | CLK   | Clock Rising Edge |

Note) a 24.576 MHz clock is required for reset operation. After application of clock, the /RESET pin should be pulled low. This power-on RESET is recommended whenever power is applied or removed from the AK8851, until as applying voltage to the AK8851 cannot ensure proper device initialization. Only a reset sequence can ensure this.

Output pins except for CLK27MO pin become low during the reset sequence.

.

[AK8851]

#### www.Da(5);/RDtpincelease reset

Before setting /PD pin to Low, at least 100 clock cycles must be applied to the device..

After releasing /PD pin to high, the /RESET pin must be kept low until the analog reference voltage and current are stabilized.

| Parameter               | Symbol | Min. | Тур. | Max. | Units | Remark            |

|-------------------------|--------|------|------|------|-------|-------------------|

| Set /PD RESET width     | sRES   | 100  |      |      | CLK   | Clock Rising Edge |

| Release /PD Reset width | hRES   | 10   |      |      | msec  |                   |

Note) a 24.576 MHz clock is required for reset operation.

After application of clock, the /RESET pin should be pulled low. This power-on RESET is recommended whenever power is applied or removed from the AK8851, as applying voltage to the AK8851 cannot ensure proper device initialization. Only a reset sequence can ensure this.

until.

Output pins except for CLK27MO pin become low during the reset sequence.

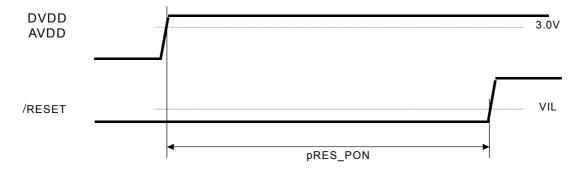

#### (6) Power-On-Reset

At power-on, /RESET pin must be kept low until the analog reference voltage and current are stabilized.

| Parameter          | Symbol   | Min. | Тур. | Max. | Units | Remark |

|--------------------|----------|------|------|------|-------|--------|

| /RESET pulse width | pRES_PON | 10   |      |      | msec  |        |

Note) For reset operation, a 24.576 MHz clock is required.

System control pins ( SELA,CLKINV,/PD ) must be kept valid until the 10-clock time after the rising edge of reset pulse.

Output pins except for CLK27MO pin become low during the reset sequence.

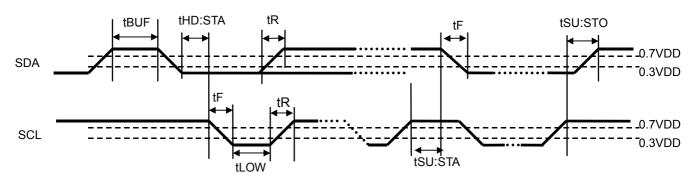

ASAHI KASEI (7) I2C bus Input and Output Timing www.DataSheet4U.com

(7-1) Timing 1

| Item                        | Symbol  | Min | Max | Unit |

|-----------------------------|---------|-----|-----|------|

| Bus Free Time               | tBUF    | 1.3 |     | usec |

| Hold Time (Start Condition) | tHD:STA | 0.6 |     | usec |

| Clock Pulse Low Time        | tLOW    | 1.3 |     | usec |

| Input Signal Rise Time      | tR      |     | 300 | nsec |

| Input Signal Fall Time      | tF      |     | 300 | nsec |

| Setup Time(Start Condition) | tSU:STA | 0.6 |     | usec |

| Setup Time(Stop Condition)  | tSU:STO | 0.6 |     | usec |

All the figures shown above are restricted by the  ${\rm I}^2C$  Bus standard. Please see the official  ${\rm I}^2C$  Bus standard for further details.

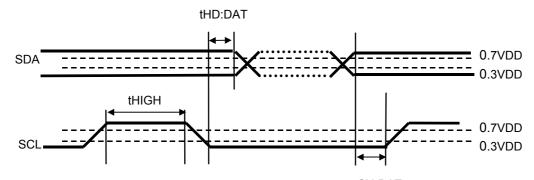

(7-2) Timing 2

| tSI | J: | D٨ | 1 | Г |

|-----|----|----|---|---|

|     |    |    |   |   |

| Item                  | Symbol  | Min     | Max     | Unit |

|-----------------------|---------|---------|---------|------|

| Data Setup Time       | tSU:DAT | 100 (1) |         | nsec |

| Data Hold Time        | tHD:DAT | 0.0     | 0.9 (2) | usec |

| Clock Pulse High Time | tHIGH   | 0.6     |         | usec |

(1) In case of normal I<sup>2</sup>C Bus mode tSU:DAT≥250nsec

(2) Using under minimum tLOW, this value must be satisfied

## 6. Functional Summary www.DataSheet4U (1) Clock

[AK8851]

The AK8851 operates in one of 3 clock modes.

1. Line Locked Clock mode:

An operating mode where the device uses a clock that is synchronized with the Horizontal Sync signal for each line.

2.Frame Locked Clock mode:

The device operates by a clock that is synchronized with the Vertical Sync signal for each Frame.

3.Fixed Clock mode:

An operating mode where the device operates by an asynchronous clock.

These clock modes are set by the [Control 1 register].

Since both Line Locked and Frame Locked modes use an input-signal synchronized clock, ITU-R BT.656\* compatible output is available (however ,depending upon the input signal quality, ITU-R BT.656 may not be satisfied ).

(2) Analog Interface

The AK8851 accepts Composite and discrete Y/C signals (S-video) as input. 6 channels are assigned for these input pins. Channel selection is set via register.

The following input signal combinations are possible.

- (a) select a single channel from composite video signal x 4

- (b) select a single channel from composite signal x 2 + S-video signal input x2

- (3) Input Signals

The device accepts NTSC-M,NTSC-4.43,PAL-B,D,G,H,I,N,NcM,60,SECAM composite video signals and S Video signals.

It is also possible to accept an input signal with set-up features by setting the set-up register bit. In this case, the set-up is set at the 7.5% point. The automatic input signal detect function is also enabled via register settings. Required input signal quality is as follows.

#### (3-1) input signal quality

| Item              | Input Range | Unit | Conditions                                               |

|-------------------|-------------|------|----------------------------------------------------------|

| Video Input Level | +/- 6       | dB   | Video signal should be input with -6dB level             |

| Color Burst Level | +/-10       | dB   | (divided be the resistor), and through 0.1uF capacitor.) |

#### (3-2) Non-Standard input signal treatment

| Item                   | Process                                                                                  |

|------------------------|------------------------------------------------------------------------------------------|

| Lack of HSYNC          | Running with self timing                                                                 |

| Lack of VSYNC          | Running with self timing                                                                 |

| B/W Video Signal input | Set register to B/W mode .<br>Auto transition to B/W mode in auto signal detection mode. |

| Macrovision            | Information with Macrovision control register.<br>Certified Macrovision device .         |

### (4) Analog Input Signal Processing

Input Selector ( inter-channel isolation ): better than -60 dB

PGA : 0 ~ 12 dB ( approx. 0.1 dB/step)

AD converter : operates at 27 MHz

For normal operation, the Frame-locked PLL generates by the Line-locked PLL or a required internal clock.

### (5) Clamp processing

Analog Sync-Tip clamping is done and the Digital signal-processing block processes the Digital Pedestal clamping.

### (6) AGC function

The AGC adjusts the input signal level based on the amplitude difference between the Sync-Tip level and the Pedestal level of the input signal.

(7) ACC function

The ACC adjusts the input color signal level based on the color burst level of the input signal. ACC does not function for SECAM signals.

## [AK8851]

# ASAHI KASEI

(8) Y/C Separation Function www.DataSheet4U.com

#### For NTSC,NTSC-4.43 signal inputs :

Adaptive Y/C separation is used. It is also possible to lock this function to either 3-line 2 dimensional Y/C separation, or primary dimensional (BPF) Y/C separation.

#### For PAL-B,D,G,H,I,M,N,Nc,NTSC-4.43,PAL 60 signal inputs :

Adaptive Y/C separation is used. It is also possible to lock this function to either 5-line 2 dimensional Y/C separation, or primary dimensional (BPF) Y/C separation.

#### For SECAM signal input :

Only the primary dimensional (BPF) Y/C separation is effective (even if the adaptive type is set, primary Y/C separation is performed).

#### (9) input signal synchronization

The AK8851 automatically synchronize the incoming input signal when the input signal is switched or when the number of lines in a Frame changes (VLOCK function).

(10) Output Signal Bandwidth

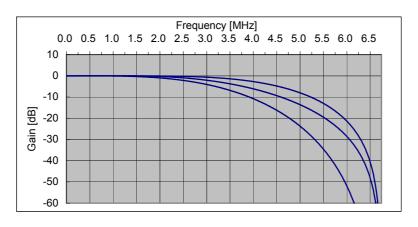

$\label{eq:Luminance Signal Bandwidth: DC \sim 5.5 \mbox{ MHz} - 0.5 \mbox{ dB ( DC } \sim 5\mbox{ MHz} +/- 0.1 \mbox{ dB ripple )} \\ The luminance bandwidth is selectable among 3 ranges via a register setting. \\ Chroma Signal Bandwidth : 750 \mbox{ KHz} \sim 1.5 \mbox{ MHz} (-3 \mbox{ dB }) ( 2 \mbox{ ranges selectable }) \\ \end{tabular}$

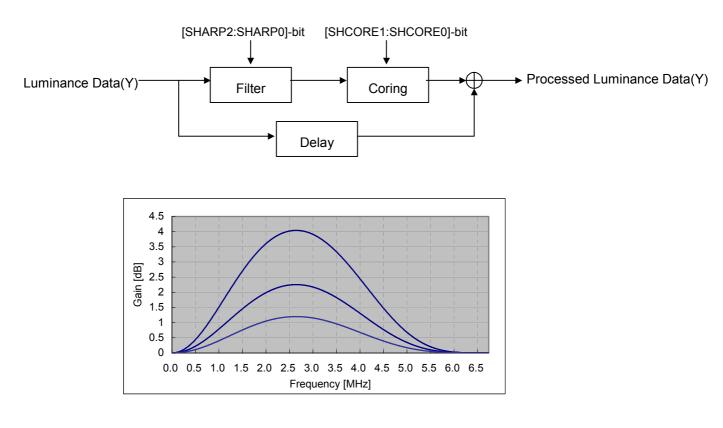

### (11) Video Image Quality Control Function

Contrast, Brightness, HUE, Saturation levels and Sharpness level are adjustable. \* HUE and Color Saturation levels are not adjustable when using SECAM signals.

#### (12) Output Interface

- ITU-R BT.601 compatible signal output levels ( with Limit On/Off function)

- Decoded data output is ITU-R BT.656 format (depending on the input signal quality).

- Enables to detect only those signals which are valid during Active Video period (720 pixels), by HSYNC/VSYNC (FIELD)/ DVALID signals.

- 8-Bit output form at 27 MHz rate or 16-Bit output form at 13.5 MHz rate (selectable by register ).

- (13) Other Functions

- Black level signal is output in self-operating mode when no signal is applied (Y = 16Cb,Cr = 128). It is also possible to output Blue level (register selectable).

- Dedicated output pin for no-signal-input detection

- I2C Bus Host Interface ( 400 KHz )

- Power Down mode

- Decoding Function for Closed Caption, VBID (CGMS-A) and WSS signals.

- CRCC that is added to CGMS-A is decoded by the AK8851.

(note) In this data sheet, Sync level and Burst level of the NTSC signals are also converted and expressed in [mV], not in [IRE].

#### [AK8851]

#### ASAHI KASEI

#### 7. Input Signal Selector

www.Data The AK8851 has 4 analog signal input pins. Signal selection is done by [AFE Control Register](R/W)[Sub Address 0x00] and the type of Video signals to be decoded is set by [Input Video Standard Register](R/W)[Sub Address 0x01]. Video signals to be decoded by the AK8851 are NTSC, NTSC-4.43, PAL B, D, G, H, I, M, N, 60 and SECAM. It is also possible to automatically distinguish input signal types by setting the AUTODET-bit of [Input Video Standard Register<sub>1</sub>.

However Automatic detections of Black and White signals and those with / without the SETUP features are not possible.

Input signals are converted into Digital codes as follows:

Composite Video signal: After it conversion to digital data through the functional blocks shown in Fig.2 Analog Block description,

| CLAMP1 BLOCH |  | PGA1 | BLOCK |  | ADC1 | BLOCK, |

|--------------|--|------|-------|--|------|--------|

|--------------|--|------|-------|--|------|--------|

It is then processed in the Digital Block.

Discrete Y/C Video signal input (S-Video signal input):

The input Luminance Signal (Y) is converted into digital data through the functional blocks shown in Fig.2 Analog Block description,

| CLAMP1 BLOCK |  | PGA1 | BLOCK |  | ADC1 | BLOCK |

|--------------|--|------|-------|--|------|-------|

|--------------|--|------|-------|--|------|-------|

and the Input Chroma Signal (C) is converted in digital data through CLAMP2 BLOCK --- PGA2 BLOCK --- ADC2 BLOCK

then each digital data is processed in the Digital block.

The following describes the Register Setting of [AFE Control Register](R/W)[Sub Address 0x00] and [Input Video Standard Register](R/W)[Sub Address 0x01].

#### [AFE Control Register](R/W)[Sub Address 0x00]:

this register sets the input signal. Its Bit Allocation is shown below:

#### Sub Address 0v00

| Sub Address 0x00         Default Value : 0x00 |           |          |          |        |        |        |        |  |

|-----------------------------------------------|-----------|----------|----------|--------|--------|--------|--------|--|

| bit 7                                         | bit 6     | bit 5    | bit 4    | bit 3  | bit 2  | bit 1  | bit 0  |  |

| CLPWIDTH1                                     | CLPWIDTH0 | CLPSTAT1 | CLPSTAT0 | EXTCLP | INSEL2 | INSEL1 | INSEL0 |  |

| Default Value                                 |           |          |          |        |        |        |        |  |

| 0                                             | 0         | 0        | 0        | 0      | 0      | 0      | 0      |  |

[INSEL2 : INSEL0]-bit:

to set the input port of input signal.

The setting is done as follows. This input port setting also controls the Analog Block's Power Saving mode.

| [INSEL2:INSEL0] | Select Input port | Input Video | Power Save                          |

|-----------------|-------------------|-------------|-------------------------------------|

| [000]           | AIN1              | CVBS        |                                     |

| [001]           | AIN2              | CVBS        | ADC2 set to Power save mode.        |

| [010]           | AIN3              | CVBS        | ADCZ Set to Fower save mode.        |

| [011]           | AIN4              | CVBS        |                                     |

| [101]           | AIN2/AIN5         | AIN2: Y     |                                     |

| [101]           |                   | AIN5: C     |                                     |

| [110]           | AIN3/AIN6         | AIN3: Y     |                                     |

| [110]           |                   | AIN6: C     |                                     |

| [100] [111]     | No signal in      |             | ADC1 and ADC2 are set to Power save |

| [100][111]      | No Signa III      |             | mode.                               |

Note: when [INSEL2:INSEL0]-bit is set to [1,0,0] or [1,1,1], ADC1 and ADC2 in Power Saving mode, including the CLAMP and PGA blocks (timing signal outputs are driven by the self-running clock as the digital blocks are in normal operating mode).

#### [Input Video Standard Register](R/W)[Sub Address 0x01]: www.D

This register sets the input signal attributes. its Bit Allocation is as follows.

#### Sub Addross 0v01

| Sub Address 0x | Sub Address 0x01 Default Value : 0x00 |       |       |       |       |       |       |  |  |

|----------------|---------------------------------------|-------|-------|-------|-------|-------|-------|--|--|

| bit 7          | bit 6                                 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |  |  |

| AUTODET        | SETUP                                 | B/W   | VLF   | VCEN1 | VCEN0 | VSCF1 | VSCF0 |  |  |

|                | Default Value                         |       |       |       |       |       |       |  |  |

| 0              | 0                                     | 0     | 0     | 0     | 0     | 0     | 0     |  |  |

#### \* [VSCF1:VSCF0]-bit:

Input signal Sub-carrier frequency is set using the IVSCF1:VSCF01-bit.

| [VSCF1:VSCF0] | Sub-Carrier Freq.[MHz] | Note          |  |

|---------------|------------------------|---------------|--|

| [00]          | 3.57954545             | NTSC          |  |

| [01]          | 3.57561188             | PAL-M         |  |

| [10]          | 3.582054               | PAL-N(Arg.)   |  |

| [11]          | 4.43361875             | PAL-B,D,G,H,I |  |

#### \* [VCEN1:VCEN0]-bit:

Input signal Color encoding is set using the [VCEN1:VCEN0]-bit.

| [VCEN1:VCEN0]-bit | Color Encode Type | Note |

|-------------------|-------------------|------|

| 00                | NTSC              |      |

| 01                | PAL               |      |

| 10                | SECAM             |      |

| 11                | Reserved          |      |

#### \*[VLF]-bit:

Number of input signal Lines per Frame is set using the [VLF]-bit.

| [VLF]-bit | Number of Lines | Note |

|-----------|-----------------|------|

| 0         | 525 lines       |      |

| 1         | 625 lines       |      |

\*[B/W]-bit:

When the input signal is Black and White, set the [B/W]-bit.

| [B/W]-bit | Type of Signal         | Note |

|-----------|------------------------|------|

| 0         | Color Signal           |      |

| 1         | Black and White Signal |      |

### (footnote)

When this bit is set, the input signal is processed as a Black and White signal and the digitized sampling data through the ADC is processed as Luminance through Luminance process. Namely, when this bit is ON, all input signals fed to the Y/C separation block are treated as Luminance, and the data is output to the Luminance signal-processing block from Y/C Separation block.

#### \*[SETUP]-bit:

Lack or presence of input signal SETUP features is set by [SETUP]-bit.

| [SET | UP]-bit | SETUP             | Note       |

|------|---------|-------------------|------------|

|      | 0       | w/o Setup Signal  |            |

|      | 1       | with Setup Signal | 7.5% SETUP |

#### (footnote)

when [SETUP]-bit is set to "1",Luminance and Chroma signals are processed as follows.

Luminance signal: Y=Y(1-0.075)/0.925

: U=U/0.925 Chroma signal

V=V/0.925

[AK8851]

[AUTODET]-bit:

www.DaseTifie AUTODET]-bit in order to automatically distinguish input signals.

|   | [AUTODET]-bit | On/Off | Note                            |

|---|---------------|--------|---------------------------------|

|   | 0             | OFF    |                                 |

| Ĩ | 1             | ON     | Cannot detect with or w/o Setup |

(footnote)

following input signal characteristics are automatically detected.

Number of Lines per each Frame:525/625 Sub-Carrier frequency : 3.58/4.43 MHZ

Color Encoding systems: NTSC/PAL/SECAM

With the automatic distinguishing capability described above, the input signal is verified to be one of the following:

NTSC/NTSC-4.43/PAL-B, D, G, H, I/PAL-M/PAL-N (ARG)/PAL-60/SECAM.

The verification result is stored in [Input Video Status Register][sub Address 0x00].

Automatic verification of the SETUP feature is not performed. The following set-up process is performed while the automatic verification function is enabled.

| Recognized Signal             | Setup Recognition (Default)<br>[Control 2 Register]<br>[STUPATOFF-bit ] = 0 | Validation of SETUP-bit                                   |  |  |

|-------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------|--|--|

| NTSC<br>PAL-B,D,G,H,I,N,Nc,60 | No setup process                                                            | Setup Procedure is done with SETUP-bit is 1               |  |  |

| SECAM                         |                                                                             |                                                           |  |  |

| PAL-M                         | Satur process                                                               | Satur hit is disable. The eatur presedure is always done  |  |  |

| NTSC-4.43                     | Setup process                                                               | Setup-bit is disable. The setup procedure is always done. |  |  |

Please set the [Input Video Standard Register][Sub Address 0x01] [SETUP]-bit when an input signal with values other than those shown above is input (SETUP process is performed regardless of SETUP-bit status for PAL-M and NTSC-4.43 signal). The automatic set-up process can be turned off by [STUPATOFF-bit] of the Control2 Register. In this case, use the SETUP-bit to enable/disable the set-up process.

Please refer to [SETUP]-bit description for details.

Automatic input signal detect registers are listed below:

#### \*[Input Video Status Register]:

Sub Address 0x19

| bit 7 | bit 6 | bit 5  | bit 4  | bit 3    | bit 2    | bit 1    | bit 0    |

|-------|-------|--------|--------|----------|----------|----------|----------|

| FIXED | UNDEF | ST_B/W | ST_VLF | ST_VCEN1 | ST_VCEN0 | ST_VSCF1 | ST_VSCF0 |

#### \*[ST-VSCF1:ST-VSCF0]-bit:

Input signal Sub-carrier verification result is indicated by [ST-VSCF1: ST-VSCF0]-bit.

| [ST_VSCF1:ST_VSCF0] | Sub-Carrier Freq.[MHz] | Note |

|---------------------|------------------------|------|

| [00]                | 3.57954545             |      |

| [01]                | 3.57561188             |      |

| [10]                | 3.582054               |      |

| [11]                | 4.43361875             |      |

#### \*[ST-VCEN1:ST-VCEN0]-bit:

Color Encoding System Verification is indicated by [VCEN1:VCEN0]-bit.

| [ST_VCEN1:ST_VCEN0]-bit | Type of Color Encode | Note |

|-------------------------|----------------------|------|

| 00                      | NTSC                 |      |

| 01                      | PAL                  |      |

| 10                      | SECAM                |      |

| 11                      | Reserved             |      |

#### \*[ST-VLF]-bit:

Number of Lines per each Frame is indicated by [VLF]-bit.

| [ST_VLF]-bit | Number of Lines | Note |

|--------------|-----------------|------|

| 0            | 525lines        |      |

| 1            | 625lines        |      |

\*[**ST-B/W]-bit:** www.Dawhen the input signal is Black and White,[ST-B/W]-bit indicates the status.

| [ST_B/W]-bit | Type of Signal         | Note |

|--------------|------------------------|------|

| 0            | Color Signal           |      |

| 1            | Black and White Signal |      |

Since Black and White signal decisions are made by the color killer level, the color killer bit must be turned "ON".

When a user intentionally enables the B/W-bit, the automatic input signal detect function only checks if the Line number is 525 or 625. In this case, please refer to [ST-VLF]-bit information only.

#### \*[UNDEF]-bit:

if the input signal type is not identified, this bit becomes "1".

| [UNDEF]-bit | Status               | Note |

|-------------|----------------------|------|

| 0           | During recognition   |      |

| 1           | Cannot be recognized |      |

#### \*[FIXED]-bit:

when the input signal type is identified, this bit becomes "1".

| [FIXED]-bit | Status             | Note |

|-------------|--------------------|------|

| 0           | During recognition |      |

| 1           | Recognized         |      |

8.PGA ( Programmable Gain Amp.) www.DataSpectal J com The Ak8851 has 2 PGAs (Programmable Gain Amps), PGA1 and PGA2 on the input stage. The gain range of each PGA is from 0dB to 12dB with a gain step of approx. 0.1 dB/step. Input signals to the AK8851 are attenuated to 50 % level by an external resistor-divider.

PGA1 adjusts the gains of Composite and Y signals for discrete Y/C signals, and PGA2 handles the C signal gain of the discrete Y/C signal (refer to Fig.2).

PGA1 set is done by [PGA1 Control Register](R/W)[Sub Address 0x0A]. PGA2 set is done by [PGA2 Control Register](R/W)[Sub Address 0x0B].

When the AGC function is enabled by [AGC and ACC Control Register], the PGA registers are disabled. When the AGC function is disabled, the gains of PGA1 and PGA2 can be adjusted independently. Bit Allocation of [PGA1/PGA2 Control Register] is shown below.

# \*[PGA1 Control Register]

| Sub Address 0 | X0A    |        |        |        |        | Defaul | t Value : 0x46 |

|---------------|--------|--------|--------|--------|--------|--------|----------------|

| bit 7         | bit 6  | bit 5  | bit 4  | bit 3  | bit 2  | bit 1  | bit 0          |

| Reserved      | PGA1_6 | PGA1_5 | PGA1_4 | PGA1_3 | PGA1_2 | PGA1_1 | PGA1_0         |

| Default Value |        |        |        |        |        |        |                |

| 0             | 1      | 0      | 0      | 0      | 0      | 0      | 0              |

### \*[PGA2 Control Register]

| Sub Address 0 | Sub Address 0x0B Default Value : 0x46 |        |        |        |        |        |        |

|---------------|---------------------------------------|--------|--------|--------|--------|--------|--------|

| bit 7         | bit 6                                 | bit 5  | bit 4  | bit 3  | bit 2  | bit 1  | bit 0  |

| Reserved      | PGA2_6                                | PGA2_5 | PGA2_4 | PGA2_3 | PGA2_2 | PGA2_1 | PGA2_0 |

| Default Value |                                       |        |        |        |        |        |        |

| 0             | 1                                     | 0      | 0      | 0      | 0      | 0      | 0      |

#### 9.AGC

The AK8851 measures the input signal's SYNC signal level (the difference between SYNC-Tip level and Pedestal level) and then judges the input signal level. The AGC function controls PGA gain so that the SYNC signal level equals 286 [mV]/300 [mV].

This function ensures a proper level to the ADC by amplifying the incoming input signal.

For Y/C inputs, the C signal is either amplified or attenuated by the same gain value as the SYNC level of the Y signal adjustment to be 286 [mV]/300 [mV] (a fine tuning of the C signal is done by the Auto Color Control (ACC) function in the digital block).

AGC Adjustable levels expressed in 10-bit code are shown in the following table.

| Input Signal             | Target ADC value(decimal) | Note    |

|--------------------------|---------------------------|---------|

| NTSC-M                   |                           |         |

| NTSC-4.43                | 224                       | 286[mV] |

| PAL-M                    |                           |         |

| PAL-B, D, G, H, I, N, Nc |                           |         |

| SECAM                    | 236                       | 300[mV] |

| PAL-60                   |                           |         |

AGC value can be frozen via a register setting. When it is frozen, the pre-set gain constant is held in the AGC. When AGC function is disabled, PGA1 and PGA2 gains can be independently set.

Set the AGC parameter by programming [AGC and ACC Control Register](R/W)[Sub Address 0x06].

| Sub Address 0 | x06   |       |        |          |       | Defaul | t Value : 0x00 |

|---------------|-------|-------|--------|----------|-------|--------|----------------|

| bit 7         | bit 6 | bit 5 | bit 4  | bit 3    | bit 2 | bit 1  | bit 0          |

| ACCFRZ        | ACC1  | ACC0  | AGCFRZ | Reserved | AGCC  | AGCT1  | AGCT0          |

| Default Value |       |       |        |          |       |        |                |

| 0             | 0     | 0     | 0      | 0        | 0     | 0      | 0              |

. . . .

| [AGCT1:AGCT0]-bit | Time constant of AGC | Note                          |

|-------------------|----------------------|-------------------------------|

| [00]              | Disable              | PGA control Register is valid |

| [01]              | Fast                 |                               |

| [10]              | Middle               |                               |

| [11]              | Slow                 |                               |

#### [AGCC]-bit:

\*[AGCC]-bit sets the non-sensing range ( coring level ) of AGC.

| [AGCC]-bit | non-sensing range of AGC | Note |

|------------|--------------------------|------|

| 0          | +/-2-bit                 |      |

| 1          | +/-3-bit                 |      |

#### [AGCFRZ]-bit:

\* This bit controls the AGC freeze function.

When [AGCFRZ]-bit is stopgap gain values are maintained.

| [AGCFRZ]-bit | Status of AGC           | Note                                  |  |  |

|--------------|-------------------------|---------------------------------------|--|--|

| 0            | AGC function is working | Invalid when AGC function is disable. |  |  |

| 1            | AGC function is frozen  | Current AGC Value is kept             |  |  |

(footnote)

AGC gain set function is set based on the SYNC signal level only.

When the input signal's SYNC signal level is small but still at a valid level, PGA gain set by the AGC function becomes larger than normal.

If the decoded output code exceeds 254, [PKWHITE]-bit in [Status 1 Register](R)[Sub Address 0x16] or [OVCOL]-bit becomes "1", which indicates an overflow of the decoded data. As for the input level overflow, it is described in a later section.

#### 10.CLAMP www.DataSheet4U.c

#### [Analog Clamp circuit]:

The AK8851 uses an analog circuit to clamp the input signal to the Sync-Tip level (Analog Sync-Tip clamp). Clamp timing is set by [AFE Control Register](R/W)[Sub Address 0x00].

The clamp timing pulse is generated for a fixed time specified by [AFE Control Register] at the falling edge of SYNC signal as a starting point that is SYNC-separated within the AK8851. The Pedestal clamp of A to D converted input data is then processed in the digital signal-processing block (Digital Pedestal Clamp). The Digital Pedestal Clamp is described in a later section.

Analog SYNC-Tip clamping is set by [AFE Control Register](R/W)[Sub Address 0x00].

[AFE Control Register] sets the timing of the SYNC-Tip clamp in the AK8851.

This adjusts the start timing of the clamp and its pulse width.

#### Sub Address 0x00

#### Default Value : 0x00

| bit 7         | bit 6     | bit 5    | bit 4    | bit 3  | bit 2  | bit 1  | bit 0  |

|---------------|-----------|----------|----------|--------|--------|--------|--------|

| CLPWIDTH1     | CLPWIDTH0 | CLPSTAT1 | CLPSTAT0 | EXTCLP | INSEL2 | INSEL1 | INSEL0 |

| Default Value |           |          |          |        |        |        |        |

| 0             | 0         | 0        | 0        | 0      | 0      | 0      | 0      |

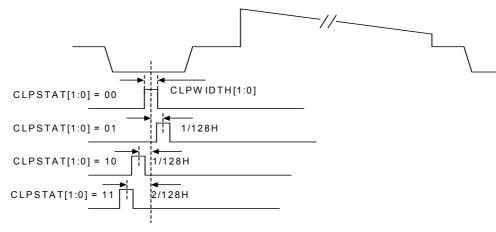

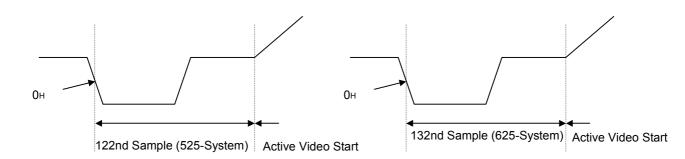

[CLPSTAT1:CLPSTAT0]-bit: timing pulse is generated at the center position of SYNC signal. Its pulse position is adjustable(refer to Fig.5).

| [CLPSTAT1:CLPSTAT0]-bit | Start position of Clamp timing pulse [clock counts] | Note |

|-------------------------|-----------------------------------------------------|------|

| [00]                    | Center of Sync signal                               |      |

| [01]                    | 1/128H(496nsec) Delay from center of Sync signal.   |      |

| [10]                    | 1/128H(496nsec) before from center of Sync signal   |      |

| [11]                    | 2/128H (1usec) before from center of Sync signal    |      |

#### [CLPWIDTH1:CLPWIDTH0]-bit:

This sets the clamp timing pulse width for the input signal. \*Pulse Width is set by [CLPWIDTH1:CLPWIDTH0]-bit (refer to Fig.5)

|  | [CLPWIDTH1:CLPWIDTH0]-bit | Width of clamp timing pulse [clock counts] | Note |  |  |  |

|--|---------------------------|--------------------------------------------|------|--|--|--|

|  | [00]                      | 275nsec                                    |      |  |  |  |

|  | [01]                      | 555nsec                                    |      |  |  |  |

|  | [10]                      | 1.1usec                                    |      |  |  |  |

|  | [11]                      | 2.2usec                                    |      |  |  |  |

Fig.5 Clamp timing pulse

#### [EXTCLP]-bit:

This sets the attributes of the EXTCLP pin. Input/Output selection of EXTCLP pin is done by [EXTCLP]-bit register settings. By switching the pin function, it is possible to output an internally- generated Clamp timing pulse or to clamp the input signal by an externally generated Clamp timing pulse.

| [EXTCLP]-bit | Attribution of EXTCLP                                     | Note    |

|--------------|-----------------------------------------------------------|---------|

| 0            | Output the clamp timing pulse of internal pulse generator | Default |

| 1            | Input external clamp timing pulse.                        |         |

#### 11. CLOCK

www.Dathe AK8851 operates under the following ,3 clock modes.

#### (1) Line-Locked Clock Mode

A clock can be derived from the Horizontal SYNC signal (HSYNC) of an input signal. This input signal can be a high quality source like a Standard Signal Generator or DVD. A clock generated in this way is called Line-Locked Clock. If no input signal is present while in Line-locked mode, the AK8851 will automatically switch to Fixed-Clock mode.

#### (2) Frame-Locked Clock Mode

The input signal's Vertical SYNC can be used to generate a clock when unstable input signals are present, such as those from typical consumer-grade VCR.

A clock generated in this way is called Frame-Locked Clock. If no input signal is present while in Frame-locked mode, the AK8851 will automatically switch to Fixed-Clock mode.

#### (3) Fixed-Clock Mode

This mode is not controlled by the PLL. This mode is enabled only when no signal is fed into the AK8851 or when this mode is selected via a register setting.

#### Clock modes are set by [Control 1 Register](R/W)[Sub Address 0x08].

When the clock auto select mode is enabled, the AK8851 automatically shifts its clock mode from/to the Line-locked mode to/from the Frame-locked mode until it selects an optimum mode It shifts to fixed-clock mode only when no input signal condition is detected.

Since the AK8851 uses a clock that is synchronized with an input signal in both the Line-locked and Frame-locked clock modes, ITU-R.656\* compatible output is available with input signals of appropriate quality.

PLLs in the AK8851 do not operate when the Fixed-clock mode is selected. The device uses this mode when no input signal is detected in auto select mode (register setting) . For ITU-R.BT656-compatible output, the input clock must be synchronized with the input signal.

A detailed description of the clock mode registers [Control 1 Register] is shown below.

#### Sub Address 0x08

Default Value : 0x00 bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0 CLKMODE1 CLKMODE0 INTPOL1 **INTPOL0** 16BITOUT UVFILSEL YCSEP1 YCSEP0 **Default Value** 0 0 0 0 0 0 0 0

#### [CLKMODE1:CLKMODE0] -bit

| [CLKMODE1: CLKMODE0 ]<br>(bit-7: bit-6) | Clock mode       | Explanation of Clock mode                                                                   |

|-----------------------------------------|------------------|---------------------------------------------------------------------------------------------|

| 00                                      | Auto Clock mode  | Optimized clock is selected based on the input video signal. (default)                      |

| 01                                      | Line lock clock  | Line Lock clock mode<br>When no signal is input, clock mode changes to Fixed<br>clock mode. |

| 10                                      | Frame lock clock | Frame Lock clock mode.<br>When no signal is input, clock mode changes to Fixed clock mode.  |

| 11                                      | Fixed clock mode | Fixed clock mode                                                                            |

#### ASAHI KASEI 12. Decimation Filter www.Data

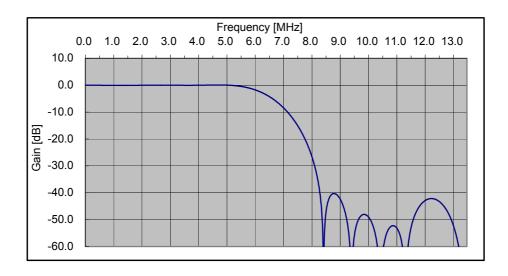

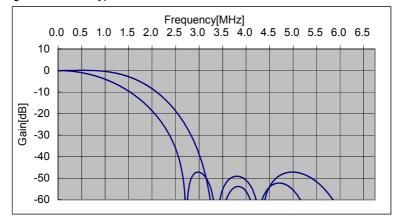

in the AK8851, the input signal is 2x over-sampled at 27 MHz, which is synchronized with the input signal, then it is down-sampled to 13.5 MHz using a decimation filter.

The decimation filter's frequency response plot is shown below.

#### 13.SYNC Separation/SYNC Detection/Phase-Error Detection/Black Level Fine Tuning

SYNC detection and SYNC separation are done on the digitized input signal. The recognized sync-signal is used as a reference the timing for decoding process. The phase error signal is calculated based on the separated SYNC signal which then controls the sampling clock.

In the SYNC separation block, the Luminance signal's Black level can be fine-tuned.

The Fine-tuning band of the Black level is 10-bit wide (before REC 601 conversion) and up to +7 LSB addition or -8 LSB subtraction is possible, in one LSB steps. Output code changes approx. 0.4 LSB per each [1] set.

Black level adjustments are done by [Pedestal Level Control Register](R/W)[Sub Address 0x0C]. Bit allocation of [Pedestal Level Control Register] is shown below.

#### Sub Address 0x0C

| Sub Address 0 | Sub Address 0x0C Default Value : 0x00 |       |       |        |        |        |        |  |  |

|---------------|---------------------------------------|-------|-------|--------|--------|--------|--------|--|--|

| bit 7         | bit 6                                 | bit 5 | bit 4 | bit 3  | bit 2  | bit 1  | bit 0  |  |  |

| DPCC1         | DPCC0                                 | DPCT1 | DCPT0 | BKLVL3 | BKLVL2 | BKLVL1 | BKLVL0 |  |  |

| Default Value |                                       |       |       |        |        |        |        |  |  |

| 0             | 0                                     | 0     | 0     | 0      | 0      | 0      | 0      |  |  |

#### \*[BKLVL3:BKLVL0]-bit:

This register controls fine-tuning of the Black level. Preset register values are added to or subtracted from the Black level. The preset value must be set in 2's complement form. Black level fine-tuning is also valid during the Vertical Blanking period.

| [BKLVL3:BKLVL0]-bit | Proc.                            | Change value in 601 level   |

|---------------------|----------------------------------|-----------------------------|

| 0111                | Add 7 code to black Level        | about 2.8LSB is added.      |

| 0110                | Add 6 code to black Level        | about 2.4LSB is added.      |

| 0101                | Add 5 code to black Level        | about 2.0LSB is added.      |

| 0100                | Add 4 code to black Level        | about 1.6LSB is added.      |

| 0011                | Add 3 code to black Level        | about 1.2LSB is added.      |

| 0010                | Add 2 code to black Level        | about 0.8LSB is added.      |

| 0001                | Add 1 code to black Level        | about 0.4LSB is added.      |

| 0000                | Default                          |                             |

| 1111                | Subtract 1 code from black level | about 0.4LSB is subtracted. |

| 1110                | Subtract 2 code from black level | about 0.8LSB is subtracted. |

| 1101                | Subtract 3 code from black level | about 1.2LSB is subtracted. |

| 1100                | Subtract 4 code from black level | about 1.6LSB is subtracted. |

| 1011                | Subtract 5 code from black level | about 2.0LSB is subtracted. |

| 1010                | Subtract 6 code from black level | about 2.4LSB is subtracted. |

| 1001                | Subtract 7 code from black level | about 2.8LSB is subtracted. |

| 1000                | Subtract 8 code from black level | about 3.2LSB is subtracted. |

# 14. Digital Pedestal Clamp

The input signal's digitally-converted Pedestal position is clamped in the digital signal-processing block. It handles 2 types of input signals (286 mV-type SYNC signal and 300 mV-type SYNC signal) and it outputs the pedestal position as code 16 (8-bit Rec.601 level) for both input cases.

The digital pedestal clamp function sets the time constant (including ON/OFF) and it also sets the coring level. Digital Pedestal Clamp characteristics are set by [DPCT1:DPCT0]-bit and [DPCC1:DPCC0]-bit of [Pedestal Level Control

#### Register](R/W)[Sub Address 0x0C].

Bit allocation of [Pedestal Level Control Register] is as follows.

#### Sub Address 0x0C

| S             | bub Address 0x0C Default Value : 0x00 |       |       |       |        |        |        |        |  |

|---------------|---------------------------------------|-------|-------|-------|--------|--------|--------|--------|--|

|               | bit 7                                 | bit 6 | bit 5 | bit 4 | bit 3  | Bit 2  | bit 1  | bit 0  |  |

|               | DPCC1                                 | DPCC0 | DPCT1 | DCPT0 | BKLVL3 | BKLVL2 | BKLVL1 | BKLVL0 |  |

|               | Default Value                         |       |       |       |        |        |        |        |  |

| 0 0 0 0 0 0 0 |                                       |       |       |       |        |        | 0      |        |  |

#### \*[DPCT1:DPCT0]-bit:

This sets the time constant of the digital pedestal clamp.

| [DPCT1:DPCT0]-bit | Time constant of Digital Pedestal Clamp | Note |

|-------------------|-----------------------------------------|------|

| [00]              | Fast                                    |      |

| [01]              | Middle                                  |      |

| [10]              | Slow                                    |      |

| [11]              | Disable                                 |      |

#### \*[DPCC1:DPCC0]-bit:

This sets the non-sensing bandwidth (coring level) of the digital pedestal clamp.

| [DPCC1:DPCC0]-bit | Non-sensing bandwidth of digital<br>pedestal clamp | Note |

|-------------------|----------------------------------------------------|------|

| [00]              | 1-bit                                              |      |

| [01]              | 2-bit                                              |      |

| [10]              | 3-bit                                              |      |

| [11]              | No non-sensing range                               |      |

#### **15.YC Separation**

The AK8851 employs adaptive, two-dimensional Y/C separation.

In the adaptive YC separation function, a correlator detector selects a best-correlated direction among vertical, horizontal and diagonal samples and an optimized YC separation method is selected.

For NTSC-4.43, PAL 60 and SECAM signal input, a primary dimensional Y/C separation mode is selected, regardless of the bit setting.

YC separation control register is set by [Control 1 Register](R/W)[Sub Address 0x08].

Bit allocation of [Control 1 Register] is as follows.

#### Sub Address 0x08

| Sub Address 0x00 Default value . |          |         |         |          |          |        |        |

|----------------------------------|----------|---------|---------|----------|----------|--------|--------|

| bit 7                            | bit 6    | bit 5   | bit 4   | bit 3    | bit 2    | bit 1  | bit 0  |

| CLKMODE1                         | CLKMODE0 | INTPOL1 | INTPOL0 | 16BITOUT | UVFILSEL | YCSEP1 | YCSEP0 |

| Default Value                    |          |         |         |          |          |        |        |

| 0                                | 0        | 0       | 0       | 0        | 0        | 0      | 0      |

#### \*[YCSEP1:YCSEP0]-bit:

this selects YC separation method.

| [YCSEP1:YC | CSEP0]-bit | YC Separation mode          | Note                                                          |  |  |  |  |  |

|------------|------------|-----------------------------|---------------------------------------------------------------|--|--|--|--|--|

| [00]       | ]          | Adaptive YC Separation mode | 1-D YC separation mode is selected when SECAM signal is input |  |  |  |  |  |

| [01        | ]          | 1-Dim YC Separation mode    |                                                               |  |  |  |  |  |

| [10        | ]          | 2-Dim YC Separation mode    | 1-D YC separation mode is selected when SECAM signal is input |  |  |  |  |  |

| [11        |            | Reserved                    |                                                               |  |  |  |  |  |

Default Value · 0x00

#### 16. Auto Color Control (ACC)

WWW.Data U control value can be input signal's Color Burst level to its appropriate level (NTSC:286 [mV]/ PAL:300 [mV]). The ACC control value can be frozen by register settings. The input color signal level is detected from the Color Burst signal. ACC characteristics are set by [ACC1: ACC0]-bit of [AGC and ACC Control Register](R/W)[Sub Address 0x06]. Bit allocation of [AGC and ACC Control Register] is shown below.

#### Sub Address 0x06

| bit 7         | bit 6 | bit 5 | bit 4  | bit 3 | bit 2 | bit 1 | bit 0 |  |

|---------------|-------|-------|--------|-------|-------|-------|-------|--|

| ACCFRZ        | ACC1  | ACC0  | AGCFRZ | AGCC1 | AGCC0 | AGCT1 | AGCT0 |  |

| Default Value |       |       |        |       |       |       |       |  |

| 0             | 0     | 0     | 0      | 0     | 0     | 0     | 0     |  |

#### [ACC1:ACC0]-bit:

This selects enabling/disabling ACC function and its time constant.

| [ACC1:ACC0]-bit | ACC Time Constant | Note |

|-----------------|-------------------|------|

| [00]            | Disable           |      |

| [01]            | Fast              |      |

| [10]            | Middle            |      |

| [11]            | Slow              |      |

The ACC and Color Saturation functions operate independently (when the ACC is enabled, Color Saturation adjustment is done on the properly adjusted signal by the ACC).

#### \*[ ACCFRZ]-bit:

This is a control bit to freeze the ACC control value.

| [ACCFRZ]-bit | ACC Status                  | Note |

|--------------|-----------------------------|------|

| 0            | ACC function is working     |      |

| 1            | ACC control Value is frozen |      |

#### **17.Color Killer**

The Chroma signal quality is evaluated from the input signal's Color Burst level.

The incoming signal quality's threshold level is setusing the [Color Killer Control Register].

When the input chroma signal level is lower than the preset level, the input chroma signal is treated as insufficient and it is processed as a Black and White signal.

When the Color Burst signal level is lower than the Standard signal levels (NTSC:286 [mV] / PAL:300 [mV]), the Color Killer function is activated.

In this case, Cb/Cr data from the AK8851 is fixed at 0x80 in 601 levels.

#### Note)

When the Color Killer function is activated, all input signals fed to the YC separation module are processed as Y signal in the same way as in the Black and White mode which is set by [B/W]-bit of [Input Video Standard Register]. Bit allocation of [Color Killer Control Register](R/W)[Sub Address 0x0D] is shown below.

#### Sub Address 0x0D

# Default Value : 0x08

| bit 7         | bit 6    | bit 5  | bit 4  | bit 3  | bit 2  | bit 1  | bit 0  |  |

|---------------|----------|--------|--------|--------|--------|--------|--------|--|

| COLKILL       | Reserved | CKSCM1 | CKSCM0 | CKLVL3 | CKLVL2 | CKLVL1 | CKLVL0 |  |

| Default Value |          |        |        |        |        |        |        |  |