## Description

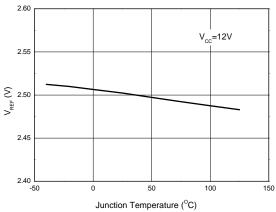

The AL6562 is a current mode Power Factor Correction Controller and is designed for operating in Transition Mode. With a superior linear performance multiplier, it ensures the device operates over a wide input voltage range with superior THD (Total Harmonics Distortion). The output voltage is controlled by means of an error amplifier and a precise (1% @  $T_J = +25^{\circ}$ C) internal voltage reference.

The AL6562 is designed to meet stringent energy-saving standards with low start-up current, and can operate with low current consumption when entering stand-by mode.

OVP circuitry increases system robustness, allowing the device to withstand transient caused at start-up and during load-disconnects.

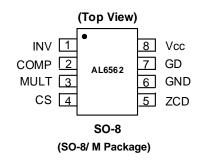

## **Pin Assignments**

### **Transition Mode PFC LED Controller**

### **Features**

- Single Stage Fly-Back PFC Controller

- Transition Mode Operation

- Low Start-Up, Operating and Quiescent Currents

- Internal Start-Up Timer

- Enable/Disable Function on INV Input

- Totem Pole, Push-Pull Output Drive

- Adjustable Output Overvoltage Protection

- SO-8 : Available in "Green" Molding Compound (No Br, Sb)

- Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)

- Halogen and Antimony Free. "Green" Device (Note 3)

## Applications

- Electronic Single-Stage LED Driver

- PFC Pre-Regulators to meet IEC61000-3-2

- High-End AC-DC Adaptor / Charger

- Notes: 1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS) & 2011/65/EU (RoHS 2) compliant.

- 2. See http://www.diodes.com/quality/lead\_free.html for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

- 3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

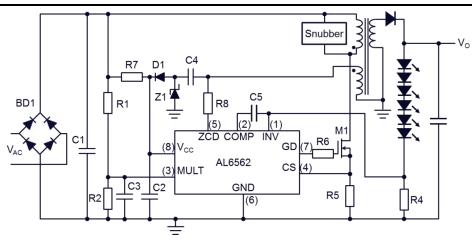

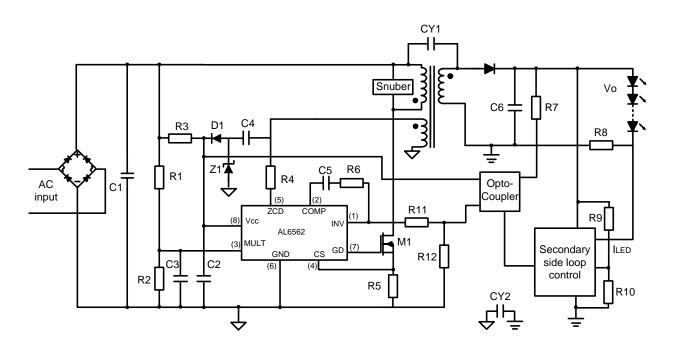

# **Typical Applications Circuit**

Figure 1 High Power Factor Non-Isolated Constant-Current LED Driver

# **Pin Descriptions**

| Pin Number | Pin Name | Brief Description                                                                                                                                                                                                                                                                                                                                                                |

|------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |          | Inverting Input Pin of the Internal Error Amplifier                                                                                                                                                                                                                                                                                                                              |

| 1 INV      |          | This pin is connected externally via a resistor divider from the regulated output voltage. It can provide input to inverting input of internal error amplifier. This pin can also be used as ENABLE/DISABLE control input.                                                                                                                                                       |

|            |          | Output from Error Amplifier                                                                                                                                                                                                                                                                                                                                                      |

| 2          | COMP     | A feedback compensation network consisting of resistor and capacitor connects between INV (Pin1) and this pin to reduce the bandwidth and achieve stability of the voltage control loop and ensure high power factor and low THD.                                                                                                                                                |

|            |          | Input to the Internal Multiplier                                                                                                                                                                                                                                                                                                                                                 |

| 3          | MULT     | This pin connects to the rectified mains voltage through external resistor divider to provide a sinusoidal voltage reference for the control current loop.                                                                                                                                                                                                                       |

|            |          | Current Sense Connecting to External Resistor for Current Feedback                                                                                                                                                                                                                                                                                                               |

| 4          | CS       | The current flowing in the MOSFET is sensed through a resistor, the resulting voltage is applied to this<br>pin and compared with an internal sinusoidal-shaped reference generated by the multiplier to determine<br>MOSFET's turn-off. This pin has an internal Leading-Edge-Blanking of about 200 nanoseconds to<br>improve noise immunity.                                   |

|            |          | Zero Current Detection                                                                                                                                                                                                                                                                                                                                                           |

| 5          | ZCD      | This pin takes input from inductor's demagnetization sensing to achieve zero current detection, required for Transition Mode (TM) operation. A negative-going edge triggers turn-on of MOSFET.                                                                                                                                                                                   |

| 6          | GND      | System Ground                                                                                                                                                                                                                                                                                                                                                                    |

| 0          | 0 P      | Ground for circuit. Current return for both the signal circuitry and the gate drive stage.                                                                                                                                                                                                                                                                                       |

| 7          | GD       | Gate Driver Output<br>This pin is able to drive external MOSFET. The totem-pole output stage is able to drive MOSFET with a<br>peak current of 600mA/800mA for source and sink capability respectively. The high level voltage of this<br>pin is internally clamped at about 12V to avoid excessive gate voltage in case V <sub>CC</sub> pin is supplied by a<br>higher voltage. |

|            |          | System Power Input Pin                                                                                                                                                                                                                                                                                                                                                           |

| 8          | Vcc      | This pin is for supply voltage of both the signal part and gate driver of the IC. Upper limit is extended to a maximum of 22V to provide more headroom for supply voltage changes. This pin has an internal 25V Zener to protect the IC itself from overvoltage transients.                                                                                                      |

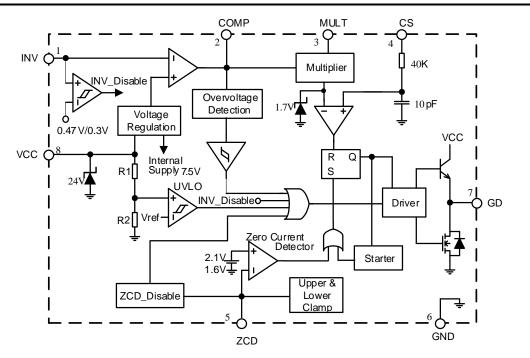

# **Functional Block Diagram**

# Absolute Maximum Ratings (Note 4)

| Symbol                    | Description                                          | Value                   | Unit     |

|---------------------------|------------------------------------------------------|-------------------------|----------|

| V <sub>CC</sub>           | IC Supply Voltage                                    | Self Limited            | V        |

| lcc                       | Operating Supply Current                             | 30                      | mA       |

| VINV, VCOMP, VMULT        | Input/Output of Error Amplifier, Input of Multiplier | -0.3 to 7               | V        |

| I <sub>ZCD</sub> (Note 5) | Zero Current Detector Max. Current                   | Source: -50<br>Sink: 10 | mA<br>mA |

| ESD(HBM)                  | ESD (Human Body Model)                               | 3000                    | V        |

| ESD(MM)                   | ESD (Machine Model)                                  | 200                     | V        |

| TJ                        | Junction Temperature Range                           | -40 to +150             | °C       |

| T <sub>STG</sub>          | Storage Temperature Range                            | -65 to +150             | °C       |

| P <sub>TOT</sub>          | Power Dissipation                                    | 0.65                    | W        |

| R <sub>0JA</sub>          | Thermal Resistance (Junction – Ambient)              | 150                     | °C/W     |

| T <sub>LEAD</sub>         | Lead Temperature (Soldering, 10 sec)                 | +260                    | °C       |

Stresses greater than the 'Absolute Maximum Ratings' specified above, may cause permanent damage to the device. These are stress ratings only; functional operation of the device at these or any other conditions exceeding those indicated in this specification is not implied. Device reliability may be affected by exposure to absolute maximum rating conditions for extended periods of time.

Currents flowing into device pins are considered as positive and out of device pins are considered as negative. Notes:

# **Electrical Characteristics**

| Symbol                                | Parameter                              | Conditions                                                                                 | Min   | Тур.       | Max   | Units |

|---------------------------------------|----------------------------------------|--------------------------------------------------------------------------------------------|-------|------------|-------|-------|

| UPPLY VOL                             | TAGE                                   |                                                                                            | •     |            |       |       |

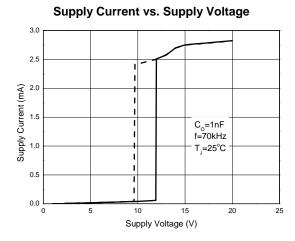

| V <sub>cc</sub>                       | IC Supply Voltage                      | After turn-on                                                                              | 10.3  |            | 22    | V     |

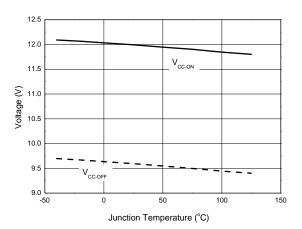

| V <sub>CC</sub><br>V <sub>CC ON</sub> | IC Supply Voltage<br>Turn-On Threshold |                                                                                            | 10.3  | 12.0       | 13.0  | v     |

| VCC ON<br>VCC OFF                     | Turn-Off Threshold                     | —                                                                                          | 8.7   | 9.5        | 10.3  | V     |

|                                       |                                        |                                                                                            |       | 9.5<br>2.5 | 2.8   | V     |

| V <sub>CC-HYS</sub><br>V <sub>7</sub> | Hysteresis                             |                                                                                            | 2.2   |            | 2.0   | V     |

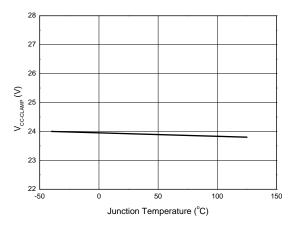

|                                       | Zener Voltage                          | $I_{CC} = 20 \text{ mA}$                                                                   | 22    | 24         | _     | V     |

|                                       |                                        |                                                                                            |       | 40         | 70    |       |

| Istart-up                             | Start-Up Current                       | Before turn-on, V <sub>CC</sub> =11V                                                       |       | 40         | 70    | μA    |

| lα                                    | Quiescent Current                      | After turn-on                                                                              |       | 2.5        | 3.75  | mA    |

|                                       |                                        | @ 70kHz                                                                                    | —     | 3.5        | 5     | mA    |

| I <sub>cc</sub>                       | Operating Supply Current               |                                                                                            |       |            |       |       |

|                                       |                                        | In OVP condition, $V_{INV} = 2.7V$                                                         |       | 1.4        | 2.2   | mA    |

|                                       |                                        | V <sub>ZCD</sub> ≪150mV, V <sub>CC</sub> >V <sub>CC-OFF</sub>                              |       |            | 2.2   | mA    |

| la                                    | Quiescent Current                      |                                                                                            |       |            |       | IIIA  |

| IQ                                    | Quescent Current                       | V <sub>ZCD</sub> ≪150mV, V <sub>CC</sub> <v<sub>CC-OFF</v<sub>                             |       | 50         | 00    | mA    |

|                                       |                                        | vzcd≪ ISOIIIv, vcc <vcc-off< td=""><td>20</td><td>50</td><td>90</td><td>ША</td></vcc-off<> | 20    | 50         | 90    | ША    |

| RROR AMP                              |                                        | <b>T</b> 0500                                                                              | 0.405 | 0.5        | 0.505 |       |

| VINV                                  | Voltage Feedback Input Threshold       | $T_J = +25^{\circ}C$                                                                       | 2.465 | 2.5        | 2.535 | V     |

|                                       |                                        | $10.3V < V_{cc} < 22V$                                                                     | 2.44  | —          | 2.56  |       |

|                                       | Line Regulation                        | $V_{CC} = 10.3V \text{ to } 22V$                                                           |       | 2          | 5     | mV    |

|                                       | -                                      | (Note 6)                                                                                   |       |            |       |       |

| I <sub>INV</sub>                      | Input Bias Current                     | $V_{INV} = 0$ to 3V                                                                        |       | -0.1       | -1    | μA    |

| Gv                                    | Voltage Gain                           | OPEN LOOP                                                                                  | 60    | 80         |       | dB    |

| GB                                    | Gain-Bandwidth                         |                                                                                            |       | 1          |       | MHz   |

| lagua                                 | Source Current                         | $V_{COMP} = 4V, V_{INV} = 2.4V$                                                            | -2    | -4.0       | -8    | mA    |

| COMP                                  | Sink Current                           | $V_{COMP} = 4V, V_{INV} = 2.6V$                                                            | 2.5   | 4.5        | _     | mA    |

| V <sub>COMP</sub>                     | Upper Clamp Voltage                    | $I_{SOURCE} = 0.5 \text{ mA}$                                                              |       | 5.8        | _     | V     |

|                                       | Lower Clamp Voltage                    | $I_{SINK} = 0.5 \text{ mA}$ (Note 6)                                                       | 2.1   | 2.25       | 2.4   | V     |

| V <sub>INVdis</sub>                   | Disable Threshold                      | _                                                                                          | 250   | 300        | 350   | mV    |

| V <sub>INVen</sub>                    | Restart Threshold                      | _                                                                                          | 400   | 470        | 540   | mV    |

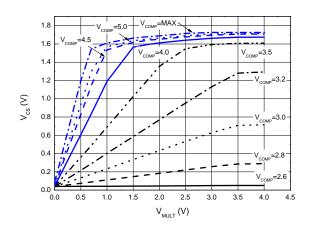

| ULTIPLIER                             | INPUT                                  |                                                                                            | •     | •          |       |       |

| V <sub>MULT</sub>                     | Linear Operation Range                 |                                                                                            | 0 - 3 | 0 - 3.5    |       | V     |

|                                       |                                        |                                                                                            |       |            |       |       |

| $\Delta V_{CS}$                       | - Output Maximum Slope                 | $V_{MULT} = 0$ to 0.5V,                                                                    | 1.65  | 1.9        | _     | V/V   |

| $\Delta V_{\text{MULT}}$              |                                        | V <sub>COMP</sub> = upper clamp                                                            |       |            |       | .,.   |

| К                                     | Gain (Note 7)                          | $V_{MULT} = 1V, V_{COMP} = 4V$                                                             | 0.6   | 0.75       | 0.9   | 1/V   |

|                                       | ENT DETECTOR                           |                                                                                            | 0.0   | 0.70       | 0.0   | 1/ V  |

| V <sub>ZCDH</sub>                     | Upper Clamp Voltage                    | I <sub>ZCD</sub> = 3mA                                                                     | 4.7   | 5.2        | 6.1   | V     |

| VZCDH                                 | Lower Clamp Voltage                    | $I_{ZCD} = -3mA$                                                                           | 0.3   | 0.65       | 1.0   | v     |

| VZCDL                                 | Arming Voltage                         | Positive-going edge                                                                        | 0.0   | 2.1        | 1.0   | v     |

| V <sub>ZCDA</sub>                     | Triggering Voltage                     | Negative-going edge                                                                        | +     | 1.6        |       | V     |

| V ZCDT                                | Input Bias Current                     | $V_{ZCD}$ =1 to 4.5V                                                                       | +     | 2          |       | μA    |

| I <sub>ZCDb</sub>                     |                                        |                                                                                            |       |            | 40    |       |

| ZCDsrc                                | Source Current Capability              |                                                                                            | -2.5  |            | -10   | mA    |

| ZCDsnk                                | Sink Current Capability                | — —                                                                                        | 3.0   |            |       | mA    |

| $V_{\text{ZCDdis}}$                   | Disable Threshold                      |                                                                                            | 150   | 200        | 250   | mV    |

| V <sub>ZCDen</sub>                    | Restart Threshold                      |                                                                                            | 330   | 400        | 470   | mV    |

| I <sub>ZCDres</sub>                   | Restart Current after Disable          | $V_{ZCD} < V_{DIS}, V_{CC} > V_{CC-OFF}$                                                   | -80   | -120       |       | μA    |

| TARTER                                |                                        |                                                                                            | -     |            |       |       |

| t <sub>start</sub>                    | Start Timer Period                     | —                                                                                          | 75    | 130        | 300   | μs    |

| es: 6.                                | All parameters are in tracking.        |                                                                                            |       |            |       |       |

# **Electrical Characteristics**

| Symbol                 | Parameter                      | Conditions                                        | Min | Тур  | Max | Units |

|------------------------|--------------------------------|---------------------------------------------------|-----|------|-----|-------|

| OUTPUT OV              | ER-VOLTAGE                     | ·                                                 | •   |      | •   |       |

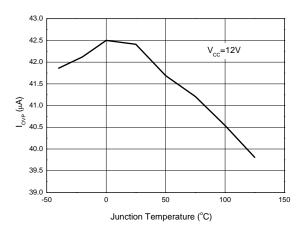

| I <sub>OVP</sub>       | Dynamic OVP Triggering Current | _                                                 | 35  | 40   | 45  | μA    |

| VOVP_TH                | Static OVP Threshold           |                                                   | 2.1 | 2.25 | 2.4 | V     |

| CURRENT S              | SENSE COMPARATOR               |                                                   |     |      |     |       |

| lcs                    | Input Bias Current             | $V_{CS} = 0$                                      | _   |      | -1  | μA    |

| td <sub>(H-L)</sub>    | Delay to Output                | —                                                 |     | 200  | 350 | ns    |

| V <sub>CS-clamp</sub>  | Current Sense Clamp            | V <sub>COMP</sub> = upper clamp                   | 1.6 | 1.7  | 1.8 | V     |

|                        | Current Sense Offset           | $V_{MULT} = 0$                                    | —   | 30   | _   | mV    |

| V <sub>CS-offset</sub> |                                | $V_{MULT} = 2.5V$                                 | —   | 5    | —   |       |

| GATE DRIV              | ER                             |                                                   |     |      |     |       |

| V <sub>OL</sub>        | Output Low Dropout Voltage     | I <sub>GDsink</sub> = 200 mA                      | —   | 0.9  | 1.9 | V     |

|                        | Output High Dropout Voltage    | I <sub>GDsource</sub> = 200 mA                    |     | 2.5  | 3.0 | V     |

| V <sub>OH</sub>        |                                |                                                   | —   | 2.0  | 2.8 | V     |

|                        |                                | I <sub>GDsource</sub> = 20 mA                     |     |      |     |       |

| t <sub>f</sub>         | Voltage Fall Time              | —                                                 | —   | 30   | 70  | ns    |

| tr                     | Voltage Rise Time              | _                                                 |     | 60   | 110 | ns    |

| V <sub>Oclamp</sub>    | Output Clamp Voltage           | I <sub>SOURCE</sub> = 5 mA, V <sub>CC</sub> =20 V | 9   | 11   | 13  | V     |

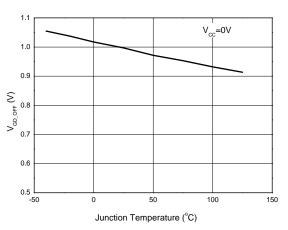

| Vos                    |                                | V <sub>CC</sub> =0 V to V <sub>CCon</sub> ,       |     | —    | 1.1 | V     |

| VUS                    | UVLO Saturation                | $I_{SINK} = 10 \text{ mA}$                        |     |      |     |       |

## **Performance Characteristics**

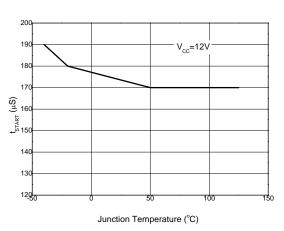

### Icc Consumption vs.T<sub>J</sub>

Feedback Reference Voltage vs. T<sub>J</sub>

Start-up & UVLO Vs. TJ

Vcc Zener Voltage Vs. T<sub>J</sub>

### OVP Current vs. TJ

## Performance Characteristics (cont.)

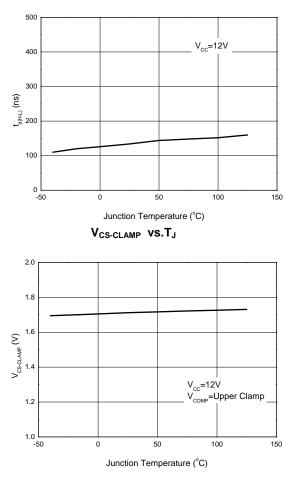

### Delay-to-output vs.TJ

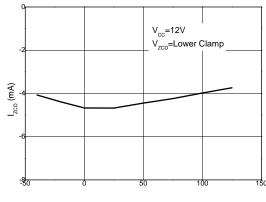

ZCD Source Capability vs.TJ

Junction Temperature (°C)

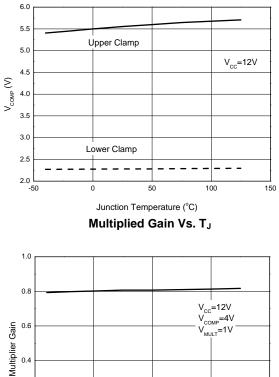

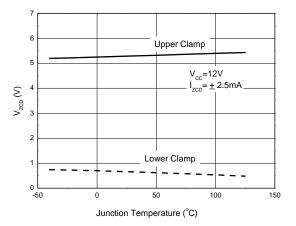

## E/A Output Clamp Levels Vs. T<sub>J</sub>

ZCD Clamp Levels Vs. T<sub>J</sub>

## Performance Characteristics (cont.)

Start-up Timer vs.TJ

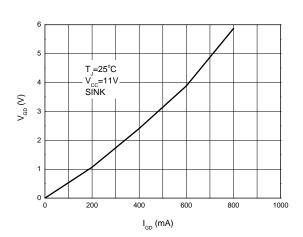

# Gate-driver Output Low Saturation

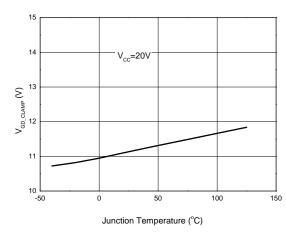

Gate-driver Clamp vs. TJ

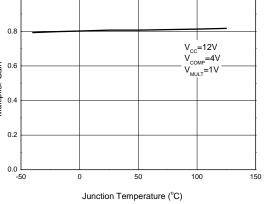

**Multiplier Characteristics**

$V_{GD}(V)$ V<sub>cc</sub>-2.0 Tj=25°C V<sub>cc</sub>-2.5 V<sub>cc</sub>=11V SOURCE V<sub>cc</sub>-3.0 V<sub>cc</sub>-3.5 V<sub>cc</sub>-4.0 100 300 400 0 200 500 600 700 I<sub>GD</sub> (mA)

### UVLO Saturation vs. TJ

Gate-driver Output High Saturation

## **Application Information**

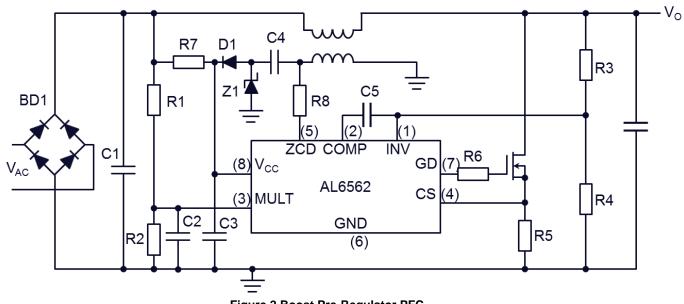

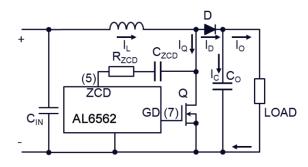

### Figure 2 Boost Pre-Regulator PFC

### POWER FACTOR CORRECTION

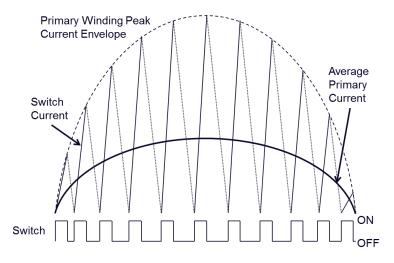

AL6562 functions as a transition mode PFC IC, meaning the MOSFET turns on when inductor current reaches zero, and turns off when the current meets desired input current reference voltage, as shown in Figure 3. A typical current waveform is depicted with envelope as shown, with the input current following that of the input voltage, achieving good power factor.

### Figure 3 Typical Waveform of Inductor Current with Fixed ON Time

From a mathematical point of view, a PF value can be defined by:

$$PF = \cos(\theta) * k_{D} = \frac{\cos(\theta)}{\sqrt{1 + \sum_{2}^{\infty} \left(\frac{\operatorname{Irms} n}{\operatorname{Irms} 1}\right)^{2}}}$$

Where  $\cos(\theta)$  represents displacement factor with  $\theta$  as the displacement angle between voltage and current fundamentals, and  $k_D$  represents distortion respectively.

### Application Information (cont.)

$k_{\rm D}$ , the distortion can further be defined by:

$$k_{\rm D} = \frac{I_{\rm rms\_1}}{I_{\rm rms}} = \frac{I_{\rm rms\_1}}{\sqrt{I_{\rm rms\_2}^2 + I_{\rm rms\_3}^2 + \dots}}$$

Where  $I_{rms_1}$  and  $I_{rms_n}$  are the RMS (Root Mean Square) value n-th fundamental component of the current respectively. If the current and voltage are in phase, then  $\theta$ = 0, which will lead to  $\cos(\theta) = 1$ , and the PF will be simplified as:

$PF = k_D$

#### **ZCD (Zero Current Detection)**

The ZCD feature detects when the transformer primary current falls to zero, as the voltage across the inductor reverses, to initiate a new cycle that switches on the power MOSFET. The signal for ZCD is obtained by an auxiliary winding on the boost inductor, as shown in Figure 2.

#### **Multiplier**

The internal multiplier takes two inputs, one from a portion of the instantaneous rectified line voltage (via pin 3, MULT) and the other from the output of the E/A (via pin 2, COMP), to feed the PWM comparator to determine the exact instant when the MOSFET is to be switched off. The output of multiplier is a rectified sinusoid, similar to the instantaneous rectified line voltage, multiplied by the scaling factor determined by output of the Error Amplifier. The MULT output is then fed into the PWM comparator and is compared to the current sense voltage  $V_{CS}$ , to switch the Power MOSFET off. The formula governing all parameters is given by:

Multiplier Output:

$$V_{CS} = k x (V_{COMP} - 2.5V) x V_{MULT}$$

Where: k is the multiplier gain. V<sub>MULT</sub> is set by external resistors R1 and R2.

#### **OVP (Output Overvoltage Protection)**

The output voltage can be kept constant by the operation of the PFC circuit close to its nominal value, as shown by Figure 2, which is set by the ratio of the two external resistors R3 and R4. Neglecting ripple current, current flowing through R3,  $I_{R3}$ , will equal the current through R4,  $I_{R4}$ . As the non-inverting input of the error amplifier is biased inside the AL6562 at 2.5V, the current through R4 is:

$$I_{R4} = \frac{2.5}{R_4} = I_{R3} = \frac{V_0 - 2.5}{R_3}$$

(1)

If any abrupt change of output voltage,  $\Delta V_O > 0$  occurs due to a load drop, the voltage at pin INV will be kept at 2.5V by the local feedback of the EA. The network connected between INV and COMP introduces a time constant to achieve high PF. The current through R4 will remain equal to 2.5/R4, but I<sub>R3</sub> will become:

$$I'_{R3} = \frac{V_0 + \Delta V_0 - 2.5}{R_3}$$

(2)

The difference current  $\Delta I_{R3} = I'_{R3} - I_{R3} = \Delta V_0/R3$  will flow through the compensation network and enter the error amplifier output via pin COMP. The AL6562 monitors the current flowing into the error amplifier output pin. When the detected current is higher than 40µA, the dynamic OVP is triggered. The IC will be disabled and the driver signal will be stopped.

The output  $\Delta$ Vo that is able to trigger the Dynamic OVP function is then:

$$\Delta V_0 = 40 \text{uA x R3}$$

## Application Information (cont.)

On the other hand, when the loading of PFC pre-regulator becomes low, the output voltage tends to stay steadily above the nominal value, which is not the case when OVP is triggered by abrupt voltage increase. If this occurs, the E/A will saturate low, the external power transistor is switched OFF, and the IC is put in idle state (static OVP). Normal operation is resumed as the error amplifier goes back into its linear region. As a result, the device will work in burst-mode, with a repetition rate that can be very low. When either OVP is activated, the quiescent consumption of the IC is reduced to minimum by the discharge of the capacitor and increases the hold-up capability of the IC supply.

### **THD (Total Harmonics Distortion)**

The AL6562 reduces the THD by reducing conduction dead-angle occurring to the AC input current near the zero-crossings of the line voltage.

The important reason for this distortion to take place is the inability of the system to transfer energy effectively when the instantaneous line voltage is very low, which is the case near line-voltage zero-crossing. This effect is magnified by the high-frequency filter capacitor placed after the bridge rectifier, which retains some residual voltage that causes the diodes of the bridge rectifier to be reverse-biased and the input current flow to temporarily stop.

To overcome this issue, the circuit section designed in the AL6562 forces the PFC regulator to process more energy near the line voltage zero-crossings, as compared to that commanded by the control loop. This results in both minimizing the time interval when energy transfer is lacking, and fully discharging the high-frequency filter capacitor after the bridge.

In essence, the circuit artificially increases the ON-Time of the Power Switch with a positive offset added to the output of the multiplier in the proximity of the line voltage zero-crossings. This offset is reduced as the instantaneous line voltage increases, so that it becomes negligible as the line voltage moves towards the peak of the sinusoidal waveform.

Therefore, to maximize the benefit from the THD improvement circuit, the high-frequency filter capacitor after the bridge rectifier should be minimized and kept to satisfy the EMI filtering requirements.

#### Non-Latched IC Disable (Enable)

Pin 1, INV, inverting input to the error amplifier, can be adapted to disable the system when the voltage on this pin is below 0.2V. In order to restart the system, a voltage exceeding 0.45V must be applied. The ON/OFF control signal can be driven by a PWM controller and using an NPN transistor to pin 1 to shut it down.

## Application Information (Cont.)

### Single Stage LED Driver with PFC

One of the major applications of AL6562 is to provide a single stage power module with high PF for LED lighting. The following circuit, Figure 4, shows a simplified fly-back AC-DC converter with both CC and CV feedback from output side, to prevent overload and also provide an over-voltage protection facility.

Figure 4 Single Stage PFC Isolated LED lighting

With its high performance, the AL6562 offers the following advantages that make this solution an appropriate method against the traditional PWM controller, where a good PF value is required:

- The input capacitance can be reduced to replace a bulky and expensive high-voltage electrolytic capacitor (as required by regular offline SMPS) by a small-size, cheaper film capacitor.

- Transition mode ensures low turn-on losses in MOSFET and higher efficiency can be achieved.

- Lower parts count means lower material cost, as well as lower assembly cost for limited space.

## Application Information (Cont.)

#### **PFC Pre-Regulator**

Another major application of AL6562 is to implement a wide-range mains input PFC pre-regulator, which acts as the input stage for the cascaded DC-DC converter and can deliver above 350W in general.

There are two methods, in general, to design a pre-regulator stage:

- 1. With fixed frequency

- or

- 2. With fixed ON time

The AL6562 can easily be implemented with fixed ON time due to its simplicity, while the fixed frequency technique is more complicated.

In fixed ON time mode, AL6562 is also working in transition mode where the inductor current will be turned on when zero crossing is detected.

By using boost-switching technique, the AL6562 shapes the input current by drawing a quasi-sinusoidal current in-phase with the line voltage. A simplified circuit, shown in Figure 5, explains the operation as follows:

#### Figure 5 ZCD Pin Synchronization without Auxiliary Winding

The AC mains voltage is rectified by a diode bridge and delivered to the boost converter which boosts the rectified input voltage to a higher regulated DC bus  $V_{O}$ .

The error amplifier compares a portion of the output voltage with an internal reference and generates a signal error proportional to the difference between them. The bandwidth of the internal error amplifier is set to be narrow within 20Hz; the output would be a DC value over a given half-cycle. Output of E/A fed into multiplier, multiplied by a portion of the rectified mains voltage, will generate a scaled rectified sinusoid whose peak amplitude depends on the rectified mains peak voltage as well as the value of error signal.

The output of the multiplier is fed into the non-inverting pin of the internal PWM comparator. As the output from the multiplier, a sinusoidal reference for PWM, equals the voltage on the current sense pin CS(4), the MOSFET will be turned off. As a consequence, the peak inductor current will follow the envelope of a rectified sinusoid. After the MOSFET is turned off, the boost inductor discharges its stored energy to the load until zero current is detected and then the MOSFET will be turned on again.

In the case where there is no auxiliary winding on the boost inductor, a solution can be implemented by sconnecting the ZCD pin to the drain of the power MOSFET through an R-C network: in this way the high-frequency edges experienced by the drain will be transferred to the ZCD pin, hence arming and triggering the ZCD comparator.

The resistance value must be properly chosen to limit the current sourced/sunk by the ZCD pin. In typical applications with output voltages around 400V, recommended values for these components are 22pF (or 33pF) for  $C_{ZCD}$  and 330K for  $R_{ZCD}$ . With these values proper operation is ensured even with a few volts difference between the regulated output voltage and the peak input voltage.

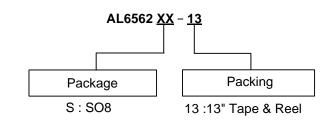

# **Ordering Information**

| Dant Namelaan | Deskerne | Destance et a | 13" Tape and Reel |                    |  |

|---------------|----------|---------------|-------------------|--------------------|--|

| Part Number   | Package  | Package code  | Quantity          | Part Number Suffix |  |

| AL6562S-13    | SO-8     | S             | 2,500/Tape & Reel | -13                |  |

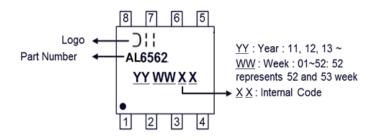

# **Marking Information**

(1) SO-8

## Package Outline Dimensions (All Dimensions in mm.)

Please see AP02002 at http://www.diodes.com/datasheets/ap02002.pdf for the latest version.

| SO-8   |                      |      |  |  |

|--------|----------------------|------|--|--|

| Dim    | Min                  | Max  |  |  |

| Α      | -                    | 1.75 |  |  |

| A1     | 0.10                 | 0.20 |  |  |

| A2     | 1.30                 | 1.50 |  |  |

| A3     | 0.15                 | 0.25 |  |  |

| b      | 0.3                  | 0.5  |  |  |

| D      | 4.85                 | 4.95 |  |  |

| Е      | 5.90                 | 6.10 |  |  |

| E1     | 3.85                 | 3.95 |  |  |

| е      | 1.27                 | Тур  |  |  |

| h      | -                    | 0.35 |  |  |

| L      | 0.62                 | 0.82 |  |  |

| θ      | 0°                   | 8°   |  |  |

| All Di | All Dimensions in mm |      |  |  |

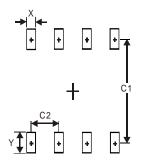

# **Suggested Pad Layout**

Please see AP02001 at http://www.diodes.com/datasheets/ap02001.pdf for the latest version.

| Dimensions | Value (in mm) |

|------------|---------------|

| Х          | 0.60          |

| Y          | 1.55          |

| C1         | 5.4           |

| C2         | 1.27          |

#### IMPORTANT NOTICE

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes Incorporated.

#### LIFE SUPPORT

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

A. Life support devices or systems are devices or systems which:

- 1. are intended to implant into the body, or

- 2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

- B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systemsrelated information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2015, Diodes Incorporated

#### www.diodes.com