晶采光電科技股份有限公司 AMPIRE CO., LTD.

# SPECIFICATIONS FOR LCD MODULE

| CUSTOMER          |                         |

|-------------------|-------------------------|

| CUSTOMER PART NO. |                         |

| AMPIRE PART NO.   | AM-320240N1TMQW-TW5H(R) |

| APPROVED BY       |                         |

| DATE              |                         |

- **☑** Approved For Specifications

- ☐ Approved For Specifications & Sample

AMPIRE CO., LTD.

Building D., 2F., No.88, Sec. 1, Sintai 5th Rd., Sijhih City, Taipei County 221, Taiwan (R.O.C.)

台北縣汐止市新台五路一段 88 號 2 樓(東方科學園區 D 棟)

TEL:886-2-26967269, FAX:886-2-86967196 or 26967270

| APPROVED BY | CHECKED BY | ORGANIZED BY |

|-------------|------------|--------------|

|             |            |              |

|             |            |              |

|             |            |              |

Date: 2008/4/29 AMPIRE CO., LTD.

The contents of this document are confidential and must not be disclosed wholly or in part to any third part without the prior written consent of AMPIRE CO., LTD

## RECORD OF REVISION

| Revision Date | Page | Contents                                                                   | Editor |

|---------------|------|----------------------------------------------------------------------------|--------|

| 2007/10/9     | -    | New Release                                                                | Edward |

|               |      | TFT LCD controller + Pin Header ( 8bit 80 interface ) + TP + TP controller |        |

| 2008/4/1      | 6    | Modify electrical characteristic of led back-light                         | Kasha  |

|               | 46   | Add guarantee declaration                                                  | Kasha  |

| 2008/4/29     |      | Modify 8.3 65K/262K selection                                              | Kokai  |

|               |      |                                                                            |        |

|               |      |                                                                            |        |

|               |      |                                                                            |        |

|               |      |                                                                            |        |

|               |      |                                                                            |        |

|               |      |                                                                            |        |

|               |      |                                                                            |        |

|               |      |                                                                            |        |

|               |      |                                                                            |        |

|               |      |                                                                            |        |

|               |      |                                                                            |        |

|               |      |                                                                            |        |

|               |      |                                                                            |        |

|               |      |                                                                            |        |

|               |      |                                                                            |        |

|               |      |                                                                            |        |

|               |      |                                                                            |        |

|               |      |                                                                            |        |

|               |      |                                                                            |        |

|               |      |                                                                            |        |

The contents of this document are confidential and must not be disclosed wholly or in part to any third part without the prior written consent of AMPIRE CO., LTD

#### 1 Features

5.7 inch Amorphous-TFT-LCD (Thin Film Transistor Liquid Crystal Display) module. This module is composed of a 5.7" TFT-LCD panel, LCD controller, power driver circuit and backlight unit.

#### 1.1 TFT Panel Feature:

- (1) Construction: 5.7" a-Si color TFT-LCD, White LED / CCFL Backlight and PCB.

- (2) Resolution (pixel): 320(R.G.B) X240

- (3) Number of the Colors: 262K colors (R, G, B 6 bit digital each)

- (4) LCD type: Transmissive Color TFT LCD (normally White)

- (5) Interface: 34 pin Pin Header.

- (6) Power Supply Voltage: 3.3V single power input. Built-in power supply circuit.

- (7) Viewing Direction: 6 O'clock (The direction it's hard to be discolored):

#### 1.2 LCD Controller Feature:

- (1) MCU interface 8/9/16/18 bit 80&68 series MCU interface.

- (2) Display RAM size: 640x240x3x6 bits. Ex:320x240 two frame buffer with 262K colors.

- (3) Arbitrary display memory start position selection.

- (4) MCU interface: 8 bit 80 MPU interface.

- (5) 8 bit / 16 bit interface support 65K ( R5G6B5) /262K(R6G6B6) colors data format.

- (6) 9 bit / 18 bit interface support 262K(R6G6B6) colors data format only.

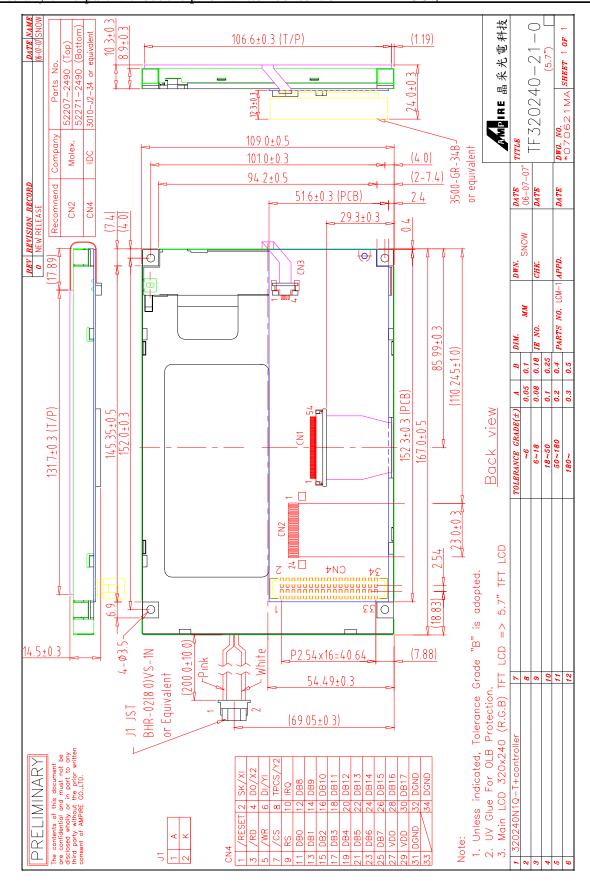

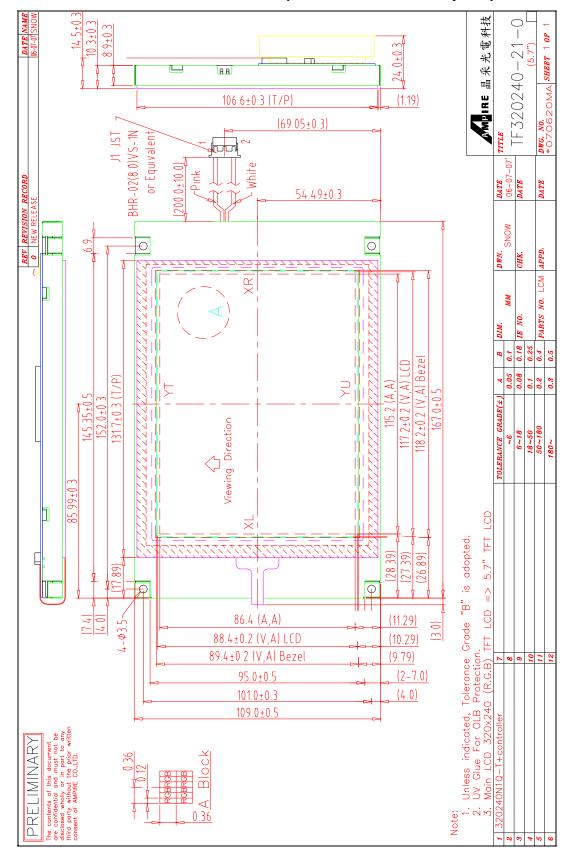

## 2 Physical specifications

| Item                    | Specifications            | Unit |  |

|-------------------------|---------------------------|------|--|

| Display resolution(dot) | 960 (W) x 240(H)          | Mm   |  |

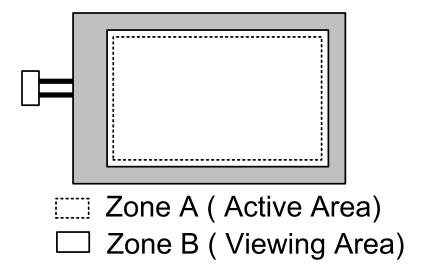

| Active area             | 115.2 (W) x 86.4 (H)      | Mm   |  |

| Screen size             | 5.7(Diagonal)             | Mm   |  |

| Pixel size              | 120 (W) x 360 (H)         | Um   |  |

| Color configuration     | R.G.B stripe              |      |  |

| Overall dimension       | 131.0(W)x102.2(H)x14.5(D) | Mm   |  |

| Weight                  | T.B.D                     | Mg   |  |

| Backlight unit          | LED                       |      |  |

The contents of this document are confidential and must not be disclosed wholly or in part to any third part without the prior written consent of AMPIRE CO., LTD

## 3 Default Setting & Option

#### • Interface:

The user can select the MCU interface by change the Jumper & Resister Array.

| Setting            | JP1       | RA1  | RA2  | RA3  | RA4  | Remark  |

|--------------------|-----------|------|------|------|------|---------|

| Interface Type     |           |      |      |      |      |         |

| 80-18Bit interface | 1,2 short | 2K   | OPEN | OPEN | OPEN |         |

|                    | 2,3 open  | ohm  |      |      |      |         |

| 80-16Bit interface | 1,2 short | OPEN | 2K   | OPEN | OPEN |         |

|                    | 2,3 open  |      | ohm  |      |      |         |

| 80-9Bit interface  | 1,2 short | OPEN | OPEN | 2K   | OPEN |         |

|                    | 2,3 open  |      |      | ohm  |      |         |

| 80-8Bit interface  | 1,2 short | OPEN | OPEN | OPEN | 2K   | Default |

|                    | 2,3 open  |      |      |      | ohm  |         |

| 68-18Bit interface | 1,2 open  | 2K   | OPEN | OPEN | OPEN |         |

|                    | 2,3 short | ohm  |      |      |      |         |

| 68-16Bit interface | 1,2 open  | OPEN | 2K   | OPEN | OPEN |         |

|                    | 2,3 short |      | ohm  |      |      |         |

| 68-9Bit interface  | 1,2 open  | OPEN | OPEN | 2K   | OPEN |         |

|                    | 2,3 short |      |      | ohm  |      |         |

| 68-8Bit interface  | 1,2 open  | OPEN | OPEN | OPEN | 2K   |         |

|                    | 2,3 short |      |      |      | ohm  |         |

#### Connector

The user can select the connector type.

| Option                                        | Support inter | face Remark              |

|-----------------------------------------------|---------------|--------------------------|

| 24 Pin FFC Cable<br>( Pitch1.0x24pin)         | 80/68 8bit    | interface only           |

| 34Pin Pin Header<br>( Pitch 2.54 x 34<br>pin) | 80/68 8/9/16/ | 18 bit interface Default |

#### Touch panel and Touch panel controller:

The user can select the with TP controller or without TP controller.

| Pin Define                   | SK/X1 | DO/X2 | DI/Y1 | TPCS/Y2 | IRQ | Remark  |

|------------------------------|-------|-------|-------|---------|-----|---------|

| Option                       |       |       |       |         |     |         |

| Without TP                   | NC    | NC    | NC    | NC      | NC  |         |

| With TP / Without            | X1    | X2    | Y1    | Y2      | NC  |         |

| TP controller                |       |       |       |         |     |         |

| With TP / With TP controller | SK    | DO    | DI    | TPCS    | IRQ | Default |

If user want to change the default setting for mass production, please contact with Amprie. We'll apply a new P/N for you.

## 4 Electrical specification

#### 4.1 Absolute max. ratings

#### 4.1.1 Electrical Absolute max. ratings

| Item          | Symbol            | Condition | Min. | Max.    | Unit | Remark |

|---------------|-------------------|-----------|------|---------|------|--------|

| Power voltage | VDD               | VSS=0     | -0.3 | 5.5     | V    |        |

| Input voltege | V <sub>in</sub> . |           | -0.3 | VDD+0.3 | V    | Note 1 |

Note1: /CS,/WR,/RD,RS,DB0~DB7

#### 4.1.2 Environmental Absolute max. ratings

|               | OPERATING |         | STOF           | RAGE |                 |

|---------------|-----------|---------|----------------|------|-----------------|

| Item          | MIN       | MAX     | MIN            | MAX  | Remark          |

| Temperature   | -20       | 70      | -30            | 80   | Note2,3,4,5,6,7 |

| Humidity      | No        | te1     | No             | te1  |                 |

| Corrosive Gas | Not Acc   | eptable | Not Acceptable |      |                 |

Note1: Ta <= 40°C: 85% RH max

Ta >  $40^{\circ}$ C : Absolute humidity must be lower than the humidity of 85%RH at  $40^{\circ}$ C

Note2 : For storage condition Ta at  $-30^{\circ}$ C < 48h , at  $80^{\circ}$ C < 100h For operating condition Ta at  $-20^{\circ}$ C < 100h

Note3: Background color changes slightly depending on ambient temperature. This phenomenon is reversible.

Note4: The response time will be slower at low temperature.

Note5 : Only operation is guarantied at operating temperature. Contrast , response time, another display quality are evaluated at +25°C

#### Note6:

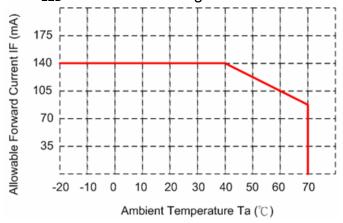

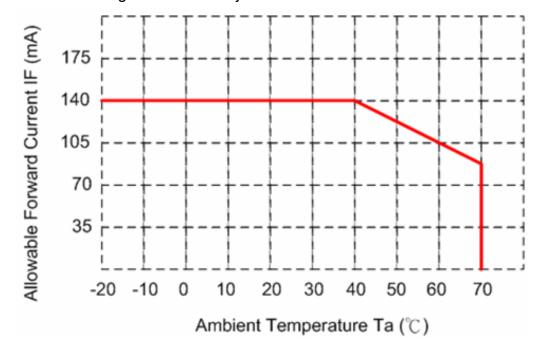

## LED BL: When LCM is operated over 40°C ambient temperature, the I<sub>LED</sub> of the LED back-light should be follow:

The contents of this document are confidential and must not be disclosed wholly or in part to any third part without the prior written consent of AMPIRE CO., LTD

Note7 : This is panel surface temperature, not ambient temperature. Note8 :

■ LED BL:When LCM be operated over than 40°C, the life time of the LED back-light will be reduced.

#### 4.1.3 LED back-light Unit Absolute max. ratings

| Item                 | Symbol | Ratings | Unit | Remark |

|----------------------|--------|---------|------|--------|

| Peak forward Current | IF     | 350     | mA   |        |

| Reverse Voltage      | VR     | 30      | V    |        |

| Power Dissipation    | Po     | 1.2     | W    |        |

#### 4.2 Electrical characteristics

#### 4.2.1 DC Electrical characteristic of the LCD

Typical operting conditions (VSS=0V)

| Item                        | `       | Symbol            | Min. | Тур. | Max. | Unit | Remark |

|-----------------------------|---------|-------------------|------|------|------|------|--------|

| Power supp                  | ly      | VDD               | 3.1  | 5.0  | 5.2  | V    |        |

| Input Voltage               | H Level | V <sub>IH</sub> . | 2.0  | -    | 5.5  | V    | Note 1 |

| for logic                   | L Level | V <sub>IL</sub>   | VSS  | ı    | 0.8  | V    | NOLE I |

| Output Voltage for<br>Logic | H Level | V <sub>OH</sub> . | 2.4  | 1    | VDD  | V    | Note 2 |

|                             | L Level | V <sub>OL</sub>   | VSS  |      | 0.4  | V    | Note 2 |

| Power Supply current        |         | IDD               | -    | 150  | -    | mA   | Note 3 |

Note1: With 5V Tolerance Input, /CS, /WR,/RD,RS,DB0~DB17

Note2: DB0~DB17

Note3: fV = 60Hz, Ta = 25°C, VDD = 3.3V, DCLK = 10MHz, PLL frequency = 40MHz,

Display pattern : All Black

Date: 2008/4/29 AMPIRE CO., LTD.

6

The contents of this document are confidential and must not be disclosed wholly or in part to any third part without the prior written consent of AMPIRE CO., LTD

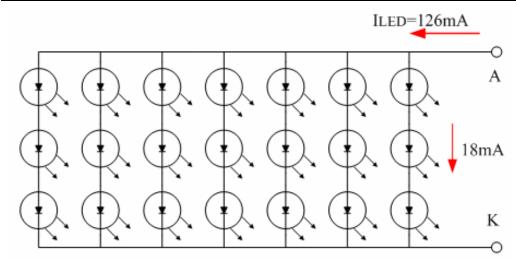

4.2.2 Electrical characteristic of LED Back-light

| Paramenter          | Symbol           | Min. | Тур.                                    | Max. | Unit | Condiction     |                  |

|---------------------|------------------|------|-----------------------------------------|------|------|----------------|------------------|

| LED walters         |                  |      | .,   ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | 10.5 | 40   |                | I <sub>LED</sub> |

| LED voltage         | V <sub>AK</sub>  |      | 10.5   12                               | 12   | V    | =140mA,Ta=25°C |                  |

| LED forward ourrent | I <sub>LED</sub> |      | 126                                     | 140  | mA   | Ta=25°C        |                  |

| LED forward current | I <sub>LED</sub> |      | 84                                      | 105  | mA   | Ta=60°C        |                  |

■ The constant current source is needed for white LED back-light driving.

When LCM is operated over 60°C ambient temperature, the I<sub>LED</sub> of the LED

## 3.3 AC Timing characteristic of the Graphic TFT LCD controller

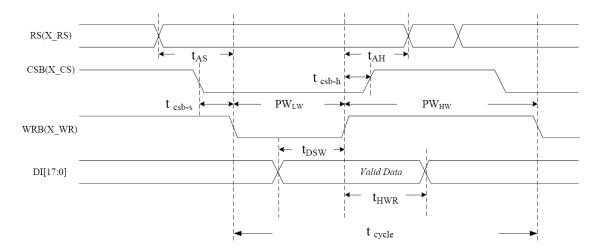

## 4.3 80 series Timing

| Symbol       | Parameter                     | Min | Тур | Max | Unit | Remark |

|--------------|-------------------------------|-----|-----|-----|------|--------|

| tcycle       | Enable cycle time             | 100 | 200 |     | ns   |        |

| <b>PW</b> HW | Enable high-level pulse width | 66  | 70  |     | ns   |        |

| <b>PW</b> LW | Enable low-level pulse width  | 33  | 130 |     | ns   |        |

| tas          | RS setup time                 | 16  | 25  |     | ns   |        |

| tan          | RS hold time                  | 16  | 45  |     | ns   |        |

| tosw         | Write data setup time         | 50  | 50  |     | ns   |        |

| thwr         | Write data hold time          | 50  | 40  |     | ns   |        |

| tcsb-s       | CSB setup time                | 16  | 20  |     | ns   |        |

| tcsb-h       | CSB hold time                 | 16  | 30  |     | ns   |        |

The contents of this document are confidential and must not be disclosed wholly or in part to any third part without the prior written consent of AMPIRE CO., LTD

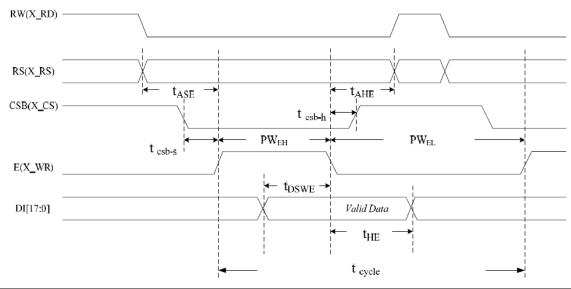

## 4.4 68eries Timing

| Symbol       | Parameter                     | Min | Тур | Max | Unit | Remark |

|--------------|-------------------------------|-----|-----|-----|------|--------|

| tcycle       | Enable cycle time             | 100 | 200 |     | ns   |        |

| <b>PW</b> EH | Enable high-level pulse width | 66  | 70  |     | ns   |        |

| PWEL         | Enable low level pulse width  | 33  | 130 |     | ns   |        |

| tase         | RS setup time                 | 16  | 25  |     | ns   |        |

| <b>t</b> AHE | RS hold time                  | 16  | 45  |     | ns   |        |

| toswe        | Write data setup time         | 50  | 50  |     | ns   |        |

| the          | Write data hold time          | 50  | 40  |     | ns   |        |

| tcsb-s       | CSB setup time                | 16  | 20  |     | ns   |        |

| tcsbh        | CSB hold time                 | 16  | 30  |     | ns   |        |

## 5 Optical specification

## 5.1 Optical characteristic:

| Item                                 |                   | Symbol            | Conditon                                 | Min.                 | Тур.                 | Max.        | Unit              | Remark                  |

|--------------------------------------|-------------------|-------------------|------------------------------------------|----------------------|----------------------|-------------|-------------------|-------------------------|

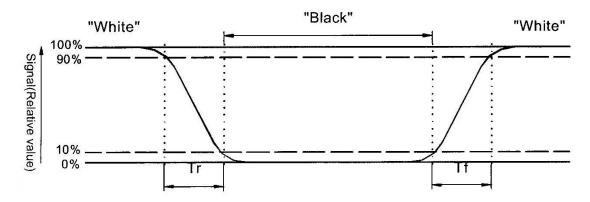

| Response                             | Rise              | T <sub>r</sub> .  | Θ=0°                                     | -                    | 15                   | 30          | ms                | Note 1,2,3,5            |

| Time                                 | Fall              | T <sub>f</sub>    |                                          | -                    | 35                   | 50          | ms                | 14010 1,2,3,3           |

| Contrast i                           | atio              | CR                | At optimized viewing angle               | 200                  | 350                  | -           |                   | Note 1,2,4,5            |

| Viewing Angle Top Botto m Left Right |                   |                   | CR≧10                                    | 55<br>45<br>55<br>55 | 60<br>50<br>60<br>60 | -<br>-<br>- | deg.              | Note1,2, 5,6            |

| Brightness<br>LED BL<br>Without TP   |                   | Y <sub>-L</sub>   | $I_{LED}$ =126mA, $25^{\circ}\mathbb{C}$ | 427.5                | 450                  | -           | cd/m <sup>2</sup> | Note 7                  |

|                                      |                   | I . <u>L</u> .    | $I_{LED}$ =140mA, $25^{\circ}$ C         | 475                  | 500                  | -           | cd/m <sup>2</sup> |                         |

| Brightne<br>LED B                    |                   | Y <sub>-L</sub> . | I <sub>LED</sub> =126mA, $25^{\circ}$ ℂ  | 342                  | 360                  | -           | cd/m <sup>2</sup> | Note 7                  |

| With Ti                              |                   | I .L.             | I <sub>LED</sub> =140mA, $25$ °C         | 380                  | 400                  | -           | cd/m <sup>2</sup> |                         |

| Pod chrom                            | aticity           | XR                |                                          | 0.610                | 0.640                | 0.670       |                   | Note 7                  |

| Red chrom                            | alicity           | YR                |                                          | 0.314                | 0.344                | 0.374       |                   | Note 7                  |

| Croop obrop                          | acticity.         | XG                |                                          | 0.268                | 0.298                | 0.328       |                   | For reference           |

| Green chromaticity                   |                   | YG                | Θ=0°                                     | 0.553                | 0.583                | 0.613       |                   | only. These             |

| Dlug obromoticity                    |                   | Хв                | Θ=0°                                     | 0.102                | 0.132                | 0.162       |                   | data should             |

| blue chiforn                         | Blue chromaticity |                   |                                          | 0.107                | 0.137                | 0.167       |                   | be update according the |

| \M\bito obron                        | acticity          | XW                |                                          | 0.282                | 0.312                | 0.342       |                   | prototype.              |

| White chron                          | ialicity          | YW                |                                          | 0.299                | 0.329                | 0.359       |                   | prototype.              |

( )For reference only. These data should be update according the prototype.

#### Note 1:

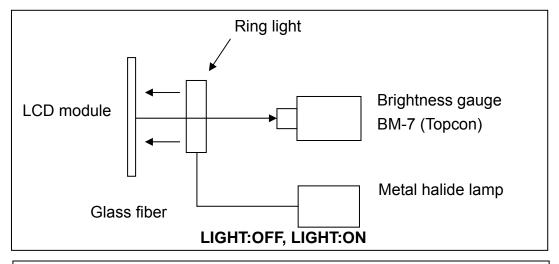

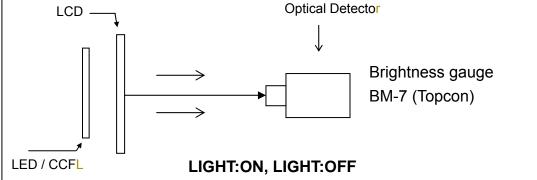

- LED BL :Ambient temperature=25<sup>o</sup>C, and lamp current I<sub>LED</sub>=140mA. To be measured in the dark room.

- CCFL BL: Ambient temperature=25<sup>o</sup>C, and lamp current I<sub>L</sub>=6 mArms. To be measured in the dark room.

Note 2:To be measured on the center area of panel with a viewing cone of 1°by Topcon luminance meter BM-7,after 10 minutes operation.

#### Note 3. Definition of response time:

The output signals of photo detector are measured when the input signals are changed from "black" to "white" (falling time) and from "white" to "black" (rising time), respectively. The response time is defined as the time interval between the 10% and 90% of amplitudes. Refer to figure as below.

The contents of this document are confidential and must not be disclosed wholly or in part to any third part without the prior written consent of AMPIRE CO., LTD

Note 4. Definition of contrast ratio:

Contrast ratio is calculated with the following formula.

Note 5:White

$$V_i=V_{i50}+1.5V$$

Black  $V_i=V_{i50}+2.0V$

Date: 2008/4/29

"±"means that the analog input signal swings in phase with V<sub>сом</sub> signal.

$V_{\text{i50}}$ : The analog input voltage when transmission is 50%. The 100% Transmission is defined as the transmission of LCD panel when all the Input terminals of module are electrically opened.

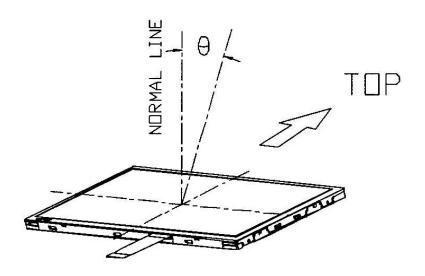

Note 6.Definition of viewing angle, Refer to figure as below.

<sup>&</sup>quot;- " means that the analog input signal swings out of phase with  $V_{\text{COM}}$  signal.

Note 7.Measured at the center area of the panel when all the input terminals of LCD panel are electrically opened.

The contents of this document are confidential and must not be disclosed wholly or in part to any third part without the prior written consent of AMPIRE CO., LTD

## 5.2 Optical characteristic of the LED Back-light

| ITEM                  | MIN  | TYP  | MAX  | UNIT  | Condition                       |

|-----------------------|------|------|------|-------|---------------------------------|

| Bare Brightness       | 3500 | 1    |      | Cd/m2 | I <sub>LED</sub> =140mA,Ta=25°C |

| AVG. X of 1931 C.I.E. | 0.28 | 0.31 | 0.34 |       | I <sub>LED</sub> =140mA,Ta=25°C |

| AVG. X of 1931 C.I.E. | 0.28 | 0.31 | 0.34 |       | I <sub>LED</sub> =140mA,Ta=25°C |

| Brightness Uniformity | 80   | 1    |      | %     | I <sub>LED</sub> =140mA,Ta=25°C |

<sup>( )</sup>For reference only. These data should be update according the prototype.

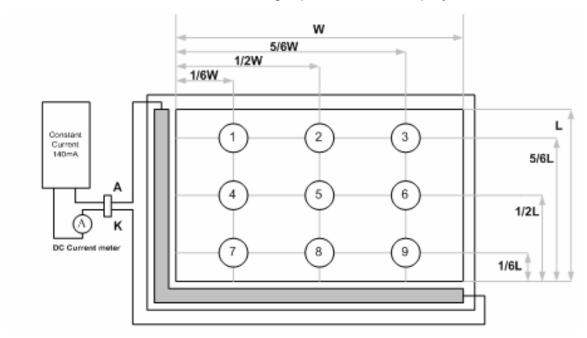

Note1 : Measurement after 10 minutes from LED BL operating.

Note2: Measurement of the following 9 places on the display.

Note3: The Uniformity definition

Date: 2008/4/29

(Min Brightness / Max Brightness) x 100%

The contents of this document are confidential and must not be disclosed wholly or in part to any third part without the prior written consent of AMPIRE CO., LTD

## 5.3 Touch Panel Electrical Specification

| Parameter             | Condition | Standard Value        |  |  |  |  |  |

|-----------------------|-----------|-----------------------|--|--|--|--|--|

| Terminal Resistance   | X Axis    | 400 ~ 900 Ω           |  |  |  |  |  |

| Terminal Resistance   | Y Axis    | 200 ~ 500 Ω           |  |  |  |  |  |

| Insulating Resistance | DC 25 V   | More than $10M\Omega$ |  |  |  |  |  |

| Linearity             |           | ±1.5 %                |  |  |  |  |  |

| Notes life by Pen     | Note a    | 100,000 times(min)    |  |  |  |  |  |

| Input life by finger  | Note b    | 1,000,000 times (min) |  |  |  |  |  |

#### Note A.

Notes area for pen notes life test is 10 x 9 mm.

Size of word is 7.5 x 6.72 Shape of pen end : R0.8

Load: 250 g

Note B

By Silicon rubber tapping at same point

Shape of rubber end: R8

Load: 200g

Frequency: 5 Hz

Date: 2008/4/29

#### Interface

| No. | Symbol | Function                           |

|-----|--------|------------------------------------|

| 1   | XR     | Touch Panel Right Signal in X Axis |

| 2   | YU     | Touch Panel Upper Signal in Y Axis |

| 3   | XL     | Touch Panel Left Signal in X Axis  |

| 4   | YL     | Touch Panel Low Signal in Y Axis   |

The contents of this document are confidential and must not be disclosed wholly or in part to any third part without the prior written consent of AMPIRE CO., LTD

## 6 Interface specifications

## 6.1 Driving signals for the TFT panel

## 6.1.1 24pin FFC connector ( Without for reference only)

(Suitable ZIF connector)

| Pin no | Symbol   | I/O | Description                                           | Remark |

|--------|----------|-----|-------------------------------------------------------|--------|

| 1      | /RESET   | -   | Reset signal for TFT LCD controller                   |        |

| 2      | /RD(R/W) | ı   | 80mode : /RD low active signal for TFT LCD controller |        |

|        | /KD(K/W) | ı   | 68mode : R/W signal Hi: read Lo:Write                 |        |

| 3      | /WR(E)   | 1   | 80mode : /WR low active signal for TFT LCD controller |        |

|        |          | '   | 68mode : E signal latch on rising edge                |        |

| 4      | /CS      |     | Chip select low active signal for TFT LCD controller  |        |

| 5      | RS       |     | Register and Data select for TFT LCD controller       |        |

| 6      | DB0      |     | Data Bus                                              |        |

| 7      | DB1      | I/O | Data Bus                                              |        |

| 8      | DB2      | I/O | Data Bus                                              |        |

| 9      | DB3      | I/O | Data Bus                                              |        |

| 10     | DB4      | I/O | Data Bus                                              |        |

| 11     | DB5      | I/O | Data Bus                                              |        |

| 12     | DB6      | I/O | Data Bus                                              |        |

| 13     | DB7      | I/O | Data Bus                                              |        |

| 14     | VDD      | ı   | Power supply for the logic (3.3V)                     |        |

| 15     | VSS      | ı   | GND                                                   |        |

| 16     | NC       | ı   | No connection                                         |        |

| 17     | NC       | ı   | No connection                                         |        |

| 18     | SK/X1    |     | Serial clock for Touch panel controller               |        |

|        | SIVAT    | -   | Touch Panel Left Signal in X Axis                     |        |

| 19     | DO/X2    | _   | Data Output for Touch panel controller                |        |

|        | DOIAZ    |     | Touch Panel Right Signal in X Axis                    |        |

| 20     | DI/Y1    | _   | Data In for Touch panel controller                    |        |

|        |          |     | Touch Panel Upper Signal in Y Axis                    |        |

| 21     | TPCS /   | _   | Chip Select for Touch panel controller                |        |

|        | Y2       | _   | Touch Panel Lower Signal in X Axis                    |        |

| 22     | INT      | -   | Interrupt for Touch panel controller                  |        |

| 23     | NC       | -   | No connection                                         |        |

| 24     | NC       | -   | No connection                                         |        |

18~22 : SK, DO, DI, CS, INT for Touch Panel controller TSC2046

/ X1, X2, Y1, Y2 for Touch Panel (without TSC2046)

The contents of this document are confidential and must not be disclosed wholly or in part to any third part without the prior written consent of AMPIRE CO., LTD

## 6.1.234pin PIN Header

| Pin no | Symbol                                                      | Description                                          |  |  |  |  |

|--------|-------------------------------------------------------------|------------------------------------------------------|--|--|--|--|

| 1      | /RESET                                                      | Reset signal for TFT LCD controller                  |  |  |  |  |

| 3      | /RD(R/W)                                                    | 80mode: /RD low active signal for TFT LCD controller |  |  |  |  |

|        | /KD(K/W)                                                    | 68mode : R/W signal Hi: read Lo:Write                |  |  |  |  |

| 5      | /WR(E) 80mode: /WR low active signal for TFT LCD controller |                                                      |  |  |  |  |

|        | /VVIX(L)                                                    | 68mode : E signal latch on rising edge               |  |  |  |  |

| 7      | /CS                                                         | Chip select low active signal for TFT LCD controller |  |  |  |  |

| 9      | RS                                                          | Register and Data select for TFT LCD controller      |  |  |  |  |

| 11     | DB0                                                         | Data Bus                                             |  |  |  |  |

| 13     | DB1                                                         | Data Bus                                             |  |  |  |  |

| 15     | DB2                                                         | Data Bus                                             |  |  |  |  |

| 17     | DB3                                                         | Data Bus                                             |  |  |  |  |

| 19     | DB4                                                         | Data Bus                                             |  |  |  |  |

| 21     | DB5                                                         | Data Bus                                             |  |  |  |  |

| 23     | DB6                                                         | Data Bus                                             |  |  |  |  |

| 25     | DB7                                                         | Data Bus                                             |  |  |  |  |

| 27     | VDD                                                         | Power supply for the logic (3.3V)                    |  |  |  |  |

| 29     | VDD                                                         | Power supply for the logic (3.3V)                    |  |  |  |  |

| 31     | VSS                                                         | GND                                                  |  |  |  |  |

| 33     | VSS                                                         | GND                                                  |  |  |  |  |

| Pin no | Symbol    | Description                             |

|--------|-----------|-----------------------------------------|

| 2      | SK/X1     | Serial clock for Touch panel controller |

|        |           | Touch Panel Left Signal in X Axis       |

| 4      | DO/X2     | Data Output for Touch panel controller  |

|        |           | Touch Panel Right Signal in X Axis      |

| 6      | DI / Y1   | Data In for Touch panel controller      |

|        | D17 1 1   | Touch Panel Upper Signal in Y Axis      |

| 8      | TPCS / Y2 | Chip Select for Touch panel controller  |

|        |           | Touch Panel Lower Signal in X Axis      |

| 10     | INT       | Interrupt for Touch panel controller    |

| 12     | DB8       | Data Bus                                |

| 14     | DB9       | Data Bus                                |

| 16     | DB10      | Data Bus                                |

| 18     | DB11      | Data Bus                                |

| 20     | DB12      | Data Bus                                |

| 22     | DB13      | Data Bus                                |

| 24     | DB14      | Data Bus                                |

| 26     | DB15      | Data Bus                                |

| 28     | DB16      | Data Bus                                |

| 30     | DB17      | Data Bus                                |

| 32     | NC        | No connection                           |

| 34     | NC        | No connection                           |

Pni No 2,4,6,8: SK, DO, DI, CS, INT for Touch Panel controller TSC2046

/ X1, X2, Y1, Y2 for Touch Panel (without TSC2046)

Date: 2008/4/29 AMPIRE CO., LTD. 16

The contents of this document are confidential and must not be disclosed wholly or in part to any third part without the prior written consent of AMPIRE CO., LTD

## **Driving signals for the back-light**

## 6.1.3 LED Back-light

JST Housing: BHR-03VS-1

| Pin no | Symbol | Level | Description   | Remark |

|--------|--------|-------|---------------|--------|

| 1      | Α      | -     | LED Anode     |        |

| 2      | NC     | -     | No connection |        |

| 3      | K      | -     | LED Cathode   |        |

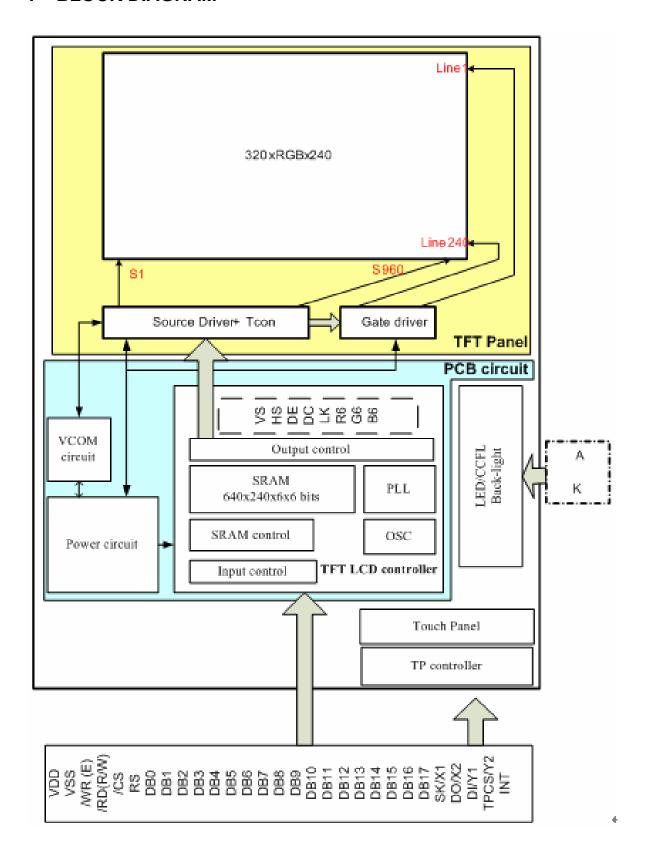

## 7 BLOCK DIAGRAM

The contents of this document are confidential and must not be disclosed wholly or in part to any third part without the prior written consent of AMPIRE CO., LTD

#### 8 Interface Protocol

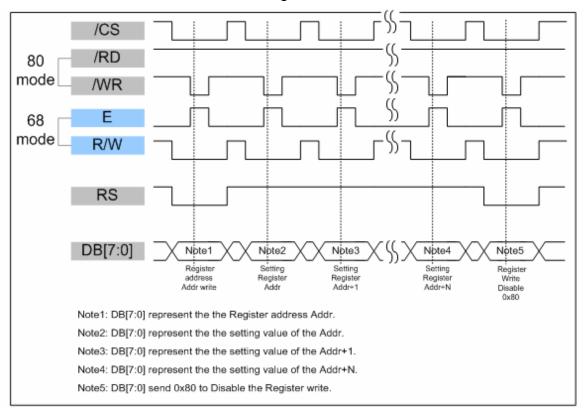

#### 8.1 8Bit-80/68- Write to Command Register

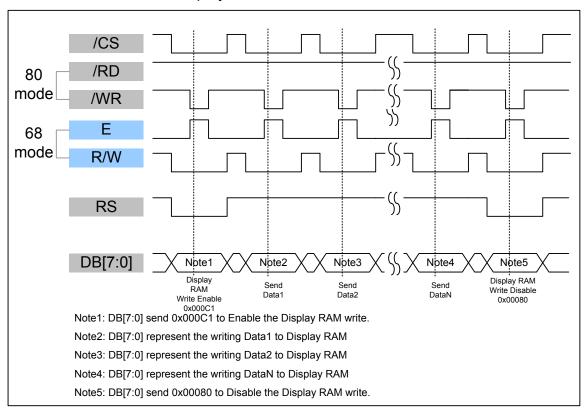

#### 8.2 8Bit-80/68-Write to Display RAM

The contents of this document are confidential and must not be disclosed wholly or in part to any third part without the prior written consent of AMPIRE CO., LTD

## 8.3 Data transfer order Setting

## 8.3.1 bit interface 65K color (JP2 1,2 short 65K/262K =Low)

| DB                   | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|----------------------|----|----|----|----|----|----|---|---|----|----|----|----|----|----|----|----|

| 1.st data            | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Х | Х | R4 | R3 | R2 | R1 | R0 | G5 | G4 | G3 |

| 2 <sup>nd</sup> data | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ | Χ | G2 | G1 | G0 | B4 | В3 | B2 | B1 | B0 |

## 8.3.28 bit interface 262K color (JP2 2,3 short 65K/262K =High)

| DB                      | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-------------------------|----|----|----|----|----|----|---|---|----|----|----|----|----|----|----|----|

| 1.st data               | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ | Χ |    |    |    |    |    |    | R5 | R4 |

| 2 <sup>nd</sup> data    | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ | Χ | R3 | R2 | R1 | R0 | G5 | G4 | G3 | G2 |

| 3. <sup>rd</sup> . data | Х  | Х  | Χ  | Χ  | Х  | Χ  | Х | Х | G1 | G0 | B5 | B4 | B3 | B2 | B1 | B0 |

The contents of this document are confidential and must not be disclosed wholly or in part to any third part without the prior written consent of AMPIRE CO., LTD

## 9 Register Depiction

| Register<br>Address<br>(Hex) | Default<br>(Hex)                                       | DB7       | DB6                                            | DB5       | DB4       | DB3      | DB2      | DB1   | DB0 | Remark |  |

|------------------------------|--------------------------------------------------------|-----------|------------------------------------------------|-----------|-----------|----------|----------|-------|-----|--------|--|

| 00                           | 00                                                     |           | <u> </u>                                       | MSB of    | X-axis    | start p  | osition  | )     |     |        |  |

| Description                  | set the ho                                             | orizonta  |                                                |           |           |          |          |       | l   |        |  |

| Register<br>Address<br>(Hex) | Default<br>(Hex)                                       | DB7       | DB6                                            | DB5       | DB4       | DB3      | DB2      | DB1   | DB0 | Remark |  |

| 01                           | 00                                                     |           |                                                | LSB of    | X-axis    | start p  | osition  |       |     |        |  |

| Description                  | set the ho                                             | orizonta  | ıls star                                       | t positio | on of di  | isplay a | active r | egion |     |        |  |

| Register<br>Address<br>(Hex) | Default<br>(Hex)                                       | DB7       | DB6                                            | DB5       | DB4       | DB3      | DB2      | DB1   | DB0 | Remark |  |

| 02                           | 01                                                     |           |                                                | MSB o     | f X-axis  | s end p  | osition  | •     |     |        |  |

| Description                  | set the ho                                             | rizonta   | izontals end position of display active region |           |           |          |          |       |     |        |  |

| Register<br>Address<br>(Hex) | Default<br>(Hex)                                       | DB7       | DB6                                            | DB5       | DB4       | DB3      | DB2      | DB1   | DB0 | Remark |  |

| 03                           | 3F                                                     |           |                                                | LSB of    | X-axis    | end p    | osition  |       |     |        |  |

| Description                  | set the ho                                             | rizonta   | ls end                                         | positio   | n of dis  | splay a  | ctive re | egion |     |        |  |

| Register<br>Address<br>(Hex) | Default<br>(Hex)                                       | DB7       | DB6                                            | DB5       | DB4       | DB3      | DB2      | DB1   | DB0 | Remark |  |

| 04                           | 00                                                     |           | 1                                              | MSB of    | Y-axis    | start p  | osition  | ]     |     |        |  |

| Description                  | set the ve                                             | ertical s |                                                |           |           |          |          |       | Į.  |        |  |

| Register<br>Address<br>(Hex) | Default<br>(Hex)                                       | DB7       | DB6                                            | DB5       | DB4       | DB3      | DB2      | DB1   | DB0 | Remark |  |

| 05                           | 00                                                     |           |                                                | LSB of    | Y-axis    | start p  | osition  |       |     |        |  |

| Description                  | Set the ve                                             | ertical s | tart po                                        | sition c  | of displa | ay activ | ve regio | on    |     |        |  |

| Register<br>Address<br>(Hex) | Default<br>(Hex)                                       | DB7       | DB6                                            | DB5       | DB4       | DB3      | DB2      | DB1   | DB0 | Remark |  |

| 06                           | 00                                                     |           | I                                              | MSB o     | f Y-axis  | s end p  | osition  |       |     |        |  |

| Description                  | set the ve                                             | ertical e | nd pos                                         | ition of  | displa    | y active | e regio  | n     |     |        |  |

| Register<br>Address<br>(Hex) | Default<br>(Hex)                                       | DB7       | DB6                                            | DB5       | DB4       | DB3      | DB2      | DB1   | DB0 | Remark |  |

| 07                           | EF                                                     |           |                                                |           |           |          |          |       |     |        |  |

| Description                  | Set the vertical end position of display active region |           |                                                |           |           |          |          |       |     |        |  |

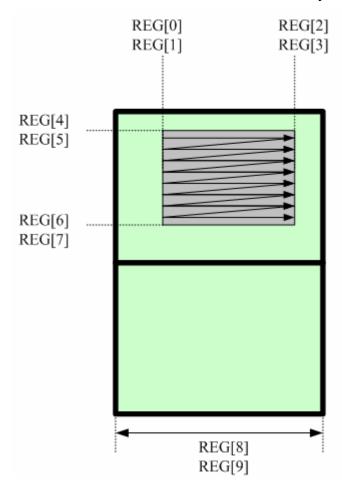

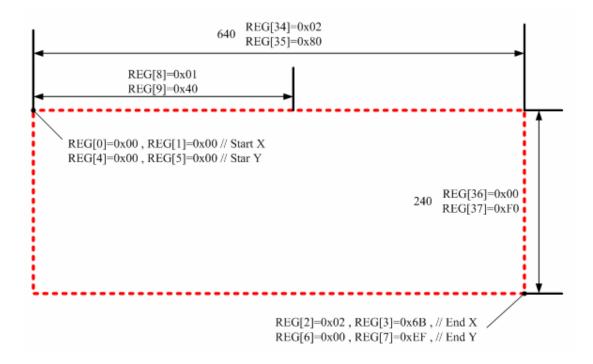

To simplify the address control of display RAM access, the window area address function

allows for writing data only within a window area of display RAM specified by registers REG[00]~REG[07].

The contents of this document are confidential and must not be disclosed wholly or in part to any third part without the prior written consent of AMPIRE CO., LTD

After writing data to the display RAM, the Address counter will be increased within setting window address-range which is specified by

MIN X address (REG[0] & REG[1])

MAX X address (REG[2] & REG[3])

MIN Y address (REG[4] & REG[5])

MAX Y address (REG[6] & REG[7])

Therefore, data can be written consecutively without thinking the data address.

| Register<br>Address<br>(Hex) | Default<br>(Hex) | DB7    | DB6  | DB5  | DB4     | DB3     | DB2      | DB1 | DB0               | Remark |

|------------------------------|------------------|--------|------|------|---------|---------|----------|-----|-------------------|--------|

| 08                           | 01               | Х      | X    | Χ    | Х       | Х       | Х        | _   | IXSize<br>te[1:0] |        |

| Description                  | Set the p        | anel X | size |      |         |         |          |     |                   |        |

| Register<br>Address<br>(Hex) | Default<br>(Hex) | DB7    | DB6  | DB5  | DB4     | DB3     | DB2      | DB1 | DB0               | Remark |

| 09                           | 40               |        |      | _Par | nelXSiz | ze L_By | /te[7:0] |     |                   |        |

| Description                  | Set the p        | anel X | size |      |         |         |          |     |                   |        |

The contents of this document are confidential and must not be disclosed wholly or in part to any third part without the prior written consent of AMPIRE CO., LTD

The register REG[08] and REG[09] is use to calculate the RAM address. If you want to use the TFT as Landscape mode (320x240), the REG[08] & RGE[09] must set to 320. If you want to use the TFT as Portrait mode (240x320), the REG[08] & RGE[09] must set to 240.

| Register<br>Address<br>(Hex) | Default<br>(Hex) | DB7                      | DB6     | DB5     | DB4   | DB3       | DB2      | DB1                             | DB0     | Remark |

|------------------------------|------------------|--------------------------|---------|---------|-------|-----------|----------|---------------------------------|---------|--------|

| 0A                           | 00               | X                        | X       | X       | X     | X         | memo     | :16] bit<br>ory writ<br>addres: | e start |        |

| Description                  | Memory           | write st                 | art add | Iress   |       |           |          |                                 |         |        |

| Register<br>Address<br>(Hex) | Default<br>(Hex) | DB7                      | DB6     | DB5     | DB4   | DB3       | DB2      | DB1                             | DB0     | Remark |

| 0B                           | 00               |                          | [15:8]  | bits of | memo  | ry write  | start a  | ddress                          |         |        |

| Description                  | Memory           | write st                 | art add | Iress   |       |           |          |                                 |         |        |

| Register<br>Address<br>(Hex) | Default<br>(Hex) | DB7                      | DB6     | DB5     | DB4   | DB3       | DB2      | DB1                             | DB0     | Remark |

| 0C                           | 00               |                          | [7:0]   | bits of | memor | y write s | start ac | ldress                          |         |        |

| Description                  | Memory           | nory write start address |         |         |       |           |          |                                 |         |        |

| Register<br>Address<br>(Hex) | Default<br>(Hex)                                                                                                                                    | DB7                                                                                                                                           | DB6                                                                                                                                                        | DB5                                                                             | DB4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DB3                       | DB2      | DB1     | DB0       | Remark |  |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|----------|---------|-----------|--------|--|

| 0x10                         | 0x0D                                                                                                                                                | Bit_SWAP                                                                                                                                      | OUT_TEST                                                                                                                                                   | BUS                                                                             | _SEL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Blanking                  | P/S_SEL  | CLK.    | _SEL      |        |  |

| Description                  | "0x10_C<br>are for s<br>00 : 20M<br>"0x10_p<br>interface<br>0 : seria<br>"0x10_b<br>0 : OFF<br>"0x10_b<br>00=R, C<br>"0x10_o<br>0 : norm<br>When se | clk_sel[1:<br>elect the<br>flhz 01: 1<br>s_sel[2]"<br>e. These<br>I Panel 1<br>lanking_t<br>(blanking<br>us_sel[5:<br>01=G, 10<br>out_test[6] | O]": The T<br>TFT pane<br>OMhz 02:<br>The TFT<br>bits are for<br>Parallel p<br>mp[3]"<br>D) 1: ON (<br>A]": It only<br>D=B<br>J": Self test<br>to "1", the | FT con<br>I dot c<br>5 Mhz<br>contro<br>r select<br>panel<br>normal<br>y for se | ontroller subtended to the operation of | pport paut timetion) anel | 40Mhz I  | PLL clo | ock. Th   |        |  |

|                              | "0x10_bit_swap[7]" : 0-normal The default setting is suitable for AM320240N1. Don't need to modify it.                                              |                                                                                                                                               |                                                                                                                                                            |                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                           |          |         |           |        |  |

|                              | The defa                                                                                                                                            | ault setting                                                                                                                                  | g is suitabl                                                                                                                                               | e for A                                                                         | M3202                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <u>40N1. D</u>            | on't nee | d to mo | odify it. |        |  |

The contents of this document are confidential and must not be disclosed wholly or in part to any third part without the prior written consent of AMPIRE CO., LTD

| Register<br>Address<br>(Hex) | Default<br>(Hex)                                                                                                                           | DB7                                             | DB6        | DB5    | DB4    | DB3 | DB2       | DB1  | DB0     | Remark |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|------------|--------|--------|-----|-----------|------|---------|--------|

| 0x11                         | 00                                                                                                                                         | Х                                               | Х          |        | EVEN   |     |           | _ODD |         |        |

| Description                  | " Even lii panel 000: RG 001: GR 011: GB 100: RG 001: GR 011: GB 100: GR 011: GB 100: BR 011: GB 100: BR 011: GB 100: BR 011: BG 0thers: I | B G R Geserved of serial   B G B R G R Teserved | panel data | out se | quence |     | ata bus o |      | paralle | el     |

| Register<br>Address<br>(Hex) | Default<br>(Hex)                  | DB7                                                                                                                          | DB6     | DB5  | DB4    | DB3   | DB2    | DB1         | DB0     | Remark     |  |

|------------------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------|---------|------|--------|-------|--------|-------------|---------|------------|--|

| 0x12                         | 00                                |                                                                                                                              |         |      |        | Hsy   | nc_st⊦ | I_Byte      | [3:0]   |            |  |

| Description                  | For TFT of Hsync start The defail | art posi                                                                                                                     | tion H- | Byte | for AM | 32024 | 0N1. D | on't ne     | ed to n | nodify it. |  |

| Register<br>Address<br>(Hex) | Default<br>(Hex)                  | DB7                                                                                                                          | DB6     | DB5  | DB4    | DB3   | DB2    | DB1         | DB0     | Remark     |  |

| 0x13                         | 00                                |                                                                                                                              |         | Hsy  | nc_stL | _Byte | 7:0]   |             |         |            |  |

| Description                  | Hsync sta                         | output timing adjust: art position L-Byte jult setting is suitable for AM320240N1. Don't need to modify it.                  |         |      |        |       |        |             |         |            |  |

| Register<br>Address<br>(Hex) | Default<br>(Hex)                  | DB7                                                                                                                          | DB6     | DB5  | DB4    | DB3   | DB2    | DB1         | DB0     | Remark     |  |

| 0x14                         | 00                                |                                                                                                                              |         |      |        | Hsyr  | nc_pwl | -<br>I_Byte | [3:0]   |            |  |

| Description                  | Hsync pu                          | or TFT output timing adjust: sync pulse width H-Byte he default setting is suitable for AM320240N1. Don't need to modify it. |         |      |        |       |        |             |         |            |  |

| Register<br>Address<br>(Hex) | Default<br>(Hex)                  | DB7                                                                                                                          | DB6     | DB5  | DB4    | DB3   | DB2    | DB1         | DB0     | Remark     |  |

| 0x15                         | 10                                |                                                                                                                              |         | Hsyr | nc_pwl | Byte  | [7:0]  |             |         |            |  |

The contents of this document are confidential and must not be disclosed wholly or in part to any third part without the prior written consent of AMPIRE CO. LTD.

| to any third p               | <u>art without</u>                                                                                                             | the pri                                                                                                                               | <u>or writ</u> | ten con     | sent of | <u>AMPIF</u> | <u>RE CO.</u> | <u>, LTD</u> |         |            |  |  |  |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------|---------|--------------|---------------|--------------|---------|------------|--|--|--|

| Description                  | For TFT of Hsync pu                                                                                                            | lse wid                                                                                                                               | th L-Bی        | yt <b>é</b> | for AM  | 32024        | 0N1. D        | on't ne      | ed to n | nodify it. |  |  |  |

| Register<br>Address<br>(Hex) | Default<br>(Hex)                                                                                                               | DB7                                                                                                                                   | DB6            | DB5         | DB4     | DB3          | DB2           | DB1          | DB0     | Remark     |  |  |  |

| 0x16                         | 00                                                                                                                             |                                                                                                                                       |                |             |         | Had          | ct_stH        | Byte[        | 3:0]    |            |  |  |  |

| Description                  | DE pulse                                                                                                                       | For TFT output timing adjust: DE pulse start position H-Byte The default setting is suitable for AM320240N1. Don't need to modify it. |                |             |         |              |               |              |         |            |  |  |  |

| Register<br>Address<br>(Hex) | Default<br>(Hex)                                                                                                               | DB7                                                                                                                                   | DB6            | DB5         | DB4     | DB3          | DB2           | DB1          | DB0     | Remark     |  |  |  |

| 0x17                         | 38                                                                                                                             | J J J J                                                                                                                               |                |             |         |              |               |              |         |            |  |  |  |

| Description                  | DE pulse                                                                                                                       | For TFT output timing adjust: DE pulse start position L-Byte The default setting is suitable for AM320240N1. Don't need to modify it. |                |             |         |              |               |              |         |            |  |  |  |

| Register<br>Address<br>(Hex) | Default<br>(Hex)                                                                                                               | DB7                                                                                                                                   | DB6            | DB5         | DB4     | DB3          | DB2           | DB1          | DB0     | Remark     |  |  |  |

| 0x18                         | 01                                                                                                                             |                                                                                                                                       |                |             |         | Hac          | t_pwH         | _Byte        | 3:0]    |            |  |  |  |

| Description                  | For TFT of DE pulse The defail                                                                                                 | width I                                                                                                                               | H-Byte         |             | for AM  | 32024        | 0N1. D        | on't ne      | ed to n | nodify it. |  |  |  |

| Register<br>Address<br>(Hex) | Default<br>(Hex)                                                                                                               | DB7                                                                                                                                   | DB6            | DB5         | DB4     | DB3          | DB2           | DB1          | DB0     | Remark     |  |  |  |

| 0x19                         | 40                                                                                                                             |                                                                                                                                       |                |             | t_pwL   | _Byte[       | 7:0]          | -            |         |            |  |  |  |

| Description                  | For TFT output timing adjust:  DE pulse width L-Byte  The default setting is suitable for AM320240N1. Don't need to modify it. |                                                                                                                                       |                |             |         |              |               |              |         |            |  |  |  |

| Register<br>Address<br>(Hex) | Default<br>(Hex)                                                                                                                 | DB7     | DB6    | DB5 | DB4    | DB3   | DB2    | DB1     | DB0     | Remark     |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------|---------|--------|-----|--------|-------|--------|---------|---------|------------|

| 0x1A                         | 01                                                                                                                               |         |        |     |        | Ht    | otalH_ | Byte[3  | :0]     |            |

| Description                  | For TFT of Hsync tot The defar                                                                                                   | al cloc | ks H-B | yte | for AM | 32024 | 0N1. D | on't ne | ed to n | nodify it. |

| Register<br>Address<br>(Hex) | Default<br>(Hex)                                                                                                                 | DB7     | DB6    | DB5 | DB4    | DB3   | DB2    | DB1     | DB0     | Remark     |

| 0x1B                         | B8 HtotalL Byte[7:0]                                                                                                             |         |        |     |        |       |        |         |         |            |

| Description                  | For TFT output timing adjust: Hsync total clocks H-Byte The default setting is suitable for AM320240N1. Don't need to modify it. |         |        |     |        |       |        |         |         |            |

The contents of this document are confidential and must not be disclosed wholly or in part to any third part without the prior written consent of AMPIRE CO., LTD

| to any time p                | art without                                                                                                                                    | the pri  | OI WIII  | ten con | SCIII OI | AWII II | LE CO.       | , LID   |         |            |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|---------|----------|---------|--------------|---------|---------|------------|

| Register<br>Address<br>(Hex) | Default<br>(Hex)                                                                                                                               | DB7      | DB6      | DB5     | DB4      | DB3     | DB2          | DB1     | DB0     | Remark     |

| 0x1C                         | 00                                                                                                                                             |          |          |         |          | Vsv     | nc_stH       | Bvte    | [3:0]   |            |

|                              | For TFT (                                                                                                                                      | output 1 | imina    | adiust: |          |         |              |         |         |            |

| Description                  | Vsync sta                                                                                                                                      | art posi | tion H-  | Byte    | for AM   | 32024   | 0N1. D       | on't ne | ed to n | nodify it. |

| Register<br>Address          | Default                                                                                                                                        | DB7      | DB6      | DB5     | DB4      | DB3     | DB2          | DB1     | DB0     | Remark     |

| (Hex)                        | (Hex)                                                                                                                                          |          |          |         |          |         |              |         |         |            |

| 0x1D                         | 00                                                                                                                                             |          |          | Vsy     | nc_stL   | _Byte[  | 7:0]         |         |         |            |

| Description                  | For TFT of Vsync state The defau                                                                                                               | art posi | tion Ľ-l | 3yte    | for AM   | 32024   | 0N1. D       | on't ne | ed to n | nodify it. |

| Register<br>Address<br>(Hex) | Default<br>(Hex)                                                                                                                               | DB7      | DB6      | DB5     | DB4      | DB3     | DB2          | DB1     | DB0     | Remark     |

| 0x1É                         | 00                                                                                                                                             |          |          |         |          | Vsyr    | c_pwl        | 1_Byte  | [3:0]   |            |

| Description                  | For TFT of Vsync pu                                                                                                                            | lse wid  | th H-B   | yté     | for AM   | 32024   | 0N1. D       | on't ne | ed to n | nodify it. |

| Register<br>Address<br>(Hex) | Default<br>(Hex)                                                                                                                               | DB7      | DB6      | DB5     | DB4      | DB3     | DB2          | DB1     | DB0     | Remark     |

| 0x1F                         | 08                                                                                                                                             |          |          | Vsyr    | nc_pwl   | Byte    | [7:0]        |         |         |            |

| Description                  | For TFT of Vsync pu                                                                                                                            | lse wid  | th L-By  | ⁄te     | for AM   | 32024   | 0N1. D       | on't ne | ed to n | nodify it. |

| Register<br>Address<br>(Hex) | Default<br>(Hex)                                                                                                                               | DB7      | DB6      | DB5     | DB4      | DB3     | DB2          | DB1     | DB0     | Remark     |

| 0x20                         | 00                                                                                                                                             |          |          |         |          | Vac     | ct_stH_      | Byte    | 3:01    |            |

| Description                  | For TFT of Vertical Default                                                                                                                    | E puls   | e start  | positio |          |         | 0N1. D       | on't ne | ed to n | nodify it. |

| Register<br>Address<br>(Hex) | Default<br>(Hex)                                                                                                                               | DB7      | DB6      | DB5     | DB4      | DB3     | DB2          | DB1     | DB0     | Remark     |