Version: C

2018-01-10

# Specification for Approval

| Customer:   |  |

|-------------|--|

| Model Name: |  |

| Sı           | Customer approval |             |  |

|--------------|-------------------|-------------|--|

| R&D Designed | R&D Approved      | QC Approved |  |

| Peter        | Peng Jun          |             |  |

Version: C

2018-01-10

# **Revision Record**

| REV NO. | REV DATE   | CONTENTS                         | Note |

|---------|------------|----------------------------------|------|

| Α       | 2015-07-01 | NEW ISSUE                        |      |

| В       | 2016-09-08 | Remove the double-sided adhesive |      |

| С       | 2018-01-10 | Change P.6 pin41 and pin42       |      |

|         |            |                                  |      |

|         |            |                                  |      |

|         |            |                                  |      |

|         |            |                                  |      |

|         |            |                                  |      |

|         |            |                                  |      |

|         |            |                                  |      |

|         |            |                                  |      |

|         |            |                                  |      |

|         |            |                                  |      |

|         |            |                                  |      |

|         |            |                                  |      |

|         |            |                                  |      |

|         |            |                                  |      |

|         |            |                                  |      |

|         |            |                                  |      |

|         |            |                                  |      |

|         |            |                                  |      |

|         |            |                                  |      |

Version: C

2018-01-10

# **Table of Contents**

| List | Description                             | Page No. |

|------|-----------------------------------------|----------|

|      | Cover                                   | 1        |

|      | Revision Record                         | 2        |

|      | Table of Contents                       | 3        |

| 1    | Scope                                   | 4        |

| 2    | General Information                     | 4        |

| 3    | External Dimensions                     | 5        |

| 4    | Interface Description                   | 6        |

| 5    | Absolute Maximum Ratings                | 9        |

| 6    | DC Characteristics                      | 9        |

| 7    | Timing Characteristics                  | 10       |

| 8    | Backlight Characteristics               | 19       |

| 9    | Optical Characteristics                 | 20       |

| 10   | Reliability Test Conditions and Methods | 22       |

| 11   | Inspection Standard                     | 23       |

| 12   | Handling Precautions                    | 28       |

| 13   | Precaution for Use                      | 29       |

| 14   | Packing Method                          | 29       |

Version: C

2018-01-10

## 1. Scope

This specification defines general provisions as well as inspection standards for TFT module supplied by AMSON electronics.

If the event of unforeseen problem or unspecified items may occur, naturally shall negotiate and agree to solution.

## 2. General Information

### LCM

| ITEM                  | STANDARD VALUES                                                                                        | UNITS |

|-----------------------|--------------------------------------------------------------------------------------------------------|-------|

| LCD type              | 3.5"TFT                                                                                                |       |

| Dot arrangement       | 480(RGB)×800                                                                                           | dots  |

| Color filter array    | RGB vertical stripe                                                                                    |       |

| Display mode          | IPS / Transmission / Normally Black                                                                    | -     |

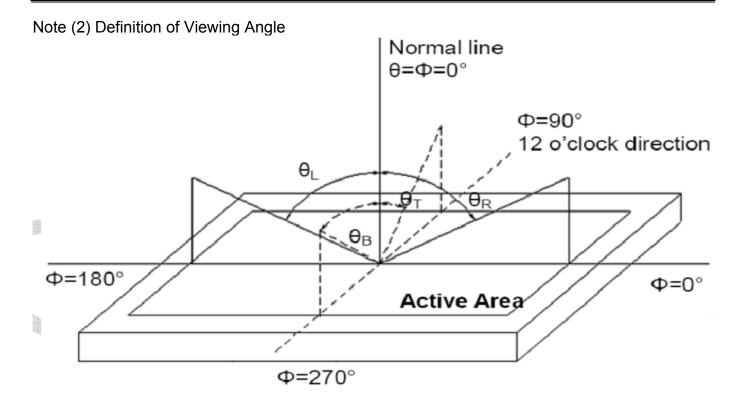

| Viewing Direction     | 80/80/80/80 deg(U/D/L/R @ C/R>10)                                                                      |       |

| Driver IC             | HX8369A                                                                                                |       |

| Module size           | 50.56(W)×86.20(H)×3.05(T)                                                                              | mm    |

| Active area           | 45.36(W)×75.60(H)                                                                                      | mm    |

| Dot pitch             | 0.0945(W)×0.0945(H)                                                                                    | mm    |

| Interface             | 8/ 9/16/18-bit i80-series system interface<br>SPI + 16/18/24-bit RGB interface<br>SPI + MIPI interface |       |

| Operating temperature | -20 ~ +70                                                                                              | °C    |

| Storage temperature   | -30 ~ +80                                                                                              | °C    |

| Back Light            | 8 White LED                                                                                            |       |

| Weight                | TBD                                                                                                    | g     |

## **RTP**

| ITEM                  | STANDARD VALUES                | UNITS |

|-----------------------|--------------------------------|-------|

| RTP type              | Film + Glass + FPC             |       |

| Surface hardness      | 3H                             |       |

| Transmittance         | ≥80%                           |       |

| RTP size              | 50.56 (W)×86.20 (H)×1.2(T)     | mm    |

| Active area           | 45.96(W)×76.20 (H)             | mm    |

| Response Time         | ≤10ms                          | ms    |

| Linearity             | ≤1.5%                          | %     |

| Hitting Life          | ≥1000000times                  | Times |

| Insulation resistance | >20MΩ                          | ΜΩ    |

| Operation force ≤120g |                                | g     |

| Resistance            | X:300Ω ~ 900Ω<br>Y:200Ω ~ 500Ω | Ω     |

Version: C

2018-01-10

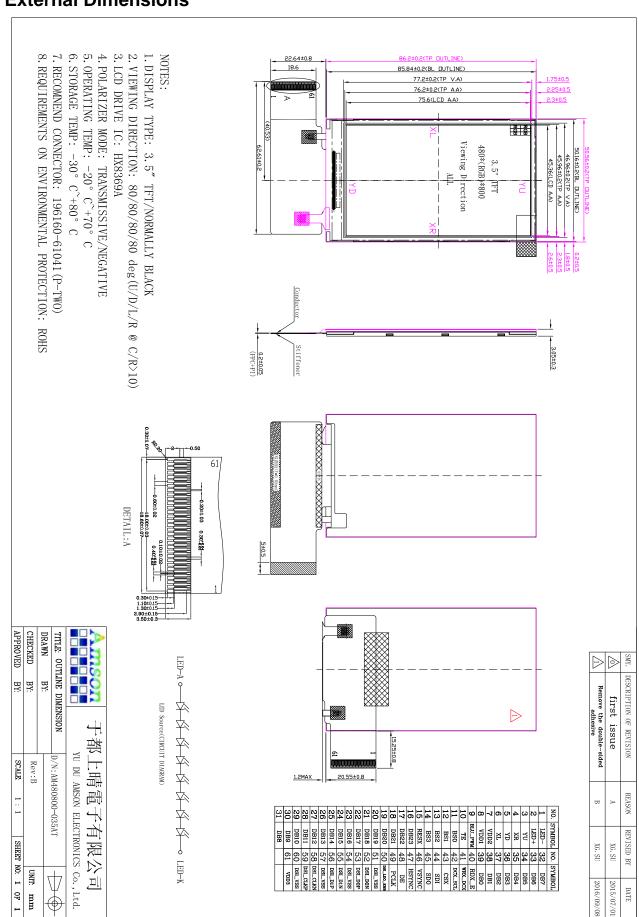

### 3. External Dimensions

Version: C

2018-01-10

## 4. Interface Description

| 1 LEDK LED backlight (Cathode). 2 LEDA LED backlight (Anode). 3 YU 4 XR 5 YD 6 XL 7 VDD2 A supply voltage to the analog circuit. 8 VDD1 A supply voltage to the I/O circuit. Backlight on/off control pin. If use CABC function, the pin can                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       | lace Descrip |                                                                       |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------|-----------------------------------------------------------------------|--|--|--|--|

| 2 LEDA LED backlight (Anode). 3 YU 4 XR 5 YD 6 XL 7 VDD2 A supply voltage to the analog circuit. 8 VDD1 A supply voltage to the I/O circuit. 9 BLU_PWM BACKJIGHT on/off control pin. If use CABC function, the pin can Connect to external LED driver IC. Please refer to Brightness control block. 10 TE Output a frame head pulse signal. 11 BS0 12 BS1 MPU interface mode selection signal. Must be connected to GND or VDD1.For the details, please refer to NOTE3 14 BS3 PB[23:00] Data bus. For the connection condition of the MPU & RGB Interface mode, please refer to NOTE3 16~39 DB[23:00] Data bus. For the connection condition of the MPU & RGB Interface mode, please refer to NOTE3 40 RDX_E DBI Type-A: 0: Read/Write disable, 1: Read / Write enable. DBI Type-B: a read signal and read data at the low level. 41 WRX_DCX Writes strobe signal to write data when WRX is "Low" in MPU I/F. Data / Command Selection pin in 4-wire SPI I/F. 42 DCX_SCL Display data / command selection in 80-series MPU I/F. A synchronous clock signal in SPI I/F. 43 CSX Chip select input pin ("Low" enable) in MPU I/F and SPI I/F. 44 SDI Serial input signal in SPI I/F. 45 SDO Serial output signal in RGB I/F. 46 VSYNC Vertical sync signal in RGB I/F. 47 HSYNC Horizontal sync signal in RGB I/F. 48 DE Data enable signal in RGB I/F. 50 DSI_DDENB High: Disable the DSI_LDO. The default setting is Low. High: Disable the DSI_LDO. Low: Enable the DSI_LDO. It must be connected to VDD1 or GND. (latch type) 51 DSI_VSS Ground. 52 DSI_DON MIPI-DSI Data differential signal input pins. (Data lane 0) 53 DSI_DON MIPI-DSI Data differential signal input pins. (Data lane 0) 55 DSI_D1P MIPI-DSI Data differential signal input pins. (Data lane 1)                          | PIN   | PIN NAME     | DESCRIPTION                                                           |  |  |  |  |

| 3 YU 4 XR 5 YD 6 XL 7 VDD2 A supply voltage to the analog circuit. 8 VDD1 A supply voltage to the I/O circuit. 8 VDD1 A supply voltage to the I/O circuit. 9 BLU_PWM Connect to external LED driver IC. Please refer to Brightness contro block. 10 TE Output a frame head pulse signal. 11 BS0 MPU interface mode selection signal. Must be connected to GND or VDD1.For the details, please refer to NOTE3 14 BS3 MPU interface mode selection condition of the MPU & RGB Interface mode, please refer to NOTE3 15 RESX Reset input pin, Active "L". 16~39 DB[23:00] Data bus. For the connection condition of the MPU & RGB Interface mode, please refer to NOTE3 40 RDX_E DBI Type-A: 0: Read/Write disable, 1: Read / Write enable. DBI Type-B: a read signal and read data at the low level. 41 WRX_DCX Writes strobe signal to write data when WRX is "Low" in MPU I/F. Data / Command Selection pin in 4-wire SPI I/F. 42 DCX_SCL Display data / command selection in 80-series MPU I/F. A synchronous clock signal in SPI I/F. 43 CSX Chip select input pin ("Low" enable) in MPU I/F and SPI I/F. 44 SDI Serial input signal in SPI I/F. 45 SDO Serial output signal in SPI I/F. 46 VSYNC Vertical sync signal in RGB I/F. 47 HSYNC Horizontal sync signal in RGB I/F. 48 DE Data enable signal in RGB I/F. 49 PCLK Pixel clock signal in RGB I/F. 50 DSI_LDO_ENB High: Disable the DSI _LDO. The default setting is Low. 150 LDO_ENB High: Disable the DSI _LDO. Low: Enable the DSI _LDO. It must be connected to VDD1 or GND. (latch type) 51 DSI_VSS Ground. 52 DSI_DON MIPI-DSI Data differential signal input pins. (Data lane 0) 53 DSI_DON MIPI-DSI Data differential signal input pins. (Data lane 0) 54 DSI_DIP MIPI-DSI Data differential signal input pins. (Data lane 1) | 1     | LEDK         | LED backlight (Cathode).                                              |  |  |  |  |

| 4       XR         5       YD         6       XL         7       VDD2       A supply voltage to the analog circuit.         8       VDD1       A supply voltage to the I/O circuit.         8       VDD1       A supply voltage to the I/O circuit.         9       BLU_PWM       Backlight on/off control pin. If use CABC function, the pin can Connect to external LED driver IC. Please refer to Brightness control block.         10       TE       Output a frame head pulse signal.         11       BS0       MPU interface mode selection signal. Must be connected to GND or VDD1.For the details, please refer to NOTE3         13       BS2       please refer to NOTE3         14       BS3       Reset input pin, Active "L".         15       RESX       Reset input pin, Active "L".         Data bus. For the connection condition of the MPU & RGB Interface mode, please refer to NOTE3         40       RDX_E       DBI Type-A: O: Read/Write disable, 1: Read / Write enable. DBI Type-B: a read signal and read data at the low level.         41       WRX_DCX       Writes strobe signal to write data when WRX is "Low" in MPU I/F. Data / Command Selection pin in 4-wire SPI I/F.         42       DCX_SCL       Chip select input pin ("Low" enable) in MPU I/F and SPI I/F.         43       CSX       Chip select input pin ("Low" enable) in MPU I/F and SP                                                                                                                                                                                                                                                                                                                                                                                                      | 2     | LEDA         | LED backlight (Anode).                                                |  |  |  |  |

| Touch pin.  A supply voltage to the analog circuit.  A supply voltage to the I/O circuit.  Backlight on/off control pin. If use CABC function, the pin can Connect to external LED driver IC. Please refer to Brightness contro block.  TE Output a frame head pulse signal.  MPU interface mode selection signal. Must be connected to GND or VDD1.For the details, please refer to NOTE3  BS3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3     | YU           |                                                                       |  |  |  |  |

| 5 YD 6 XL 7 VDD2 A supply voltage to the analog circuit. 8 VDD1 A supply voltage to the I/O circuit.  8 VDD1 A supply voltage to the I/O circuit.  9 BLU_PWM Connect to external LED driver IC. Please refer to Brightness contro block. 10 TE Output a frame head pulse signal. 11 BS0 MPU interface mode selection signal. Must be connected to GND or VDD1.For the details, please refer to NOTE3 13 BS2 please refer to NOTE3 15 RESX Reset input pin, Active "L". 16~39 DB[23:00] Data bus. For the connection condition of the MPU & RGB Interface mode, please refer to NOTE3 40 RDX_E DBI Type-A: 0: Read/Write disable, 1: Read / Write enable. DBI Type-B: a read signal and read data at the low level. 41 WRX_DCX Writes strobe signal to write data when WRX is "Low" in MPU I/F. Data / Command Selection pin in 4-wire SPI I/F. 42 DCX_SCL Display data / command selection in 80-series MPU I/F. A synchronous clock signal in SPI I/F. 43 CSX Chip select input pin ("Low" enable) in MPU I/F and SPI I/F. 44 SDI Serial input signal in SPI I/F. 45 SDO Serial output signal in RGB I/F. 46 VSYNC Vertical sync signal in RGB I/F. 47 HSYNC Horizontal sync signal in RGB I/F. 48 DE Data enable signal in RGB I/F. 50 DSI_DO_ENB DSI I/F: Control signal of DSI_LDO. The default setting is Low. 51 DSI_VSS Ground. 52 DSI_DOP MIPI-DSI Data differential signal input pins. (Data lane 0) 53 DSI_DON MIPI-DSI Data differential signal input pins. (Data lane 0) 54 DSI_VSS Ground.                                                                                                                                                                                                                                                                                         | 4     | XR           | Touch nin                                                             |  |  |  |  |

| 7 VDD2 A supply voltage to the analog circuit. 8 VDD1 A supply voltage to the I/O circuit. 9 BLU_PWM Connect to external LED driver IC. Please refer to Brightness contro block. 10 TE Output a frame head pulse signal. 11 BS0 MPU interface mode selection signal. Must be connected to GND or VDD1.For the details, please refer to NOTE3 13 BS2 please refer to NOTE3 15 RESX Reset input pin, Active "L". 16~39 DB[23:00] Data bus. For the connection condition of the MPU & RGB interface mode, please refer to NOTE3 40 RDX_E DBI Type-A: 0. Read/Write disable, 1: Read / Write enable. DBI Type-B: a read signal and read data at the low level. 41 WRX_DCX Writes strobe signal to write data when WRX is "Low" in MPU I/F. Data / Command Selection pin in 4-wire SPI I/F. 42 DCX_SCL Display data / command selection in 80-series MPU I/F. A synchronous clock signal in SPI I/F. 43 CSX Chip select input pin ("Low" enable) in MPU I/F and SPI I/F. 44 SDI Serial output signal in SPI I/F. 45 SDO Serial output signal in RGB I/F. 46 VSYNC Vertical sync signal in RGB I/F. 47 HSYNC Horizontal sync signal in RGB I/F. 48 DE Data enable signal in RGB I/F. 49 PCLK Pixel clock signal in RGB I/F. 50 DSI_DO_ENB High: Disable the DSI_LDO. The default setting is Low. 51 DSI_VSS Ground. 52 DSI_DOP MIPI-DSI Data differential signal input pins. (Data lane 0) 53 DSI_DON MIPI-DSI Data differential signal input pins. (Data lane 0) 54 DSI_VSS Ground.                                                                                                                                                                                                                                                                                                                  | 5     | YD           | Touch pin.                                                            |  |  |  |  |

| 8 VDD1 A supply voltage to the I/O circuit.  BLU_PWM Connect to external LED driver IC. Please refer to Brightness contro block.  Output a frame head pulse signal.  10 TE Output a frame head pulse signal.  11 BS0 MPU interface mode selection signal. Must be connected to GND or VDD1.For the details, please refer to NOTE3  14 BS3 PBS2 Please refer to NOTE3  15 RESX Reset input pin, Active "L".  DBI[23:00] Data bus. For the connection condition of the MPU & RGB Interface mode, please refer to NOTE3  40 RDX_E DBI Type-A: 0: Read/Write disable, 1: Read / Write enable. DBI Type-B: a read signal and read data at the low level.  41 WRX_DCX Writes strobe signal to write data when WRX is "Low" in MPU I/F. Data / Command Selection pin in 4-wire SPI I/F.  42 DCX_SCL Display data / command selection in 80-series MPU I/F. A synchronous clock signal in SPI I/F.  43 CSX Chip select input pin ("Low" enable) in MPU I/F and SPI I/F.  44 SDI Serial input signal in SPI I/F.  45 SDO Serial output signal in SPI I/F.  46 VSYNC Vertical sync signal in RGB I/F.  47 HSYNC Horizontal sync signal in RGB I/F.  48 DE Data enable signal in RGB I/F.  50 DSI_LDO_ENB High: Disable the DSI_LDO. The default setting is Low. Pixel clock signal of DSI_LDO. Low: Enable the DSI_LDO. It must be connected to VDD1 or GND. (latch type)  51 DSI_VSS Ground.  52 DSI_DDN MIPI-DSI Data differential signal input pins. (Data lane 0)  53 DSI_DDN MIPI-DSI Data differential signal input pins. (Data lane 0)  54 DSI_VSS Ground.                                                                                                                                                                                                                                         | 6     | XL           |                                                                       |  |  |  |  |

| Backlight on/off control pin. If use CABC function, the pin can Connect to external LED driver IC. Please refer to Brightness control block.  10 TE Output a frame head pulse signal.  11 BS0 12 BS1 MPU interface mode selection signal. Must be connected to GND or VDD1.For the details, please refer to NOTE3  14 BS3 15 RESX Reset input pin, Active "L".  16~39 DB[23:00] Data bus. For the connection condition of the MPU & RGB Interface mode, please refer to NOTE3  40 RDX_E DBI Type-A: 0: Read/Write disable, 1: Read / Write enable. DBI Type-B: a read signal and read data at the low level.  41 WRX_DCX Write strobe signal to write data when WRX is "Low" in MPU I/F. Data / Command Selection pin in 4-wire SPI I/F.  42 DCX_SCL Display data / command selection in 80-series MPU I/F. A synchronous clock signal in SPI I/F.  43 CSX Chip select input pin ("Low" enable) in MPU I/F and SPI I/F.  44 SDI Serial input signal in SPI I/F.  45 SDO Serial output signal in SPI I/F.  46 VSYNC Vertical sync signal in RGB I/F.  47 HSYNC Horizontal sync signal in RGB I/F.  48 DE Data enable signal in RGB I/F.  DSI I/F: Control signal of DSI LDO. The default setting is Low. High: Disable the DSI LDO. Low: Enable the DSI LDO. It must be connected to VDD1 or GND. (latch type)  50 DSI_DOP MIPI-DSI Data differential signal input pins. (Data lane 0)  53 DSI_DON MIPI-DSI Data differential signal input pins. (Data lane 0)  54 DSI_VSS Ground.                                                                                                                                                                                                                                                                                                               | 7     | VDD2         | A supply voltage to the analog circuit.                               |  |  |  |  |

| 9 BLU_PWM Connect to external LED driver IC. Please refer to Brightness contro block.  10 TE Output a frame head pulse signal.  11 BS0 12 BS1 Connected to GND or VDD1.For the details, please refer to NOTE3  13 BS2 please refer to NOTE3  15 RESX Reset input pin, Active "L".  16~39 DB[23:00] Data bus. For the connection condition of the MPU & RGB Interface mode, please refer to NOTE3  40 RDX_E DBI Type-A: 0: Read/Write disable, 1: Read / Write enable. DBI Type-B: a read signal and read data at the low level. Writes strobe signal to write data when WRX is "Low" in MPU I/F. Data / Command Selection pin in 4-wire SPI I/F.  41 DCX_SCL Display data / command selection in 80-series MPU I/F. A synchronous clock signal in SPI I/F.  42 DCX_SCL Chip select input pin ("Low" enable) in MPU I/F and SPI I/F.  43 CSX Chip select input signal in SPI I/F.  44 SDI Serial output signal in SPI I/F.  45 SDO Serial output signal in SPI I/F.  46 VSYNC Vertical sync signal in RGB I/F.  47 HSYNC Horizontal sync signal in RGB I/F.  48 DE Data enable signal in RGB I/F.  49 PCLK Pixel clock signal in RGB I/F.  DSI I/F: Control signal of DSI_LDO. The default setting is Low. High: Disable the DSI_LDO. Low: Enable the DSI_LDO. It must be connected to VDD1 or GND. (latch type)  50 DSI_LDO_ENB MIPI-DSI Data differential signal input pins. (Data lane 0)  51 DSI_VSS Ground.  52 DSI_DDP MIPI-DSI Data differential signal input pins. (Data lane 0)  53 DSI_DDP MIPI-DSI Data differential signal input pins. (Data lane 0)                                                                                                                                                                                                                                 | 8     | VDD1         |                                                                       |  |  |  |  |

| 11 BS0 12 BS1 13 BS2 14 BS3 15 RESX Reset input pin, Active "L".  16~39 DB[23:00]  40 RDX_E DBI Type-A: 0: Read/Write disable, 1: Read / Write enable. DBI Type-B: a read signal and read data at the low level.  Writes strobe signal to write data when WRX is "Low" in MPU I/F. Display data / command selection in 80-series MPU I/F.  42 DCX_SCL A synchronous clock signal in SPI I/F.  43 CSX Chip select input pin ("Low" enable) in MPU I/F and SPI I/F.  44 SDI Serial input signal in SPI I/F.  45 SDO Serial output signal in SPI I/F.  46 VSYNC Vertical sync signal in RGB I/F.  47 HSYNC Horizontal sync signal in RGB I/F.  48 DE Data enable signal in RGB I/F.  DSI LDO_ENB High: Disable the DSI LDO. The default setting is Low. High: Disable the DSI LDO. Low: Enable the DSI LDO. It must be connected to VDD1 or GND. (latch type)  51 DSI_VSS Ground.  55 DSI_DDP MIPI-DSI Data differential signal input pins. (Data lane 0)  54 DSI_DDP MIPI-DSI Data differential signal input pins. (Data lane 0)  55 DSI_DDP MIPI-DSI Data differential signal input pins. (Data lane 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9     | BLU_PWM      | Connect to external LED driver IC. Please refer to Brightness control |  |  |  |  |

| MPU interface mode selection signal. Must be connected to GND or VDD1.For the details, please refer to NOTE3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10    | TE           | Output a frame head pulse signal.                                     |  |  |  |  |

| connected to GND or VDD1.For the details, please refer to NOTE3  13 BS2 please refer to NOTE3  15 RESX Reset input pin, Active "L".  16~39 DB[23:00] Data bus. For the connection condition of the MPU & RGB Interface mode, please refer to NOTE3  40 RDX_E DBI Type-A: 0: Read/Write disable, 1: Read / Write enable. DBI Type-B: a read signal and read data at the low level.  41 WRX_DCX Writes strobe signal to write data when WRX is "Low" in MPU I/F. Data / Command Selection pin in 4-wire SPI I/F.  42 DCX_SCL Display data / command selection in 80-series MPU I/F. A synchronous clock signal in SPI I/F.  43 CSX Chip select input pin ("Low" enable) in MPU I/F and SPI I/F.  44 SDI Serial input signal in SPI I/F.  45 SDO Serial output signal in SPI I/F.  46 VSYNC Vertical sync signal in RGB I/F.  47 HSYNC Horizontal sync signal in RGB I/F.  48 DE Data enable signal in RGB I/F.  49 PCLK Pixel clock signal in RGB I/F.  50 DSI_LDO_ENB High: Disable the DSI_LDO. The default setting is Low. High: Disable the DSI_LDO. Low: Enable the DSI_LDO. It must be connected to VDD1 or GND. (latch type)  51 DSI_VSS Ground.  52 DSI_DOP MIPI-DSI Data differential signal input pins. (Data lane 0)  53 DSI_DON MIPI-DSI Data differential signal input pins. (Data lane 0)  54 DSI_VSS Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 11    | BS0          |                                                                       |  |  |  |  |

| 13 BS2 14 BS3 15 RESX Reset input pin, Active "L".  16~39 DB[23:00] Data bus. For the connection condition of the MPU & RGB Interface mode, please refer to NOTE3  40 RDX_E DBI Type-A: 0: Read/Write disable, 1: Read / Write enable. DBI Type-B: a read signal and read data at the low level.  41 WRX_DCX Writes strobe signal to write data when WRX is "Low" in MPU I/F. Data / Command Selection pin in 4-wire SPI I/F.  42 DCX_SCL Display data / command selection in 80-series MPU I/F. A synchronous clock signal in SPI I/F.  43 CSX Chip select input pin ("Low" enable) in MPU I/F and SPI I/F.  44 SDI Serial input signal in SPI I/F.  45 SDO Serial output signal in SPI I/F.  46 VSYNC Vertical sync signal in RGB I/F.  47 HSYNC Horizontal sync signal in RGB I/F.  48 DE Data enable signal in RGB I/F mode  49 PCLK Pixel clock signal in RGB I/F.  50 DSI_LDO_ENB DSI I/F: Control signal of DSI_LDO. The default setting is Low. High: Disable the DSI_LDO. Low: Enable the DSI_LDO. It must be connected to VDD1 or GND. (latch type)  51 DSI_VSS Ground.  52 DSI_DOP MIPI-DSI Data differential signal input pins. (Data lane 0)  53 DSI_DON MIPI-DSI Data differential signal input pins. (Data lane 0)  54 DSI_VSS Ground.  55 DSI_D1P MIPI-DSI Data differential signal input pins. (Data lane 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 12    | BS1          |                                                                       |  |  |  |  |

| 15 RESX Reset input pin, Active "L".  16~39 DB[23:00] Data bus. For the connection condition of the MPU & RGB Interface mode, please refer to NOTE3  40 RDX_E DBI Type-A: 0: Read/Write disable, 1: Read / Write enable. DBI Type-B: a read signal and read data at the low level.  41 WRX_DCX Writes strobe signal to write data when WRX is "Low" in MPU I/F. Data / Command Selection pin in 4-wire SPI I/F.  42 DCX_SCL Display data / command selection in 80-series MPU I/F. A synchronous clock signal in SPI I/F.  43 CSX Chip select input pin ("Low" enable) in MPU I/F and SPI I/F.  44 SDI Serial input signal in SPI I/F.  45 SDO Serial output signal in SPI I/F.  46 VSYNC Vertical sync signal in RGB I/F.  47 HSYNC Horizontal sync signal in RGB I/F.  48 DE Data enable signal in RGB I/F.  50 DSI_LDO_ENB High: Disable the DSI_LDO. The default setting is Low. High: Disable the DSI_LDO. Low: Enable the DSI_LDO. It must be connected to VDD1 or GND. (latch type)  51 DSI_VSS Ground.  52 DSI_DOP MIPI-DSI Data differential signal input pins. (Data lane 0)  53 DSI_DON MIPI-DSI Data differential signal input pins. (Data lane 0)  54 DSI_VSS Ground.  55 DSI_D1P MIPI-DSI Data differential signal input pins. (Data lane 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 13    | BS2          | ,                                                                     |  |  |  |  |

| DB[23:00] Data bus. For the connection condition of the MPU & RGB Interface mode, please refer to NOTE3  40 RDX_E DBI Type-A: 0: Read/Write disable, 1: Read / Write enable. DBI Type-B: a read signal and read data at the low level.  41 WRX_DCX Writes strobe signal to write data when WRX is "Low" in MPU I/F. Data / Command Selection pin in 4-wire SPI I/F.  42 DCX_SCL Display data / command selection in 80-series MPU I/F. Display data / command selection in 80-series MPU I/F.  43 CSX Chip select input pin ("Low" enable) in MPU I/F and SPI I/F.  44 SDI Serial input signal in SPI I/F.  45 SDO Serial output signal in SPI I/F.  46 VSYNC Vertical sync signal in RGB I/F.  47 HSYNC Horizontal sync signal in RGB I/F.  48 DE Data enable signal in RGB I/F.  49 PCLK Pixel clock signal in RGB I/F.  DSI I/F: Control signal of DSI_LDO. The default setting is Low. High: Disable the DSI_LDO. Low: Enable the DSI_LDO. It must be connected to VDD1 or GND. (latch type)  51 DSI_VSS Ground.  52 DSI_DDP MIPI-DSI Data differential signal input pins. (Data lane 0)  53 DSI_DDN MIPI-DSI Data differential signal input pins. (Data lane 0)  54 DSI_VSS Ground.  55 DSI_D1P MIPI-DSI Data differential signal input pins. (Data lane 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 14    | BS3          | product to the filler                                                 |  |  |  |  |

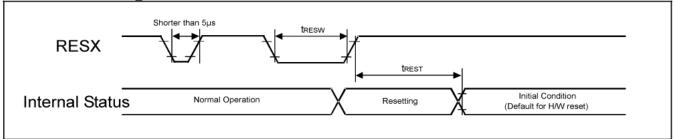

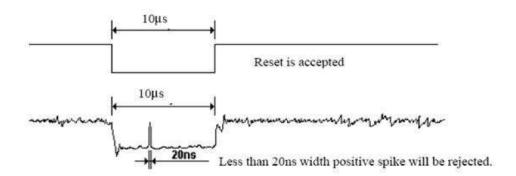

| Interface mode, please refer to NOTE3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 15    | RESX         | Reset input pin, Active "L".                                          |  |  |  |  |

| WRX_DCX  WRX_DCX  Writes strobe signal to write data when WRX is "Low" in MPU I/F. Data / Command Selection pin in 4-wire SPI I/F.  DCX_SCL  Display data / command selection in 80-series MPU I/F. A synchronous clock signal in SPI I/F.  CSX  Chip select input pin ("Low" enable) in MPU I/F and SPI I/F.  SDI  Serial input signal in SPI I/F.  SDO  Serial output signal in SPI I/F.  VSYNC  Vertical sync signal in RGB I/F.  HSYNC  Horizontal sync signal in RGB I/F.  DE  Data enable signal in RGB I/F.  DSI I/F: Control signal of DSI_LDO. The default setting is Low. High: Disable the DSI_LDO. Low: Enable the DSI_LDO. It must be connected to VDD1 or GND. (latch type)  SI DSI_VSS  Ground.  DSI_DON  MIPI-DSI Data differential signal input pins. (Data lane 0)  DSI_VSS  Ground.  DSI_D1P  MIPI-DSI Data differential signal input pins. (Data lane 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 16~39 | DB[23:00]    |                                                                       |  |  |  |  |

| Data / Command Selection pin in 4-wire SPI I/F.  DCX_SCL Display data / command selection in 80-series MPU I/F.  A synchronous clock signal in SPI I/F.  CSX Chip select input pin ("Low" enable) in MPU I/F and SPI I/F.  SDI Serial input signal in SPI I/F.  SDO Serial output signal in SPI I/F.  VSYNC Vertical sync signal in RGB I/F.  HSYNC Horizontal sync signal in RGB I/F.  DE Data enable signal in RGB I/F.  DE Data enable signal in RGB I/F.  DSI I/F: Control signal of DSI_LDO. The default setting is Low.  High: Disable the DSI_LDO. Low: Enable the DSI_LDO.  It must be connected to VDD1 or GND. (latch type)  DSI_DOP MIPI-DSI Data differential signal input pins. (Data lane 0)  DSI_VSS Ground.  DSI_VSS Ground.  DSI_D1P MIPI-DSI Data differential signal input pins. (Data lane 0)  DSI_D1P MIPI-DSI Data differential signal input pins. (Data lane 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 40    | RDX_E        | DBI Type-B: a read signal and read data at the low level.             |  |  |  |  |

| 42 DCX_SCL A synchronous clock signal in SPI I/F.  43 CSX Chip select input pin ("Low" enable) in MPU I/F and SPI I/F.  44 SDI Serial input signal in SPI I/F.  45 SDO Serial output signal in SPI I/F.  46 VSYNC Vertical sync signal in RGB I/F.  47 HSYNC Horizontal sync signal in RGB I/F.  48 DE Data enable signal in RGB I/F mode  49 PCLK Pixel clock signal in RGB I/F.  DSI I/F: Control signal of DSI_LDO. The default setting is Low.  High: Disable the DSI_LDO. Low: Enable the DSI_LDO. It must be connected to VDD1 or GND. (latch type)  51 DSI_VSS Ground.  52 DSI_DOP MIPI-DSI Data differential signal input pins. (Data lane 0)  53 DSI_VSS Ground.  54 DSI_VSS Ground.  55 DSI_D1P MIPI-DSI Data differential signal input pins. (Data lane 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 41    | WRX_DCX      |                                                                       |  |  |  |  |

| 44 SDI Serial input signal in SPI I/F. 45 SDO Serial output signal in SPI I/F. 46 VSYNC Vertical sync signal in RGB I/F. 47 HSYNC Horizontal sync signal in RGB I/F. 48 DE Data enable signal in RGB I/F mode 49 PCLK Pixel clock signal in RGB I/F.  DSI I/F: Control signal of DSI_LDO. The default setting is Low. High: Disable the DSI_LDO. Low: Enable the DSI_LDO. It must be connected to VDD1 or GND. (latch type)  51 DSI_VSS Ground. 52 DSI_DOP MIPI-DSI Data differential signal input pins. (Data lane 0) 53 DSI_DON MIPI-DSI Data differential signal input pins. (Data lane 0) 54 DSI_VSS Ground. 55 DSI_D1P MIPI-DSI Data differential signal input pins. (Data lane 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 42    | DCX_SCL      |                                                                       |  |  |  |  |

| 45 SDO Serial output signal in SPI I/F.  46 VSYNC Vertical sync signal in RGB I/F.  47 HSYNC Horizontal sync signal in RGB I/F.  48 DE Data enable signal in RGB I/F mode  49 PCLK Pixel clock signal in RGB I/F.  DSI I/F: Control signal of DSI_LDO. The default setting is Low. High: Disable the DSI_LDO. Low: Enable the DSI_LDO. It must be connected to VDD1 or GND. (latch type)  51 DSI_VSS Ground.  52 DSI_DOP MIPI-DSI Data differential signal input pins. (Data lane 0)  53 DSI_DON MIPI-DSI Data differential signal input pins. (Data lane 0)  54 DSI_VSS Ground.  55 DSI_D1P MIPI-DSI Data differential signal input pins. (Data lane 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 43    | CSX          | Chip select input pin ("Low" enable) in MPU I/F and SPI I/F.          |  |  |  |  |

| 46 VSYNC Vertical sync signal in RGB I/F.  47 HSYNC Horizontal sync signal in RGB I/F.  48 DE Data enable signal in RGB I/F mode  49 PCLK Pixel clock signal in RGB I/F.  DSI I/F: Control signal of DSI_LDO. The default setting is Low. High: Disable the DSI_LDO. Low: Enable the DSI_LDO. It must be connected to VDD1 or GND. (latch type)  51 DSI_VSS Ground.  52 DSI_DOP MIPI-DSI Data differential signal input pins. (Data lane 0)  53 DSI_DON MIPI-DSI Data differential signal input pins. (Data lane 0)  54 DSI_VSS Ground.  55 DSI_D1P MIPI-DSI Data differential signal input pins. (Data lane 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 44    | SDI          | Serial input signal in SPI I/F.                                       |  |  |  |  |

| 47 HSYNC Horizontal sync signal in RGB I/F.  48 DE Data enable signal in RGB I/F mode  49 PCLK Pixel clock signal in RGB I/F.  50 DSI_LDO_ENB High: Disable the DSI_LDO. The default setting is Low. High: Disable the DSI_LDO. Low: Enable the DSI_LDO. It must be connected to VDD1 or GND. (latch type)  51 DSI_VSS Ground.  52 DSI_DOP MIPI-DSI Data differential signal input pins. (Data lane 0)  53 DSI_DON MIPI-DSI Data differential signal input pins. (Data lane 0)  54 DSI_VSS Ground.  55 DSI_D1P MIPI-DSI Data differential signal input pins. (Data lane 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 45    | SDO          | Serial output signal in SPI I/F.                                      |  |  |  |  |

| 48 DE Data enable signal in RGB I/F mode  49 PCLK Pixel clock signal in RGB I/F.  50 DSI_LDO_ENB DSI I/F: Control signal of DSI_LDO. The default setting is Low. High: Disable the DSI_LDO. Low: Enable the DSI_LDO. It must be connected to VDD1 or GND. (latch type)  51 DSI_VSS Ground.  52 DSI_DOP MIPI-DSI Data differential signal input pins. (Data lane 0)  53 DSI_DON MIPI-DSI Data differential signal input pins. (Data lane 0)  54 DSI_VSS Ground.  55 DSI_D1P MIPI-DSI Data differential signal input pins. (Data lane 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 46    | VSYNC        | Vertical sync signal in RGB I/F.                                      |  |  |  |  |

| PCLK Pixel clock signal in RGB I/F.  DSI I/F: Control signal of DSI_LDO. The default setting is Low. High: Disable the DSI_LDO. Low: Enable the DSI_LDO. It must be connected to VDD1 or GND. (latch type)  DSI_VSS Ground.  DSI_DOP MIPI-DSI Data differential signal input pins. (Data lane 0)  DSI_DON MIPI-DSI Data differential signal input pins. (Data lane 0)  DSI_VSS Ground.  DSI_D1P MIPI-DSI Data differential signal input pins. (Data lane 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 47    | HSYNC        | Horizontal sync signal in RGB I/F.                                    |  |  |  |  |

| DSI I/F: Control signal of DSI_LDO. The default setting is Low. High: Disable the DSI_LDO. Low: Enable the DSI_LDO. It must be connected to VDD1 or GND. (latch type)  DSI_VSS Ground.  DSI_DOP MIPI-DSI Data differential signal input pins. (Data lane 0)  DSI_DON MIPI-DSI Data differential signal input pins. (Data lane 0)  DSI_VSS Ground.  DSI_D1P MIPI-DSI Data differential signal input pins. (Data lane 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 48    | DE           | Data enable signal in RGB I/F mode                                    |  |  |  |  |

| 50 DSI_LDO_ENB High: Disable the DSI_LDO. Low: Enable the DSI_LDO. lt must be connected to VDD1 or GND. (latch type)  51 DSI_VSS Ground.  52 DSI_DOP MIPI-DSI Data differential signal input pins. (Data lane 0)  53 DSI_DON MIPI-DSI Data differential signal input pins. (Data lane 0)  54 DSI_VSS Ground.  55 DSI_D1P MIPI-DSI Data differential signal input pins. (Data lane 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 49    | PCLK         | <u> </u>                                                              |  |  |  |  |

| 52 DSI_D0P MIPI-DSI Data differential signal input pins. (Data lane 0) 53 DSI_D0N MIPI-DSI Data differential signal input pins. (Data lane 0) 54 DSI_VSS Ground. 55 DSI_D1P MIPI-DSI Data differential signal input pins. (Data lane 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 50    | DSI_LDO_ENB  | High: Disable the DSI_LDO. Low: Enable the DSI_LDO.                   |  |  |  |  |

| 53 DSI_D0N MIPI-DSI Data differential signal input pins. (Data lane 0) 54 DSI_VSS Ground. 55 DSI_D1P MIPI-DSI Data differential signal input pins. (Data lane 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 51    | DSI_VSS      | Ground.                                                               |  |  |  |  |

| 54 DSI_VSS Ground. 55 DSI_D1P MIPI-DSI Data differential signal input pins. (Data lane 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 52    | DSI_D0P      | MIPI-DSI Data differential signal input pins. (Data lane 0)           |  |  |  |  |

| 55 DSI_D1P MIPI-DSI Data differential signal input pins. (Data lane 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 53    | DSI_D0N      | MIPI-DSI Data differential signal input pins. (Data lane 0)           |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 54    | DSI_VSS      | Ground.                                                               |  |  |  |  |

| 56 DSI_D1N MIPI-DSI Data differential signal input pins. (Data lane 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 55    | DSI_D1P      | MIPI-DSI Data differential signal input pins. (Data lane 1)           |  |  |  |  |

| ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 56    | DSI_D1N      | MIPI-DSI Data differential signal input pins. (Data lane 1)           |  |  |  |  |

Version: C

2018-01-10

| 57 | DSI_VSS  | Ground.                                        |

|----|----------|------------------------------------------------|

| 58 | DSI_CLKP | MIPI-DSI CLOCK differential signal input pins. |

| 59 | DSI_CLKN | MIPI-DSI CLOCK differential signal input pins. |

| 60 | DSI_VSS  | Ground.                                        |

| 61 | VDD3     | A supply voltage to the logic circuit.         |

## **Brightness control block**

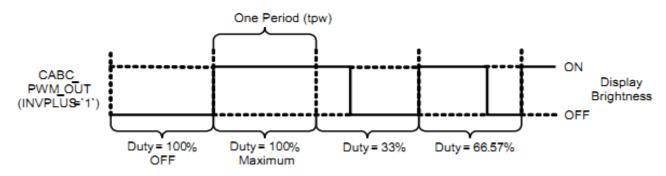

There is an external output signal from brightness block, CABC\_PWM\_OUT, to control the LED driver IC in order to control display brightness.

There are resister bits, DBV [7:0] of R51h, for display brightness of manual brightness setting. The CABC\_PWM\_OUT duty is calculated as (DBV [7:0])/255 x CABC duty (generated after one-frame display data content analysis).

For ex: CABC\_PWM\_OUT period=2.95 ms, and DBV [7:0] (R51h)='228DEC' and CABC duty is 74%. Then CABC\_PWM\_OUT duty=(228) / 255 x 74.42%'66.54%.

Correspond to the CABC\_PWM\_OUT period=2.95 ms, the high-level of CABC\_PWM\_OUT (high effective) = 1.96ms, and the low-level of CABC\_PWM\_OUT

=0.99ms.

## CABC\_PWM\_OUT output duty

| Symbol | Parameter   | Min.   | Max. | Unit | Description |

|--------|-------------|--------|------|------|-------------|

| tpw    | Pulse width | 0.0333 | 8.33 | ms   | -           |

## **CABC** timing table

**Note1:** The signal rise and fall times (tf, tr) are stipulated to be equal to or less than 15ns.

**Note2:** The pulse width range by setting CABC related registers is locate between 0.0333ms to 8.33ms.

When Architecture II module is used (BL='0') with the example below, the

CABC\_PWM\_OUT is always output low and the DBV [7:0] (R51h) will be read a value as 169DEC ((169)/255° 66.27%).

Version: C

2018-01-10

## NOTE3:

| NO I E3 |     |     |     |                                         |                                                                    |              |

|---------|-----|-----|-----|-----------------------------------------|--------------------------------------------------------------------|--------------|

| BS3     | BS2 | BS1 | BS0 | MPU interface mode                      | DB pins                                                            | Display mode |

| 0       | 0   | 0   | 0   | DBI TYPE-A 8-bit<br>(CLK-E)             | DB23-DB8: Unused,<br>DB7-DB0: Data                                 | Type 1       |

| 0       | 0   | 0   | 1   | DBI TYPE-A 9-bit<br>(CLK-E)             | DB23-DB9:Unused,<br>DB8-DB0: Data                                  | Type 1       |

| 0       | 0   | 1   | 0   | DBI TYPE-A 16-bit<br>(CLK-E)            | DB23-DB16: Unused, DB15-DB0: Data                                  | Type 1       |

| 0       | 0   | 1   | 1   | DBI TYPE-A 18-bit<br>(CLK-E)            | DB23-DB18: Unused, DB17-DB0: Data                                  | Type 1       |

| 0       | 1   | 0   | 0   | DBI TYPE-B 8-bit                        | DB23-DB8: Unused DB7-DB0: Data                                     | Type 1       |

| 0       | 1   | 0   | 1   | DBI TYPE-B 9-bit                        | DB23-DB9:Unused,<br>DB8-DB0: Data                                  | Type 1       |

| 0       | 1   | 1   | 0   | DBI TYPE-B 16-bit                       | DB23-DB16: Unused, DB15-DB0: Data                                  | Type 1       |

| 0       | 1   | 1   | 1   | DBI TYPE-B 18-bit                       | DB23-DB18: Unused, DB17-DB0: Data                                  | Type 1       |

| 1       | 0   | 0   | 0   | DSI<br>(Command mode)                   | DSI_CLKP,<br>DSI_CLKN,<br>DSI_D0P,<br>DSI_D0N,<br>DSI_D1P, DSI_D1N | Type 1       |

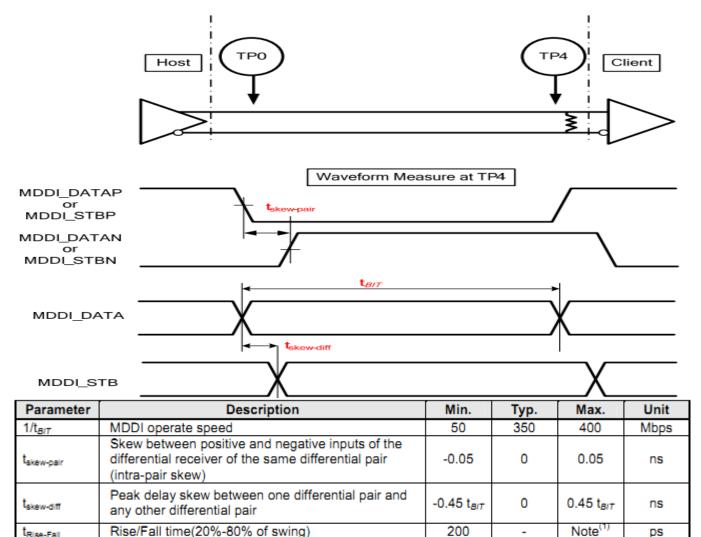

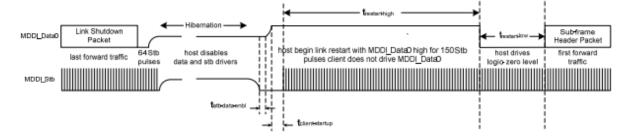

| 1       | 0   | 0   | 1   | 3-wire serial + MDDI interface (note 1) | MDDI_STBP, MDDI_STBN, MDDI_D0P, MDDI_D0N, MDDI_D1P, MDDI_D1N,      | -            |

| 1       | 0   | 1   | 0   | DBI TYPE-B 24-bit                       | DB23-DB0: Data                                                     | Type 1       |

| 1       | 1   | 0   | 0   | DSI (Video mode)                        | DSI_CLKP,<br>DSI_CLKN,<br>DSI_DOP,<br>DSI_DON,<br>DSI_D1P, DSI_D1N | Type 3       |

| 1       | 1   | 0   | 1   | DPI/DBI TYPE-C<br>Option 1              | SDI/SDO,<br>DB23-DB0                                               | Type 3       |

| 1       | 1   | 1   | 0   | DPI/DBI TYPE-C<br>Option 2              | SDI/SDO,<br>DB23-DB0                                               | Type 3       |

| 1       | 1   | 1   | 1   | DPI/DBI TYPE-C<br>Option 3              | SDI/SDO,<br>DB23-DB0                                               | Type 3       |

Version: C

2018-01-10

5. Absolute Maximum Ratings

| Item                  | Symbol | Min. | Max.     | Unit |

|-----------------------|--------|------|----------|------|

| Logic Supply Voltage  | VDD1   | -0.3 | 3.6      | V    |

| Analog Supply Voltage | VDD2,3 | -0.3 | 5.5      | V    |

| Input Voltage         | Vin    | -0.3 | VDD1+0.3 | V    |

| Operating Temperature | Тор    | -20  | 70       | °C   |

| Storage Temperature   | Тѕт    | -30  | 80       | °C   |

| Storage Humidity      | HD     | 20   | 90       | %RH  |

## 6. DC Characteristics

| o. Do onaraoteristios |                 |         |         |         |      |        |

|-----------------------|-----------------|---------|---------|---------|------|--------|

| Item                  | Symbol          | Min.    | Тур.    | Max.    | Unit | Remark |

| Logic Supply Voltage  | VDD1            | 1.65    | 1.8/2.8 | 3.3     | V    | -      |

| Analog Supply Voltage | VDD2,3          | 2.3     | 2.8     | 3.3     | V    | -      |

| Input High Voltage    | V <sub>IH</sub> | 0.7VDD1 | -       | IVDD1   | V    | -      |

| Input Low Voltage     | V <sub>IL</sub> | GND     | -       | 0.3VDD1 | V    | -      |

| Output High Voltage   | V <sub>OH</sub> | 0.8VDD1 | -       | VDD1    | V    | -      |

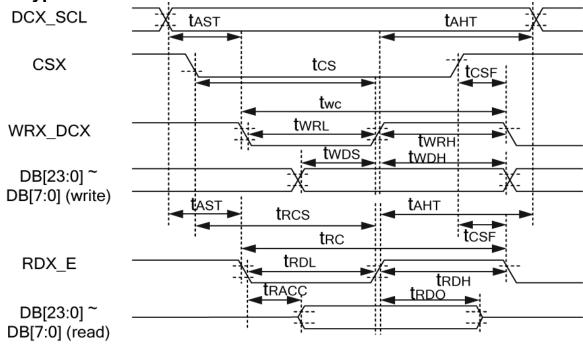

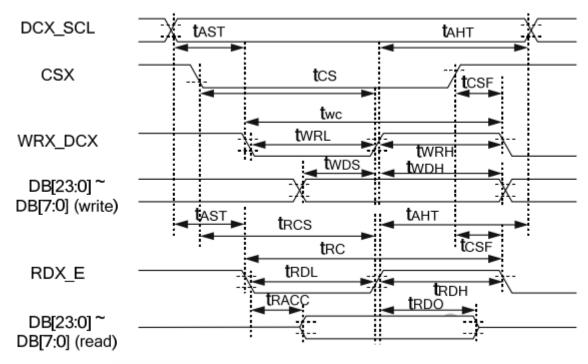

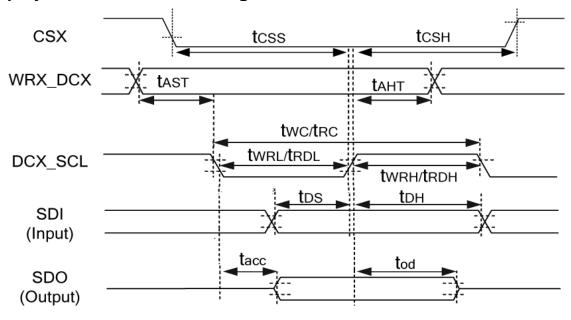

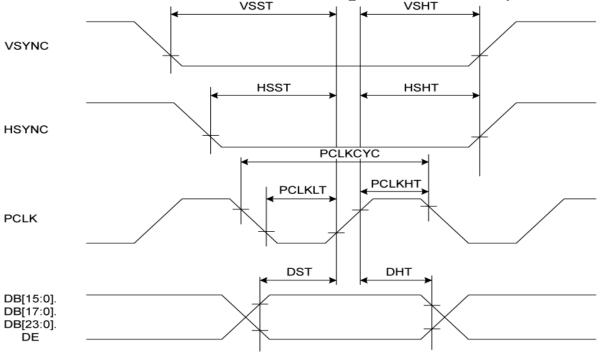

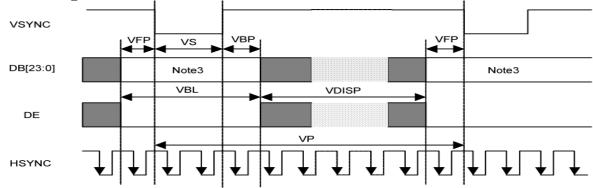

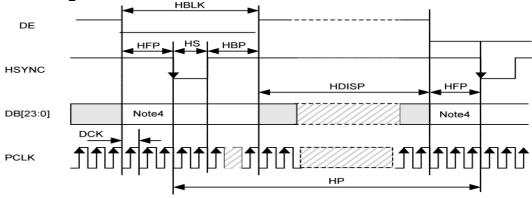

| Output Low Voltage    | V <sub>OL</sub> | GND     | -       | 0.2VDD1 | V    | -      |