# D

## **Am685**

### **Voltage Comparator**

## Advanced Micro Devices

### **DISTINCTIVE CHARACTERISTICS**

- 6.5 ns Maximum Propagation Delay at 5 mV Overdrive

- 3.0 ns Latch Setup Time

- Complementary ECL Outputs

- 50 Ω Line Driving Capability

#### **GENERAL DESCRIPTION**

The Am685 is a fast voltage comparator manufactured with an advanced bipolar-NPN, Schottky-diode high-frequency process that ensures very short propagation delays (6.5 ns) without sacrificing the excellent matching characteristics hitherto associated only with slow, high-performance linear ICs. The circuit has differential analog inputs and complementary logic outputs compatible with most forms of ECL. The output-current capability is adequate for driving terminated 50  $\Omega$  transmission lines. The low input offset and high resolution

make this comparator especially suitable for high-speed precision analog-to-digital processing.

A latch function is provided so that the comparator can be used in a sample-hold mode. If the Latch Enable input is HIGH, the comparator functions normally. If the Latch Enable is driven LOW, the comparator outputs are locked in their existing logic states. If the latch function is not used, the Latch Enable must be connected to ground.

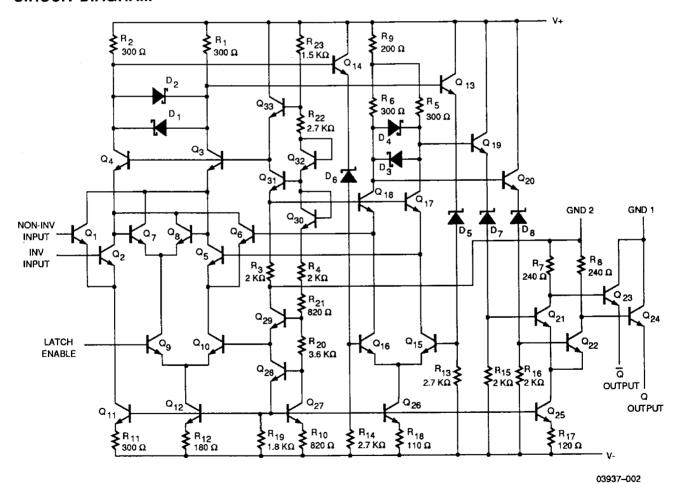

#### **CIRCUIT DIAGRAM**

Publication # 03937 Rev. C Amendment to issue Date: March, 1989

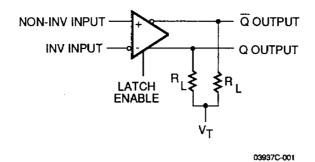

#### **FUNCTIONAL DIAGRAM**

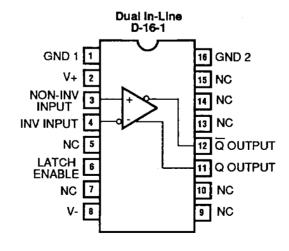

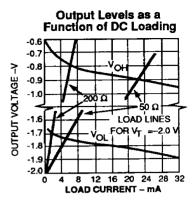

The outputs are open emitters, therefore external pulldown resistors are required. These resistors may be in the range of 50-200  $\Omega$  connected to -2.0 V, or 200-2000  $\Omega$  connected to -5.2 V.

03937-001

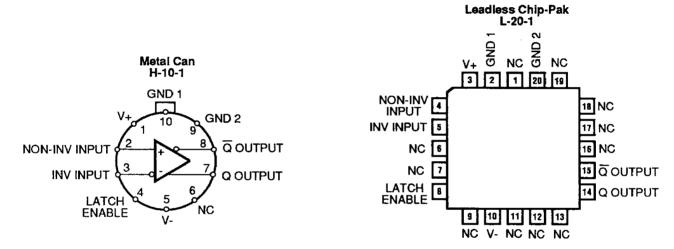

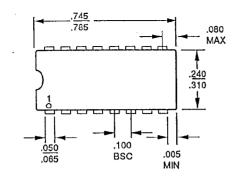

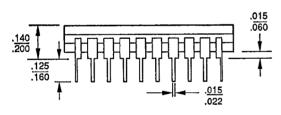

## CONNECTION DIAGRAMS Top View

Note 1 On metal package, pin 5 is connected to case. On DIP, pin 8 is connected to case.

03937-003

2-40 www.DataSheet4U.com

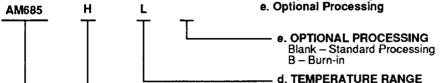

## ORDERING INFORMATION

#### Standard Products

AMD standard products are available in several packages and operating ranges. The ordering number (Valid

Combination) is formed by a combination of:

a. Device Number

b. Speed Option (if applicable)

c. Package Type

d. Temperature Range

L = Industrial (-30 to 85°C)

c. PACKAGE TYPE

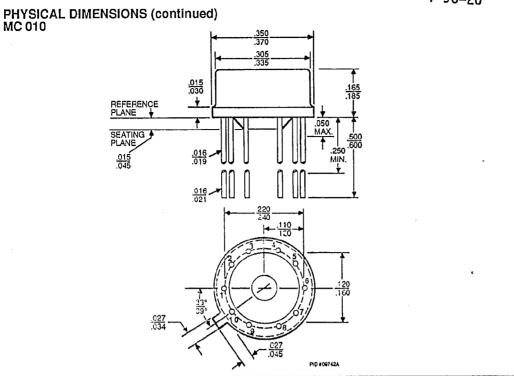

D = 16-Pin Ceramic DIP (CD 016) H = 10-Pin Metal Can (MC 010)

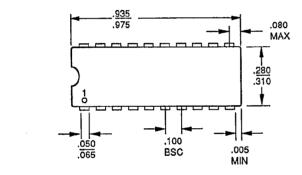

L = 20-Pin Ceramic Leadless Chip Carrier (CL 020)

X = Dice

**b. SPEED OPTION** a. DEVICE NUMBER/DESCRIPTION

**Valid Combinations** HL, DL, LMB, AM685

Am685

Voltage Comparator

XL, XM

Not Applicable

#### Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

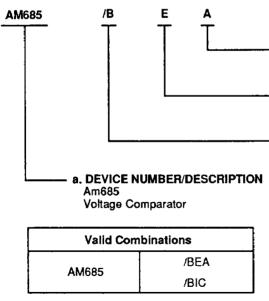

#### **MILITARY ORDERING INFORMATION**

#### **APL Products**

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. APL (Approved Products List products are fully compliant with MIL-M-38510 and MIL-STD-883C requirements. The order number (Valid Combination) for APL products is formed by a combination of: a. Device Number

b. Speed Option (if applicable)

f. Device Class

g. Package Type

h. Lead Finish

h. LEAD FINISH

A = Hot Solder Dip

C = Gold

g. PACKAGE TYPE (PER 09-000)

E = 16-Pin Ceramic DIP (CD 016) I = 10-Pin Metal Can (MC 010)

f. DEVICE CLASS /B = Class B

**b. SPEED OPTION**

## Not Applicable

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check on newly released combinations.

Valid Combinations

### **Group A Tests**

Group A Tests consist of sub-groups 1, 2, 3, 4, 5,

#### **MAXIMUM RATINGS**

Positive Supply Voltage +7 V

Negative Supply Voltage -7 V

Input Voltage ±4 V

Differential Input Voltage ±6 V

Minimum Operating Voltage

(V+ to V-) 9.7 V

Output Current 30 mA

Power Dissipation (Note 2) Storage Temperature

Range

-65°C to +150°C

Lead Temperature

(Soldering, 60 sec.)

300°C

500 mW

\* To duplicate high power steady state operation, parts are pulse tested at these correlated temperatures:  $685 \, L = -10^{\circ} \, C$

to  $+105^{\circ}C$ , 685 M = -35C to  $+145^{\circ}C$

#### **Operating Temperature Range**

Am685-L\* -30°C to +85°C Am685-M\* -55°C to +125°C Die Size .032" x .054"

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

Over the operating temperature ranges (unless otherwise specified)

#### DC Characteristics (Included in Group A, Subgroup 1,2,3,4,5,6, unless noted)

| Parameter | Parameter                                                     | Test Conditions                                                                                                  | Am685-L                    |                            | Am685-M                    |                            | Unit     |

|-----------|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------|----------------------------|----------------------------|----------|

| Symbol    | Description                                                   |                                                                                                                  | Min.                       | Max.                       | Min.                       | Max.                       |          |

| Vos       | Input Offset Voltage                                          | $\begin{array}{l} Rs = 100 \; \Omega, \; T_A = 25^{\circ}C \\ Rs = 100 \; \Omega \end{array}$                    | -2.0<br>-2.5               | +2.0<br>+2.5               | -2.0<br>-3.0               | +2.0<br>+3.0               | m∨<br>m∨ |

| ΔVos/Δτ   | Average Temperature<br>Coefficient of Input Offset<br>Voltage | Rs = 100 Ω (Note 6)                                                                                              | -10                        | +10                        | -10                        | +10                        | μV/°C    |

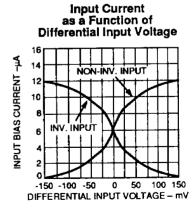

| los       | Input Offset Current                                          | T <sub>A</sub> = 25°C                                                                                            | -1.0<br>-1.3               | +1.0<br>+1.3               | -1.0<br>-1.6               | +1.0<br>+1.6               | μΑ<br>μΑ |

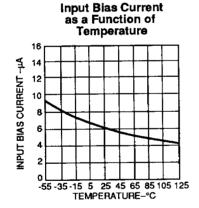

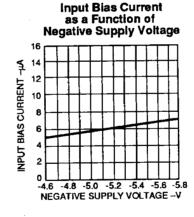

| lв        | Input Bias Current                                            | Ta = 25°C                                                                                                        |                            | 10<br>13                   |                            | 10<br>16                   | μΑ<br>μΑ |

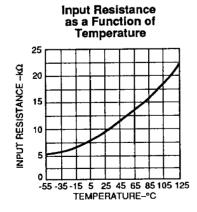

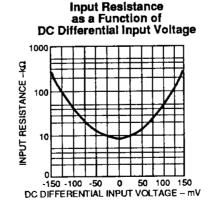

| Rin       | Input Resistance                                              | T <sub>A</sub> = 25°C (Note 5)                                                                                   | 6.0                        |                            | 6.0                        |                            | kΩ       |

| Cin       | Input Capacitance<br>(Note 1)                                 | Ta = 25°C                                                                                                        |                            | 3.0                        |                            | 3.0                        | pF       |

| Vсм       | Input Voltage Range                                           |                                                                                                                  | -3.3                       | +3.3                       | -3.3                       | +3.3                       | ٧        |

| CMMR      | Common Mode<br>Rejection Ratio                                | Rs = 100 $\Omega$ ,<br>-3.3 <vcм<+3.3 td="" v<=""><td>80</td><td></td><td>80</td><td></td><td>dB</td></vcм<+3.3> | 80                         |                            | 80                         |                            | dB       |

| SVRR      | Supply Voltage<br>Rejection Ratio                             | Rs = $100 \Omega$ , $\Delta Vs = \pm 5$                                                                          | 60                         |                            | 60                         |                            | dB       |

| Vон       | Output HIGH Voltage                                           | TA = TA (min) TA = TA (max) TA = 25°C                                                                            | -1.060<br>-0.890<br>-0.960 | -0.890<br>-0.700<br>-0.810 | -1.100<br>-0.850<br>-0.960 | -0.920<br>-0.620<br>-0.810 | ><br>>>  |

| Vol       | Output LOW Voltage                                            | TA = TA (min) TA = TA (max) TA = 25°C                                                                            | -1.890<br>-1.825<br>-1.850 | -1.675<br>-1.625<br>-1.650 | -1.910<br>-1.810<br>-1.850 | -1.690<br>-1.575<br>-1.650 | >>>      |

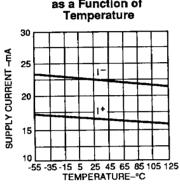

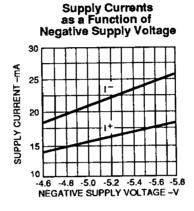

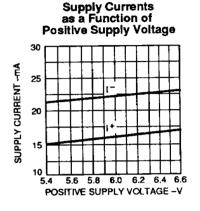

| l+        | Positive Supply Current                                       |                                                                                                                  |                            | 22                         |                            | 22                         | m        |

| l-        | Negative Supply Current                                       |                                                                                                                  |                            | 26                         |                            | 26                         | mΑ       |

| Poiss     | Power Dissipation                                             |                                                                                                                  |                            | 300                        |                            | 300                        | mW       |

#### Switching Characteristics (Vin = 100 mV, Vod = 5 mV) Included in Group A subgroup unless noted.

| Parameter<br>Symbol  | Parameter<br>Description                        | Test Conditions                       | Am685-L    |            | Am685-M    |            | Unit     |

|----------------------|-------------------------------------------------|---------------------------------------|------------|------------|------------|------------|----------|

|                      |                                                 |                                       | Min.       | Max.       | Min.       | Max.       |          |

| t <sub>pd+</sub>     | Input to Output HIGH (Note 6)                   | Ta (min) < Ta < 25°C<br>Ta = Ta (max) | 4.5<br>5.0 | 6.5<br>9.5 | 4.5<br>5.5 | 6.5<br>12  | ns<br>ns |

| t <sub>pd</sub>      | Input to Output LOW<br>(Note 6)                 | Ta (min) < Ta < 25°C<br>Ta = Ta (max) | 4.5<br>5.0 | 6.5<br>9.5 | 4.5<br>5.5 | 6.5<br>12  | ns<br>ns |

| t <sub>pd+</sub> (E) | Latch Enable to<br>Output HIGH<br>(Note 4)      | TA (min) < TA < 25°C<br>TA = TA (max) | 4.5<br>5.0 | 6.5<br>9.5 | 4.5<br>5.5 | 6.5<br>12  | ns<br>ns |

| t <sub>pd-</sub> (E) | Latch Enable to<br>Output LOW<br>(Note 4)       | TA (min) < TA < 25°C<br>TA = TA (max) | 4.5<br>5.0 | 6.5<br>9.5 | 4.5<br>5.5 | 6.5<br>12  | ns<br>ns |

| ts                   | Minimum Set-up Time<br>(Note 4)                 | TA (min) < TA < 25°C<br>TA = TA (max) |            | 3.0<br>4.0 |            | 3.0<br>6.0 | ns<br>ns |

| th                   | Minimum Hold Time<br>(Note 4)                   | TA (min) < TA < TA (max)              |            | 1.0        |            | 1.0        | ns       |

| t <sub>pw</sub> (E)  | Minimum Latch<br>Enable Pulse<br>Width (Note 4) | TA (min) < TA < 25°C<br>TA = TA (max) |            | 3.0<br>4.0 |            | 3.0<br>5.0 | ns<br>ns |

#### Notes:

- 1) For MC only; CERDIP = 7 pF.

- 2) For the metal can package, derate at 6.8 mW/°C for operation at ambient temperatures above +100°C; for the dual in-line package, derate at 9 mW/°C for operation at ambient temperatures above +105°C.

- 3) Unless otherwise specified V<sub>+</sub> = 6.0 V, V<sub>-</sub> = -5.2 V, V<sub>τ</sub> = -2.0 V, and R<sub>L</sub> = 50 Ω; all switching characteristics are for a 100 mV input step with 5 mV overdrive. The specifications given for V<sub>os</sub>, I<sub>os</sub>, I<sub>B</sub>, CMMR, SVRR, t<sub>pd+</sub> and t<sub>pd-</sub> apply over the full V<sub>cm</sub> range and for ±5 supply voltages. The Am685 is designed to meet the specifications given in the table after thermal equilibrium has been established with a transverse air flow of 500 LFPM or greater.

- 4) Owing to the difficult and critical nature of switching measurements involving the latch, these parameters cannot be tested in production. Engineering data indicates that at least 95% of the units will meet specifications given.

- 5) Guaranteed, not tested.

- 6) Not 100% tested. Group A only.

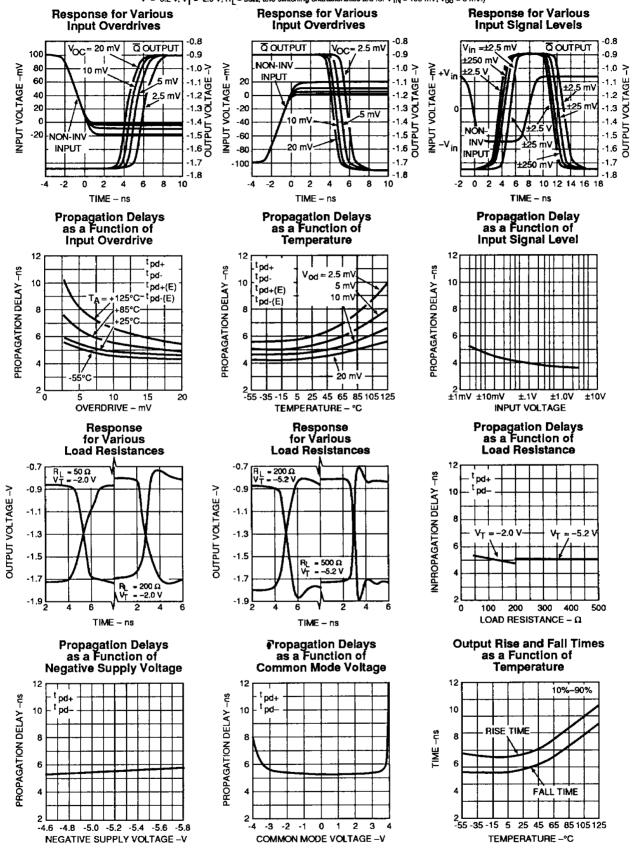

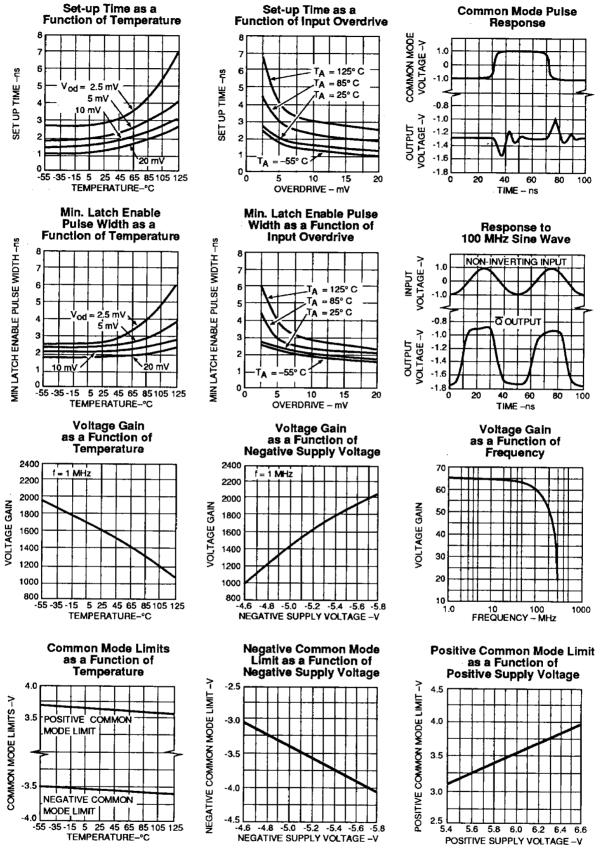

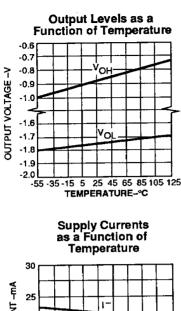

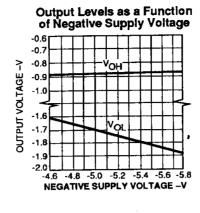

#### **PERFORMANCE CURVES**

(Unless otherwise specified, standard conditions for all curves are  $T_A = 25^{\circ}C$ ,  $V_+ = 6.0 \text{ V}$ ,  $V_- = -5.2 \text{ V}$ ,  $V_- = -2.0 \text{ V}$ ,  $R_1 = 50\Omega$ , and switching characteristics are for  $V_{IN} = 100 \text{ mV}$ ,  $V_{od} = 5 \text{ mV}$ .)

#### **PERFORMANCE CURVES, (Continued)**

#### **PERFORMANCE CURVES, (Continued)**

03937-007

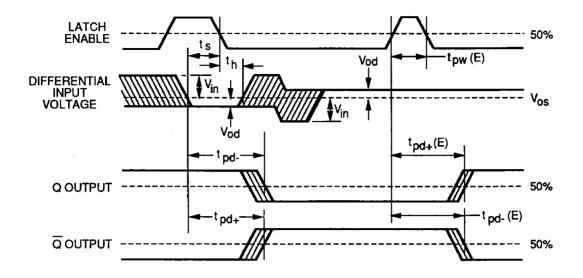

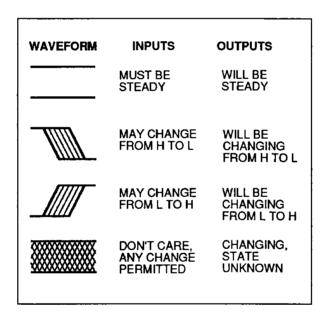

#### **TIMING DIAGRAMS**

03937-008

Figure 1.

The set-up and hold times are a measure of the time required for an input signal to propagate through the first stage of the comparator to reach the latching circuitry.

Input signal changes occurring before to will be detected and held; those occurring after to will not be detected. Changes between to and to may or may not be detected.

#### **DEFINITION OF TERMS**

- Vos INPUT OFFSET VOLTAGE That voltage which must be applied between the two input terminals through two equal resistances to obtain zero voltage between the two outputs.

- $\Delta V_{os}/\Delta \tau$  AVERAGE TEMPERATURE COEFFICIENT OF INPUT OFFSET VOLTAGE The ratio of the change in input offset voltage over the operating temperature range to the temperature range.

- los INPUT OFFSET CURRENT The difference between the currents into the two input terminals when there is zero voltage between the two outputs.

- In Input BIAS CURRENT The average of the two input currents.

- Rin INPUT RESISTANCE The resistance looking into either input terminal with the other grounded.

- CIN INPUT CAPACITANCE The capacitance looking into either input terminal with the other grounded.

- Vcm INPUT VOLTAGE RANGE The range of voltages on the input terminals for which the offset and propagation delay specifications apply.

- CMRR COMMON MODE REJECTION RATIO —

The ratio of the input voltage range to the peak-to-peak change in input offset voltage over this range.

- SVRR SUPPLY VOLTAGE REJECTION RATIO —

The ratio of the change in input offset voltage to the change in power supply voltages producing it.

- Voh OUTPUT HIGH VOLTAGE The logic HIGH output voltage with an external pull-down resistor returned to a negative supply.

- Vol. OUTPUT LOW VOLTAGE The logic LOW output voltage with an external pull-down resistor returned to a negative supply.

- POSITIVE SUPPLY CURRENT The current required from the positive supply to operate the comparator.

- I— NEGATIVE SUPPLY CURRENT The current required from the negative supply to operate the comparator.

- PDISS POWER DISSIPATION The power dissipated by the comparator with both outputs terminated in 50  $\Omega$  to -2.0 V.

#### **Switching Terms (refer to Figure 1)**

- tpd+ INPUT TO OUTPUT HIGH DELAY The propagation delay measured from the time the input signal crosses the input offset voltage to the 50 point of an output LOW to HIGH transition.

- tpd- INPUT TO OUTPUT LOW DELAY The propagation delay measured from the time the input signal crosses the input offset voltage to the 50 point of an output HIGH to LOW transition.

- t<sub>pd+</sub>(E) LATCH ENABLE TO OUTPUT HIGH DELAY The propagation delay measured from the 50 point of the Latch Enable signal LOW to HIGH transition to the 50 point of an output LOW to HIGH transition.

- t<sub>pd</sub>-(E)

LATCH ENABLE TO OUTPUT LOW DELAY

The propagation delay measured from the

50 point of the Latch Enable signal LOW to

HIGH transition to the 50 point of an output

HIGH to LOW transition.

- t. MINIMUM SET-UP TIME The minimum time before the negative transition of the Latch Enable signal that an input signal change must be present in order to be acquired and held at the outputs.

- th MINIMUM HOLD TIME The minimum time after the negative transition of the Latch Enable signal that the input signal must remain unchanged in order to be acquired and held at the outputs.

- t<sub>pw</sub>(E) MINIMUM LATCH ENABLE PULSE WIDTH

The minimum time that the Latch Enable signal must be HIGH in order to acquire and hold an input signal change.

#### Other Symbols

- T<sub>A</sub> Ambient temperature

- Rs Input source resistance

- Vs Supply voltages

- V+ Positive supply voltage

- V- Negative supply voltage

- V<sub>T</sub> Output load terminating voltage

- RL Output load resistance

- Vin Input pulse amplitude

- V<sub>od</sub> Input overdrive

- f Frequency

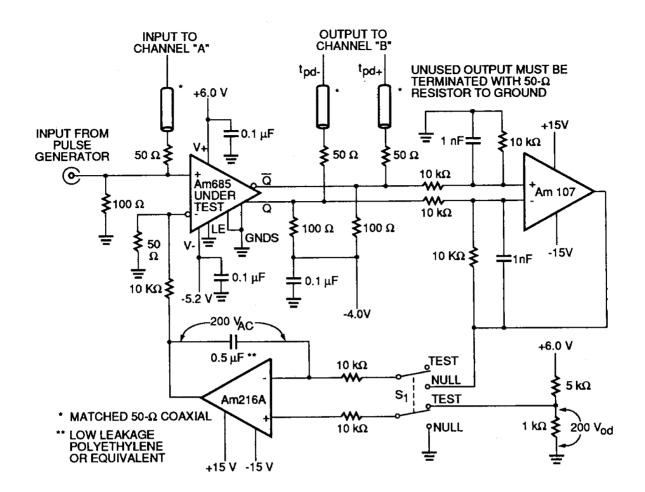

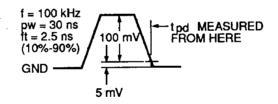

#### Measurement Of Propagation Delay

A voltage comparator must be able to respond to input signal levels ranging from a few millivolts to several volts, ideally with little variation in propagation delay. The most difficult condition is where the comparator has been driven hard into one state by a large signal, and the next input signal is just barely enough to make it switch to the other state. This forces the input stage of the circuit to swing from a full off (or on) state to a point somewhere near the center of its linear range, thus exercising both its large and small signal responses. If the comparator is fast for this condition, it should be as fast or faster for almost any other condition. The unofficial industry standard input signal is a 100 mV step with an overdrive of 5 mV (the overdrive is the voltage in excess of that needed to bring the output to the center of its dynamic range). The 100 mV is more than enough to fully turn on the input stage, but not so large to make measurement a problem. Large pulses would require exceptionally good control on waveform purity, since only a few tenths of a percent of overshoot or ripple would be enough to affect the value of the overdrive and, for sensitive comparators, result in false switching. The propagation delay is measured from the time the input signal crosses the input threshold voltage (i.e., the offset voltage) to the 50 point of either output. This definition ensures that each unit is measured under equal conditions, and also makes the measurement relatively independent of the input rise and fall times.

The test circuit of Figure 2 provides a means of automatically nulling out the offset voltage and applying the overdrive. With S1 in the "NULL" position, the feedback loop around the Am685 via the two operational amplifiers corrects for the offset of the circuit including any do shift in the ground level of the input signal. When switched to "TEST", the offset is held on the storage capacitor of the Am216A and the overdrive is added at the Am216A non-inverting input. The duty cycle of the signal is made low so that the presence of the input pulse during nulling will not disturb the offset. A solid ground plane is used for the test jig, and capacitors bypass the supply voltages. All power and signal leads are kept as short as possible. The Am685 input and output run directly into the 50  $\Omega$  inputs of the sampling scope via equal lengths of 50  $\Omega$  coaxial cable. For the conditions shown in the figure, tpd. is measured at the Q output and tpd- at the Q output. If it is desired to measure to opposite output polarities, the polarities of the input signal and overdrive must be reversed.

#### Thermal Considerations

To achieve the high speed of the Am685, a certain amount of power must be dissipated as heat. This increases the temperature of the die relative to the ambient temperature. In order to be compatible with ECL III and ECL 10,000, which normally use air flow as a means of package cooling, the Am685 characteristics are specified when the device has an air flow across the package of 500 linear feet per minute or greater. Thus, even though different ECL circuits on a printed circuit board may have different power dissipations, all will have the same input and output levels, etc., provided each sees the same air flow and air temperature. This eases design, since the only change in characteristics between devices is due to the increase in ambient temperature of the air passing over the devices. If the Am685 is operated without air flow, the change in electrical characteristics due to the increased die temperature must be taken into account.

#### Interconnection Techniques

All high-speed ECL circuits require that special precautions be taken for optimum system performance. The Am685 is particularly critical because it features very high gain (60 dB) at very high frequencies (100 MHz). A ground plane must be provided for a good, low inductance, ground current return path. The impedance at the inputs should be as low as possible and lead lengths as short as practical. It is preferable to solder the device directly to the printed circuit board instead of using a socket. Open wiring on the outputs should be limited to less than one inch, since severe ringing occurs beyond this length. For longer lengths, the printed-circuit interconnections become microstrip transmission lines when backed up by a ground plane, with a characteristic impedance of 50 to 150  $\Omega$ . Reflections will occur unless the line is terminated in its characteristic impedance. The termination resistors normally go to -2.0 V, but a Thevenin equivalent to V- can be used at some increase in power. Best results are usually obtained with the terminating resistor at the end of the driven line. The lower impedance lines are more suitable for driving capacitance loads. The supply voltages should be well decoupled with RF capacitors connected to the ground plane as close to the device supply pins as possible.

03937-009

Figure 2.

#### TYPICAL APPLICATIONS

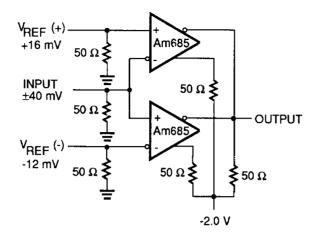

Typical Applications High-Speed Window Detector

03937-010

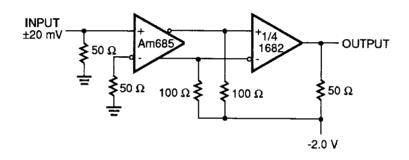

Typical Applications 300 MHz Line Receiver

03937-011

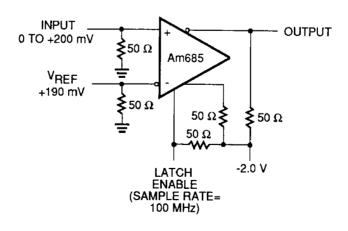

Typical Applications High-Speed Sampling

03937-012

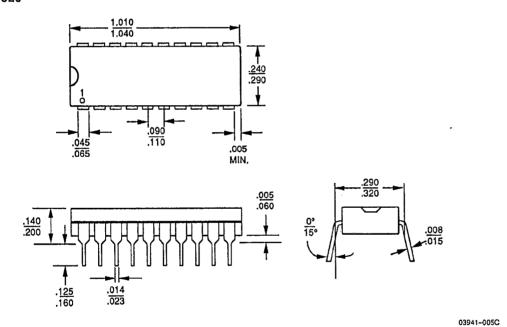

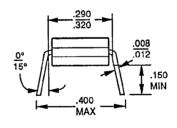

## PHYSICAL DIMENSIONS CD 016

07319B

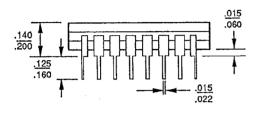

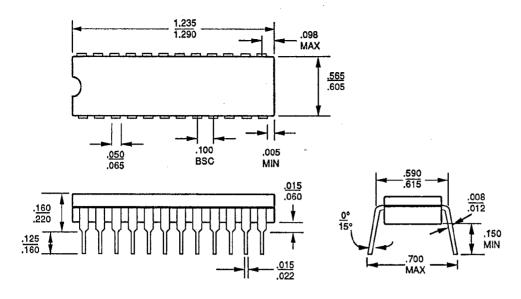

#### CD 020

03941-004C

T-90-20

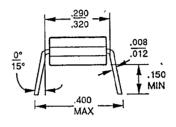

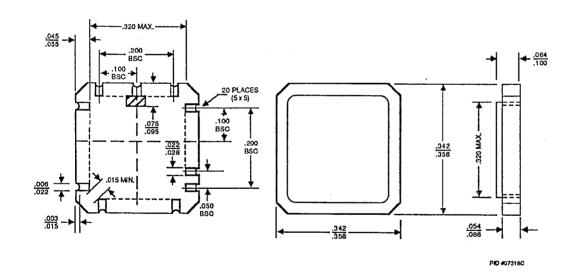

## PHYSICAL DIMENSIONS (continued) CD 024

03067-008A

#### **CL 020**

T-90-20

PD 020