# Am9516A

Universal DMA Controller (UDC)

## FINAL

## **DISTINCTIVE CHARACTERISTICS**

- Transfer Modes: Single, demand dedicated with bus hold, demand dedicated with bus release, demand interleave

- 16 MB physical addressing range

- Automatic loading/reloading of control parameters by each channel

- · Optional automatic chaining of operations

- Channel interleave operations

- Interleave operations with system bus

- Masked data pattern matching for search operations

- Vectored interrupts on selected transfer conditions

- Software DMA request

- Software or hardware wait state insertion

- Transfer up to 6.66 MB/second at 10 MHz clock

www.DataSheet4U.com

DataSheet4U.com

## **GENERAL DESCRIPTION**

The Am9516A Universal DMA Controller (UDC) is a high performance peripheral interface circuit for 8086 and 68000 CPUs. In addition to providing data block transfer capability between memory and peripherals, each of the UDC's two channels can perform peripheral-to-peripheral as well as memory-to-memory transfer. A special Search Mode of Operation compares data read from a memory or peripheral source to the content of a pattern register.

For all DMA operations (search, transfer, and transfer-and-search), the UDC can operate with either byte or word data sizes. In some system configurations it may be necessary to transfer between word-organized memory and a byte-oriented peripheral. The UDC provides a byte packing/unpacking capability through its byte-word funneling transfer or transfer-and-search option. Some DMA applications may continuously transfer data between the same two memory areas. These applications may not require the flexibility inherent in reloading registers from memory tables. To service these repetitive DMA operations, base registers are provided on each channel which re-initialize the current source and destination Address and Operation Count registers. To change the data transfer direction

under CPU control, provision is made for reassigning the source address as a destination and the destination as a source, eliminating the need for actual reloading of these address registers.

Frequently DMA devices must interface to slow peripherals or slow memory. In addition to providing a hardware WAIT input, the Am9516A UDC allows the user to select independently for both source and destination addresses and automatic insertion of 0, 1, 2 or 4 wait states. The user may even disable the WAIT input pin function altogether and use these software programmed wait states exclusively.

High throughput and powerful transfer options are of limited usefulness if a DMA requires frequent reloading by the host CPU. The Am9516A UDC minimizes CPU interactions by allowing each channel to load its control parameters from memory into the channel's control registers. The only action required of the CPU is to load the address of the control parameter table into the channel's Chain Address register and then issue a "Start Chain" Command to start the register loading operation.

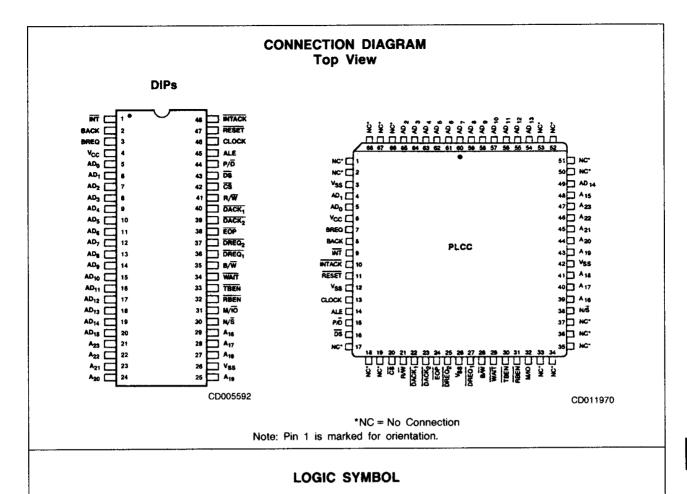

The Am9516A UDC is packaged in a 48-pin DIP and uses a single +5 V Power Supply.

et4U.com

DataSheet4U.com

DataShe

2-156 Am9516A

ataSheet4U.com www.DataSheet4U.com

et4U.com \*DataSheet4U AD AD. A<sub>19</sub> UPPER A<sub>20</sub> AD AD, A<sub>21</sub> AD<sub>6</sub> A22 AD-ADDRESS DATA BUS AD<sub>8</sub> M/IŌ AD N/Š AD<sub>10</sub> STATUS B/W AD<sub>11</sub> R/W AD<sub>12</sub> TBEN AD<sub>13</sub> RBEN AD<sub>14</sub> P/Ö AD<sub>15</sub> BUS CONTROL BREQ BACK DREQ, DREQ **Շ**\$ DACK<sub>1</sub>, DACK<sub>2</sub> EOP RESET DS. INTACK ALE +57 GND CLOCK LS001331

Am9516A

2-157

DataSheet4U.com

www.DataSheet4U.com

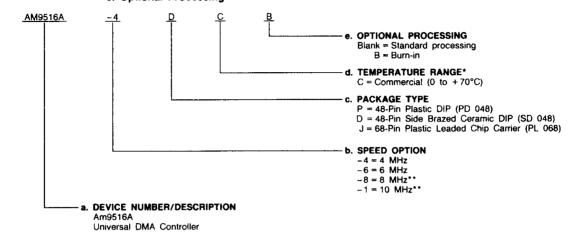

## ORDERING INFORMATION

#### **Standard Products**

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of: a. Device Number

- b. Speed Option (if applicable)

- c. Package Type

- d. Temperature Range

- e. Optional Processing

| Valid C   | Valid Combinations |  |  |  |

|-----------|--------------------|--|--|--|

| AM9516A-4 |                    |  |  |  |

| AM9516A-6 | DC, DCB, PC, JC    |  |  |  |

| AM9516A-8 |                    |  |  |  |

| AM9516A-1 | DC                 |  |  |  |

## **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

DataSheet4U.com

\*\*Preliminary; to be announced.

DataShe

2-158 Am9516A

DataSheet4U.com www.DataSheet4U.com

<sup>\*</sup>This device is also available in Military temperature range.

## 2

# DataShe

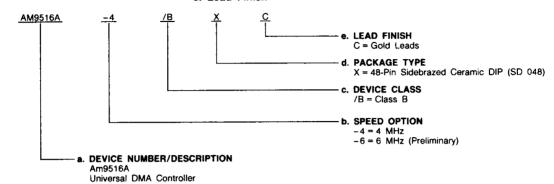

## MILITARY ORDERING INFORMATION

## **APL Products**

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. APL (Approved Products List) products are fully compliant with MIL-STD-883C requirements. The order number (Valid Combination) for APL products is formed by a combination of: **a. Device Number**

- b. Speed Option (if applicable)

- c. Device Class

- d. Package Type

- e. Lead Finish

Am9516A

## **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

## **Group A Tests**

Group A tests consist of Subgroups DataSheet4U.com 1, 2, 3, 7, 8, 9, 10, 11.

| Valid     | Com | binations |  |

|-----------|-----|-----------|--|

| AM9516A-4 | *** | /BXC      |  |

et4U.com

www.DataSheet4U.com

2-159

| Pin No. | Name                               | 1/0 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------|------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4       | Vcc                                |     | +5 V Power Supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 26      | V <sub>SS</sub>                    | Ì   | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 46      | CLOCK                              | 1   | Clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

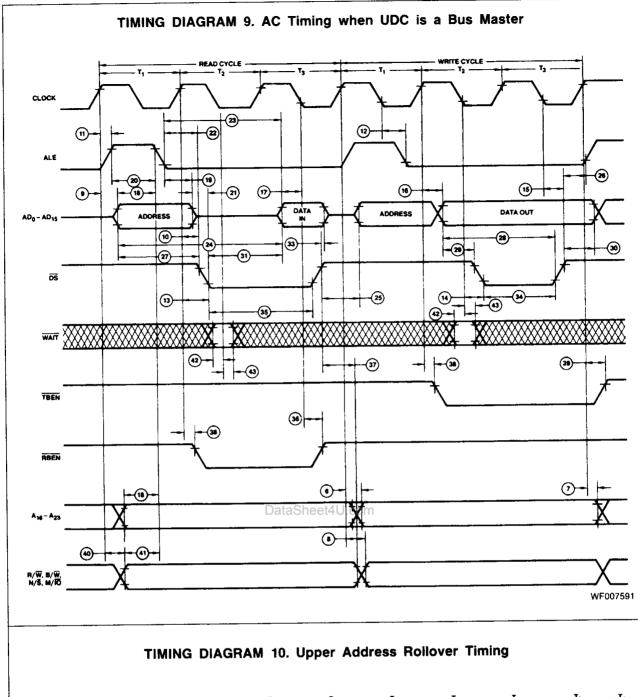

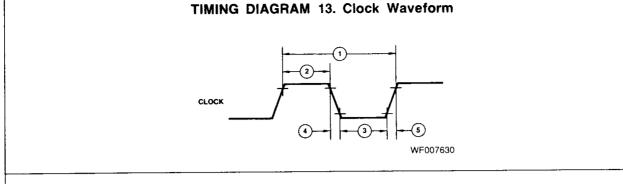

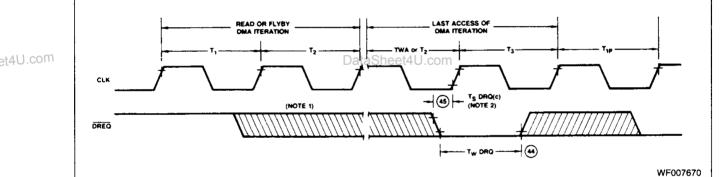

| 46      | CLOCK                              | l   | (Clock). The Clock signal controls the internal operations and the rates of data transfers. It is usuall derived from a master system clock or the associated CPU clock. The Clock input requires a high voltage input signal. Many UDC input signals can make transitions independent of the UDC clock; these signals can be asynchronous to the UDC clock. On other signals, such as WAIT inputs, transitions must meet setup and hold requirements relative to the UDC clock. See the Timing diagrams for details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5-20    | AD <sub>0</sub> – AD <sub>15</sub> | 1/0 | (Address-Data Bus, Three-State). The Address Data Bus is a time-mulitiplexed, bidirectional, active high, three-state bus used for all I/O and memory transactions. HIGH on the bus corresponds to 1 and LOW corresponds to 0. AD <sub>0</sub> is the least significant bit position and AD <sub>15</sub> is the most significant. The presence of addresses is defined by the timing edge of ALE, and the asserted or requested presence data is defined by the DS signal. The status output lines M/IO and N/S indicate the type of transaction either memory or I/O. The R/W line indicates the direction of the transaction. When the UDC is in control of the system bus, it dominates the AD Bus; when the UDC is not in control of the system bus the CPU or other external devices dominate the AD Bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|         |                                    |     | The presence of address of data on the $AD_0$ – $AD_{15}$ bus is defined only by ALE and $\overline{DS}$ . When the UDC is not in control of the bus, there is no required relation between the presence of address or data and the UDC clock. This allows the UDC to be used with a system bus which does not have a bussed clock signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

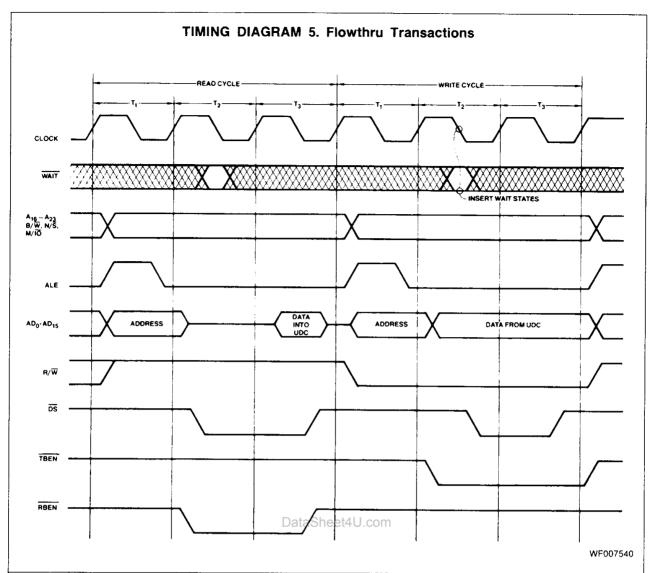

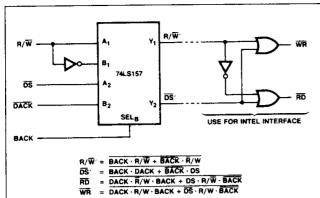

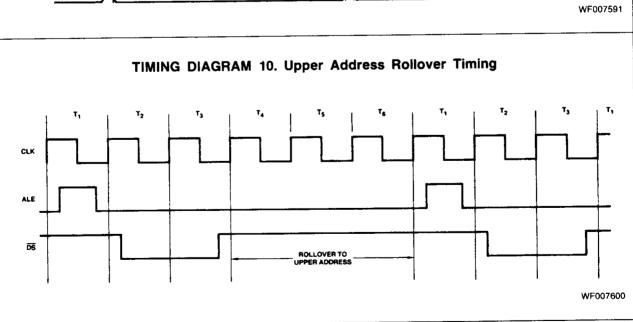

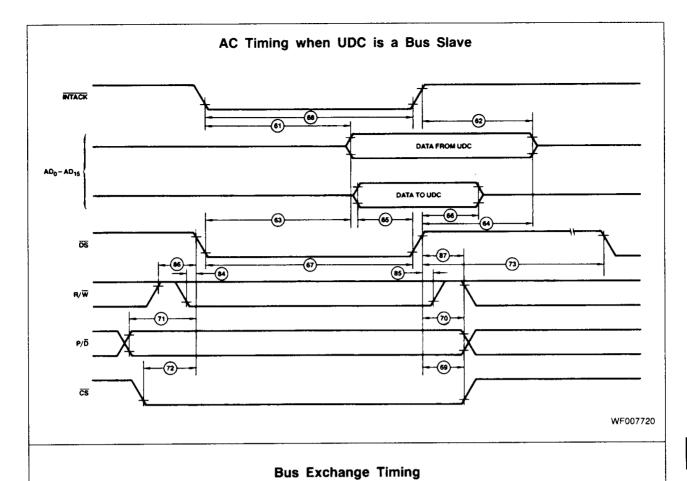

| 43      | চ্s                                | 1/0 | (Data Strobe, Three-State). Data Strobe is a bidirectional, active-low, three-state signal. A LOW on this signal indicates that the $AD_0 - AD_{15}$ bus is being used for data transfer. When the UDC is not in control of the system bus and the external system is transferring information to or from the UDC, $\overline{DS}$ is a timing input used by the UDC to move data to or from the $AD_0 - AD_{15}$ bus. Data is written into the UDC by the external ststem on the LOW-to-HIGH $\overline{DS}$ transition. Data is read from the UDC by the external system while $\overline{DS}$ is LOW. There are no timing requirements between $\overline{DS}$ as an input and the UDC clock; this allows use of the UDC with a system bus which does not have a bussed clock. During a DMA operation when the UDC is in control of the ststem, $\overline{DS}$ is an output generated by the UDC and used by the system to move data to or from the $AD_0 - AD_{15}$ bus. When the UDC has bus control, it writes to the external system by placing data on the $AD_0 - AD_{15}$ bus before the HIGH-to LOW $\overline{DS}$ transition and holding the data stable until after the LOW-to-HIGH $\overline{DS}$ transition; while reading from the external system, the LOW to-HIGH transition of $\overline{DS}$ inputs data from the $AD_0 - AD_{15}$ bus into the UDC (see Timing diagram) |

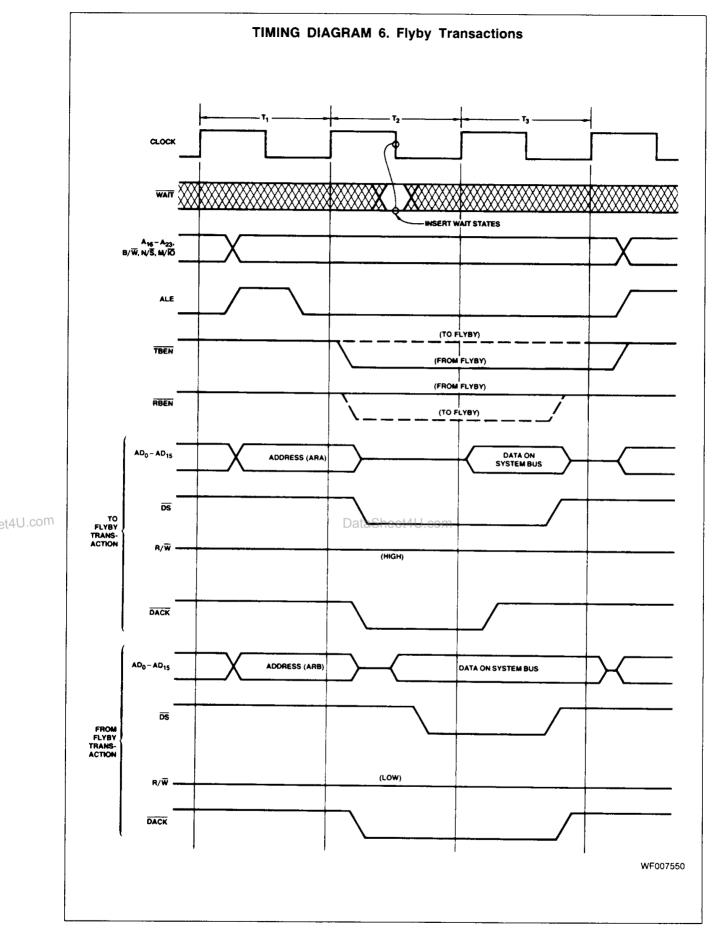

| 41      | R∕₩                                | 1/0 | (Read/Write, Three-State). Read/Write is a bidirectional, three-state signal. Read polarity is HIGH and write polarity is LOW. R/W indicates the data direction of the current bus transaction, and is stable starting when ALE is HIGH until the bus transaction ends (see Timing diagram). When the UDC is not it control of the system bus and the external system is transferring information to or from the UDC, R/W is a status input used by the UDC to determine if data is entering or leaving on the AD <sub>0</sub> – AD <sub>15</sub> bus during DS time. In such a case, Read (HIGH) indicates that the system is requesting data from the UDC, and Write (LOW) indicates that the system is presenting data to the UDC. There are no timing requirements between R/W as an input and the UDC clock, transitions on R/W as an input are only defined relative to DS. When the UDC is in control of the system bus, R/W is an output generated by the UDC, with Real indicating that data is being requested from the addressed location or device, the addressed location or device and Write indicating that data is being presented to the addressed location or device. Flyby DM/ operations are a special case where R/W is valid for the normally addressed memory or peripheral locations and must be interpreted in reverse by the "Flyby" peripheral that uses it.          |

| 33      | TBEN                               | 0   | (Transmit Buffer Enable, Open Drain). Transmit Buffer Enable is an active-low, open drain output. When UDC is a bus master, a LOW on this output indicates that the data is being transferred from the UDC to the data bus lines through the buffer. The purpose of this signal is to eliminate bus contention. When UDC is not in control of the system bus, these pins float to three-state OFF.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 32      | RBEN                               | 0   | (Receive Buffer Enable, Open Drain). Receive Buffer Enable is an active-low, open drain output. When UDC is in control of system bus, a LOW on this output indicates that the data is being transferred from the data bus lines to the UDC through the buffer. The purpose of this signal is to eliminate but contention. This pin floats to three-state OFF when the UDC is not in control of the system bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 45      | ALE                                | 0   | (Address Latch Enable). This active HIGH signal is provided by the UDC to latch the address signal $AD_0 - AD_{15}$ into the address latch. This pin is never floated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 44      | ₽/̄Ū                               | '   | (Pointer/Data). Pointer/Data is an input signal to indicate the information is on the AD <sub>0</sub> – AD <sub>15</sub> bus only when the UDC is the bus slave. A HIGH on this signal indicates the information is on the AD bus is an address of the internal register to be accessed. The data on the AD bus is loaded into the Pointer register of UDC. A LOW on this signal indicates that a data transfer is taking place between the bus any the internal register designated by the Pointer register. Note that if a transaction is carried out with R/V HIGH and P/D HIGH, the contents of the Pointer register will be read.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 31      | M/ĪŌ                               | 0   | (Memory/Input-Output, Three-State). This signal specifies the type of transaction. A HIGH on this pin indicates a memory transaction. A LOW on this pin indicates an I/O transaction. It floats to three-state OFF when UDC is not in control of the ststem bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 30      | N/S                                | 0   | (Normal/System, Three-State). This output is a three-state signal activated only when the UDC is the bus master. Normal is indicated when N/\$\overline{S}\$ is HIGH, and System is indicated when N/\$\overline{S}\$ is LOW. This signal supplements the M/\$\overline{IO}\$ line and is used to indicate which memory or I/O space is being accessed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 35      | B∕₩                                | 0   | (Byte/Word, Three-State). This output indicates the size of data transferred on the AD $_0$ – AD $_{15}$ bus HIGH indicates a byte (8-bit) and LOW indicates a word (16-bit) transfer. This output is activated when ALE is HIGH and remains valid for the duration of the whole transaction (see Timing diagram). All word sized data are word-aligned and must be addressed by even addresses (A $_0$ = 0). When addressing byte read transactions, the least significant address bit determines which byte is needed; an even address specifies the most significant byte (AD $_0$ – AD $_1$ ). (Note that the higher address specifies the least significant byte (AD $_0$ – AD $_1$ ). (Note that the higher address specifies the least significant byte) This addressing mechanism applies to memory accesses as well as I/O accesses. When the UDC is a slave, it ignore:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

2-160 Am9516A

DataSheet4U.com www.DataSheet4U.com

DataSheet4U.com

et4U.com

DataShe

|                    | PIN DESCRIPTION (continued)           |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|--------------------|---------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin No.            | Name                                  | 1/0 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| 42                 | CS .                                  | 1   | (Chip Select). This pin is an active-low input. A CPU or other external device uses $\overline{CS}$ to activate the UDC for reading and writing of its internal registers. There are no timing requirements between the $\overline{CS}$ input and the UDC clock; the $\overline{CS}$ input timing requirements are only defined relative to $\overline{DS}$ . This pin is ignored when UDC is in control of system bus.                                                                                                                                                                                                                                            |  |  |  |  |

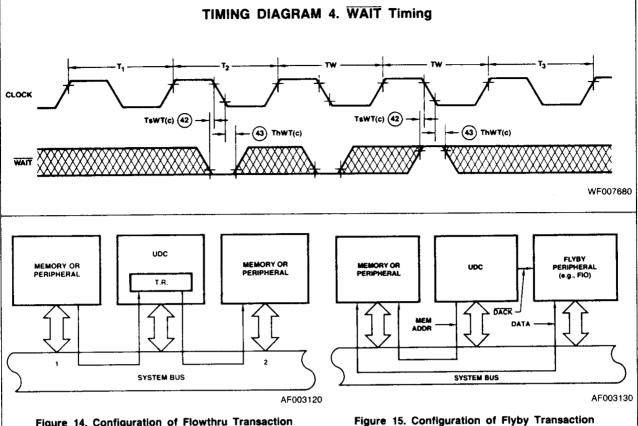

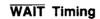

| 34                 | WAIT                                  | ı   | (WAIT). This pin is an active-low input. Slow memories and peripheral devices may use WAIT to extend DS and RBEN or TBEN during operation. Unlike the CS input, transitions on the WAIT input must meet certain timing requirements relative to the UDC clock. See Timing Diagram 4 for details. The Wait function may be disabled using a control bit in the Master Mode register (MM2).                                                                                                                                                                                                                                                                          |  |  |  |  |

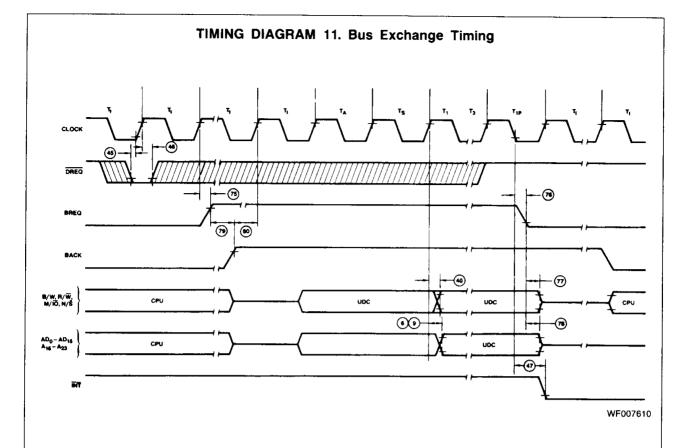

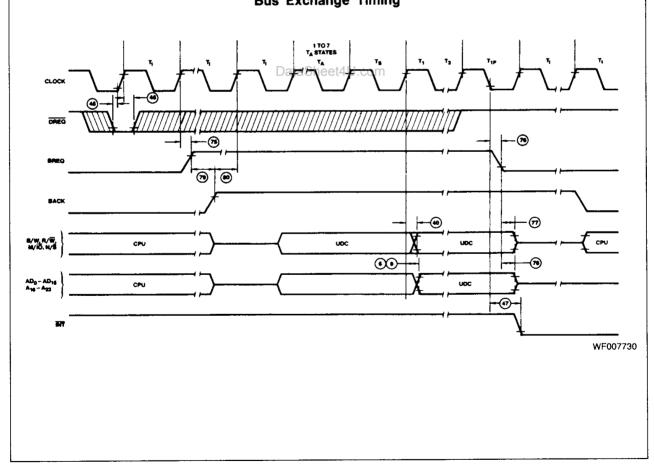

| 3                  | BREQ                                  | 0   | (Bus Request). Bus Request is an active-HIGH signal signal used by the UDC to obtain control of the bus from the CPU. BREQ lines from multiple devices are connected to a priority encoder.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| 2                  | BACK                                  | l   | (Bus Acknowledge). BACK is an active-HIGH, asynchronchronous input, indicating that the CPU has relinquished the bus and that no higher priority device has assumed bus control. Since BACK is internally synchronized by the UDC before being used, transitions on BACK do not have to be synchronous with the UDC clock. The BACK input is usually connected to the HLDA line from the CPU or to the output of a priority decoder.                                                                                                                                                                                                                               |  |  |  |  |

| 1                  | INT                                   | 0   | (Interrupt Request, Open Drain). Interrupt Request is an active-low output used to interrupt the CPU. It is driven LOW whenever the IP and CIE bits of the Status Register are set. It is cleared by UDC after receiving a clear IP command.                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

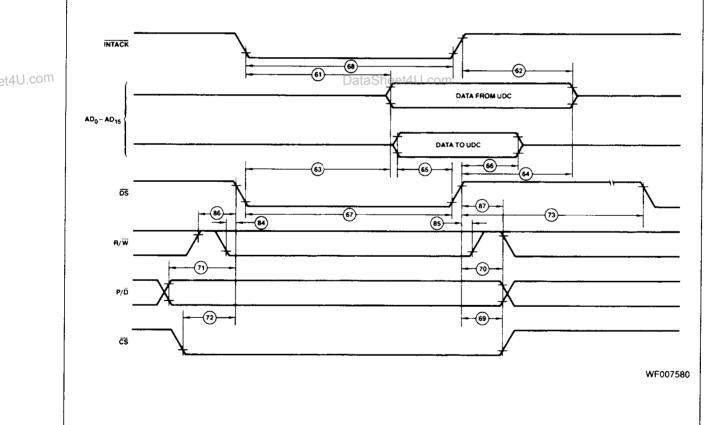

| 48                 | INTACK                                | ı   | (Interrupt Acknowledge). Interrupt Acknowledge is an active-low input indicating that the request for interrupt has been granted. The UDC will place a vector onto the AD bus if the No Vector or Interrupt bit (MM3) is reset.                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

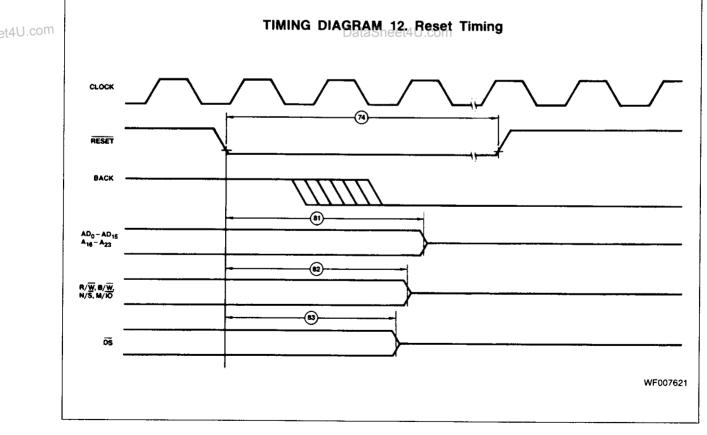

| 47                 | RESET                                 | 1   | (Reset). Reset is an active-low input to disable the UDC and clear its Master Mode register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 36, 37             | DREQ <sub>1</sub> , DREQ <sub>2</sub> | 1   | (DMA Request). The DMA Request lines are two active-low inputs, one per channel. They may make transitions independent of the UDC clock and are used by external logic to initiate and control DMA operations performed by the UDC.                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

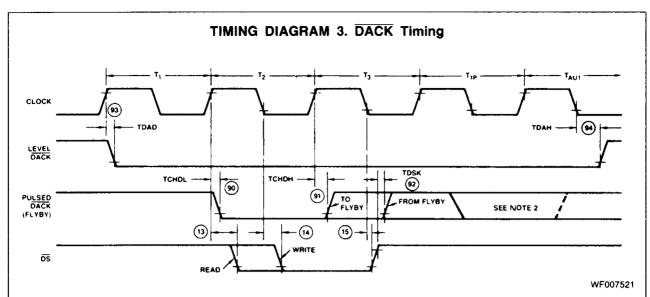

| 40, 39             | DACK <sub>1</sub> , DACK <sub>2</sub> | 0   | (DMA Acknowledge). The DMA Acknowledge lines are active-low outputs, one per channel, which indicate that the channel is performing a DMA operation. DACK is pulsed, held active or held inactive during DMA operations as programmed in the Channel Mode register. For Flowthru operations, the peripheral is fully addressed using the conventional I/O addressing protocols and therefore may choose to ignore DACK. DACK is always output as programmed in the Channel Mode register for a DMA operation, even when the operation is intiated by a CPU software request command or as a result of chaining. DACK is not output during the chaining operations. |  |  |  |  |

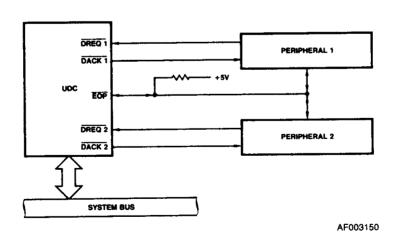

| 38                 | EOP                                   | 1/0 | (End of Process). <u>EOP</u> is an active-low, open-drain, bidirectional signal. It must be pulled up with an external resistor of 1.8 kohm or more. The UDC emits an output pulse on <u>EOP</u> when a TC or MC termination occurs, as defined later. An external source may terminate a DMA operation in progress by driving <u>EOP</u> low. <u>EOP</u> always applies to the active channel; if no channel is active, <u>EOP</u> is ignored.                                                                                                                                                                                                                    |  |  |  |  |

| 29 - 27<br>25 - 21 | A <sub>16</sub> - A <sub>23</sub>     | 0   | (Upper Address Bus, Three-state). The A <sub>16</sub> – A <sub>23</sub> address lines are three-state outputs activated only when the UDC is controlling the system bus. Combined with the lower 16 address bits appearing on AD <sub>0</sub> through AD <sub>15</sub> respectively, this 24-bit linear address allows the UDC to access anywhere within 16 megabytes of memory.                                                                                                                                                                                                                                                                                   |  |  |  |  |

Note: All inputs to the UDC, except the clock, are directly TTL compatible.

Am9516A 2-161

DataSheet4U.com www.DataSheet4U.com

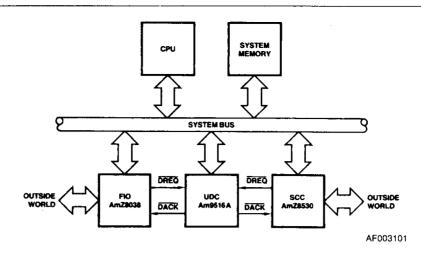

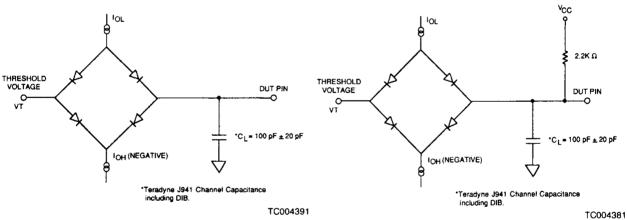

Figure 1. UDC Configurations

## **PRODUCT OVERVIEW**

## **Register Description**

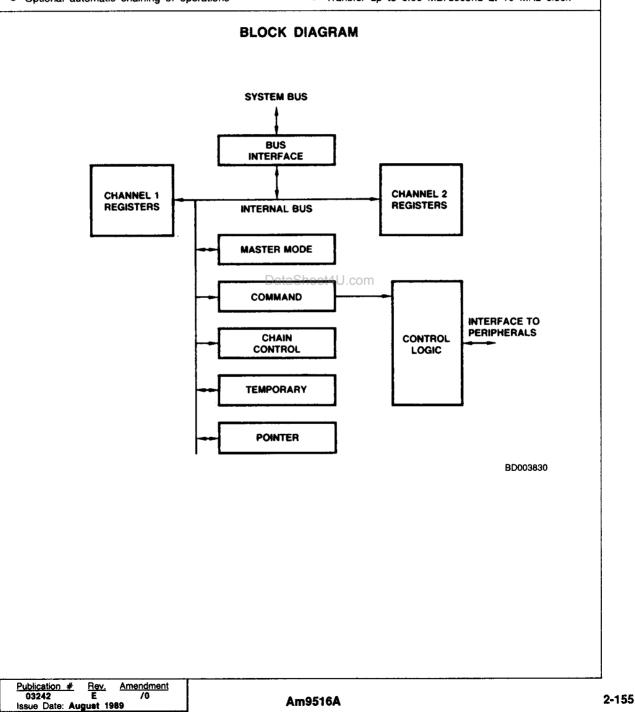

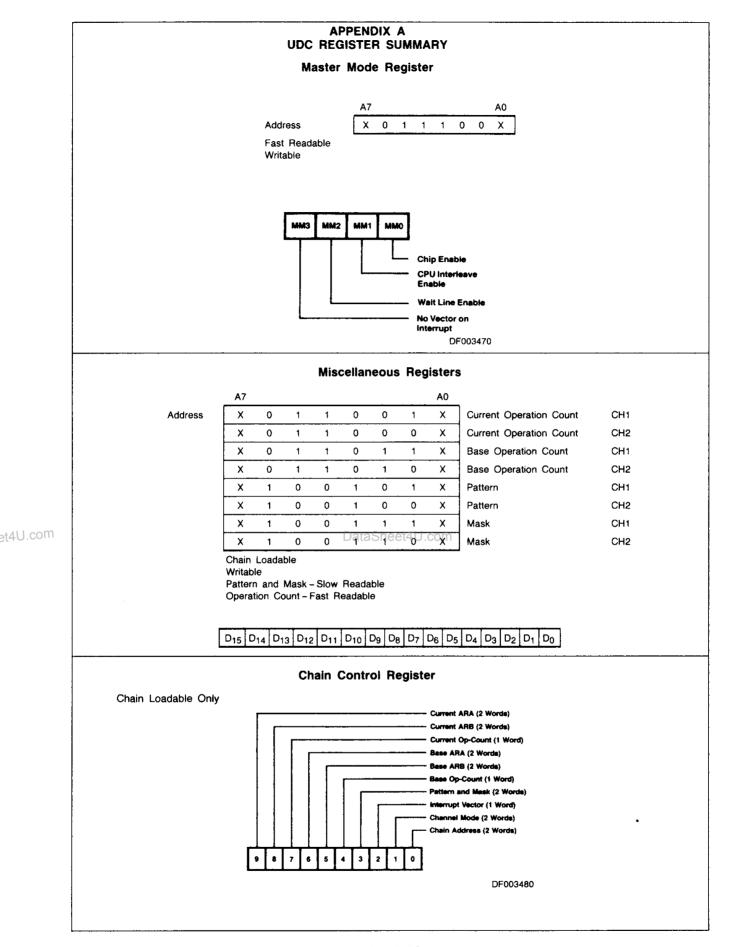

The Am9516A UDC Block Diagram illustrates the internal registers. Figure 2 lists each register along with its size and read/write access restrictions. Registers which can be read by the CPU are either fast (F) or slow (S) readable. Fast registers can be read by a normal CPU I/O operation without additional wait states. Reading slow registers requires multiple wait states. Registers can be written to by the host CPU (W) and/or can be loaded by the DMA channel itself during chaining (C). All reads or writes must be word accesses since the UDC ignores the  $B/\overline{W}$  line in slave mode. It is the responsibility of the user to supply the necessary external logic if slow readable registers are to be read.

The UDC registers can be categorized into chip-level registers, which control the overall operation and configuration of the he UDC, and channel-level registers which are duplicated for each channel. The five chip-level registers are the Master Mode register the Command register, the Chain Control register, the Pointer register and the Temporary register. The Master Mode register selects the way the UDC chip interfaces to the system. The Command register is written to by the host CPU to initiate certain operations within the UDC chip, such as resetting the unit. The Chain Control register is used by a channel while it is reloading its channel-level registers from memory. The Pointer register is written to by the host CPU when the P/D input is HIGH. The data in Pointer register is the address of the internal register to be accessed. The Temporary register is used to hold data for Flowthru Transfer/ Transfer-and-Searches.

The channel-level registers can be divided into two subcategories: general purpose registers, which would be found on most DMA chips, and special purpose registers, which provide additional features and functionality. The general purpose registers are the Base and Current Operation Count registers, the Base and Current Address registers A and B and the Channel Mode register. The special purpose registers are the Pattern and Mask registers, the Status register, the Interrupt Vector register, the Interrupt Save register and the Chain Address register.

The internal registers are read or written in two steps. First, the address of the register to be accessed is written to the Pointer

register, when the P/ $\overline{D}$  input is HIGH. Then, the data is read from or written into the desired register, which is indicated by the Pointer register, when P/ $\overline{D}$  input is LOW. Note that a read with P/ $\overline{D}$  HIGH causes the contents of the Pointer register to be read on AD<sub>1</sub> through AD<sub>6</sub>.

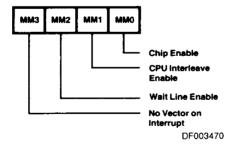

## Master Mode Register

The 4-bit Master Mode register, shown in Figure 3, controls the chip-level interfaces. It can be read from and written to by the host CPU without wait states through pins  $AD_0 - AD_3$ , but it is not loadable by chaining. On a reset, the Master Mode register is cleared to all zeroes. The function of each of the Master Mode bits is described in the following paragraphs.

The Chip Enable bit CE = 1 enables the UDC to request the bus. When enabled, the UDC can perform DMA Operations and reload registers. It can always issue interrupts and respond to interrupt acknowledges. When the Chip Enable bit is cleared, the UDC is inhibited from requesting control of the system bus and, therefore, inhibited from performing chaining or DMA operations.

The CPU Interleave bit enables interleaving between the CRU and the UDC.

The Wait Line Enable bit is used to enable sampling of the WAIT line during Memory and I/O transactions. Because the UDC provides the ability to insert software programmable wait states, many users may disable sampling of the WAIT pin to eliminate the logic driving this pin. The Wait Line Enable bit provides this flexibility. See the "Wait States" section of this document for details on wait state insertion.

The "No Vector on Interrupt" bit selects whether the UDC channel or a peripheral returns a vector during interrupt acknowledge cycles. When this bit is cleared, a channel receiving an interrupt acknowledge will drive the contents of its Interrupt Save register onto the AD $_0$  – AD $_{15}$  data bus while  $\overline{\text{INTACK}}$  is LOW. If this bit is set, interrupts are serviced in an identical manner, but the AD $_0$  – AD $_{15}$  data bus remains in a high-impedance state throughout the acknowledge cycle.

## Pointer Register

The Pointer register contains the address of the internal register to be accessed. It can be read from or written to by the CPU when the  $P/\overline{D}$  line is HIGH.

2-162 Am9516A

DataShe

www.DataSheet4U.com

| , |   | , |

|---|---|---|

|   | , |   |

| _ | • | 4 |

|   |   |   |

| Name                          | Size    | Number                                    | Access<br>Type | Port Address<br>CH-1/CH-2 |

|-------------------------------|---------|-------------------------------------------|----------------|---------------------------|

| Master Mode Register          | 4 bits  | 1                                         | FW             | 38                        |

| Pointer Register              | 6 bits  | 1                                         | FW             |                           |

| Chain-Control Register        | 10 bits | 1                                         | С              |                           |

| Temporary Register            | 16 bits | 1                                         | D              |                           |

| Command Register              | 8 bits  | 1                                         | W              | 2E/2C*                    |

| Current Address Register - A: |         |                                           | i              |                           |

| Up-Addr/Tag field             | 14 bits | 2 2                                       | CFW            | 1A/18                     |

| Lower Address field           | 16 bits | 2                                         | CFW            | 0A/08                     |

| Current Address Register - B: |         |                                           |                |                           |

| Up-Addr/Tag field             | 14 bits | 2 2                                       | CFW            | 12/10                     |

| Lower Address field           | 16 bits | 2                                         | CFW            | 02/00                     |

| Base Address Register - A:    |         | 1                                         |                |                           |

| Up-Addr/Tag field             | 14 bits | 2 2                                       | CFW            | 1E/1C                     |

| Lower Address field           | 16 bits | 2                                         | CFW            | 0E/0C                     |

| Base Address Register - B:    |         |                                           |                |                           |

| Up-Addr/Tag field             | 14 bits | 2                                         | CFW            | 16/14                     |

| Lower Address field           | 16 bits | 2                                         | CFW            | 06/04                     |

| Current Operation Count       | 16 bits | 2 2                                       | CFW            | 32/30                     |

| Base Operation Count          | 16 bits | 2                                         | CFW            | 36/34                     |

| Pattern Register              | 16 bits | 2                                         | CSW            | 4A/48                     |

| Mask Register                 | 16 bits | 2                                         | CSW            | 4E/4C                     |

| Status Register               | 16 bits | 2                                         | F              | 2E/2C                     |

| Interrupt Save Register       | 16 bits | 2                                         | F              | 2A/28                     |

| Interrupt Vector Register     | 8 bits  | 2                                         | CSW            | 5A/58                     |

| Channel Mode Register - HIGH  | 5 bits  | 2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2 | cs             | 56/54                     |

| Channel Mode Register - LOW   | 16 bits | 2                                         | CSW            | 52/50                     |

| Chain Address Register:       |         |                                           |                |                           |

| Up-Addr/Tag field             | 10 bits | 2                                         | CFW            | 26/24                     |

| Lower Address field           | 16 bits | 2                                         | CFW            | 22/20                     |

Access Codes: C = Chain Loadable

D = Accessible by UDC channel

F = Fast Readable S = Slow Readable

W = Writable by CPU

Note: The address of the register to be accessed is stored in the Pointer register.

\*Port addresses of the Command register can be used alternately for both channels except when issuing a "set or clear IP" command.

Figure 2. UDC Internal Register

#### Chain Control Register

When a channel starts a chaining operation, it fetches a Reload word from the memory location pointed to by the Chain Address register (Figure 10). This word is then stored in the Chain Control register. The Chain Control register cannot be written to or read from by the CPU. Once a channel starts a chain operation, the channel will not relinquish bus control until all registers specified in the Reload word are reloaded unless an EOP signal is issued to the chip. Issuing an EOP to a channel during chaining will prevent the chain operation from resuming and the contents of the Reload Word register can be discarded.

Figure 3. Master Mode Register

## **Temporary Register**

The Temporary register is used to stage data during Flowthru transfers and to hold data being compared during a Search or a Transfer-and-Search. The temporary register cannot be written to or read from by the CPU. In byte-word funneling,

data may be loaded into or from the Temporary register on a byte-by-byte basis, with bytes sometimes moving between the low byte of the data bus and the high byte of the Temporary register or vice-versa. See the "Transfer" section for details.

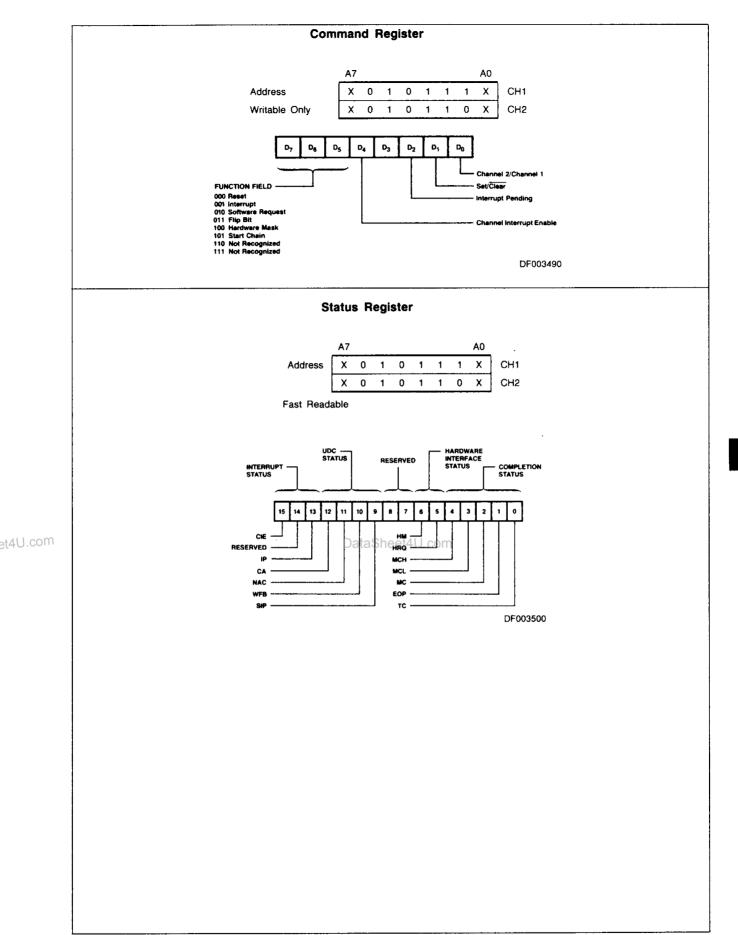

## Command Register

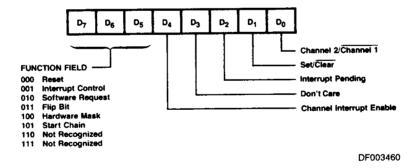

The UDC Command register (Figure 19) is an 8-bit write-only register written to by the host CPU. The Command register is loaded from the data on AD7 – AD6; the data on AD15 – AD8 is disregarded. A complete discussion of the commands is given in the "Command Descriptions" section.

#### Current and Base Address Registers A and B

The Current Address registers A and B (Current ARA and ARB) are used to point to the source and destination addresses for DMA operations. The contents of the Base ARA and ARB registers are loaded into the Current ARA and ARB registers at the end of a DMA operation if the user enables Base-to-Current reloading in the Completion Field of the Channel Mode register. This facilitates DMA operations without reloading of the Current registers. The ARA and ARB registers can be loaded during chaining, can be written to by the host CPU without wait states and can be read by the CPU.

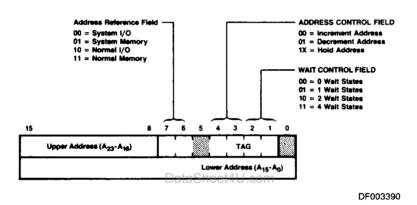

Each of the Base and Current ARA and ARB registers consists of two words organized as a 6-bit Tag Field and an 8-bit Upper Address in one word and a 16-bit Lower Address in the other. See Figure 5. The Tag Field selects whether the address is to be incremented, decremented or left unchanged, and the status codes associated with the address. The Tag field also allows the user to insert 0, 1, 2 or 4 wait states into memory or I/O accesses addressed by the offset and segment fields.

Am9516A 2-163

The Address Reference Select Field in the Tag field selects whether the address pertains to memory space or I/O space. Note that the N/S output pin may be either HIGH (indicating Normal) or LOW (indicating System) for space. At the end of each iteration of a DMA Operation, the user may select to leave the address unchanged or to increment it or to decrement it. I/O addresses, if changed, are always incremented/ decremented by 2. Memory addresses are changed by 1 if the address points to a byte operand (as programmed in the Channel Mode register's Operation field) and by 2 if the address points to a word operand. Note that, if an I/O or memory address is used to point to a word operand, the address must be even to avoid unpredictable results. An address used to point to a byte operand may be even or odd. Since memory byte operand addresses will increment/decrement by 1, they will toggle between even and odd values. Since I/O byte operand addresses will increment/decrement by 2, once programmed to an even or odd value, they will remain even or odd, allowing consecutive I/O operations to access the same half of the data bus. High bus is for even address and low bus for odd.

## **Current and Base Operation Count Registers**

Both the Current and Base Operation Count registers may be loaded during chaining and may be written to and read from by the host CPU.

The 16-bit Current Operation Count register is used to specify the number of words or bytes to be transferred, searched or transferred-and-searched. For word-to-word operations and byte-word funneling, the Current Operation Count register must be programmed with the number of words to be transferred or searched.

Each time a datum is transferred or searched, the Operation Count register is decremented by 1. Once all of the data is transferred or searched, the transfer or search operation will stop, the Current Operation Count register will contain all zeroes, and the TC bit in Status Register will be "1." If the transfer or search stops before the Current Operation Count register reaches 0, the contents of the register will indicate the number of bytes or words remaining to be transferred or searched. This allows a channel which had been stopped prematurely to be restarted where it left off without requiring reloading of the Current Operation Count register.

For the byte-to-byte operations, the Current Operation Count register should specify the number of bytes to be transferred or searched. The maximum number of bytes which can be specified is 64K bytes by setting the Current Operation Count register to 0000.

Figure 4. Address Registers A and B

## Pattern and Mask Registers

The 16-bit Pattern and Mask registers are used in Search and Transfer-and-Search operations. Both the Pattern and Mask registers may be loaded by chaining, may be written to by the host CPU and may be read from by the host CPU, provided wait states are inserted, since these registers are slow readable. The Pattern register contains the pattern that the read data is compared to. Setting a Mask register bit to "1" specifies that the bit always matches. See the "Search" and "Transfer-and-Search" sections for further details.

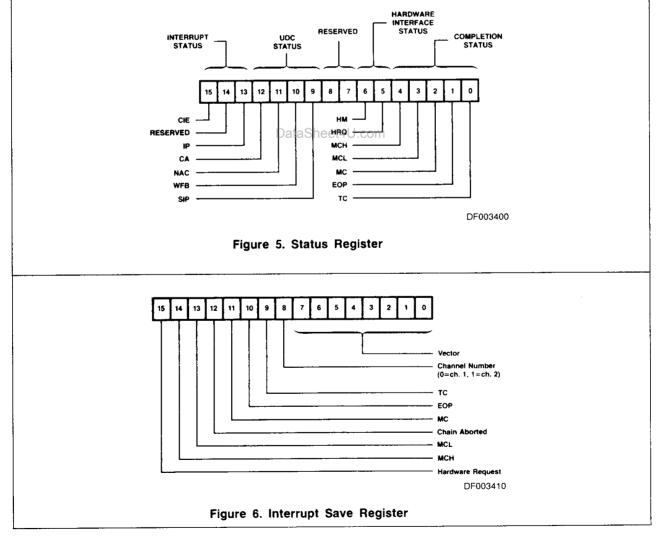

## Status Register

The two 16-bit Status registers, depicted in Figure 5, are readonly registers which can be read by the CPU without wait states. Each of these registers reports on the status of its associated channel.

The Interrupt Status Field in the Status register contains the Channel Interrupt Enable (CIE) and Interrupt Pending (IP) bits. These bits are described in detail in the "Interrupt" section of this document.

The UDC status field contains the current channel status. The

"channel initialized and waiting for request" status is not explicitly stated - it is reflected by Status register bits ST12 through ST<sub>9</sub> being all zero. The "Waiting for Bus" (WFB) status will cause bit ST10 to be set and indicates that the channel wants bus control to perform a DMA operation. The channel may or may not actually be asserting BREQ HIGH, depending on the programming of the Master Mode Chip Enable bit (MMO) when the channel decided it wanted the bus. See the "Bus Request/Grant" section for details. If a channel completes a DMA operation and neither Base-to-Current reloading nor auto-chaining were enabled, the No Auto-Reload or Chaining (NAC) bit will be set. The NAC bit will be reset when the channel receives a "Start Chain Command." If two interrupts are queued, the Second Interrupt Pending bit (SIP) will be set and the channel will be inhibited from further activity until an interrupt acknowledge occurs. See the "Interrupt" section for details. Finally, if the channel is issued an EOP during chaining, the Chaining Abort (CA) and the NAC will be set. These bits are also set when a "reset" is issued to the UDC. The CA bit holds the NAC bit in the set state. The CA bit is cleared when a new Chain Upper Address and Tag word or Lower Address word is loaded into the channel.

DataShe

2-164 Am9516A

www.DataSheet4U.com

2

DataShe

The Hardware Interface Field provides a Hardware Request (HRQ) bit which provides a means of monitoring the channels DREQ input pin. When the DREQ pin is LOW, the HRQ bit will be "1" and vice-versa. The Hardware Mask (HM) bit, when set, prevents the UDC from responding to a LOW on DREQ. Note, however, that the Hardware Request bit always reports the true (unmasked) status of DREQ regardless of the setting of the HM bit.

The Completion Field stores data at the end of each DMA operation. This data indicates why the DMA operation ended. When the next DMA operation ends, new data is loaded into these bits overwriting, thereby erasing the old setting. Three bits indicate whether the DMA operation ended as a result of a TC, MC or EOP termination. The TC bit will be "1" if the Operation Count reaching zero ended the DMA operation. The MC bit will be "1" if an MC termination occurred regardless of whether Stop-on-Match or Stop-on-no-Match was selected. The EOP bit is set only when an external EOP ends a DMA transfer; it is not set for EOP issued during chaining. Note that two or even all three of MC, TC and EOP may be set if multiple reasons exist for ending the DMA operation. The MCH and MCL bits report on the match state of the upper and lower comparator bytes, respectively. These bits are set when the associated comparator byte has a match and are reset otherwise, regardless of whether Stop-on-Match or Stop-onno-Match is programmed. Regardless of the DMA operation performed, these bits will reflect the comparator status at the end of the DMA operation. These two bits are provided to help

determine which byte matched or did not match when using 8-bit matches with word searches and transfer-and-searches. The three reserved bits return zeroes during reads.

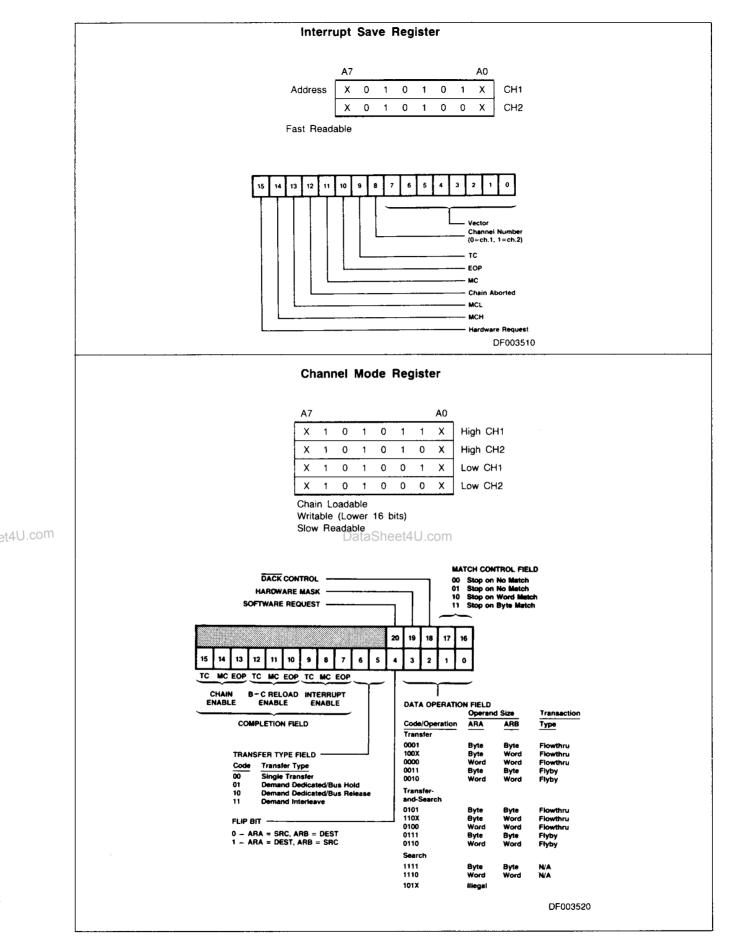

## Interrupt Vector and Interrupt Save Registers

Each channel has an Interrupt Vector register and an Interrupt Save register. The Interrupt Vector is 8-bit wide and is written to and read from on AD<sub>0</sub> – AD<sub>7</sub>. The Interrupt Save register may be read by the CPU without wait states. The Interrupt Vector register contains the vector or identifier to be output during an Interrupt Acknowledge cycle. When an interrupt occurs (IP = 1), either because a DMA operation terminated or because EOP was driven LOW during chaining, the contents of the Interrupt Vector register and part of the Channel Status register are stored in the 16-bit Interrupt Save register (see Figure 6).

Because the vector and status are stored, a new vector can be loaded into the Interrupt Vector register during chaining, and a new DMA operation can be performed before an interrupt acknowledge cycle occurs. If another interrupt occurs on the channel before the first is acknowledged, further channel activity is suspended.

As soon as the first clear IP command is issued, the status and vector for the second interrupt are loaded into the Interrupt Save register and Channel Operation resumes. The UDC can retain only two interrupts for each channel; a third operation cannot be initiated until the first interrupt has been cleared. See the "Interrupt" section for further details.

Am9516A

2-165

DataSheet4LL.com

et4U.com

www.DataSheet4U.com

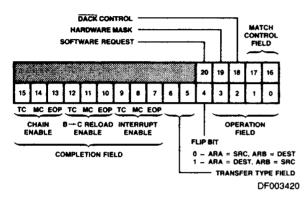

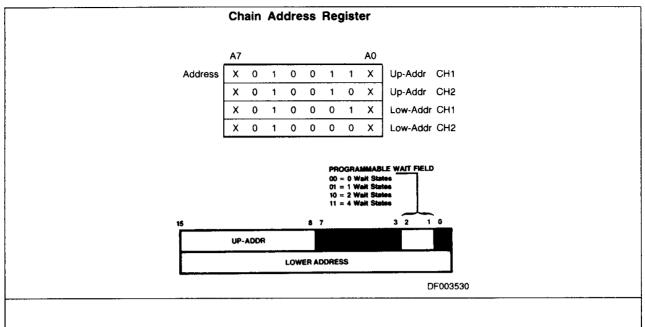

#### Channel Mode Register

The Channel Mode registers are two words wide. There are 21 bits defined in each Channel Mode register; the other 11 bits are unused. See Figure 7. The Channel Mode registers may be loaded during chaining and may be read by the host CPU. CPU reads of the Channel Mode register are slow reads and require insertion of multiple wait states. The Channel Mode Low word (bits 0–15) may be written to directly by the host CPU. The Channel Mode register selects what type of DMA operation the channel is to perform, how the operation is to be executed, and what action, if any, is to be taken when the channel finishes.

The Data Operation Field and the Transfer Type field select the type of operation the channel is to perform. It also selects the operand size of bytes or words (see Figure 8 for code-definition). The different types of operations are described in detail in the "DMA Operations" section. The Flip bit is used to select whether the Current ARA register points to the source and the Current ARB register points to the destination or vice-versal.

Figure 7. Channel Mode Register

The Completion Field is used to program the action taken by the channel at the end of a DMA operation. This field is discussed in the "Completion Options" section. The 2-bit Match Control field selects whether matches use an 8-bit or 16-bit pattern and whether the channel is to stop-on-match or stop-on-no-match. See Figure 8 and the "Search" section for details. The Software Request bit and Hardware Mask bit can be set and cleared by software command in addition to being loaded in parallel with other Channel Mode bits. These bits are described in detail in the "Initiating DMA Operations" section.

The DACK Control bit is used to specify when the DACK pin is driven active. When this bit is cleared, the channel's DACK pin will be active whenever the channel is performing a DMA Operation, regardless of the type of transaction. Note that the pin will not be active while the channel is chaining. If this bit is

set, the DACK pin will be inactive during chaining, during both Flowthru Transfers and Flowthru Transfer-and-Searches, and during Searches, but DACK will be pulsed active during Flyby Transfers and Flyby Transfers-and-Searches at the time necessary to strobe data into or out of the Flyby peripheral. Flyby operations are discussed in detail in the "Flyby Transactions" section.

| DATA OPERATION FIELD                        |         |         |                    |  |  |

|---------------------------------------------|---------|---------|--------------------|--|--|

| Opera                                       |         | nd Size | e Transaction      |  |  |

| Code/Operation                              | ARA     | ARI     |                    |  |  |

| Transfer                                    |         |         |                    |  |  |

| 0001                                        | Byte    | Byte    | Flowthru           |  |  |

| 100X                                        | Byte    | Word    | Flowthru           |  |  |

| 0000                                        | Word    | Word    |                    |  |  |

| 0011                                        | Byte    | Byte    | Flyby              |  |  |

| 0010                                        | Word    | Word    | Flyby              |  |  |

| Transfer-and-Search                         |         |         |                    |  |  |

| 0101                                        | Byte    | Byte    | Flowthru           |  |  |

| 110X                                        | Byte    | Word    | Flowthru           |  |  |

| 0100                                        | Word    | Word    | Flowthru           |  |  |

| 0111                                        | Byte    | Byte    | Flyby              |  |  |

| 0110                                        | Word    | Word    | Flyby              |  |  |

| Search                                      |         |         |                    |  |  |

| 1111                                        | Byte    | Byte    | N/A                |  |  |

| 1110                                        | Word    | Word    | N/A                |  |  |

| 101X                                        | Illegai | 1       |                    |  |  |

| TRANSFER TYPE FIELD AND MATCH CONTROL FIELD |         |         |                    |  |  |

| Transfer Typ                                | е       | Code    | Match Control      |  |  |

| Single Transfer                             |         | 00      | Stop on No Match   |  |  |

| Demand Dedicated/Bus                        | Hold    | 01      | Stop on No Match   |  |  |

| Demand Dedicated/Bus                        |         | 10      | Stop on Word Match |  |  |

|                                             |         | I       | 10.                |  |  |

Figure 8. Channel Mode Coding

Stop on Byte Match

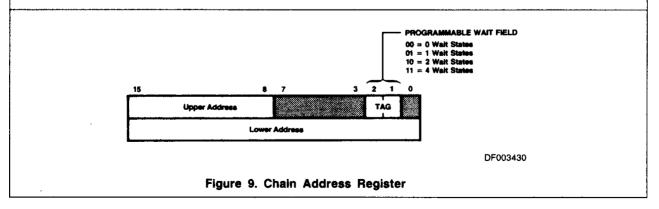

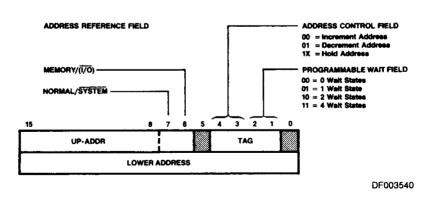

## Chain Address Register

Demand Interleave

Each channel has a Chain Address register which points to the chain control table in memory containing data to be loaded into the channel's registers. The Chain Address register, as shown in Figure 9, is two words long. The first word consists of an Upper Address and Tag field. The second word contains the 16-bit Lower Address portion of the memory address. The Tag field contains 2 bits used to designate the number of wait states to be inserted during accesses to the Chain Control Table.

The Chain Address register may be loaded during chaining and may be read from and written to by the host CPU without wait states. If an EOP is issued to the UDC during chaining, the Chain Address register holds the old address. This is true even if the access failure occurred while new Chain Address data was being loaded, since the old data is restored unless both words of the new data are successfully read. Note, however, that EOPs that occur when chaining and while loading a new Chain Address cause the new data to be lost.

2-166 Am9516A

DataShe

www.DataSheet4U.com

# 2

DataShe

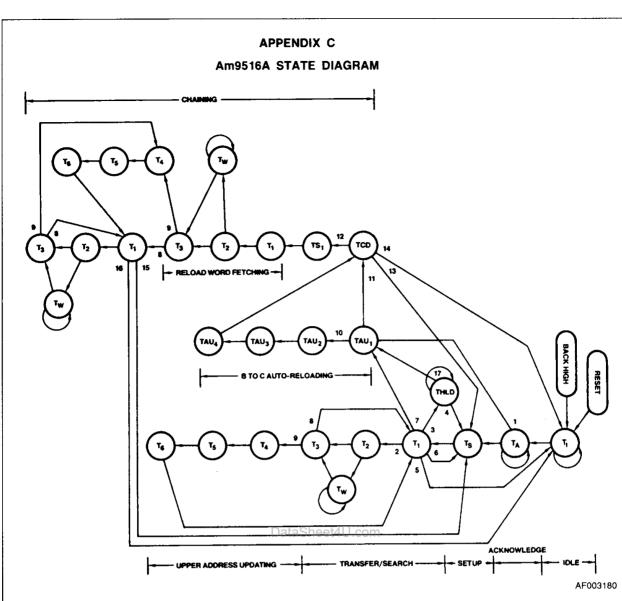

#### DETAILED DESCRIPTION

Any given DMA operation, be it a Transfer, a Search, or a Transfer-and-Search operation, consists of three phases. In the first phase, the channel's registers are initialized to specify and control the desired DMA operation. In the second phase, the DMA operation itself is started and performed. The final phase involves terminating the DMA operation and performing any actions selected to occur on termination. Each of these different phases is described in detail in the following sections.

#### Reset

The UDC can be reset either by hardware or software. The software reset command is described in the "Commands" section. Hardware resets are applied by pulling  $\overline{\text{RESET}}$  LOW. The UDC may be in control of the bus when a reset is applied. BACK is removed internally causing the outputs to go tri-state. If BACK remains HIGH after reset, the UDC will not drive the bus unless BREQ is active. As soon as BACK goes inactive, the UDC places the AD $_0$  – AD $_{15}$ , A $_{16}$  – AD $_{23}$ , R/ $\overline{\text{W}}$ ,  $\overline{\text{DS}}$ , N/ $\overline{\text{S}}$ , M/ $\overline{\text{IO}}$  B/ $\overline{\text{W}}$ ,  $\overline{\text{TBEN}}$  and  $\overline{\text{RBEN}}$  signals in the high-impedance state.

Both software and hardware resets clear the Master Mode register, clear the CIE, IP and SIP bits, and set the CA and NAC bits in each Channel's Status register. The contents of all other UDC registers will be unchanged for a software reset. Since a hardware reset may have been applied partway through a DMA operation being performed by a UDC channel, the channel's registers should be assumed to contain indeterminate data following a hardware reset.

The Master Mode register contains all zeroes after a reset. The UDC is disabled, and the CPU interleave and hardware wait are inhibited.

Because the CA and NAC bits in the Status register are set by a reset, the channel will be prevented from starting a DMA operation until its Chain Address register's Segment, Tag and Offset fields are programmed and the channel is issued a "Start Chain" Command.

Channel Initialization

The philosophy behind the Am9516A UDC design is that the UDC should be able to operate with a minimum of interaction with the host CPU. This goal is achieved by having the UDC load its own control parameters from memory into each channel. The CPU has to program only the Master Mode register and each Channel's Chain Address register. All other registers are loaded by the channels themselves from a table located in the System memory space and pointed to by the Chain Address register. This reloading operation is called chaining, and the table is called the Chain Control Table.

The Upper and Lower Address fields of the Chain Address register form a 24-bit address which points to a location in system memory space. Chaining is performed by repetitively reading words from memory. Note that the Chain Address register should always be loaded with an even Address; loading an odd Address will cause unpredictable results. The 2-bit Tag field facilitates interfacing to slow memory by allowing the user to select 0, 1, 2 or 4 programmable wait states. The UDC will automatically insert the programmed number of wait states in each memory access during chaining.

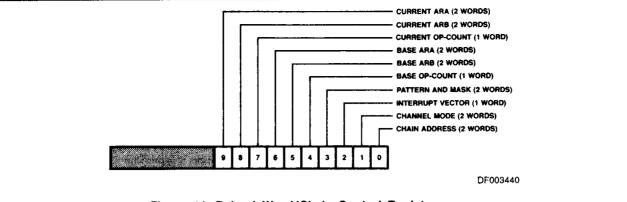

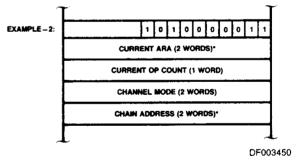

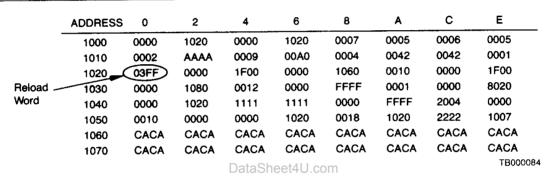

The Chain Address register points to the first word in the Chain Control Table. This word is called the Reload Word. See Figure 10. The purpose of the Reload Word is to specify which registers in the channel are to be reloaded. Reload Word bits 10 – 15 are undefined and may be 0 or 1. Each of bits 0 through 9 in the Reload Word correspond to either one or two registers in the channel (see Figure 11). When a Reload Word bit is "1," it means that the register or registers corresponding to that bit are to be reloaded. If a Reload Word bit is "0," the register or registers corresponding to that bit are not to be reloaded. The data to be loaded into the selected register(s) follow the Reload Word in memory (i.e., the data are stored at successively larger memory addresses). The Chain Control Table is a variable length table. Only the data to be loaded are in the table, and the data are packed together.

REGISTER DATA

CHAIN ADDR.

REGISTER DATA

CHAIN ADDR.

REGISTER

RELOAD WORD

CHAIN CONTROL

TABLE—1

CHAIN CONTROL

TABLE—2

Am9516A

Figure 10. Chaining and Chain Control Tables

2-167

ataSheet4LLcom

et4U.com

www.DataSheet4U.com

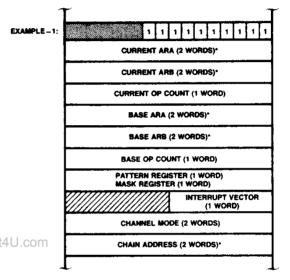

Figure 11. Reload Word/Chain Control Register

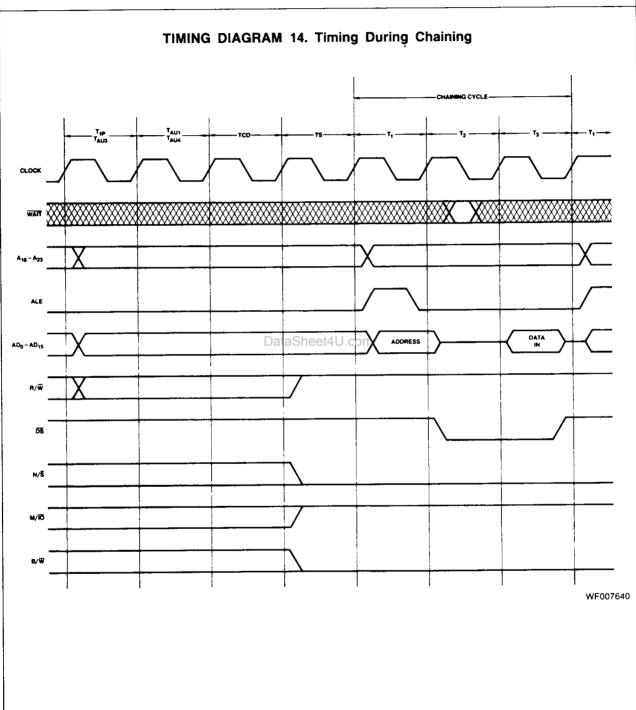

When the channel is to reload itself, it first uses the Chain Address register contents to load the Reload Word into the UDC's Chain Control register. Next, the Chain Address register contents are incremented by two to point to the next word in memory. The channel than scans the Reload Word register from bit 9 down to bit 0 to see which registers are to be reloaded. If no registers are specified (bits 9-0 are all 0), no registers will be reloaded. If at least one of bits 9-0 is set to "1," the register(s) corresponding to the set bit are reloaded, the bit is cleared and the Chain Address register is incremented by 2. The channel continues this operation of scanning the bits from the most significant to least significant bit position, clearing each set bit after reloading its associated registers and incrementing the Chain Address register by 2. If all of bits 9 to 0 are set, all the registers will be reloaded in the order: Current ARA, Current ARB, Current Operation Count, . . . Channel Mode and Chain Address. Figure 12 shows two examples of Chain Control Tables. Example 1 shows the ordering of data when all registers are to be reloaded. In example 2 only some registers are reloaded. Once the channel is reloaded, it is ready to perform a DMA operation. Note when loading address registers, the Upper Address and heet4U.com Tag word are loaded first, then the Lower Address word. Also, the Pattern register is loaded before the Mask register.

request the bus and perform transfers. See the description of the software request command for details.

## Initiating DMA Operations

DMA operations can be initiated in one of three ways — by software request, by hardware request and by loading a set software request bit into the Channel Mode register during Chaining.

## Starting After Chaining

If the software request bit of the Channel Mode register is loaded with a "1" during chaining, the channel will perform the programmed DMA operation at the end of chaining. If the channel is programmed for Single Operation or Demand, it will perform the operation immediately. The channel will give up the bus after chaining and before the operation if the CPU interleave bit in the Master Mode register is set. See the "Channel Response" section for details. Note that once a channel starts a chaining operation by fetching a Reload Word, it retains bus control at least until chaining of the last register's data is performed.

## Software Requests

The CPU can issue Software Request commands to start DMA operations on a channel. This will cause the channel to

Figure 12. Examples of Chain Control Table

\*Load the Upper Address and Tag Word first, then the Lower Address Word.

#### **Hardware Requests**

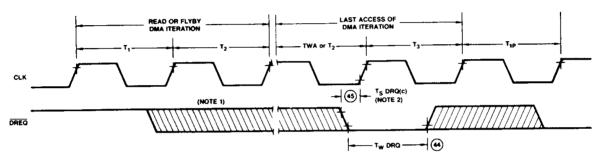

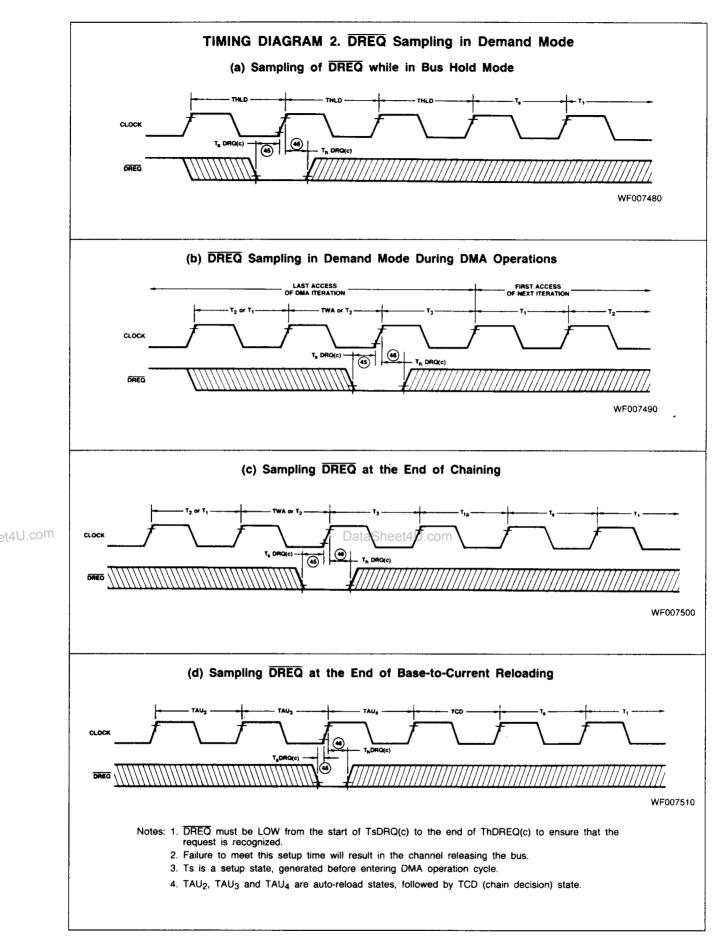

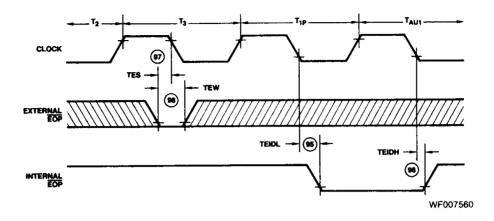

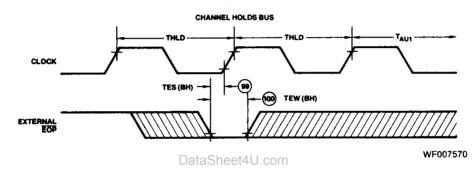

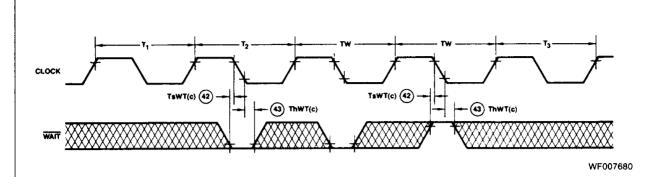

DMA operations will often be started by applying a LOW on the channel's DREQ input. The "Channel Response" section describes when the LOW DREQ signals are sampled and when the DREQ requests can be applied to start the next DMA operation after chaining (see Timing Diagrams 1 and 2).

2-168 Am9516A

www.DataSheet4U.com

DataShe

# 2

## DataShe

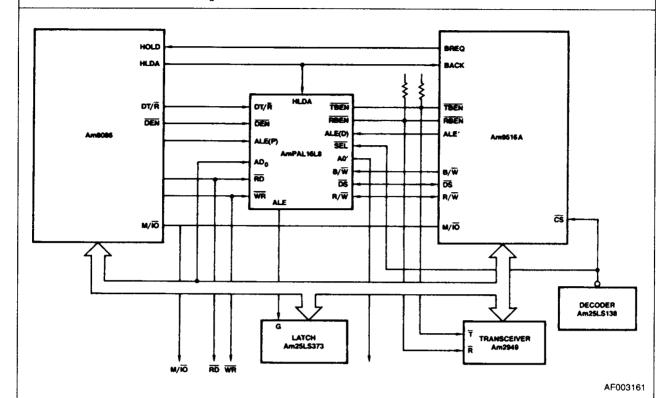

## **Bus Request/Grant**

Before the UDC can perform a DMA Operation, it must gain control of the system bus. The BREQ and BACK interface pins provide connections between the UDC and the host CPU and other devices, if present, to arbitrate which device has control of the system bus. When the UDC wants to gain bus control, it drives BREQ HIGH.

Some period of time after the UDC drives BREQ HIGH, the CPU will relinquish bus control and drive its HLDA signal HIGH. When the UDC's BACK input goes HIGH, it may begin performing operations on the system bus. When the UDC finishes its operation, it stops driving BREQ HIGH.

When more than one device is used, a priority encoder and a priority decoder are used to decide the bus grant priority.

#### **DMA Operations**

There are three types of DMA operations: Transfer, Search, and Transfer-and-Search. Transfers move data from a source location to a destination location. Two types of transfers are provided: Flowthru and Flyby. Searches read data from a source and compare the read data to the contents of the Pattern register. A Mask register allows the user to declare "don't care" bits.

The user can program that the search is to stop either when the read data matches the masked pattern or when the read data fails to match the masked pattern. This capability is called Stop-on-Match and Stop-on-no-Match. Transfer-and-Search combines the two functions to facilitate the transferring of variable length data blocks. Like Transfer, Transfer-and-Search can be performed in either Flowthru or Flyby mode.

## **Transfers**

et4U.com

Transfers use four of the Channel registers to control the transfer operation: the Current ARA and ARB registers; the Current Operation Count register; and the Channel Mode register. Channel Mode register bit CM4 is called the Flip bit and is used to select whether ARA is to point to the source and ARB is to point to the destination or vice-versa. The Current Operation Count register specifies the number of words or bytes to be transferred.

Bits  $CM_3-M_0$  in the Channel Mode register program whether a Flowthru or Flyby transfer is to be performed. Flowthru transfers are performed in either two or three steps. First, the channel outputs the address of the source and reads the source data into the UDC's Temporary register. In two-step Flowthru Transfer, the channel will then address the destination and write the Temporary register data to the destination location. The three-step Flowthru operation (i.e., the byte-word funneling) is described later in this section. The source and destination for Flowthru Transfers can both be memory locations or both peripheral devices, or one may be a memory location and the other a peripheral device. The  $\overline{DACK}$  output for the transferring channel may be programmed to be inactive throughout the transfer or active during the transfer. This is controlled by bit  $CM_{18}$  in the Channel Mode register.

Flyby transfers provide improved transfer throughput over Flowthru but are restricted to transfers between memory and peripherals or between two peripherals. Flyby operations are described in detail in the "Flyby Transactions" section.

Transfers can use both byte- and word-sized data. Flowthru byte-to-byte transfers are performed by reading a byte from the source and writing a byte to the destination. The Current Operation Count register must be loaded with the number of bytes to be transferred. Both the Current ARA and Current ARB registers, if programmed to increment/decrement, will change by ±1 if the register points to a memory space

$(TG_6 = 2)$  and by  $\pm 2$  if the register points to an I/O space  $(TG_6 = 0)$ .

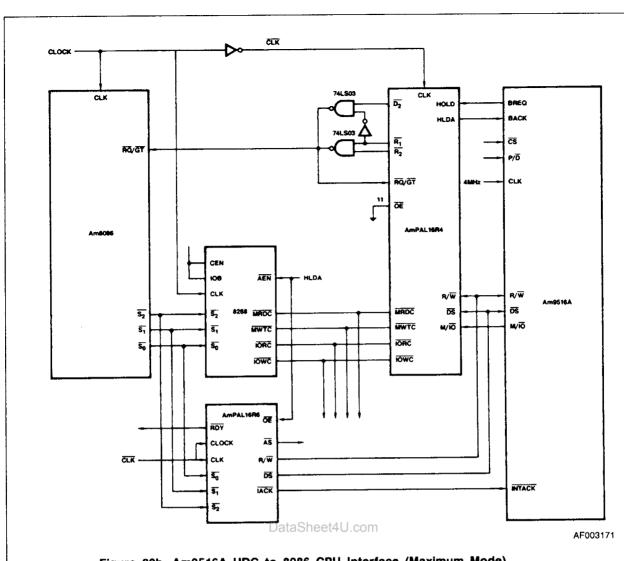

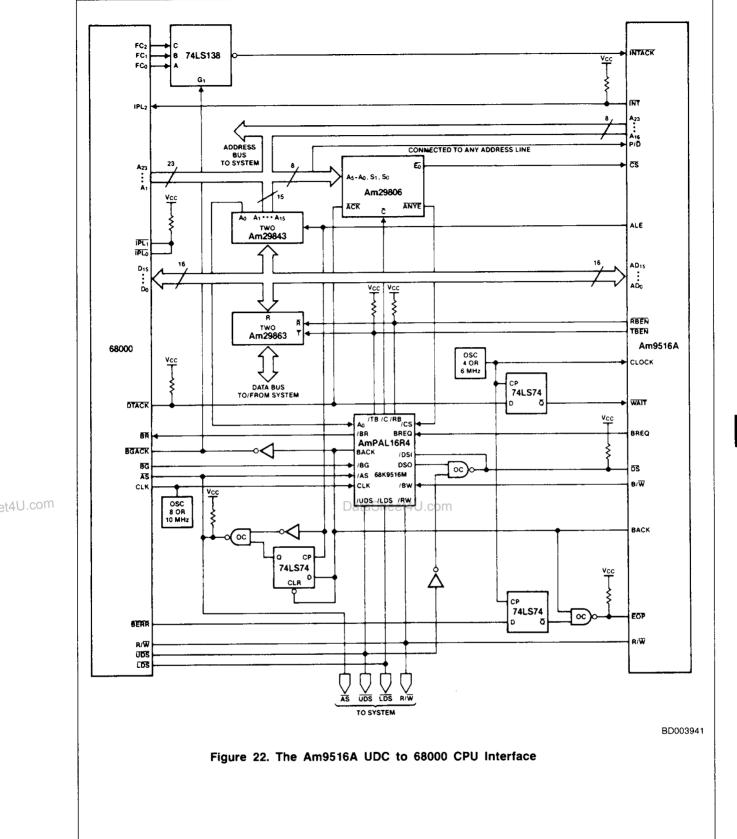

Flowthru word-to-word transfers require that the Current Operation Count specify the number of words to be transferred. Both the Current ARA and Current ARB registers, if programmed to increment/decrement, will change by ±2 regardless of whether the register points to memory or I/O space.