# AMD-762™ System Controller

**Data Sheet**

Dublishing # 24444 Day 0

Publication # 24416 Rev: C Issue Date: December 2001

#### © 2001 Advanced Micro Devices, Inc. All rights reserved.

The contents of this document are provided in connection with Advanced Micro Devices, Inc. ("AMD") products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this publication. Except as set forth in AMD's Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right.

AMD's products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD's product could create a situation where personal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice.

#### Trademarks

AMD, the AMD logo and combinations thereof, AMD Athlon, AMD-760, AMD-761, AMD-762, AMD-766, and AMD-768 are trademarks of Advanced Micro Devices, Inc.

Alpha is a trademark of Digital Equipment Corporation.

Microsoft is a registered trademark of Microsoft Corporation.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

## **Contents**

| Rev | ision Histo | ry    |                                                                                                                                                                                        | Хİ                         |

|-----|-------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 1   | Features    |       |                                                                                                                                                                                        | 1                          |

|     |             | 1.1   | AMD Athlon™ System Buses                                                                                                                                                               | . 2                        |

|     |             | 1.2   | Integrated Memory Controller                                                                                                                                                           | . 2                        |

|     |             | 1.3   | PCI Bus Controller                                                                                                                                                                     | . 3                        |

|     |             | 1.4   | AGP Features                                                                                                                                                                           | . 4                        |

|     |             | 1.5   | Power Management                                                                                                                                                                       | . 4                        |

| 2   | Functiona   | l Ope | ration                                                                                                                                                                                 | 7                          |

|     |             | 2.1   | Processor Interface                                                                                                                                                                    | . 7                        |

|     |             |       | <ul><li>2.1.1 Out of Order, Split Transaction</li></ul>                                                                                                                                | . 8                        |

|     |             | 2.2   | Memory Interface                                                                                                                                                                       | 10                         |

|     |             |       | 2.2.1 DRAM Refresh                                                                                                                                                                     |                            |

|     |             | 2.3   | PCI Bus Controller                                                                                                                                                                     | 14                         |

|     |             |       | 2.3.1 Memory Coherency 2.3.2 PCI Arbitration  Legacy Mode—Single PCI Bus Southbridge  Southbridge with an Integrated PCI-PCI Bus Bridge  Arbitration Priority  2.3.3 PCI Configuration | 16<br>. 16<br>. 17<br>. 17 |

|     |             |       | 2.3.4 PCI Parity/ECC Errors                                                                                                                                                            | 18                         |

Table of Contents iii

|   | 2.4             | Accelerated Graphics Port (AGP)                                                                                                                                                                                                                                         |

|---|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 2.5             | System Clocking                                                                                                                                                                                                                                                         |

|   |                 | 66-MHz PCI Bus                                                                                                                                                                                                                                                          |

|   | 2.6             | Power Management                                                                                                                                                                                                                                                        |

|   |                 | 2.6.1 Full-On (C0)       27         2.6.2 Halt (C1)       27         2.6.3 Throttling with STPCLK# Assertion       27         2.6.4 Power-On Suspend (S1)       28         S1 Sequence       28         2.6.5 Suspend to RAM (S3)       30         S3 Sequence       31 |

| 3 | Test            | 35                                                                                                                                                                                                                                                                      |

|   | 3.1             | Board (Three-State) Test Mode                                                                                                                                                                                                                                           |

|   |                 | 3.1.1 Board Test Mode Clocking                                                                                                                                                                                                                                          |

|   | 3.2             | NAND Tree Test Mode                                                                                                                                                                                                                                                     |

|   | 3.3             | PLL Bypass Test Mode 44                                                                                                                                                                                                                                                 |

|   | 3.4             | Clock Output Test Mode45                                                                                                                                                                                                                                                |

| 4 | Electrical Data | 47                                                                                                                                                                                                                                                                      |

|   | 4.1             | Absolute Ratings                                                                                                                                                                                                                                                        |

|   | 4.2             | Operating Ranges 48                                                                                                                                                                                                                                                     |

|   | 4.3             | DC Characteristics 49                                                                                                                                                                                                                                                   |

|   |                 | 4.3.1 Voltage Sequencing Requirements 50                                                                                                                                                                                                                                |

|   | 4.4             | Power Dissipation                                                                                                                                                                                                                                                       |

|   | 4.5             | Switching Characteristics and Requirements 53                                                                                                                                                                                                                           |

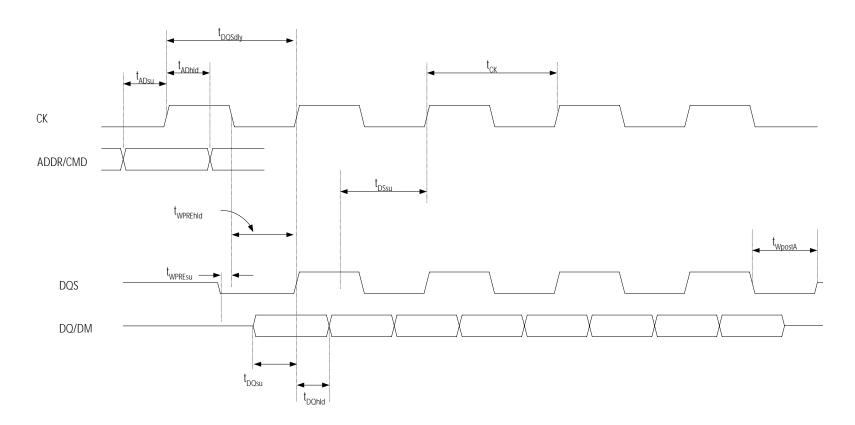

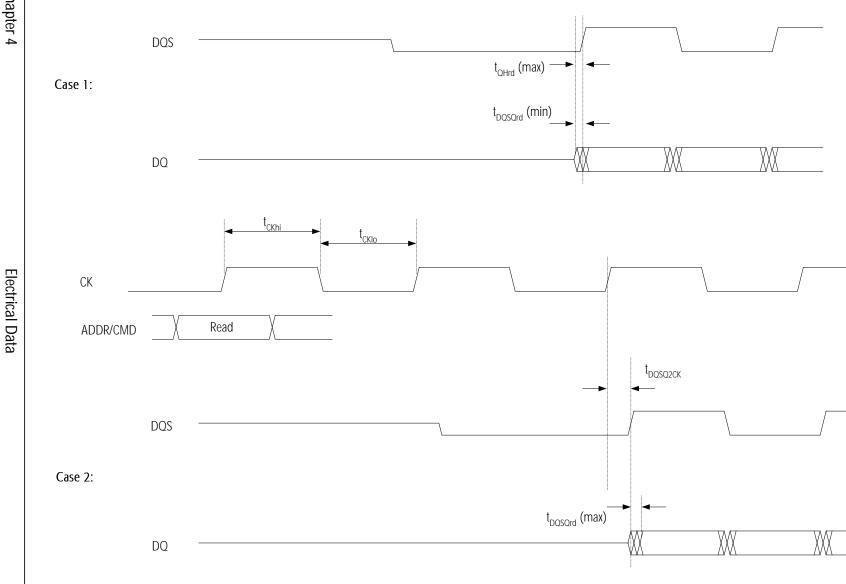

|   |                 | 4.5.1 Clock Switching Requirements 53 4.5.2 DDR Interface Timing 56 DDR Write Timing 57 DDR Read Timing 66                                                                                                                                                              |

| AMD-762™ System Controller I | Dala | Sneet |

|------------------------------|------|-------|

|------------------------------|------|-------|

|     |                  | 4.5.3 AGP/PCI Signals       |     |

|-----|------------------|-----------------------------|-----|

| 5   | Package Specifi  | cations                     | 71  |

| 6   | Pin Designation  | ns                          | 73  |

| 7   | Signal Descript  | ions                        | 81  |

|     | 7.1              | Initialization Pinstrapping | 94  |

|     | 7.2              | Pin Multiplexing            | 97  |

|     | 7.3              | Pin States at Reset         | 98  |

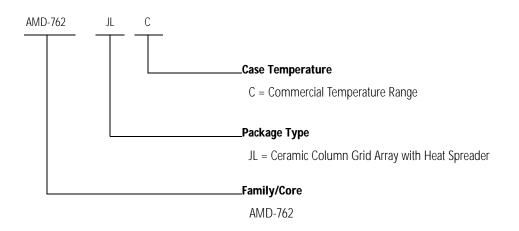

| 8   | Ordering Inform  | mation                      | 101 |

| roO | nventions, Abbre | viations, and References    | 103 |

|     |                  | Signals and Bits            | 103 |

|     |                  | Data Terminology            | 103 |

|     |                  | Abbreviations and Acronyms  | 104 |

|     |                  | Related Publications        | 109 |

|     |                  | AMD Publications            |     |

|     |                  | Bus Architecture            |     |

|     |                  | x86 Architecture            |     |

|     |                  | Websites                    |     |

Table of Contents v

AMD-762<sup>™</sup> System Controller Data Sheet

24416C – December 2001

*vi* Table of Contents

## **List of Figures**

| Figure 1.  | AMD-760MPX™ System Block Diagram (66-MHz PCI)5                                     |

|------------|------------------------------------------------------------------------------------|

| Figure 2.  | AMD-760MP™ Chipset System Block Diagram (33-MHz PCI) 6                             |

| Figure 3.  | Push-Pull Transmission Line Example 9                                              |

| Figure 4.  | Dummy Load with External Compensation Resistors9                                   |

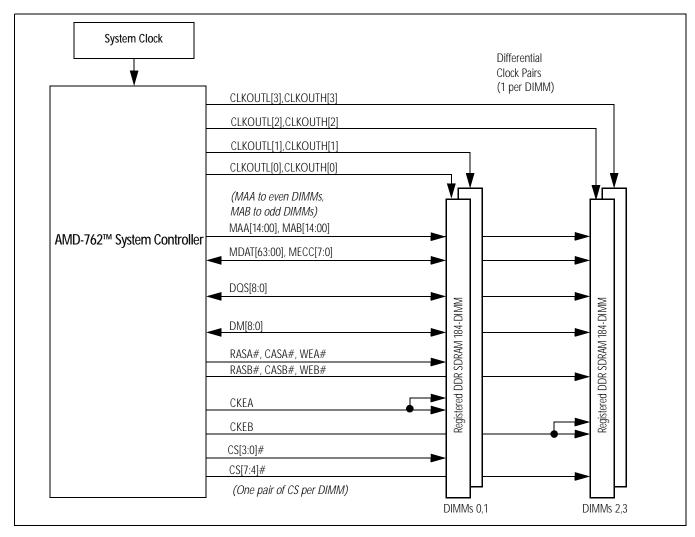

| Figure 5.  | AMD-762 $^{\scriptscriptstyle{TM}}$ System Controller Connection to DDR DIMMs . 12 |

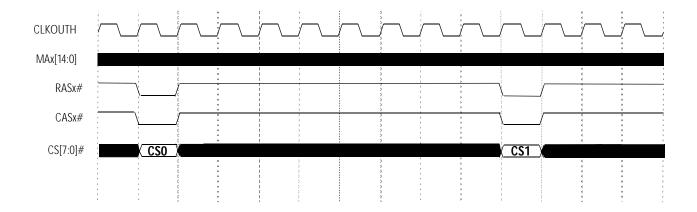

| Figure 6.  | DRAM Refresh Timing                                                                |

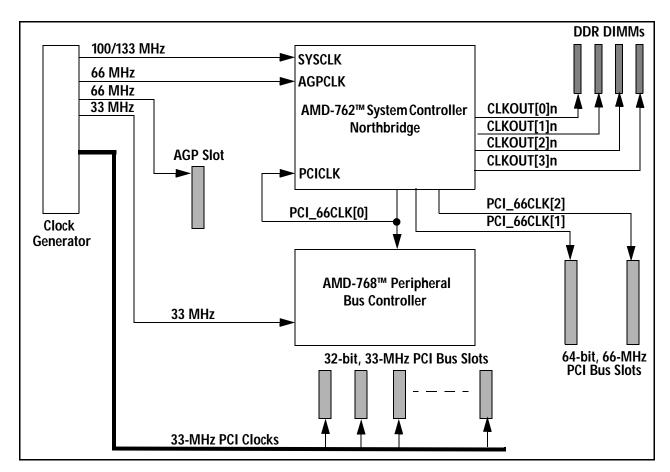

| Figure 7.  | System Clocking with 66-MHz PCI Primary Bus 23                                     |

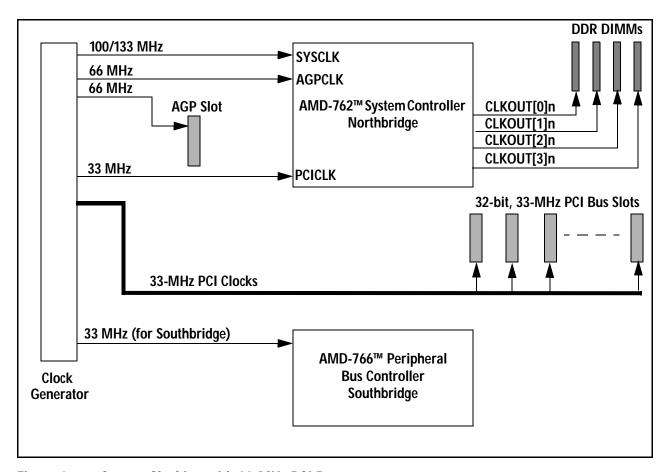

| Figure 8.  | System Clocking with 33-MHz PCI Bus                                                |

| Figure 9.  | Power Management Signal Connections25                                              |

| Figure 10. | Power On Suspend System Timing Diagram Example 30                                  |

| Figure 11. | Suspend to RAM System Timing Diagram Example 33                                    |

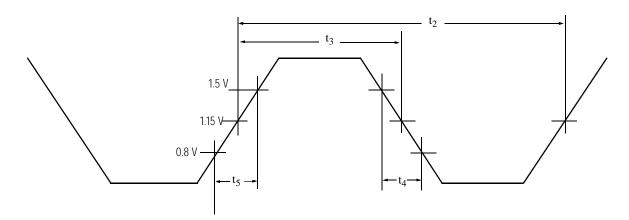

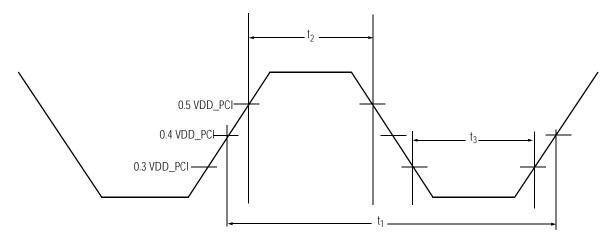

| Figure 12. | SYSCLK Waveform54                                                                  |

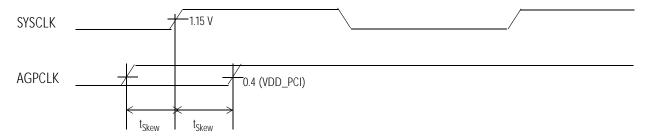

| Figure 13. | AGPCLK and PCICLK Waveform                                                         |

| Figure 14. | Clock Skew Requirements                                                            |

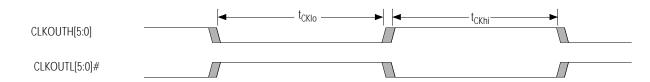

| Figure 15. | DDR Clock Specifications57                                                         |

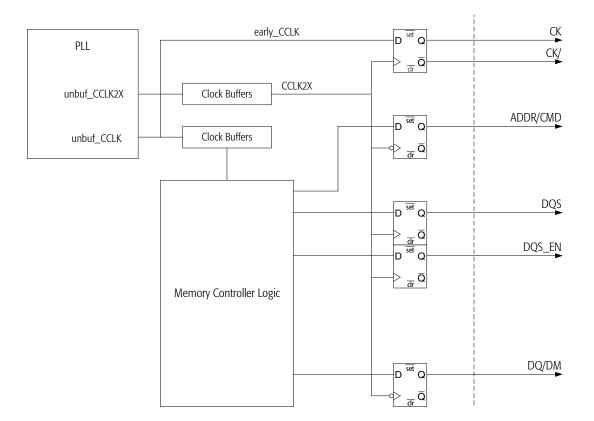

| Figure 16. | AMD-762 System Controller DDR Interface Outputs                                    |

|            | Conceptual Block Diagram58                                                         |

| Figure 17. | Address/Command and Memory Write Cycle Timing 59                                   |

| Figure 18. | AMD-762 System Controller DDR Interface Inputs                                     |

|            | Conceptual Block Diagram60                                                         |

| Figure 19. | Memory Read Cycle Timing61                                                         |

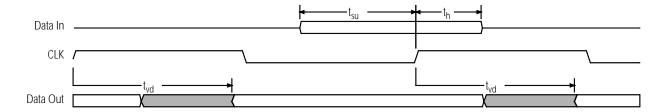

| Figure 20. | Setup, Hold, and Valid Delay Timings62                                             |

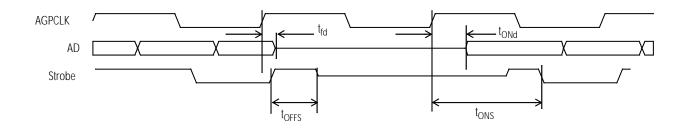

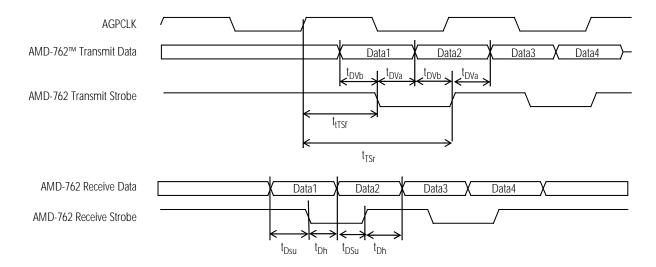

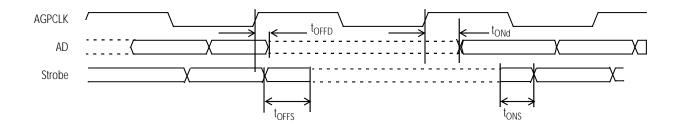

| Figure 21. | AGP 2x Strobe/Data Turnaround Timings 65                                           |

| Figure 22. | AGP 2x Timing Diagram66                                                            |

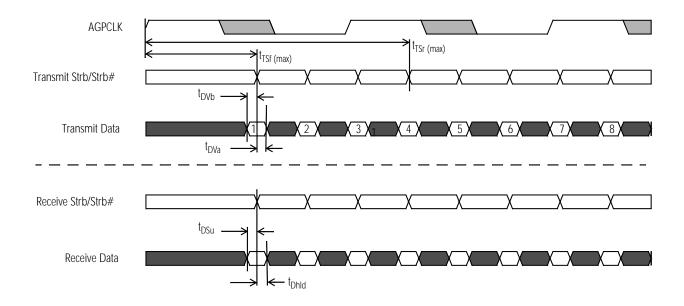

| Figure 23. | AGP 4x Timing Diagram66                                                            |

| Figure 24. | AGP 4x Strobe/Data Turnaround Timing 67                                            |

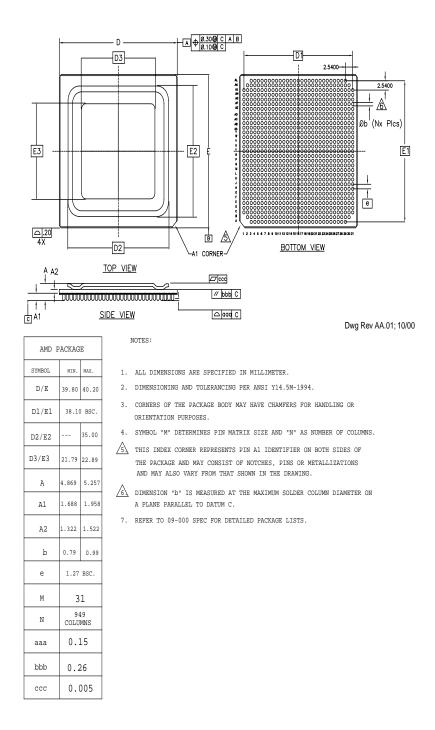

| Figure 25. | 949-Pin Ceramic Column Grid Array (CCGA) Package 72                                |

List of Figures vii

24416C-December 2001

viii List of Figures

AMD-762<sup>™</sup> System Controller Data Sheet

## **List of Tables**

| Table 1.   | Total Memory Sizes11                                         |

|------------|--------------------------------------------------------------|

| Table 2.   | AMD Athlon Processor System Bus NAND Tree Ordering38         |

| Table 3:   | AMD-762 System Controller AGP NAND Tree Ordering 41          |

| Table 4:   | AMD-762 System Controller DDR NAND Tree Ordering 42          |

| Table 5:   | AMD-762 System Controller PCI NAND Tree Ordering 44          |

| Table 6.   | Clocking Options in PLL Bypass Test Mode                     |

| Table 7.   | Clock Output Test Mode Options                               |

| Table 8.   | Absolute Ratings47                                           |

| Table 9.   | <b>Operating Ranges48</b>                                    |

| Table 10.  | DC Characteristics (IDD)49                                   |

| Table 11.  | DC Characteristics for DDR Interface                         |

| Table 12.  | DC Characteristics for PCI I/Os50                            |

| Table 13.  | AGP 1x Mode DC Specifications51                              |

| Table 14.  | AGP 2x and 4x Mode DC Specifications                         |

| Table 15.  | Typical and Maximum Power Dissipation53                      |

| Table 16.  | SYSCLK Switching Requirements                                |

| Table 17.  | AGPCLK Switching Requirements for 66-MHz Bus                 |

|            | Operation                                                    |

| Table 18.  | PCICLK Switching Requirements for 33-MHz PCI Bus 55          |

| Table 19.  | DDR Clock Switching Characteristics for 100-MHz DDR          |

|            | Operation                                                    |

| Table 20.  | DDR Clock Switching Characteristics for 133-MHz DDR          |

| T-kl- 01   | Operation                                                    |

| Table 21.  | AMD-762 System Controller Preliminary DDR Timing Information |

| Table 22.  | AGP 1x Mode Timings                                          |

| Table 23.  | AGP 2x Mode Timings                                          |

| Table 24.  | AGP 4x Mode Timings                                          |

| Table 25.  | 33-MHz PCI Interface Timings                                 |

| Table 26.  | 66-MHz PCI Interface Timings                                 |

| Table 27.  | AMD Athlon Processor System Bus/AMD-762 System               |

| - 4510 #11 | Controller AC Specification 70                               |

List of Tables ix

### AMD-762<sup>™</sup> System Controller Data Sheet

| Table 28. | AMD-762 System Controller Pin Functional Grouping (1 of 5) | 76 |

|-----------|------------------------------------------------------------|----|

| Table 29. | AMD-762 System Controller Pin Functional Grouping (2 of 5) | 77 |

| Table 30. | AMD-762 System Controller Pin Functional Grouping (3 of 5) |    |

| Table 31. | AMD-762 System Controller Pin Functional Grouping (4 of 5) | 79 |

| Table 32. | AMD-762 System Controller Pin Functional Grouping (5 of 5) | 8( |

| Table 33. | Signal Descriptions Table Definitions                      | 81 |

| Table 34. | Signal Descriptions                                        | 82 |

| Table 35. | Initialization Pinstrapping                                | 94 |

| Table 36. | Pin Multiplexing Options                                   | 98 |

| Table 37. | Reset Pin States                                           | 99 |

| Table 38. | Valid Combinations for Ordering Parts10                    | 01 |

| Table 39. | Abbreviations10                                            | 04 |

| Table 40. | Acronyms 10                                                | በብ |

24416C - December 2001

X List of Tables

## **Revision History**

| Date                                                                                                      | Rev | Description                                                                                       |  |  |

|-----------------------------------------------------------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------|--|--|

| Dec./2001 C Added AMD-768 peripheral bus controller throughout as the Southbridge device for the chipset. |     | Added AMD-768 peripheral bus controller throughout as the Southbridge device for the MPX chipset. |  |  |

| June/2001 B-1 Package name in datasheet corrected from PBGA to CCGA.                                      |     | Package name in datasheet corrected from PBGA to CCGA.                                            |  |  |

| June/2001                                                                                                 | В   | Initial public release.                                                                           |  |  |

| Nov./2000                                                                                                 | Α   | Initial NDA release.                                                                              |  |  |

Revision History xi

24416C – December 2001

xii Revision History

## 1 Features

The AMD Athlon™ processor powers the next generation in computing platforms, delivering the ultimate performance for cutting-edge applications and an unprecedented computing experience.

The AMD-760MPX<sup>™</sup> and AMD-760MP<sup>™</sup> chipsets are highly integrated system logic solutions that deliver enhanced performance for the AMD Athlon<sup>™</sup> processor and other AMD Athlon processor system bus-compatible processors. The AMD-760MPX chipset consists of the AMD-762<sup>™</sup> system controller in a 949-pin Ceramic Column Grid Array (CCGA) package and the AMD-768<sup>™</sup> peripheral bus controller. The AMD-760MP chipset consists of the AMD-762 system controller in a CCGA package and the AMD-766<sup>™</sup> peripheral bus controller.

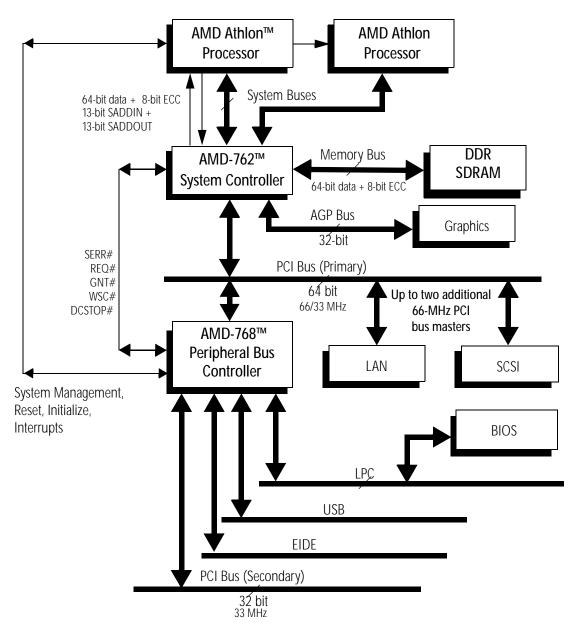

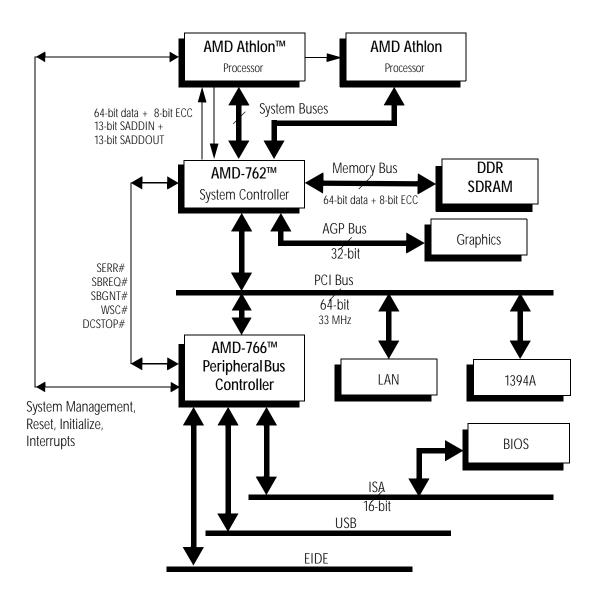

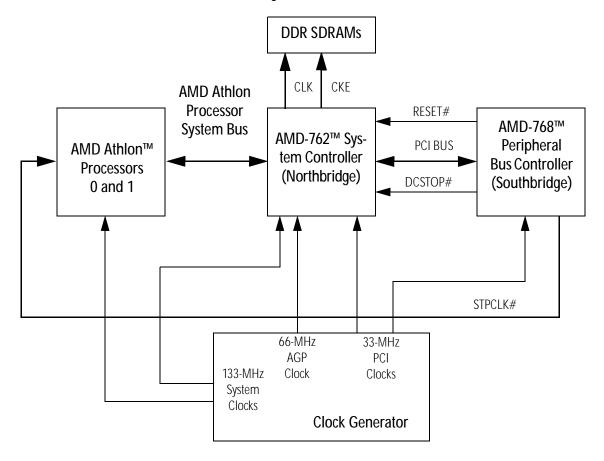

The AMD-762 system controller features the AMD Athlon system bus, system memory controller, Accelerated Graphics Port (AGP) controller, and Peripheral Component Interconnect (PCI) bus controller. Figure 1 on page 5 shows a block diagram for the AMD-760MPX chipset. Figure 2 on page 6 shows a block diagram for the AMD-760MP chipset.

The AMD-762 system controller is designed with the following features:

- Two AMD Athlon processor system buses support the high-speed, split-transaction AMD Athlon system bus interface. These buses are designed to operate at 100/200-MHz or 133/266-MHz double-data rate.

- A 66/33-MHz 64/32-bit PCI 2.2-compliant bus interface supports up to seven bus masters plus the AMD-766 peripheral bus controller at 33 MHz or up to two bus masters plus the AMD-768 peripheral bus controller at 66 MHz.

- The 66-MHz AGP 2.0-compliant interface supports 1x, 2x, and 4x data transfer mode.

- High-speed memory—The AMD-762 system controller is designed to support DDR SDRAM DIMMs, operating at either 100/200-MHz or 133/266-MHz double-data rate. Note that the DDR interface speed is always locked to the front-side bus speed.

This document describes the features and operation of the AMD-762 system controller. For a description of the AMD-766 peripheral bus controller, see the *AMD-766<sup>TM</sup> Peripheral Bus Controller Data Sheet*, order# 23167. For a description of the AMD-768 peripheral bus controller, see the *AMD-768<sup>TM</sup> Peripheral Bus Controller Data Sheet*, order# 24467. Key features of the AMD-762 system controller are provided in this section.

## 1.1 AMD Athlon™ System Buses

The AMD Athlon system buses have the following features:

- High-performance point-to-point system bus topology

- Source-synchronous clocking for high-speed transfers

- 200- or 266-MHz, split-transaction AMD Athlon system bus interface

- 1.6 Gbytes/s peak data transfer rates at 100/200 MHz, 2.1 Gbytes at 133/266 MHz

- Large 64-byte (cache line) data burst transfers

### 1.2 Integrated Memory Controller

The integrated memory controller has the following features:

- The AMD-762 system controller supports the following concurrencies:

- Processor-to-main-memory with PCI-to-main-memory

- Processor-to-main-memory with AGP-to-main-memory

- Processor-to-PCI with PCI-to-main-memory or AGP-to-main-memory

- Memory Error Correcting Code (ECC) support

- Supports the following DRAM:

- Supports 64-Mbit, 128-Mbit, 256-Mbit, and 512-Mbit technology

- 64-bit data width, plus 8-bit ECC paths

- · Flexible row and column addressing

- Supports up to 4 Gbytes of memory

- Four open pages within one CS (device selected by chip select)

- BIOS-configurable memory-timing parameters and configuration parameters

- 2.5-V memory interface operation with no external buffers or PLLs

- Concurrent DRAM writeback and read-around-write

- Burst read and write transactions

- Decoupled and burst DRAM refresh with staggered CS timing

- Provides the following refresh options:

- · Programmable refresh rate

- CAS-before-RAS

- Populated banks only

- Automatic refresh of idle slots—improves bus availability for memory access by the processor or system

### 1.3 PCI Bus Controller

The PCI bus controller has the following features:

- Compliance with *PCI Local Bus Specification*, Revision 2.2.

- Supports up to seven PCI bus masters plus the AMD-766 peripheral bus controller when operating in 33-MHz-only mode, or up to two PCI bus masters and the AMD-768 peripheral bus controller when operating in 66/33-MHz PCI mode.

- 64-bit interface, compatible with 3.3-V and 5-V PCI I/O

- Synchronous PCI bus operation up to 66 MHz

- PCI-initiator peer concurrency

- Automatic processor-to-PCI burst cycle detection

- Zero wait-state PCI initiator and target burst transfers

- Enhanced PCI command optimization, such as Memory Read Line (MRL), Memory Read Multiple (MRM), and Memory-Write-and-Invalidate (MWI)

#### **1.4** AGP Features

The AGP features include the following:

- Bus Features

- Compliance with Accelerated Graphics Port Interface Specification, Revision 2.0

- Synchronous 66-MHz 1x, 2x, and 4x data-transfer modes

- Multiplexed and demultiplexed transfers

- Up to four pipelined grants

- Support of Sideband Address (SBA) bus

- Request Queue Features

- Separate read-request and write-request queues

- Reordering of high-priority requests over low-priority requests in queue

- Simultaneous issuing of requests from both the write queue and read queue

- Graphics Address Remapping Table (GART) Features

- Conventional (two-level) GART scheme

- · Eight-entry, fully-associative GART table cache

- Three fully-associative GART directory caches

One 4-entry for PCI

One 8-entry for the processor

One 16-entry for AGP

### 1.5 Power Management

The power management features include the following:

- Compliance support for both Advanced Configuration and Power Interface (ACPI) and Microsoft® PC 99 power management

- The AMD-762 system controller supports the following power states:

- ACPI S1 (power on suspend) and S3 (suspend to RAM) sleep states

- Clock throttling with the processor's STPCLK#/stop grant mechanism

Refer to Figure 1 for a block diagram of the AMD-760MPX<sup>™</sup> chipset with an AMD-768 peripheral bus controller (66-MHz PCI). Refer to Figure 2 on page 6 for a block diagram of the AMD-760MP chipset with the AMD-766 peripheral bus controller (33-MHz PCI).

Figure 1. AMD-760MPX™ System Block Diagram (66-MHz PCI)

Figure 2. AMD-760MP™ Chipset System Block Diagram (33-MHz PCI)

## 2 Functional Operation

This section describes the functional operation of the AMD- $762^{\text{TM}}$  system controller.

### 2.1 Processor Interface

The two AMD Athlon processor system buses are high-performance, out-of-order, split-transaction buses, each capable of transferring one processor command and one probe response, one chip-set response and one probe request, and one data packet simultaneously. Data and command packets are transferred as packets of two, four, or eight datums on each edge of the 100-MHz or 133-MHz clock.

#### 2.1.1 Out of Order, Split Transaction

The split transaction buses separate the transfer of the command and the associated data into different transactions on different buses. Data may be returned in a different order than it was requested, subject to ordering rules.

A read transaction consists of a Read command sent from the processor to the memory system over the SADDOUT bus. When the memory system is ready to return data, a ReadData command is sent to the processor over the SADDIN bus to alert the processor that data is coming and identify the associated data request. The data is sent to the processor over the SDATA bus a programmable number of clocks later. Similarly, a write transaction is sent to the chipset over the SADDOUT bus, the chipset requests the associated write data over the SADDIN bus, and the data is transferred over the SDATA bus a programmable number of clocks later. Probes and probe responses are piggybacked with the other commands on the SADDIN and SADDOUT bus.

The split transaction scheme provides a high degree of parallelism between the various buses and facilitates pipeline flow or memory requests and responses.

#### 2.1.2 Point-to-Point, Source Synchronized

All of the AMD Athlon system bus signals use a terminated, point-to-point topology—that is, there is one signal connection plus termination on each end of each wire. The terminated point-to-point topology allows the use of incident wave signalling, eliminating most of the time for transmission line reflections. This feature allows high-transfer speeds while maintaining high signal integrity. All data transfer is synchronized by a clock generated at the data source. The clock and data propagate over matched length paths, minimizing skew between clock and data, and the data is sampled at the destination using this forwarded clock.

Data is sampled into a FIFO at the receiver synchronous to the forwarded clock and read out of FIFO a programmable number of processor clocks later, reducing all metastability concerns. The initialization procedure establishes the location of a common ClockN on both ends of the wire to within the system wide, clock distribution skew. A data object, transmitted from one end of the wire on ClockM, is sampled into the FIFO at the other end of the wire by ClockM forwarded with the data. It is read from the FIFO by ClockM+X that is generated in the receivers clock domain, X clocks later. X is a programmed constant that accounts for the worst case propagation delay.

A detailed description of the AMD Athlon system bus, including operations, initialization, and timing can be found in the  $AMD\ Athlon^{TM}\ System\ Bus\ Specification$ , order# 21902, and the  $AMD\ Athlon^{TM}\ System\ Bus\ Design\ Guide$ , order# 22666.

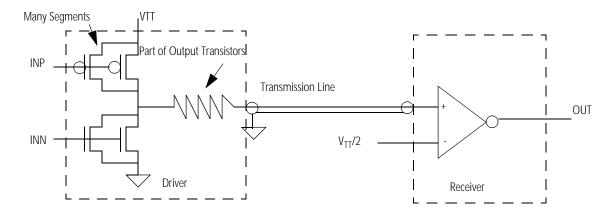

#### 2.1.3 Push-Pull Compensation

The AMD-762 system controller provides push-pull driver configuration. The push-pull driver scheme implements drivers with a user-defined output impedance. This feature allows the point-to-point signals to be source terminated without any external devices, greatly simplifying layout and reducing cost. In current semiconductor technology, it is not possible to implement a transistor with a tightly controlled impedance over realistic voltage, temperature, and process parameters. For this reason, a dynamic compensation scheme is implemented. For a push-pull transmission line example, see Figure 3 on page 9.

Figure 3. Push-Pull Transmission Line Example

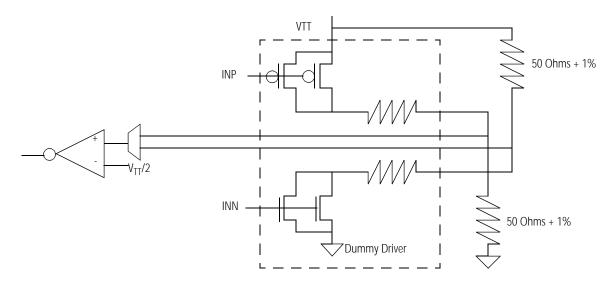

The dynamic compensation scheme implements a dummy driver with characteristics exactly matching the normal driver. An external precision resistor is attached, and the voltage of the resulting voltage divider is compared to  $V_{TT}/2$ . The drive strength is then adjusted until a voltage near  $V_{TT}/2$  is achieved. The output impedance then roughly matches the resistor value. Separate compensation is performed for the N and P transistors. The drive strength is changed in small steps when no data is being driven. Refer to Figure 4.

Figure 4. Dummy Load with External Compensation Resistors

## 2.2 Memory Interface

The AMD-762 memory controller arbitrates and optimizes incoming memory requests, handles ECC and Graphics Address Remapping Table (GART), and controls up to four double-data-rate (DDR) SDRAM DIMMs.

The AMD-762 system controller memory interface is designed to support registered DDR DIMMs. Up to four registered DIMMs can be supported by the AMD-762 system controller.

The AMD-762 system controller supports 64-Mbit, 128-Mbit, 256-Mbit, and 512-Mbit DDR devices. Device widths of x4, x8, and x16 are supported. Mixed banks are supported, meaning that a x8 DIMM can coexist with x4 and x16, etc.

Refer to Table 1 on page 11 for the total memory sizes for various registered DIMM configurations. A total of 4 Gbytes is supported.

DDR timing parameters are programmable via the AMD-762 system controller's memory controller configuration registers, allowing support of different DIMM configurations and loading. Refresh is also programmable, with support of various refresh rates as well as the ability to queue up to four outstanding refreshes. Clock pairs can also be selectively disabled to unpopulated DIMM slots via configuration register bits in the memory controller.

The memory controller supports up to four open pages in the active chip select. All pages in a chip select are closed when an access to another chip select is detected. Memory page operation can be further optimized by programming the number of idle cycles to a bank before the bank is automatically precharged.

Table 1. Total Memory Sizes

| Devices used on DIMM                                                                    | 1 DIMM<br>(2 Rows)<br>x64/x72 | 2 DIMMs<br>(2 Rows Each)<br>x64/x72 | 3 DIMMs<br>(2 Rows Each)<br>x64/x72 | 4 DIMMs<br>(2 Rows Each)<br>x64/x72 |  |

|-----------------------------------------------------------------------------------------|-------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|--|

| 64 Mbit (4M x 4 x 4 banks)                                                              | 256 Mbytes                    | 512 Mbytes                          | 768 Mbytes                          | 1 Gbytes                            |  |

| 64 Mbit (2M x 8 x 4 banks)                                                              | 128 Mbytes                    | 256 Mbytes                          | 384 Mbytes                          | 512 Mbytes                          |  |

| 64 MBit (1M x 16 x 4 banks)                                                             | 64 Mbytes                     | 128 Mbytes                          | 192 Mbytes                          | 256 Mbytes                          |  |

| 128 MBit (8M x 4 x 4 banks)                                                             | 512 Mbytes                    | 1 Gbytes                            | 1.5 Gbytes                          | 2 Gbytes                            |  |

| 128 MBit (4M x 8 x 4 banks)                                                             | 256 Mbytes                    | 512 Mbytes                          | 768 Mbytes                          | 1 Gbytes                            |  |

| 128 MBit (2M x 16 x 4 banks)                                                            | 128 Mbytes                    | 256 Mbytes                          | 384 Mbytes                          | 512 Mbytes                          |  |

| 256 MBit (16M x 4 x 4 banks)                                                            | 1 Gbytes                      | 2 Gbytes                            | 3 Gbytes                            | 4 Gbytes                            |  |

| 256 MBit (8M x 8 x 4 banks)                                                             | 512 Mbytes                    | 1 Gbytes                            | 1.5 Gbytes                          | 2 Gbytes                            |  |

| 256 MBit (4M x 16 x 4 banks)                                                            | 256 Mbytes                    | 512 Mbytes                          | 768 Mbytes                          | 1 Gbytes                            |  |

| 512 MBit (32M x 4 x 4 banks)                                                            | 2 Gbytes                      | 4 Gbytes                            | 4 Gbytes                            | 4 Gbytes                            |  |

| 512 MBit (16M x 8 x 4 banks)                                                            | 1 Gbytes                      | 2 Gbytes                            | 3 Gbytes                            | 4 Gbytes                            |  |

| 512 MBit (8M x 16 x 4 banks)                                                            | 512 Mbytes                    | 1 Gbytes                            | 1.5 Gbytes                          | 2 Gbytes                            |  |

| Note: The maximum address space supported by the AMD-762 system controller is 4 Gbytes. |                               |                                     |                                     |                                     |  |

Support of four registered DIMMs is accomplished by the AMD-762 system controller's eight DDR chip-select pins (CS[7:0]#), which allow DIMMs with two chip selects as illustrated in Figure 5 on page 12. In this example, each DIMM contains two physical DRAM banks, thus two chip selects are routed to the DIMM. The AMD-762 system controller provides one differential clock pair for each registered DIMM.

Figure 5. AMD-762™ System Controller Connection to DDR DIMMs

#### 2.2.1 DRAM Refresh

The AMD-762 system controller keeps track of when each of CS[7:0] needs to be refreshed. Each CS is refreshed independently. Refresh is only performed on rows that are populated. A concurrent refresh cycle can be executed in parallel with other read and write requests, if there is no CS conflict and the command bus is free. Figure 6 on page 13 shows DRAM refresh timing.

Refresh rates are programmable by BIOS and can accommodate various rates at 100-MHz or 133-MHz system bus speeds.

Figure 6. DRAM Refresh Timing

#### 2.2.2 DDR Data Strobes

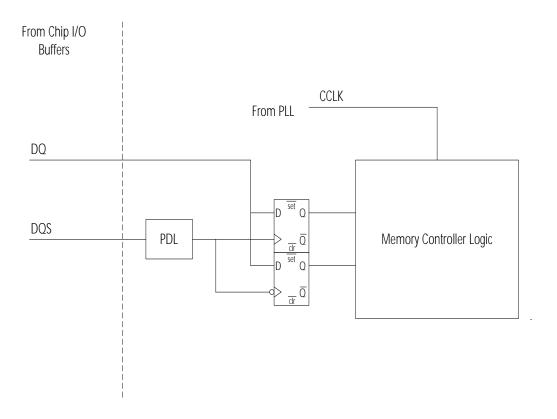

Unlike single data rate SDRAMs, Double Data Rate (DDR) does not latch data on the rising edge of the memory clock. Instead, DDR devices specify bidirectional data strobes (DQS pins) between the system memory controller and the DDR memories that are used to capture data. The data strobes are source-synchronous, which means that the DQS signals are driven by the device that is currently driving the data bus. The AMD-762 system controller provides one DQS pin per byte when using x8 and x16 DIMMs, or one per nibble when using x4 DIMMs. The Data Mask (DM) pins provide the additional DQS strobe function when accessing a x4 DIMM. The DM pins no longer provide a mask function when performing a write access to a x4 DIMM. Therefore, a read-modify-write cycle occurs for partial write accesses ("partial" implying an incomplete quadword of data). In the case of writes to memory, the AMD-762 system controller must drive DQS such that each edge is centered in the write-data valid window to allow the DDR DRAMs to capture the data on each edge of the strobe. For memory reads, the devices drive the DQS pins edge-aligned with the memory clock, and the AMD-762 system controller must center the DQS with the incoming data. Delaying the DQS accordingly for each byte or nibble is required. Because this timing is very tight, the AMD-762 system controller implements Programmable Delay Lines (PDLs) to accomplish this centering of DQS with the data. A separate PDL is implemented for each DQS pin.

Because the propagation delay of an individual buffer internal to the AMD-762 system controller is a function of Process, Voltage and Temperature (PVT), a mechanism is required to compensate for these three variables. As mentioned above, the delay value is known, but the number of buffers that provides this delay value is not known for a given PVT point. The calibration mechanism provides this piece of information. The mechanism used is a simple measurement of how many buffer delays are required to equal the system clock period. Because the system clock is generated by a PLL in the AMD-762 system controller that is already compensated for PVT, the system clock period is independent of PVT. Therefore, the clock period can be assumed to be a constant, and can be used to correlate the PDL values to units of time.

The calibration is automatically performed once after reset and once after self-refresh exit (before acknowledging self-refresh exit), and the resultant value is transferred to each PDL. Recalibration can be initiated via software. The AMD-762 system controller also has a mode that enables periodic autocalibration.

#### 2.3 PCI Bus Controller

The AMD-762 system controller supports both 32-bit and 64-bit PCI agents on a cycle-by-cycle basis as defined by the PCI bus specification. The AMD-762 system controller asserts the REQ64# pin during reset to allow 64-bit devices to detect that the host bridge supports the full 64-bit data width. All 64-bit transactions from these bus masters are then negotiated with the PCI bus REQ64#/ACK64# protocol. The address space is still 32-bits maximum when operating with 64-bit transactions.

The AMD-762 system controller supports two PCI clock speed options as follows:

■ 66/33-MHz mode that supports a 66-MHz Southbridge and two 66-MHz PCI bus slots or on-board chips. In this mode, the AMD-762 system controller provides the clocks for the Southbridge and the two optional PCI bus agents. If any of these devices are 33 MHz only (the M66EN pin is Low), then the AMD-762 system controller automatically drives 33 MHz on the PCI\_66CLK[2:0] pins during reset.

■ 33-MHz-only mode that always supports 33-MHz maximum PCI bus speed. In this mode, the Southbridge and all downstream PCI agents are clocked from the system clock generator's PCI clocks.

The desired PCI clocking mode is selected with the AD[15] pinstrap on the AMD-762 system controller. Refer to Chapter 7 on page 81 for details of the AMD-762 system controller's pinstrapping.

The AMD-762 system controller drives the 64-bit PCI bus synchronously with the PCI clock. For 32-bit agents, the AMD-762 system controller converts the 64-bit processor data to 32-bit PCI data and regenerates commands with minimal overhead. A processor-to-PCI posted write buffer enables the processor and PCI to operate concurrently. The AMD-762 system controller converts consecutive processor addresses to burst PCI cycles. A PCI-to-DRAM posted write buffer and a DRAM-to-PCI prefetch buffer enable concurrent PCI bus and processor-DRAM accesses during PCI-initiator transactions.

When the processor drives an I/O cycle to an address other than the AMD-762 system controller configuration register addresses, the AMD-762 system controller passes the I/O cycle to the PCI bus and responds to the CPU only after the PCI cycle completes. The AMD-762 system controller does not respond to I/O cycles driven by PCI initiators on the PCI bus. The AMD-762 system controller allows these cycles to complete on the PCI bus. A memory write is the only transaction permitted from PCI to AGP.

The PCI block can be broken up into two sub-blocks—the PCI target module and the PCI master module. The PCI target module handles cycles initiated by an external master on the PCI bus. The AMD-762 system controller responds to cycles that are directed to main memory or writes that are sent to the other PCI interface (the AGP interface). This module contains write buffers (PCI-to-memory and PCI-to-PCI), read buffers from memory, and a target sequencer that keeps track of the bus while the AMD-762 system controller is a PCI target.

The PCI master module handles processor-to-PCI bus cycles. Within a processor stream, no reordering is done.

#### 2.3.1 Memory Coherency

The AMD-762 system controller assures that all data accesses remain coherent:

- All PCI/AGP accesses not in the GART range generate processor probes assuring that reads receive only the latest version of the data and that writes update only the latest version of the data. Writes are always performed in order.

- The GART range is by definition not cacheable. As a result, all PCI/AGP accesses that are in the GART range are subject to non-cacheable ordering rules—that is, they do not generate probes to the processor, writes are performed in order, and reads receive the results of all earlier writes.

- Processor accesses to addresses mapped by the GART range can either use the GART for the final address translation or map the addresses through its page tables as a noncacheable memory type.

#### 2.3.2 PCI Arbitration

The AMD-762 system controller contains arbitration logic that allocates ownership of the PCI bus among itself on behalf of the processors, the Southbridge, and other PCI initiators.

The AMD-762 supports up to seven bus grant pins and a dedicated grant pin for the Southbridge when operating in legacy mode. The request/grant pairs used depend on the system configuration supported as described in the following sections.

Legacy Mode—Single PCI Bus Southbridge

The legacy mode implies a standard system configuration where the PCI bus typically operates at 33 MHz with a common Southbridge such as the AMD-766 peripheral bus controller. All PCI agents connect to this PCI bus segment and their request grant pairs are connected to the AMD-762 system controller's REQ[6:0]# and GNT[6:0]# pins, while the Southbridge connects to the SBREQ#/SBGNT# pins.

The SBREQ#/SBGNT# pins are treated differently than the standard request/grant pairs as is required for legacy ISA DMA cycles. To avoid potential deadlock conditions, the AMD-762 system controller allows the SBREQ# to be asserted for extended periods of time. Bus masters using the REQ[6:0]# and GNT[6:0]# signals are preempted when another requestor

asserts its PCI request pin, but the Southbridge is allowed to complete its transactions before the SBGNT# is deasserted.

#### Southbridge with an Integrated PCI-PCI Bus Bridge

A significant performance benefit of the AMD-762 system controller is the support of a 66-MHz, 64-bit PCI bus. This allows the system to support peripherals that consume much higher bandwidth, but it requires a 66-MHz Southbridge and is limited to a maximum of two additional PCI slots due to the tight 66-MHz PCI timing.

In this configuration, an AMD-768™ peripheral bus controller supports a 66-MHz PCI primary bus, and integrates a PCI to PCI bridge. The secondary bus of this bridge supports a 32-bit, 33-MHz PCI bus that supports up to seven slots that can be used for less bandwidth-intensive peripherals. In this system configuration, the Southbridge connects to the AMD-762 system controller's REQ[0]# and GNT[0]# request/grant pair, and the two optional slots on the primary bus connect to the REQ[2:1]# and GNT[2:1]# pairs. All 32-bit, 33-MHz PCI slots are arbitrated by the Southbridge and therefore connect their request/grant pairs to the Southbridge.

**Note:** Only REQ[2:0]# and GNT[2:0]# should be used when operating the primary PCI Bus at 66 MHz.

#### **Arbitration Priority**

Access priority rotates between the Southbridge (when connected to the SBGNT# pin) and CPU/PCI bus masters (GNT[6:0]#) such that the following arbitration sequence could be seen in a busy system:

- 1. Southbridge (SBGNT# pin only)

- 2. CPU

- 3. Southbridge (SBGNT# pin only)

- 4. PCI master (one of GNT[6:0]#)

- 5. Repeat step 1

The SBREQ#/SBGNT# pin should be used only with a legacy Southbridge such as described in "Legacy Mode—Single PCI Bus Southbridge" on page 16.

When there are no requests for the bus, ownership can default to either processor through the AMD-762 system controller or the last PCI bus master that had bus ownership. This mode is called bus parking and is controlled by the PCI Arbitration Control register (Dev 0:F0, 0x84, bit 0).

#### 2.3.3 PCI Configuration

The AMD-762 system controller uses PCI configuration mechanism #1 to select all of the options available for interaction with the processor, DRAM, and the PCI bus. This mechanism is defined in the *PCI Local Bus Specification*, Revision 2.2. All configuration functions for the AMD-762 system controller are performed by using two I/O-mapped configuration registers—IO\_CNTRL (I/O address 0CF8h) and IO\_DATA (I/O address 0CFCh).

These two registers are used to access all the other internal configuration registers of the AMD-762 system controller. The AMD-762 system controller decodes accesses to these two I/O addresses and handles them internally. A read to a nonexistent configuration register returns a value of FFh. Accesses to all other I/O addresses are forwarded to the PCI bus as regular I/O cycles. Read and write cycles involving the AMD-762 system controller configuration registers are only distinguished by the address and command that is sent.

The AMD-762 system controller implements the following configuration spaces:

- Device 0:Function 0 (host bridge configuration registers)

- Device 0:Function 1 (DDR I/O and PDL configuration)

- Device 1:Function 0 (PCI-PCI bridge, AGP configuration)

The Device 0:Function 1 space is disabled by default, and must be enabled by writing to a specific bit in the PCI Control register (Dev 0:F0:0x4C). The normal reserved PCI header space (0x00-0x3F) in this function returns all 1s.

#### 2.3.4 PCI Parity/ECC Errors

The AMD-762 system controller indicates that an ECC error occurred on the memory bus by setting a bit in the status register and optionally asserting the PCI SERR# signal. This action results in the error being reported by the Southbridge.

The AMD-762 system controller does not check parity on the PCI bus. The status bit (Dev 0:04h, bit 31) is always 0.

### 2.3.5 PCI Accesses by an Initiator

A PCI initiator begins a memory read or write cycle by asserting FRAME# and placing the memory address on AD[31:00] (note that the AMD-762 system controller supports a maximum address space of 32 bits). The AMD-762 system controller decodes the address. If the address is within the memory region as defined by PCI Top of Memory (Dev 0:F0:0x9C), the AMD-762 system controller accepts the cycle and responds as a PCI target by asserting DEVSEL#. If the address is not within the defined memory region, the AMD-762 system controller ignores the cycle and allows it to complete on the PCI.

Read requests from PCI masters to the memory subsystem are full cache lines only. After fetching the initial cache line, the AMD-762 system controller can optionally start prefetching the next cache line. Prefetching the next cache line is preferred, because the PCI master typically reads more than one line, but can waste DRAM bandwidth if this line is thrown away.

The length of a read request is always 8 quadwords (one cache line). During writes, the AMD-762 system controller attempts to accumulate an entire cache line. If the start address is not cache aligned, the AMD-762 system controller makes single write requests until it reaches a cache-aligned address. When aligned, it makes a request every 8 quadwords. If a partial cache line write is detected, no more data is accumulated, and a request is issued to the memory subsystem.

## 2.4 Accelerated Graphics Port (AGP)

The Accelerated Graphics Port (AGP) is a point-to-point connection between a graphics adapter (AGP initiator) and the AMD-762 system controller memory controller (AGP target), which enables the adapter to store and use graphics data in main memory. This connection relieves graphics traffic from the PCI bus and greatly accelerates video performance.

The AMD-762 system controller functions as an AGP target, providing all the signals, buffers, and logic required for full compliance with the *Accelerated Graphics Port Interface Specification*, Revision 2.0.

While AGP relieves traffic on the PCI bus and frees up graphics adapter memory, the greatest impact on system performance comes from the many innovations AGP brings to data transfer operations. These improvements include the following:

- *Split Transactions*—Requests to read or write data are separate from the data transfers.

- Pipelined Requests—Requests can be issued contiguously and stored in the AMD-762 system controller request queue. Pipelining allows AGP to achieve high levels of concurrency with PCI and the processor.

- *Pipeline Grants*—Pipelined GNT# signals for up to four write transactions.

- Prioritizing (reordering)—Read and write requests can be assigned a high priority or a low priority to ensure that more urgent requests are serviced first.

- *Defined-Length Requests*—The amount of data requested is indicated in the AGP command, rather than the duration of an asserted signal, such as FRAME# in PCI.

- An 8-byte minimum data size for AGP 2x/4x transfers, which provides a more efficient method for moving the large amount of data typical in a graphics request.

- A separate, optional Sideband Address (SBA) bus that enables concurrent transmissions of requests and data transfers.

- Optional 2x/4x modes that increase the AGP graphics adapter data transfer rate.

- Freedom from the coherency requirements of PCI, which eliminates the latency resulting from cache snooping.

- Full PCI 2.2 capability, which enables the AMD-762 system controller to pass programming information from the processor to the graphics adapter.

- A Graphics Address Remapping Table (GART).

The AGP request queue is split up into two queues—one for read requests and one for write requests. Because there is a reordering FIFO in the address module, the request queues do not have to be large. The read queue is big enough to hold all outstanding read requests, which avoids stalling writes that run on the bus while the reads occur to memory.

Requests from the SBA bus are multiplexed with PIPE# requests and written to the same queues. High-priority requests are inserted in front of low-priority requests so that the request to be serviced is at the top of the queue. This reordering is done dynamically as a new request is written into the queue.

Requests from each of the queues can be read out of both the queues at the same time. The reads start fetching data from memory and the write data is sent across the AGP bus at the same time.

The AGP ordering rules specify that writes are ordered ahead of reads. Reads are serviced only when all the preceding writes have been written to memory, which is only required for low-priority requests and does not affect high-priority read requests. When a low-priority request is the next one to be serviced from the read queue, the tag of that request is compared with all valid entries in the write queue. If any entry matches, then the read request is blocked. Only after the write requests are serviced are the read requests allowed to proceed.

AGP Request Queue. In general, the AGP request queue services AGP requests in the order received, subject to their priority (write High, read High, write, read).

**Ordering Rules**. The request queue is subject to the following AGP ordering rules:

- High-priority write requests are processed in the order they are received.

- High-priority read requests are processed in the order they are received.

- Low-priority write requests are processed in the order they are received.

- Low-priority read requests are processed in the order they are received.

- Low-priority reads push low-priority writes, meaning that a write request is serviced before a subsequently received read request is serviced.

- Low-priority writes can pass low-priority reads, meaning that a write request can be serviced before a previously received read request.

- There are no ordering restrictions between AGP and PCI transactions on the AGP bus.

- PCI transactions on the AGP bus follow the PCI ordering rules described in the *PCI Local Bus Specification*, Revision 2.2.

- High-priority requests are re-ordered in front of low-priority requests.

- There is no ordering relationship between high-priority reads, high-priority writes, and any other transfer type, such as low-priority reads, low-priority writes, PCI reads, or PCI writes.

If a low-priority data transfer is in progress when a high-priority request is received, the data transfer completes before the high-priority request is serviced—that is, a request is not preemptable. A high-priority request supersedes a low-priority request on a request boundary only.

## 2.5 System Clocking

The AMD-762 system controller requires the following system clocks:

- SYSCLK, used for clocking the AMD Athlon system busses and the DDR DRAM interface. This clock is typically either 100 MHz or 133 MHz. This clock is also used to create the differential DDR DRAM clock outputs (CLKOUT[5:0], CLKOUT[5:0]#).

- AGPCLK, 66 MHz, used for clocking the AGP and PCI internal logic. This feeds the PCI 66-MHz PLL in 66/33-MHz PCI mode.

- PCICLK, provides a 33-MHz PCI bus clock and is used to synchronize the PCI bus I/O signals to the 33-MHz PCI signal domain when operating in 33-MHz-only PCI mode.

There are two different clocking schemes for the PCI bus and Southbridge as described in the following sections.

#### 66-MHz PCI Bus

The highest performance option supports a 66-MHz primary PCI bus on the AMD-762 system controller, with a 33-MHz secondary PCI bus controlled by an AMD-768 peripheral bus controller's PCI to PCI bridge. This mode also provides up to two optional slots for 66-MHz peripherals.

The AMD-762 system controller provides the three 66-MHz clocks required for the Southbridge and the two PCI bus slots in this mode. If a 33-MHz-only card is inserted in one of the 66-MHz PCI slots, then the M66EN signal is deasserted, which causes the AMD-762 system controller to drive 33 MHz on the PCI\_66CLK[2:0] pins.

The 66-MHz PCI mode is illustrated in Figure 7.

#### 33-MHz PCI Bus

An alternate mode of PCI bus operation is illustrated in Figure 8 on page 24, and simply supports a standard 33-MHz PCI Southbridge and up to seven PCI slots.

In this mode, all PCI devices operate at 33 MHz and clocking is provided by the motherboard clock generator chip.

Figure 7. System Clocking with 66-MHz PCI Primary Bus

The AMD-762 system controller implements three internal PLLs to control clock skew on-chip for the SYSCLK, AGPCLK, and PCICLK domains. An external feedback path is required on the motherboard for the 66-MHz PCI PLL when operating in 66-MHz mode. This requires the PCI\_66CLK[0] output pin to be connected back into the AMD-762 system controller's PCICLK input for skew control, as shown in Figure 7 on page 23.

These PLLs can be bypassed for motherboard testing. Refer to Chapter 3 for further details of PLL bypass testing.

Figure 8. System Clocking with 33-MHz PCI Bus

# 2.6 Power Management

The AMD-762 system controller supports the Advanced Configuration Power Interface (ACPI) specification, On-Now, and PC 99 requirements through a handshake mechanism with the processor. The ACPI-defined registers required for processor and system power management are contained in the Southbridge. SMM memory remapping is handled by a model-specific register in the AMD Athlon processor. See the  $AMD\ Athlon^{TM}\ BIOS\ Developers\ Guide$ , order# 21656, for more information about the SMM remapping operation.

Figure 9 shows how the processor and system controller communicate power-state transitions.

Figure 9. Power Management Signal Connections

The processor and the AMD-762 system controller communicate power-state transitions through the AMD Athlon system bus connect/disconnect protocol and special cycles (masked writes to a defined AMD Athlon system bus address with specific data encoding). In general, the processor initiates a request for a disconnect with a special cycle, and the AMD-762 system controller may or may not actually disconnect the processor with the connect/disconnect protocol. The AMD-762 system controller performs the requested connect/disconnect as part of the process of entering and exiting certain ACPI states. The following two special cycles are of interest:

- Halt—Generated by the AMD Athlon processors in response to executing a HALT instruction. The AMD-762 system controller forwards the Halt special cycle to the PCI bus but does not perform any further power management for Halt conditions. The processor buses remain connected and the memory is not placed in self-refresh mode.

- Stop Grant—Generated by the AMD Athlon processors in response to assertion of STPCLK#. When the AMD-762 system controller receives a Stop Grant from the processor, it waits for a Stop Grant from the second processor (if installed), then it sends a Stop Grant special cycle on the PCI bus. The AMD-762 system controller initiates the following sequence of actions if the Stop Grant disconnect bit is set (Dev 0:F0:0x60):

- A. Disables PCI/AGP arbitration and waits for all queues to memory to be empty (including refresh requests).

- B. Completes the AMD Athlon system bus cycles. The AMD-762 system controller then initiates an AMD Athlon system bus disconnect to the processors, and causes the memory to enter self-refresh.

- C. The Southbridge decodes the special cycle and enters the appropriate power state. The Southbridge can then assert DCSTOP#.

Halt special cycles are generally considered part of an ACPI state definition (C1). STPCLK#, however, can be asserted at random times while the processor is in the full-running state (C0) to conserve power (clock throttling).

The AMD-762 system controller supports the following power states:

- 1. ACPI C0 full-on

- 2. ACPI C1 Halt

- 3. ACPI S1 power-on suspend

- 4. ACPI S3 suspend to RAM

These power states are described in further detail in subsequent paragraphs.

## 2.6.1 Full-On (C0)

In this state, the AMD-762 system controller is fully operational, all clock trees are running, all voltage planes are enabled, and the AMD-762 system controller provides normal refresh to DRAM.

## 2.6.2 Halt (C1)

If the AMD-762 system controller detects a Halt special cycle from either of the processors, the Halt state (C1) is entered and the Halt special cycle is driven on the PCI bus. No further activity is required. The processor buses remain connected and the memory remains in normal refresh mode.

## 2.6.3 Throttling with STPCLK# Assertion

The AMD-762 system controller supports clock throttling via assertion of the processor's STPCLK# pin. If the AMD-762 system controller has detected a Stop Grant special cycle from the processor, the AMD-762 system controller waits for a Stop Grant from the second processor (if installed), then the Stop Grant special cycle is driven on the PCI bus. If the Stop Grant disconnect bit is set (Dev 0:F0:0x60), when the Stop Grant special cycle state is received, and there is no probe traffic, the AMD-762 system controller disconnects the processor and places system memory into self-refresh mode before passing the special cycle to the PCI Bus. If the AMD-762 system controller detects a PCI DMA master transaction that needs a snoop, then the processors are connected, DRAM is taken out of self-refresh mode, and the probe cycle(s) are initiated on the AMD Athlon processor system buses. If the processors do not start any non-NOP AMD Athlon processor system bus cycles

while the probe is in progress, then the AMD-762 system controller disconnects the AMD Athlon processor system bus following the completion of the probe. If the processors start sending non-NOP AMD Athlon processor system bus cycles while connected, then the AMD-762 system controller transitions to the full-on state.

## 2.6.4 Power-On Suspend (S1)

The S1 state achieves very low power by disconnecting the processors, entering self-refresh, and then gating off most of the internal high-speed clock trees in the AMD-762 system controller. Snooping is prevented by the device drivers prior to entering this state. The DDR DRAM clocks continue to be driven as required for the registered DDR DIMMs. Most internal clocks are gated off, allowing the AMD-762 system controller to achieve a low operating current.

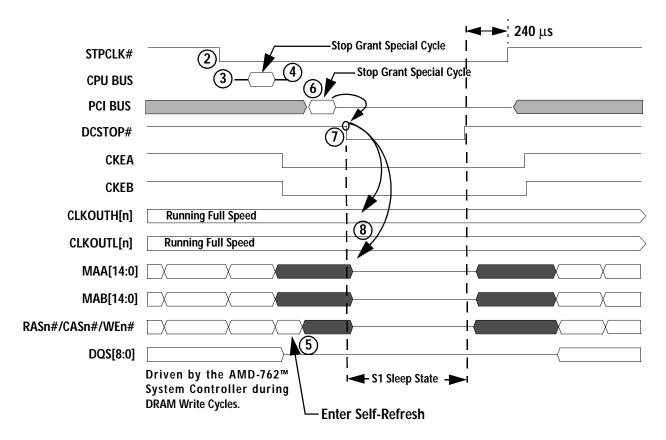

The S1 state is entered in a similar manner to clock throttling, starting with a STPCLK# assertion and the Stop Grant state. The Southbridge asserts the DCSTOP# signal, which is used by the AMD-762 system controller to gate off internal clock trees for lower power. All power supplies remain on, and the clock synthesizer chip on the motherboard continues to drive all clocks. The sequence of operation for entering the S1 state is listed below. Figure 10 on page 30 shows a power-on suspend system timing diagram example.

#### **S1 Sequence**

- 1. The operating system communicates with all device drivers, causing them to disable their respective peripherals, thus preventing any new bus master activity (DMA) on the PCI and AGP buses. DMA activity already in progress in the AMD-762 system controller completes normally.

- 2. The Southbridge asserts STPCLK# to both AMD Athlon processors.

- 3. The processors flush their buffers and generate a Stop Grant special bus cycle on the AMD Athlon processor system bus.

- 4. After receiving both Stop Grant special cycles, the AMD-762 system controller flushes all internal queues and initiates a disconnect cycle to the CPUs by deasserting their CONNECT pins. The AMD Athlon processors respond by deasserting the PROCRDY signal.

- 5. After all queues are flushed, the AMD-762 system controller's power management logic requests the DRAM controller to place the DRAM in self-refresh mode. The DRAM controller initiates self-refresh, then acknowledges to the power management logic.

- Self-refresh mode is initiated by generating an autorefresh cycle and deasserting the CKE pins.

- 6. The AMD-762 system controller issues a Stop Grant special cycle on the PCI bus.

- 7. The Southbridge detects the Stop Grant special cycle on the PCI bus and asserts the DCSTOP# signal.

- 8. The AMD-762 system controller samples DCSTOP# active and gates off most of the internal clock trees. The DDR DRAM address/command outputs are three-stated. The CKE pins remain driven Low. The external clock sources and the AMD-762 system controller PLLs continue to run.

- Note that the DDR DRAM clocks (CLKOUT[5:0], CLKOUT[5:0]#) continue to run. This action is required because the reset signal to the registered DIMMs is connected to the AMD-762 system controller's RESET# pin. The RESET# pin is not asserted in the S1 state, thus the clocks cannot be removed from the registered DIMMs.

Note: Circled numbers correspond to "S1 Sequence" on page 28.

Figure 10. Power On Suspend System Timing Diagram Example

This state is exited when the DCSTOP# signal is deasserted by the Southbridge, followed by a deassertion of STPCLK#. This action causes the AMD-762 system controller to enable the clock trees and prepare to reconnect the processor. The processors assert their respective PROCRDY signal, which causes the AMD-762 system controller to exit self-refresh and reconnect the AMD Athlon processor system buses. The AMD-762 system controller retains the state of all configuration registers during the S1 state.

## 2.6.5 Suspend to RAM (S3)

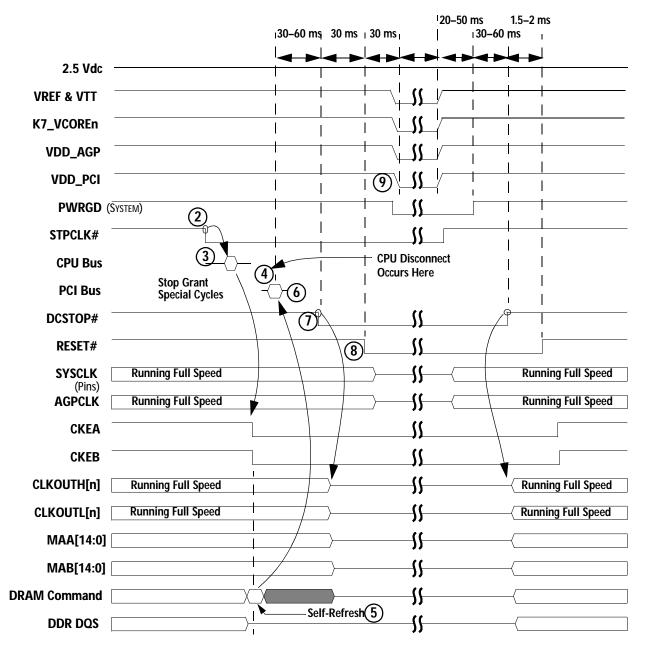

The S3 state is similar to S1. However, power is removed from most of the motherboard except the AMD-762 system controller, DRAM, and a portion of the Southbridge. S3 is the

lowest power sleep state, and allows very fast resume because system context is stored in memory instead of on disk.

The S3 state is entered similarly to S1 with a Stop Grant special cycle and DCSTOP#. After entering S3 state with DCSTOP# assertion, the Southbridge asserts the RESET# signal, which causes the AMD-762 system controller to gate off its I/O rings to accommodate the voltages being removed from the AMD Athlon processor system bus, PCI bus, and AGP bus. The AMD-762 system controller core remains powered (2.5 Vdc) as does the DDR I/O interface and the DDR DIMMs, to allow the memory to remain in self-refresh mode with the CKE pins driven Low. The sequence of operation for entering the S3 state is listed below. Figure 11 on page 33 shows a suspend to RAM system timing diagram example.

#### S3 Sequence

- 1. As with the S1 state, the device drivers are called to place all devices into the D3 device state, which prevents them from trying to master on the bus they reside (or access system memory).

- 2. The ACPI driver (or BIOS under APM) writes to the appropriate registers in the Southbridge to initiate the hardware sequence into the S3 state. In response to this write, the Southbridge asserts STPCLK# to the AMD Athlon processors. Once STPCLK# has been asserted, the power management state machine in the Southbridge waits for a Stop Grant special cycle on the PCI bus before completing the transition into the S3 state.

- 3. The CPUs recognize that STPCLK# has been asserted, flushes internal buffers, and generates a Stop Grant cycle on the AMD Athlon processor system bus.

- 4. After detecting both Stop Grant special cycles on the processor buses, the AMD-762 system controller flushes all internal queues including outstanding probes, then deasserts the CONNECT pins. The CPUs respond by deasserting their respective PROCRDY pins.

- 5. When the disconnect is complete, the AMD-762 system controller executes a self-refresh command to the DDR SDRAM and waits for it to complete (this action is accomplished by issuing an auto-refresh command and driving the CKE signals Low to the DRAM).

- 6. The AMD-762 system controller issues a Stop Grant special cycle on the PCI bus.

- 7. The Southbridge asserts DCSTOP#. The AMD-762 system controller follows the normal DCSTOP# protocol as described in "S1 Sequence" on page 28, including gating most of the internal clocks off. The DDR output clocks (CLKOUT[5:0], CLKOUT[5:0]#) continue running for an additional six clock periods from the assertion of RESET#. This action is required because the DIMM reset signal on registered DIMMs is connected to the AMD-762 system controller RESET# pin, and the DIMM clocks must be running while the DIMM reset is first asserted.

- 8. The Southbridge asserts PCIRST# (RESET# system controller). The AMD-762 AMD-762 system controller continues driving the CKE pins Low, and gates off the I/O pads to prevent driving 1s to the unpowered I/O ring and to inhibit floating inputs from the unpowered I/O rings to the powered core logic. The input clock pins (SYSCLK, AGPCLK, and PCICLK) are also gated off because these input pins are floating when the motherboard's 3.3 Vdc is powered off. The two STR bits in the DRAM Mode/Status register (Dev 0:F0:0x58) are cleared to 0s. The state of all other memory controller configuration register bits is preserved.

- 9. The Southbridge signals the power supply (deasserts PWRON#) to shut down all but the 5-Vdc and 2.5-Vdc voltages. The motherboard clock generator chip shuts down, therefore the input clocks (SYSCLK, AGPCLK, and PCICLK) float.

Note: Circled numbers correspond to "S3 Sequence" on page 31.

Figure 11. Suspend to RAM System Timing Diagram Example

The S3 state is exited when the Southbridge detects an enabled resume event. The Southbridge powers up all of the voltage planes that are off during the S3 state by asserting PWRON#. After all of the voltage planes in the system are within specification, and all of the outputs of the system clock generator are running within specification, PWRGD is asserted to the Southbridge. The Southbridge then deasserts DCSTOP# followed by deassertion of PCIRST# (the RESET# pin on the AMD-762 system controller).

The AMD-762 system controller retains the state of the memory controller configuration registers, which allows BIOS to immediately access memory to retrieve and restore the system context. There are two configuration bits that BIOS uses to allow the AMD-762 system controller to differentiate between S3 and all other states following an active to inactive transition on the RESET# pin. Upon exiting the S3 sleep state, BIOS writes the appropriate value to these bits, which causes the AMD-762 system controller to exit self-refresh. The two register bits (STR\_Control) are in the DRAM Mode/Status register (Dev 0:F0:0x58). Refer to the  $AMD-762^{TM}$  System Controller Software/BIOS Design Guide, order# 24416 for detailed information on these bits.

# 3 Test

The AMD-762<sup>TM</sup> system controller supports test modes that may be used in some cases for motherboard manufacturing test and debug. The following test modes are available on the AMD-762 system controller:

- Three-state test

- NAND tree test

- PLL bypass test

- Clock output test

Three-state test and NAND tree test can be used to prevent the AMD-762 system controller from driving its pins and to verify connectivity of the AMD-762 system controller to the motherboard. The PLL bypass and clock output test modes are provided primarily for motherboard debug and can be used to verify system clocking and drive slower clocks into the system.

Test modes are invoked in the AMD-762 system controller by the assertion of the TEST# pin in conjunction with enabling specific pinstraps on the PCI bus AD[31:0] pins, as described in each section. These pins can be used as pinstraps for various functions by connecting either a pullup or pulldown resistor as required to enable or disable the function (a 10-kohm resistor should be used). The pinstraps are sampled at reset and latched, and the value of most pinstraps can be read in the Configuration Status register (Dev 0:F0:0x88).

Asserting the RESET# pin and de-asserting the TEST# pin causes the AMD-762 system controller to exit test modes.

# 3.1 Board (Three-State) Test Mode

Board test mode forces all AMD-762 system controller outputs to a high impedance to allow board-level test equipment to drive the nodes normally driven by AMD-762 system controller pins to test board connectivity. The outputs are three-stated after a maximum of six clocks are driven on the SYSCLK and AGPCLK pins. The minimum number of clocks is required due

to some I/O cells that cannot be asynchronously forced into a three-state mode.

Board test mode is entered when the AD[25] pin is asserted High simultaneous with the TEST# pin during RESET# assertion. The test mode is then latched coming out of reset. The AD[09] pin should also be pulled up to force the internal PLLs to be bypassed.

Three-state mode can be exited by an assertion of the RESET# pin. This reset also disables the PLL bypass mode if it was entered.

## 3.1.1 Board Test Mode Clocking

When entering three-state mode, the PLLs should also be bypassed as described above. This procedure forces the clocks driven on the SYSCLK and AGPCLK input pins to be routed directly to the appropriate clock domains. The SYSCLK and AGPCLK pins must then be clocked for six clocks as required to force some AMD-762 system controller I/O pads to the three-state mode.

## 3.2 NAND Tree Test Mode

NAND tree testing is used on the tester and can also be used during board testing to test connectivity of AMD-762 system controller inputs. In this test mode, each AMD-762 system controller input can be asserted one pin at a time, and for each pin assertion there should be a change in state on the output of the respective NAND tree. The AMD-762 system controller provides multiple NAND trees, which speeds up characterization of the device, and also reduces motherboard test time. The AMD-762 system controller NAND trees are divided by I/O type, which create the following trees:

AMD Athlon system bus NAND tree

This tree includes all signals on the AMD Athlon processor system bus. SYSCLK is not included in the NAND tree. The output of this tree is the GNT[0]# pin. The ordering for this NAND tree is shown in Table 2 on page 38.

#### AGP/APC NAND tree

This tree includes AGPCLK, AGP, and the PCI-type signals that are included in the AGP interface. The output of this tree is the GNT[1]# pin. The ordering for this NAND tree is shown in Table 3 on page 41.

#### ■ DDR DRAM NAND tree

This tree includes all signals in the DDR interface. The output of this tree is the GNT[3]# pin. The ordering for this NAND tree is shown in Table 4 on page 42.

#### PCI NAND tree

This tree includes PCICLK and PCI bus signals, excluding the RESET# input. The output of this tree is the GNT[2]# pin. The ordering for this NAND tree is shown in Table 5 on page 44.

24416C - December 2001

Table 2. AMD Athlon™ Processor System Bus NAND Tree Ordering

| #  | Input Pin<br>Name  | Ball | #  | Input Pin<br>Name  | Ball | #  | Input Pin<br>Name  | Ball |

|----|--------------------|------|----|--------------------|------|----|--------------------|------|

| 1  | P0_SADDOUT[14]#    | D-1  | 32 | P0_SDATA[59]#      | L-1  | 63 | P0_SDATA[19]#      | R-5  |

| 2  | PO_SYSFILLVAL#     | J-8  | 33 | P0_SDATA[56]#      | M-2  | 64 | PO_SDATAINCLK[1]#  | R-1  |

| 3  | P0_SADDOUT[10]#    | F-5  | 34 | P0_SCHECK[7]#      | K-3  | 65 | PO_SCHECK[3]#      | T-1  |

| 4  | P0_SADDOUT[13]#    | E-2  | 35 | P0_SDATA[57]#      | L-4  | 66 | P0_SDATA[21]#      | R-4  |