## AMIS-53000 Frequency Agile Transceiver Data Sheet

www.DataSheet4U.com

# **AMIS-53000** Frequency Agile Transceiver

#### **Table of Contents**

| 1.1 Applications for the AMIS-53000                                                                                                                                                                                                                                          |                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| • •                                                                                                                                                                                                                                                                          |                |

| 1.2 Key Features                                                                                                                                                                                                                                                             | 5              |

| 1.3 Technical Features                                                                                                                                                                                                                                                       |                |

| 1.4 Circuit Overview                                                                                                                                                                                                                                                         |                |

| 1.4.1. Transmitter<br>1.4.2. Receiver                                                                                                                                                                                                                                        | 6              |

| 2.0 Operational Specifications                                                                                                                                                                                                                                               |                |

| 2.0 Operational Specifications                                                                                                                                                                                                                                               | 8              |

| 2.1 Absolute Maximum Ratings                                                                                                                                                                                                                                                 |                |

| 2.2 Recommended Operating Conditions                                                                                                                                                                                                                                         |                |

| 2.3 Operational Specifications                                                                                                                                                                                                                                               |                |

|                                                                                                                                                                                                                                                                              |                |

| 3.0 Block Diagrams                                                                                                                                                                                                                                                           | 12             |

| 3.1 AMIS-53000 Overall Block Diagram                                                                                                                                                                                                                                         |                |

| 3.2 Package                                                                                                                                                                                                                                                                  |                |

| 3.2.1. Pin Definition                                                                                                                                                                                                                                                        | 12             |

| 3.2.2. Block Diagram/Pin Definition                                                                                                                                                                                                                                          |                |

| 4.0. A a va no vivra                                                                                                                                                                                                                                                         | 4.5            |

| 4.0 Acronyms                                                                                                                                                                                                                                                                 | 13             |

|                                                                                                                                                                                                                                                                              |                |

| 5.0 Hardware Description                                                                                                                                                                                                                                                     | 16             |

| ·                                                                                                                                                                                                                                                                            |                |

| 5.1 Frequency                                                                                                                                                                                                                                                                | 16             |

| 5.1 Frequency                                                                                                                                                                                                                                                                |                |

| 5.1 Frequency                                                                                                                                                                                                                                                                |                |

| 5.1 Frequency  Www.DataSheet4U.com 5.2 Receiver.  5.2.1. Receiver Low Noise Amplifier (LNA)  5.2.2. IF Filter  5.2.3. Data Filter.                                                                                                                                           |                |

| 5.1 Frequency                                                                                                                                                                                                                                                                |                |

| 5.1 Frequency  WW DataSheet4U.com 5.2 Receiver.  5.2.1. Receiver Low Noise Amplifier (LNA)  5.2.2. IF Filter  5.2.3. Data Filter  5.3 Transmitter.  5.4 Single Antenna Option  5.5 Peak.                                                                                     |                |

| 5.1 Frequency                                                                                                                                                                                                                                                                |                |

| 5.1 Frequency  Data Sheet 4U. com 5.2 Receiver.  5.2.1. Receiver Low Noise Amplifier (LNA)  5.2.2. IF Filter  5.2.3. Data Filter.  5.4 Single Antenna Option.  5.5 Peak.  5.6 ADC.  5.7 Control Interface Serial Bus  5.8 TX/RX Data Interface Serial Bus  5.9 System Clock. | 20 21 23 25    |

| 5.1 Frequency                                                                                                                                                                                                                                                                | 20 21 22 25 25 |

| 5.1 Frequency                                                                                                                                                                                                                                                                |                |

| 5.1 Frequency                                                                                                                                                                                                                                                                |                |

| 5.1 Frequency                                                                                                                                                                                                                                                                |                |

| 6.1.2. Serial Control Interface: Configuration | 31<br>37 |

|------------------------------------------------|----------|

| 6.1.4. I <sup>2</sup> C Interface              |          |

| 6.2 Command Register                           |          |

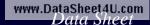

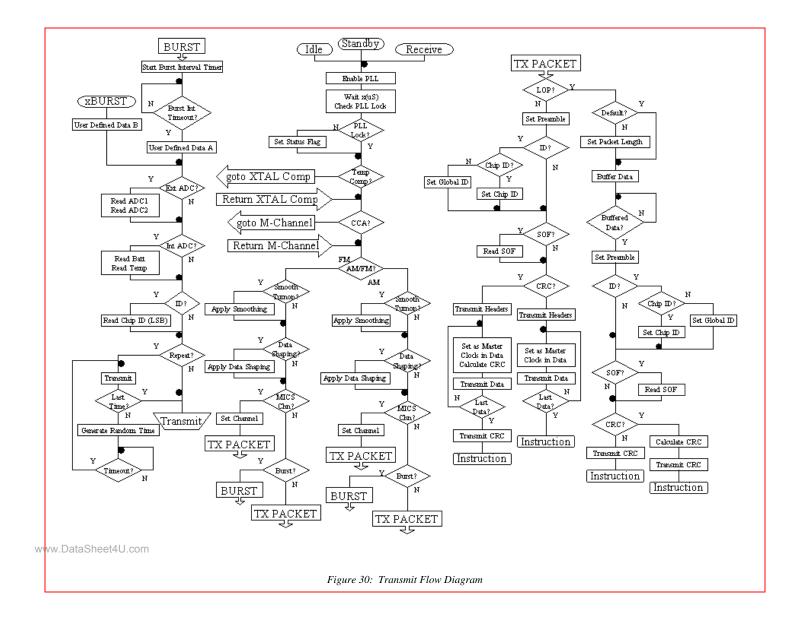

| 6.3 Functional Flow Diagrams                   |          |

| <u> </u>                                       |          |

| 6.4 Frequency Control                          |          |

| 6.4.2. 10kHz Oscillator                        |          |

| 6.4.3. System Clock                            |          |

| 6.4.4. Quick Start                             |          |

| 6.4.5. Self Calibration.                       |          |

| 6.5 Receiver                                   |          |

| 6.5.1. Receiver Circuit Brief Overview         | 48       |

| 6.6 Transmitter                                |          |

| 6.6.1. TX Config                               |          |

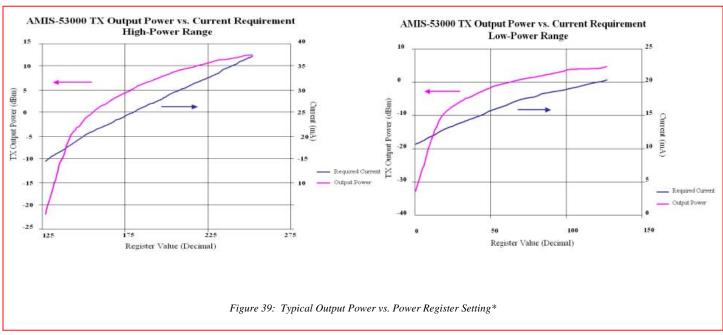

| 6.6.2. Output Power                            | 59       |

| 6.6.3. Preamble Length                         |          |

| 6.6.4. FM Transmit Data Shaping                |          |

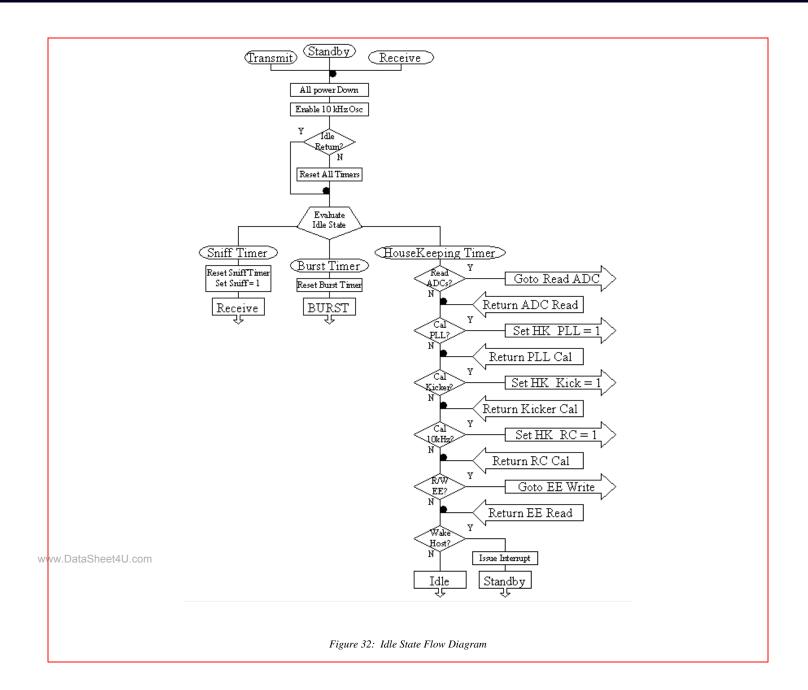

| 6.7 Idle                                       |          |

| 6.7.1. Idle Config                             |          |

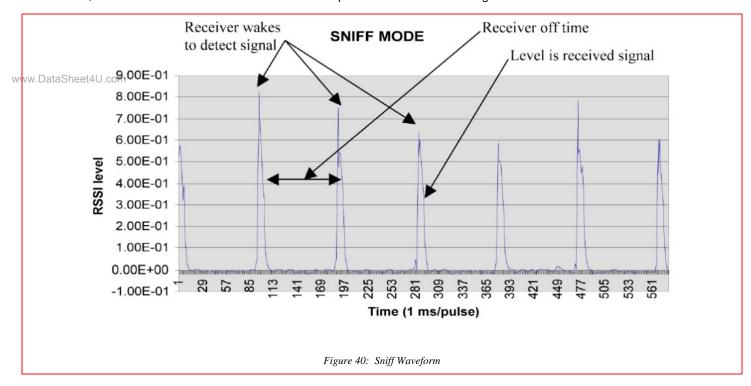

| 6.7.2. Sniff Mode Operation                    |          |

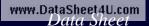

| 6.7.3. Burst Transmit Data                     |          |

| 6.8 Idle Return                                |          |

|                                                |          |

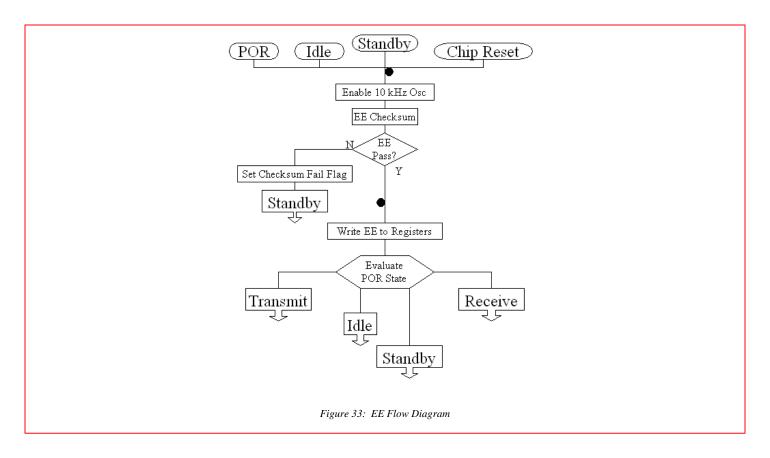

| 6.9 <i>EE</i>                                  |          |

| 6.9.1. Write EE                                |          |

| 6.9.2. Load EE                                 |          |

| 6.10 Calibrate                                 |          |

| 6.10.1. Internal Trim                          |          |

| 6.10.2. Calibrate Quick Start Oscillator       |          |

| 6.10.4. Calibrate PLL                          |          |

| 6.10.5. Calibrate LNA                          | 7        |

| 6.11 ROM 2 REGS                                | 7        |

| w.DataSheet4U.com<br>6.12 Chip Reset           |          |

| 0.12 Only Nesset                               |          |

| 6.13 ADC Conversion                            |          |

| 6.13.2. Single ADC Conversion                  |          |

| 6.13.3. Continuous ADC Conversion              |          |

| 7.0 Dete luterfees                             |          |

| 7.0 Data Interface                             | /;       |

| 7.1.1. Chip Address MSB1                       |          |

| 7.1.2. Chip Address LSB                        |          |

| 7.1.3. Data Rate/Format                        |          |

| 7.1.4. General Options A                       |          |

| 7.1.5. General Options B                       |          |

| 7.1.7. Data Rate 1                             |          |

| 7.1.7. Data Nate 1                             |          |

| 7.1.9. CRC Polynomial                          |          |

| 7.1.10. Default Length of Packet               |          |

| 7.1.11. Broadcast ID 1                         |          |

| 7.1.12. Broadcast ID 0                         | 8        |

| 7.2 TX/RX Data Interface Protocol              | 8        |

| 7.2.1. AMIS-53000 in Master Mode               |          |

| 7.2.2. AMIS-53000 in Slave Mode                | 84       |

# **AMIS-53000** Frequency Agile Transceiver

| 7.2.3. Manchester Operation                             |    |

|---------------------------------------------------------|----|

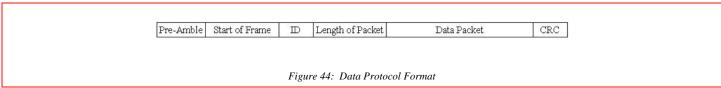

| 7.2.4. Packet Framing                                   | 84 |

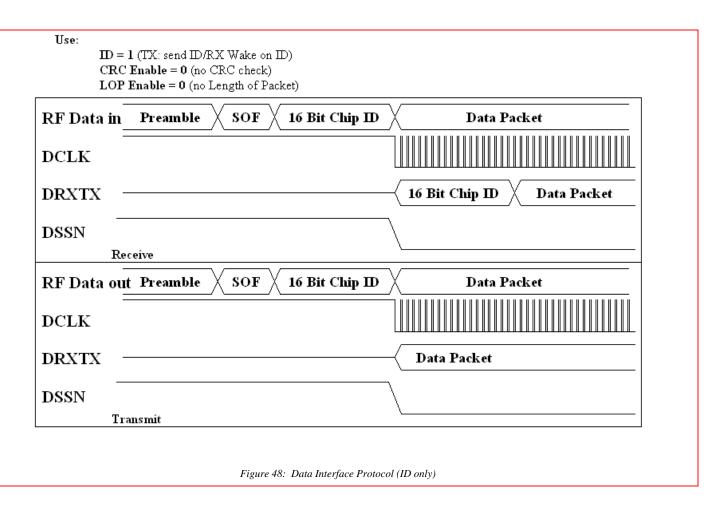

| 7.2.5. Use ID                                           |    |

| 7.2.6. Length of Packet Enable                          |    |

| 7.2.7. CRC Enable                                       |    |

| 7.2.8. SOF Byte                                         |    |

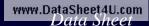

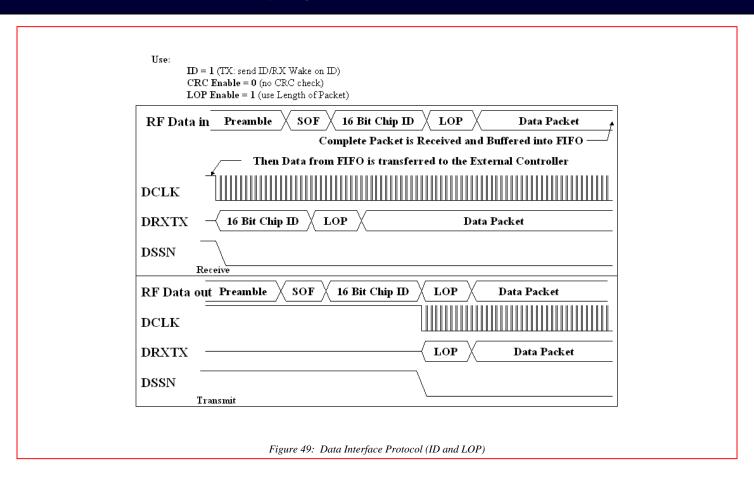

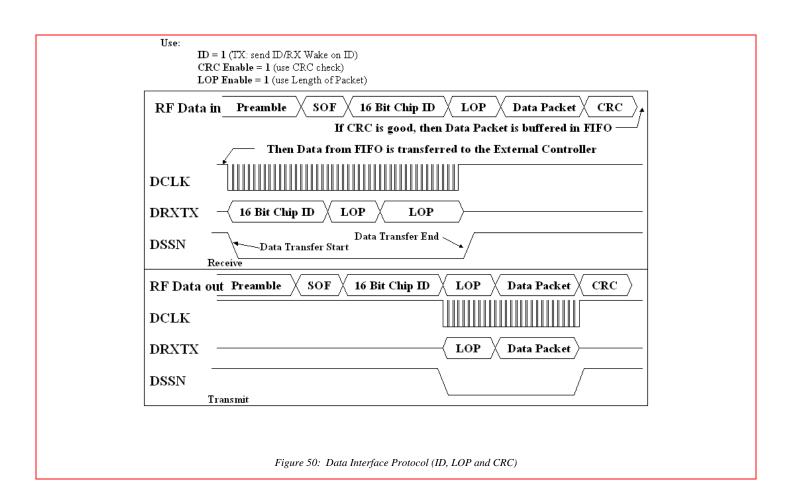

| 7.2.9. Timing Diagrams for Various Packet Framing Modes | 86 |

| 8.0 General System Functions                            | 90 |

| 8.1 Pull up Disable                                     | 90 |

| 8.2 Brown-Out POR                                       | 90 |

| 8.3 Temperature Sensor                                  | 90 |

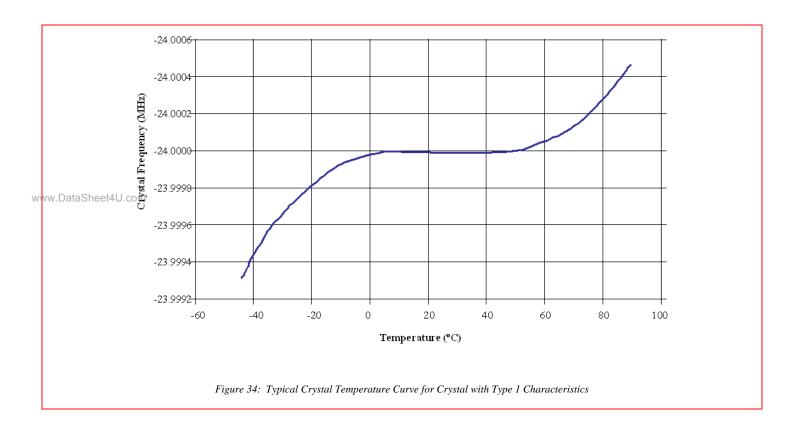

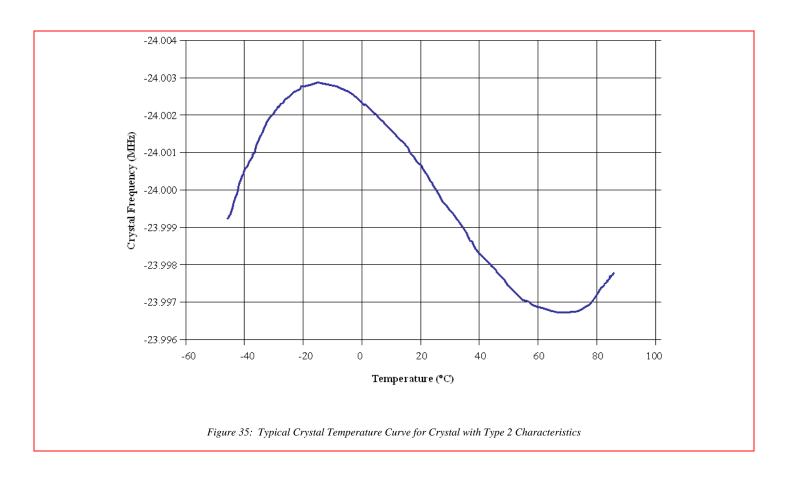

| 8.3.1. Crystal Temperature Compensation                 | 91 |

| 8.4 Software                                            |    |

| 8.4.1. AMIS Part Revision Code                          | 91 |

| 9.0 Built-in Test Functions                             | 92 |

| 9.1 TM Unlock Register                                  | 92 |

| 9.2 Test Registers                                      | 92 |

| 9.2.1. IF Amp Manual Trim A                             |    |

| 9.2.2. IF Amp Manual Trim B                             |    |

| 9.2.3. PLL Manual Trim                                  | 92 |

| 9.2.4. PLL Test Modes                                   | 93 |

| 9.2.5. Power Down RF Sections                           |    |

| 9.2.6. Analog Test Mode                                 |    |

| 9.2.7. RF Test Modes                                    |    |

| 9.2.8. Analog Test MUX                                  |    |

| 9.2.9. RF Test MUX                                      |    |

| 9.2.10. Digital Test MUX A                              |    |

| 9.2.11. Digital Test MUX B                              |    |

| 9.2.12. Digital Test MUX C                              |    |

| 9.2.13. Digital Test Mode A                             |    |

| 9.2.14. Digital Test Mode B                             |    |

| 9.2.15. Digital Test Mode C                             | 93 |

| 9.2.16. Digital Test Mode D                             | 95 |

| ww. D9.247e Memory Test Mode Address                    |    |

| 40.0 D. C. W.                                           | •  |

| 10.0 Register Definition                                | 96 |

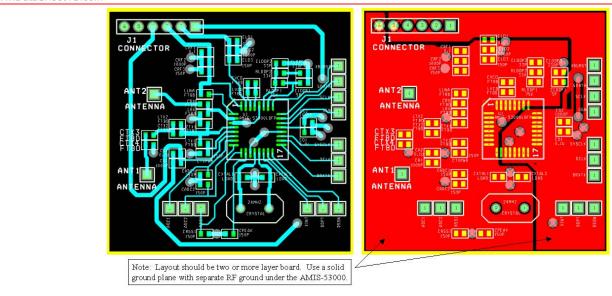

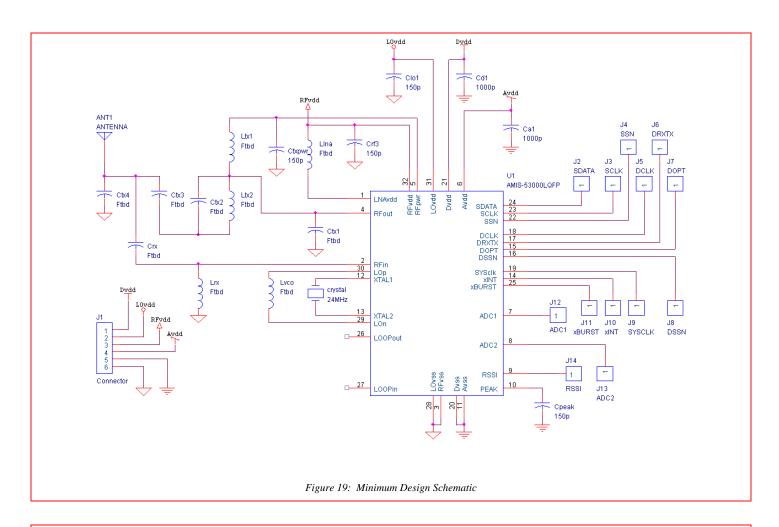

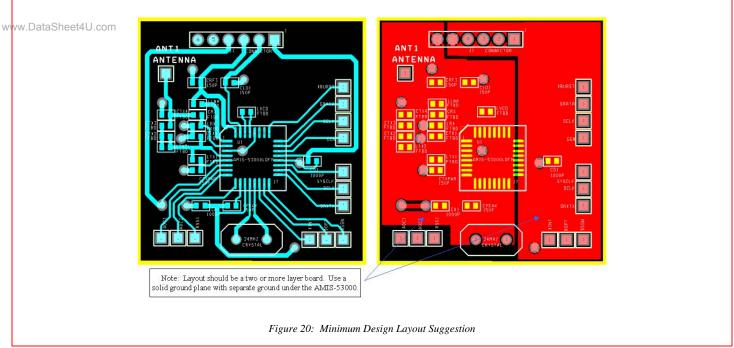

| 11.0 Applications                                       | 98 |

| 12.0 Ordering Information                               | 99 |

| 13.0 Company or Product Inquiries                       | QQ |

#### 1.0 Overview of the AMIS-53000

The AMIS-53000 is the latest highly flexible member of AMI Semiconductor's ASTRIC™ family of single-chip wireless transceivers. It is ideally suited for low to moderate data rate, low power, sub 1GHz, narrow band, FSK/GFSK/OOK, multiple channel, wireless applications in the medical, automotive and industrial markets. The AMIS-53000 can easily be interfaced to a base band processor via a serial interface bus.

#### 1.1 Applications for the AMIS-53000

- Medical Implantable Communication Systems (MICS)

- Wireless Medical Telemetry Systems

- Wireless Sensors

- RFID

- Remote Monitoring

- Access Control and Security

- Keyless Entry

- Mobile Wireless Data Terminals

- Keyless Entry

- Tire Pressure Monitors

- Wireless Toys

#### 1.2 Key Features

- Medical implant communication protocol support

- Very low power single-chip CMOS transceiver

- Patented Quick Start crystal oscillator

- Low power receive Sniff Mode™

- · Periodic transmit using Burst mode

- Internal low power 10kHz oscillator

- Internal self calibration functions

- www.DataSheel40C interface bus

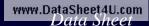

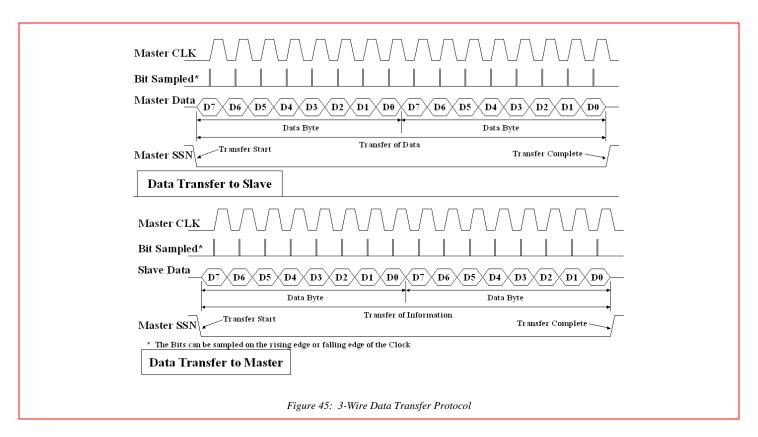

- 3-wire/4-wire serial data interface

- Two analog to digital converter channels

- Internal fractional N frequency synthesizer

- On/off shift key/frequency shift key modulation/Gaussian FSK (BT = 1)

- Internal temperature sensor

- · Minimal external components

#### 1.3 Technical Features

- Operating voltage range: 2.2 to 3.3V

- Operating temperature range: -40° to +85°C

- Operating frequency range: 300 to 928MHz

- Data rate:

- 1 to 19.2kbps (OOK)

- 2 to 128kbps (FSK/GFSK)

- Transmit output power:

- +15dBm max (high power)

- +0dBm max (low power)

- Transmit current: 50mA typical (15dBm)

## AMIS-53000 Frequency Agile Transceiver

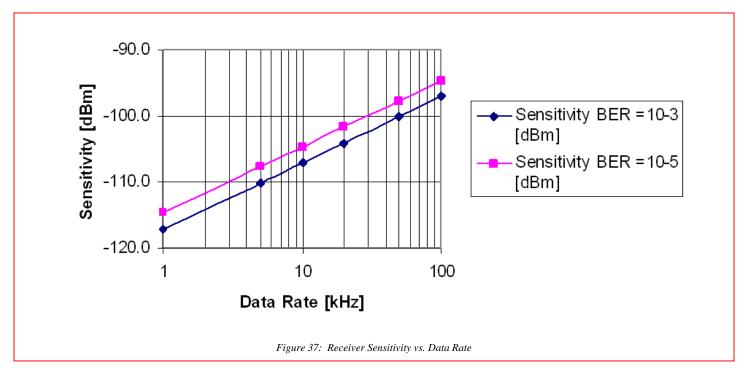

- Receiver sensitivity

- o -115dBm (OOK @ 1kbps)

- o -105dBm (FSK @ 20kbps)

- Receiver current: 12mA (continuous)

- Minimum RX energy detect time: 130uS (Sniff)

#### 1.4 Circuit Overview

#### 1.4.1. Transmitter

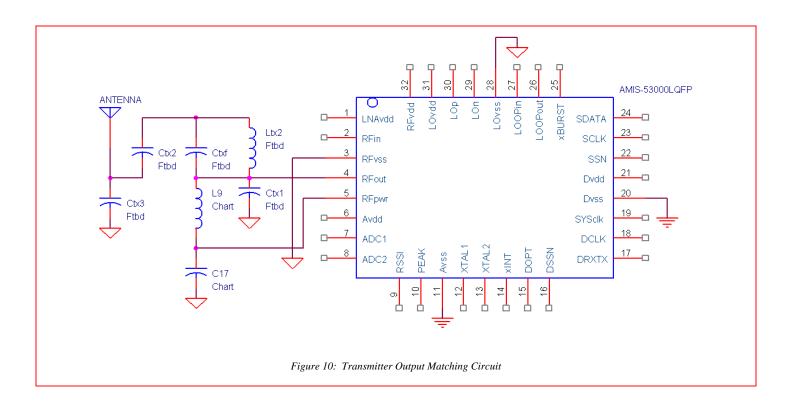

The AMIS-53000 uses a driver and class E power amplifier to output the on/off shift keyed or frequency shift keyed RF waveforms. The class E power amplifier has two output power ranges allowing more efficient output power for the one setting up to 0dBm output and the other setting for output power greater than 0dBm. The class E power amplifier can achieve output power of +12dBm to +15dBm for frequencies in the range of 300MHz to 915MHz. The output power is programmable in each of the two output power bands.

The transmit data can be NRZ or Manchester encoded. Data can also be modulated as on/off shift keyed or frequency shift keyed. Data rates for the OOK modulation can be as high as 19.2kbps. Data rates for the FSK/GFSK modulation can be as high as 128kbps. The carry frequency deviation for the FSK modulation is programmable, typically one half to one times the data rate.

The transmit data output can be wave shaped with a Gaussian format. This can reduce the occupied bandwidth of the signal.

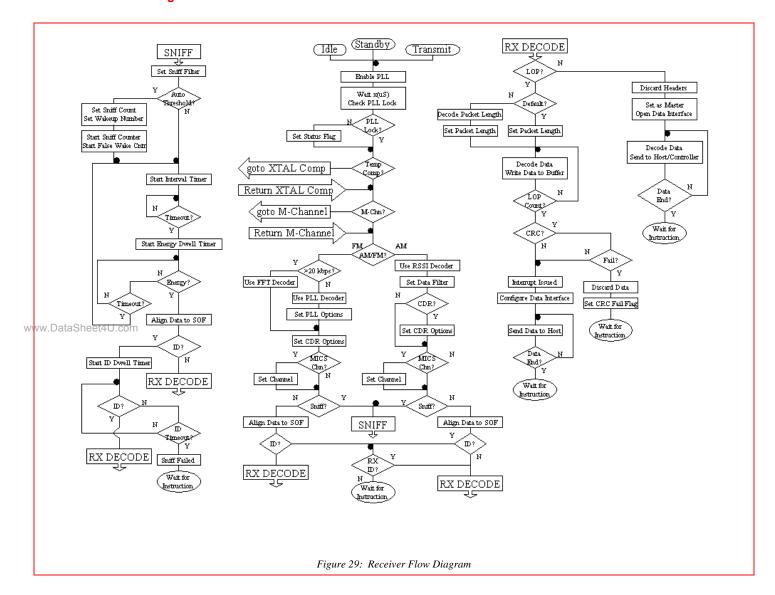

#### 1.4.2. Receiver

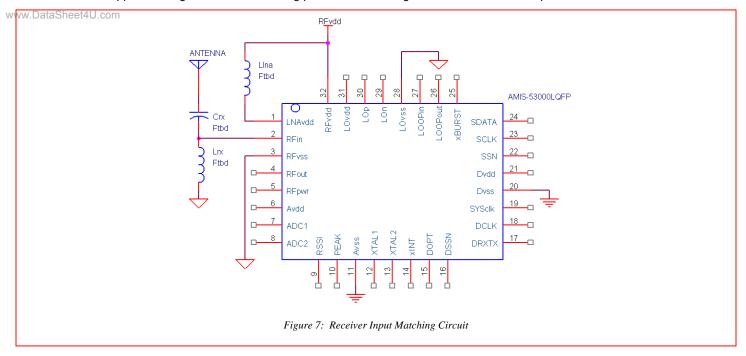

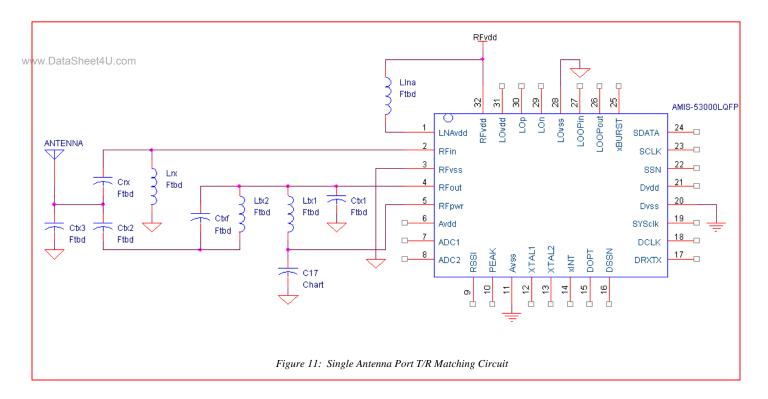

The AMIS-53000 has a single receiver channel and a single transmit channel, which can be connected to individual antennas or can be combined into a single antenna. The receiver uses four different methods to receive and recover data that has been on/off shift keyed or frequency shift keyed modulated. The FSK/GFSK data is recovered using either a PLL circuit or a FFT circuit along with a CDR circuit. The OOK data is recovered using an RSSI circuit along an optional CDR circuit. It is suggested that the CDR circuit be used when receiving OOK signals.

#### 1.4.2.1. On/Off Shift Key Modulation

The AMIS-53000 uses a logarithmic received signal strength indicator (RSSI) detector to recover the data from the on/off shift keyed modulated waveform. Data rates can be up to 19.2kbps. The AMIS-53000 has eight discrete data filters for common baud rates. The receiver can detect either NRZ or Manchester encoded data.

www.DataSheet4U.com

#### 1.4.2.2. Low Data Rate Frequency Shift Key Modulation

The AMIS-53000 uses a digital PLL detector to recover the data from the frequency shift keyed data below 20kbps. The recovered data waveform is applied to the clock and data recovery circuit to produce the digital data and a synchronized clock. The receiver can detect either NRZ or Manchester encoded data.

#### 1.4.2.3. High Data Rate Frequency Shift Key Modulation

The AMIS-53000 uses a fast fourier transform (FFT) to recover data from frequency shift keyed modulated waveforms when the data rate is higher than 20kbps. The data rate can be as high as 128kbps. The demodulated data waveform is applied to the clock and data recovery circuit to produce the digital data and a synchronized clock. The receiver can detect either NRZ or Manchester encoded data.

#### 1.4.2.4. Clock and Data Recovery

The AMIS-53000 uses a clock and data recovery circuit along with the frequency shift keyed or on/off shift keyed data detector circuits to recover the data stream. The CDR circuit synchronizes a clock with the data rate of the received data. This same circuit can be used with the on/off shift keyed waveform.

# AMIS-53000 Frequency Agile Transceiver

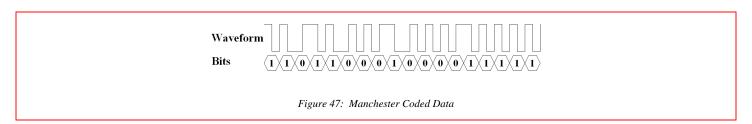

#### 1.4.2.5. Manchester Data Encoding

The AMIS-53000 can encode the data as NRZ or Manchester.

#### 1.4.2.6. Oscillators

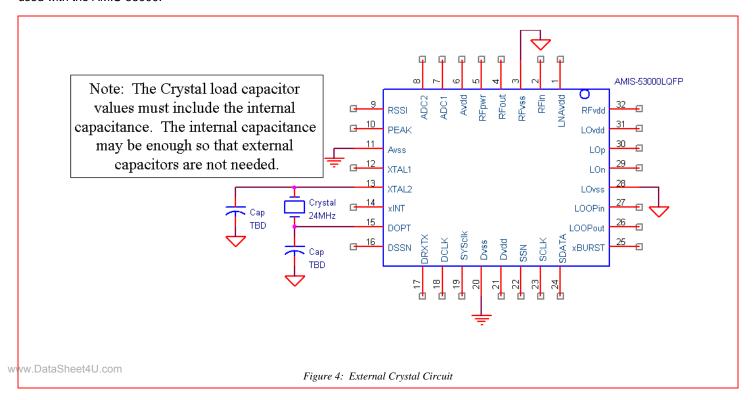

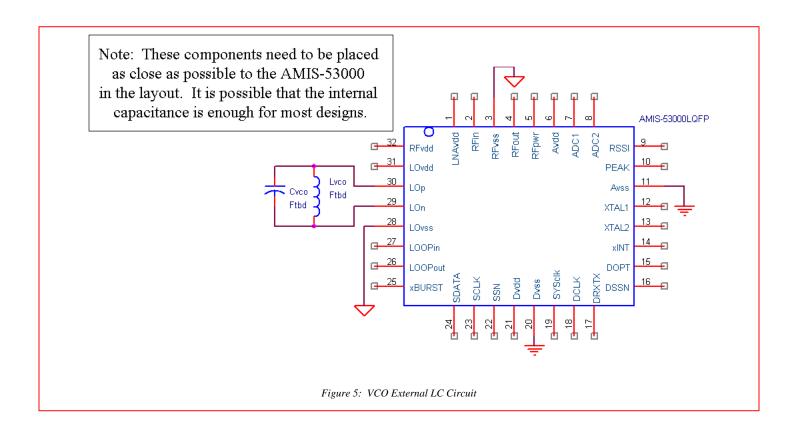

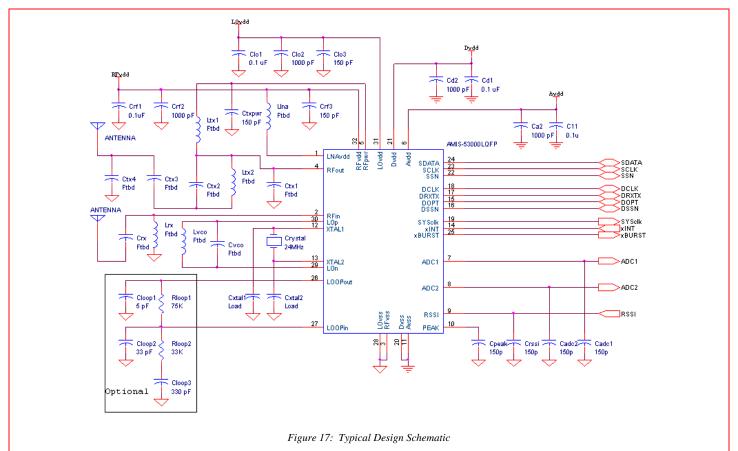

The AMIS-53000 requires a single external crystal working with the internal VCO and PLL to generate frequencies from 300MHz to 928MHz. The AMIS-53000 has internal capacitors that eliminate the need for external load capacitors when using a typical 24MHz external crystal. The VCO requires an external inductor and capacitor (including internal capacitance) to produce the desired transmit or receive RF frequency. The AMIS-53000 generates the desired RF transmit and receive frequencies from 300MHz to 928MHz by selecting the proper inductor and capacitor value along with programming the frequency in the AMIS-53000. A patented Quick Start circuit is used to force the crystal oscillator on to the desired frequency in microseconds rather than in milliseconds.

A low power internal 10kHz oscillator provides the timing for Sniff, Burst and housekeeping. The AMIS-53000 self-calibration circuits can tune this oscillator to within two percent of 10kHz.

#### 1.4.2.7. Interface Serial Bus

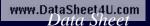

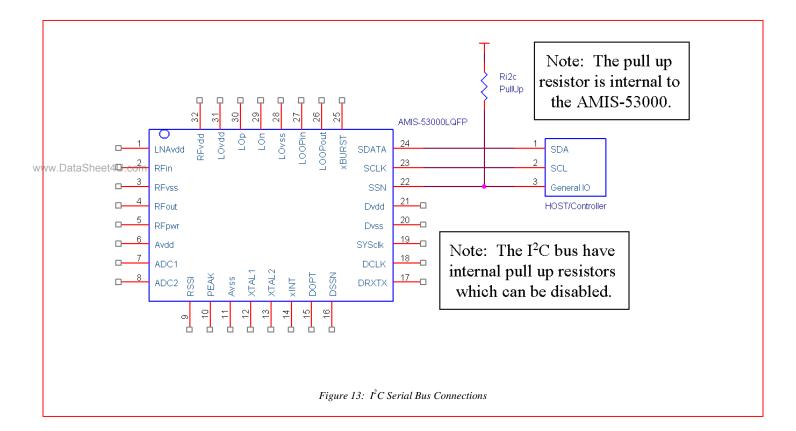

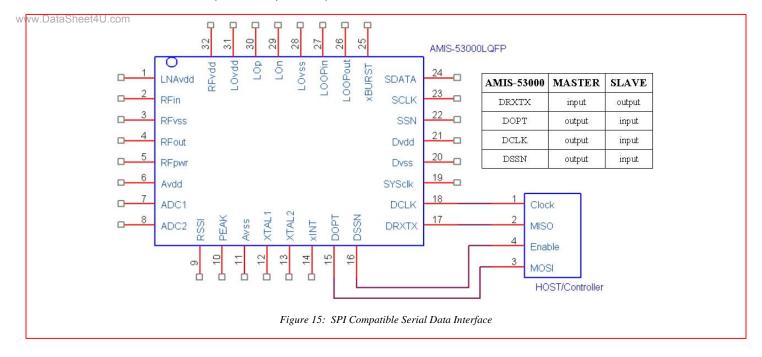

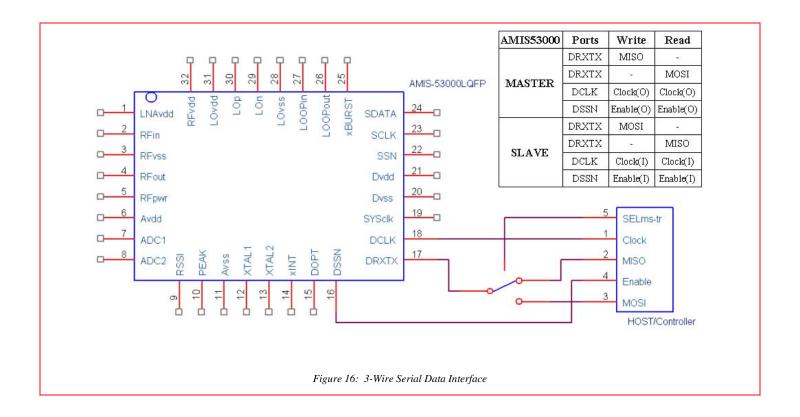

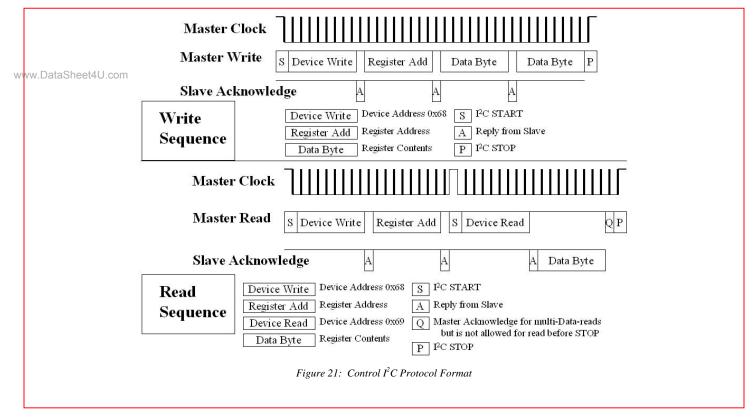

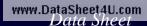

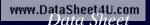

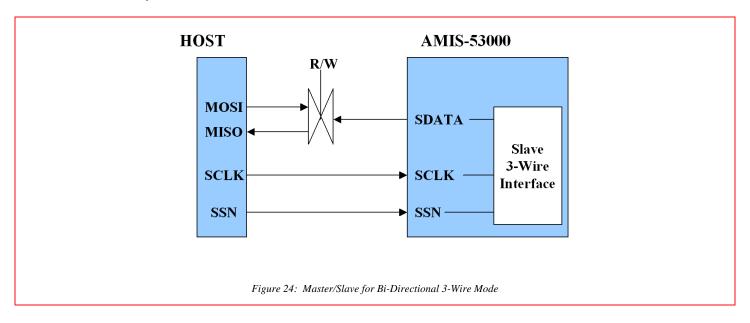

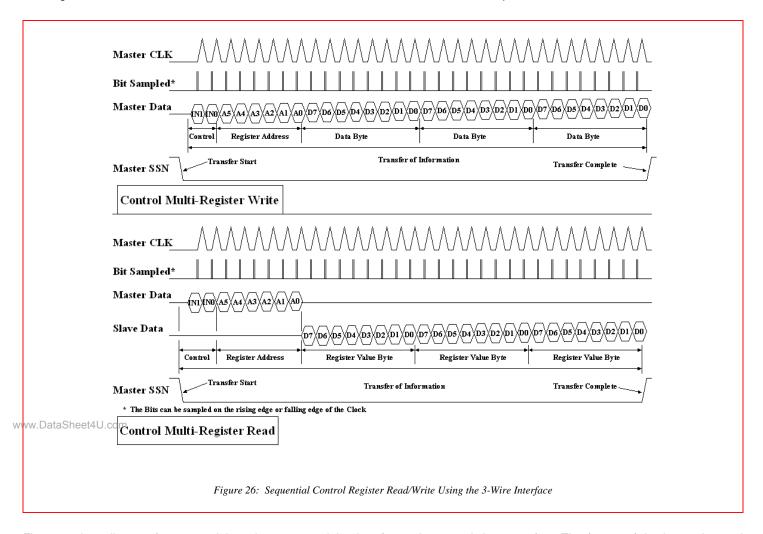

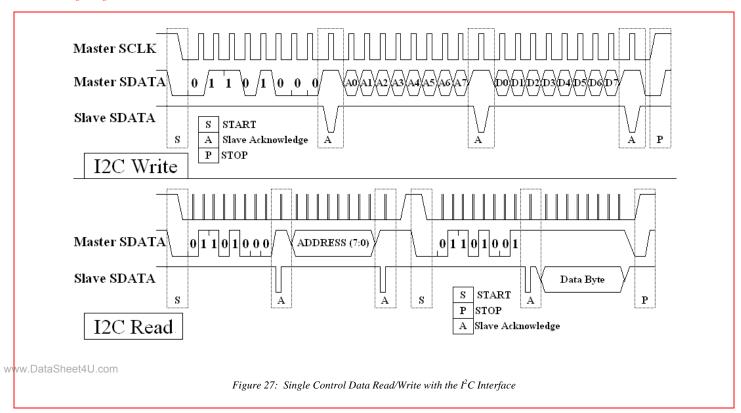

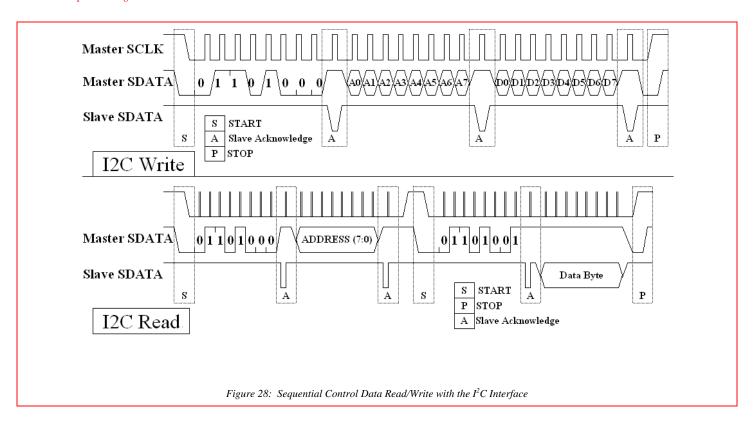

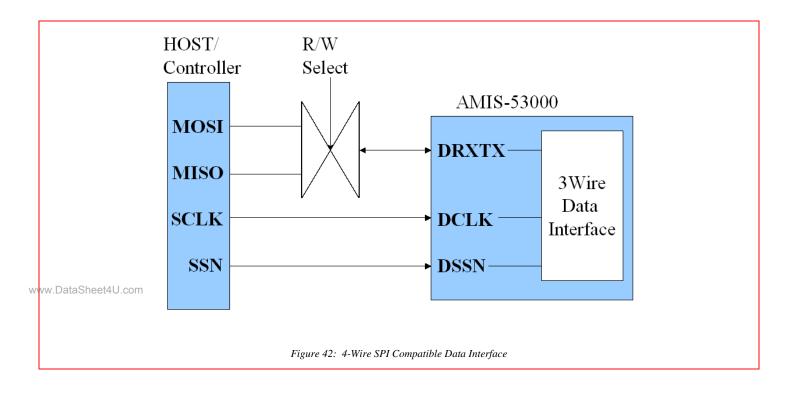

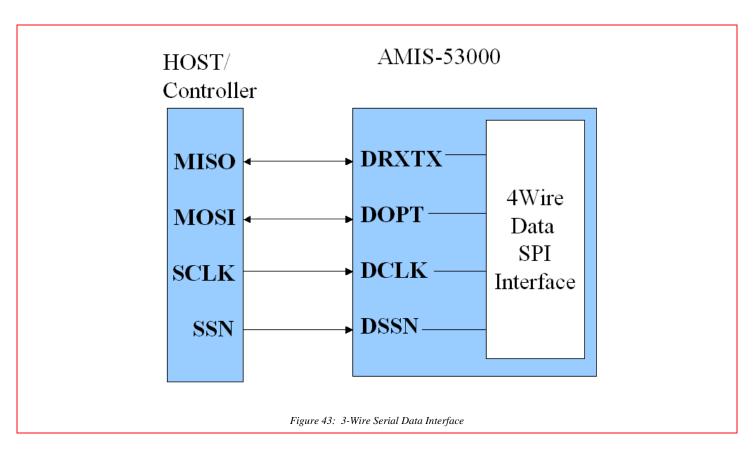

The AMIS-53000 has separate interfaces for data and control. The transfer of TX/RX data between the AMIS-53000 and an external host/controller is done with a 3-wire serial interface or a 4-wire SPI compatible serial interface. Control information is written to the AMIS-53000 registers or read from the AMIS-53000 registers using either a 3-wire serial interface or a 2-wire I<sup>2</sup>C compatible serial interface.

Once the AMIS-53000 configuration registers have data written to them for various operational modes such as, TX, RX, Sniff or other, placing the AMIS-53000 into one of these modes is accomplished through a single write to the command register.

#### TX/RX Data Interface

The transmit or receive data interface of the AMIS-53000 can be programmed to be either a proprietary 3-wire serial interface or a 4-wire SPI compatible serial bus. The data interface can be set up to do either data transfers into a buffer in the AMIS-53000 or streaming data (data is transmitted as it is received by the AMIS-53000 or data is sent to the host/controller as it is recovered in the AMIS-53000 receiver). When using the buffered data mode, the AMIS-53000 can be the master or slave, but it must be the master to do streaming data.

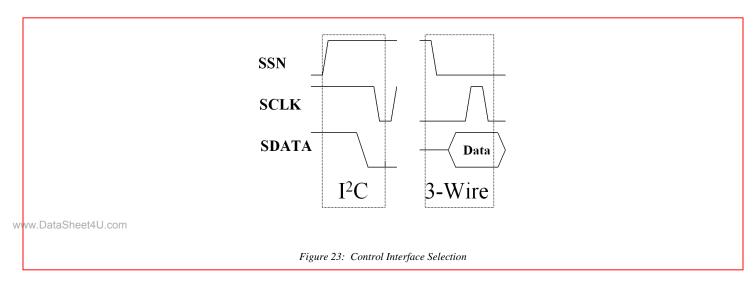

#### **Control Interface**

Once the AMIS-53000 is first powered on, an external host/controller sets the type of interface to the AMIS-53000 (3-wire or I<sup>2</sup>C) by wisimply writing to the AMIS-53000 with the desire protocol. The AMIS-53000 will continue to use that interface protocol until power is removed from the AMIS-53000. The AMIS-53000 is always a slave device for the control interface.

### 2.0 Operational Specifications

#### 2.1 Absolute Maximum Ratings

Table 1: Absolute Maximum Ratings

| Symbol             | Parameter            | Min.  | Max.    | Units | Notes  |

|--------------------|----------------------|-------|---------|-------|--------|

| Vdd                | DC Supply Voltage    | -0.3  | 3.6     | V     |        |

| Vin                | Input Pin Voltage    | -0.3  | Vdd+0.3 | V     |        |

| lin                | Input Pin Current    | -10.0 | 10.0    | mA    | 25C    |

| Tstrg              | Storage Temperature  | -55   | 150     | С     | SSOP   |

| Tlead              | Lead Temperature     |       | 300     | С     | 10 SEC |

| ESD <sub>HBM</sub> | Human Body Model     |       | 2       | kV    |        |

| ESD <sub>CDM</sub> | Charged-Device Model |       | 750     | V     |        |

| ESD <sub>MM</sub>  | Machine Model        |       | 200     | V     |        |

#### 2.2 Recommended Operating Conditions

Table 2: Operating Conditions

| Symbol | Parameter                     | Min. | Max. | Units | Notes             |

|--------|-------------------------------|------|------|-------|-------------------|

| Vdd    | DC Supply                     | 2.2  | 3.3  | V     |                   |

| ldd    | Dynamic Current               |      | 70   | mA    | (1) Continuous TX |

| Idds   | Standby Current (off current) |      | 2    | uA    | (2)               |

| Vss    | Ground                        | 0.0  | 0.0  | V     |                   |

| Та     | Ambient Temperature           | -40  | 85   | С     |                   |

- 1. Dynamic current is with the transmitter enabled at maximum output power + 15dBm in FSK mode at 928MHz.

- 2. Standby current is with all analog cells in power down. Other logic powered up with no clocks running. All outputs unloaded and inputs tied high or low. No floating inputs.

www.DataSheet4U.com

#### 2.2.1. Parametric Voltage and Current Levels

(Testing for the below currents assumes a static test setup with measurements performed while static data is applied to the device.)

#### 2.2.1.1. Inputs

Table 3: Pin Input Parameters

| Pin  | Vil         |             | Vih         |             |            | lil lih<br>(1) (1) |            |            | Notes<br>(2)              |

|------|-------------|-------------|-------------|-------------|------------|--------------------|------------|------------|---------------------------|

|      | Min.<br>(V) | Max.<br>(V) | Min.<br>(V) | Max.<br>(V) | Min.<br>uA | Max.<br>uA         | Min.<br>uA | Max.<br>uA |                           |

| Al   |             |             |             |             | 0.0        | 1.0                | -1.0       | 0.0        | Analog input              |

| DISU | 0.0         | 0.3         | 0.8         | 1.0         | 0.0        | 1.0                | -30        | -90        | CMOS with pull up Schmitt |

| DISC | 0.0         | 0.3         | 0.8         | 1.0         | 0.0        | 1.0                | -1.0       | 0.0        | CMOS Schmitt              |

- 1. lil and lih are tested at Vdd = VDDmax volts. Not tested at less than room temperature.

- Ill and in are tested at void = VDDmax voits. Not tested at less trial room temperature.

PU = Pull up, PD = Pull down, SC = Schmitt, SU = Schmitt & Pull up and SD = Schmitt and Pull down.

CMOS values are 'Vin \* VDD' and TTL values are absolute voltages.

#### 2.2.1.2. Outputs

Table 4: Pin Output Parameters

| Pin |             | ol<br>1)    | Voh<br>(2)  |             | lol<br>(1,3) |            |            | oh<br>,3)  | Notes          |

|-----|-------------|-------------|-------------|-------------|--------------|------------|------------|------------|----------------|

|     | Min.<br>(V) | Max.<br>(V) | Min.<br>(V) | Max.<br>(V) | Min.<br>mA   | Max.<br>mA | Min.<br>mA | Max.<br>mA |                |

| AO  |             |             |             |             |              |            |            |            | Analog outputs |

| DO  | 0           | 0.4         | Vdd4        |             | 2            |            | -2         |            | CMOS           |

- 1. Vol, lol are tested at Vdd = VDDmin volts unless otherwise stated.

- 2. Voh, loh are tested at Vdd = VDDmin volts unless otherwise stated.

- 3. Polarity on currents indicates direction of current: (+) for sinking and (-) for sourcing.

#### 2.2.1.3. I/O Pins

Table 5: I/O Pin Parameters

| Pin | Vil<br>V<br>Min. | Vil<br>V<br>Max. | Vih<br>V<br>Min. | Vih<br>V<br>Max. | Vol<br>V<br>(1) | Vol<br>V<br>Max.<br>(1) | Voh<br>V<br>Min.<br>(2) | Voh<br>V<br>(2) | lol<br>mA<br>Min.<br>(1) | Ioh<br>mA<br>Min.<br>(2) | lozi<br>uA<br>Max.<br>(3) | lozh<br>uA<br>Max.<br>(3) | Notes   |

|-----|------------------|------------------|------------------|------------------|-----------------|-------------------------|-------------------------|-----------------|--------------------------|--------------------------|---------------------------|---------------------------|---------|

| AIO |                  |                  |                  |                  |                 |                         |                         |                 |                          |                          |                           |                           |         |

| DIO | 0                | 0.3              | 0.8              | 1                | 0               | 0.4                     | Vdd4                    | Vdd             | 2                        | -2                       | 1                         | -1                        | Schmitt |

- 1. Vol, lol are tested at Vdd = 3.1 volts.

- 2. Voh, loh are tested at Vdd = 3.1 volts.

- 3. loz is tested with Vdd = 3.5 volts.

\*\*\* Leakage on I/O pins is typically checked for +/- 10 microamps with the output device turned off and no PU or PD device present.

#### 2.3 Operational Specifications

Table 6: Operational Specifications

| Table C. Operational Operations |                                   |      |        |       |       |                                                                    |

|---------------------------------|-----------------------------------|------|--------|-------|-------|--------------------------------------------------------------------|

| Para                            | meter                             | Min. | Тур.   | Max.  | Units | Comment                                                            |

| Rece                            | eiver                             |      |        |       |       |                                                                    |

| Frequ                           | uency Range                       | 300  |        | 928   | MHz   |                                                                    |

| Sens                            |                                   | -107 |        | -114  | dBm   | @ 10kHz data rate (FSK/GFSK modulation)                            |

| OCITO                           | ittivity                          | -104 |        | -111  | dBm   | @ 10kHz data rate (OOK modulation)                                 |

| Noise                           | e Figure                          | 6.0  | 7.8    | 9.0   | dB    |                                                                    |

| IIP2                            |                                   |      | +60    |       | dBm   | Dual tone test using RSSI                                          |

| IIP3                            |                                   |      | +5     |       | dBm   | Dual tone test using RSSI                                          |

| Imag                            | e Rejection                       | 30   | 40     | 50    | dB    | Modulated desired, single tone interferer                          |

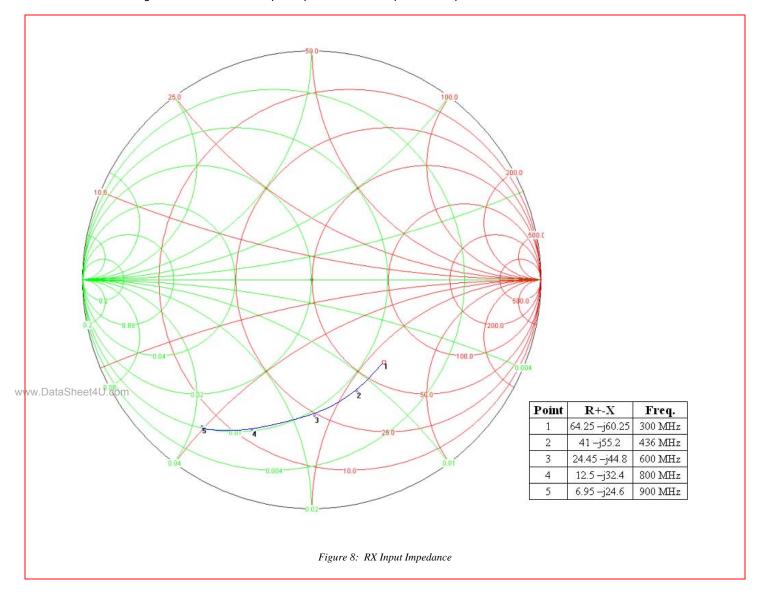

| Input Impedance                 |                                   |      | 15-j35 |       | Ω     | @ 900MHz series equivalent                                         |

| input                           | impedance                         |      | 72-j62 |       | Ω     | @ 433MHz series equivalent                                         |

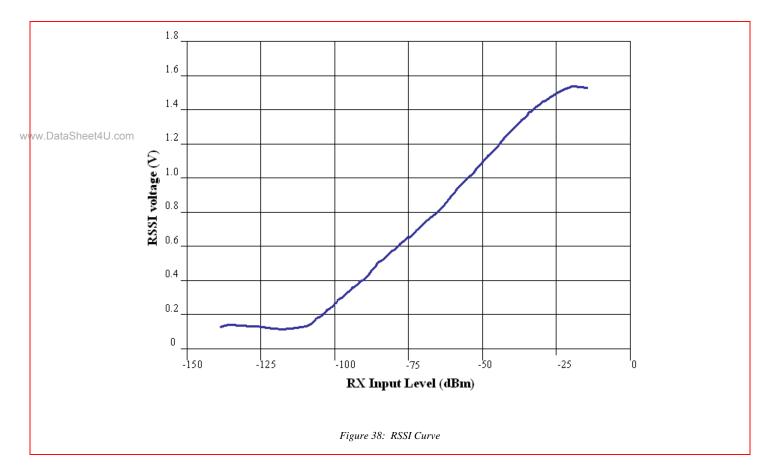

| RSSI                            | Gain                              | 14   | 16     | 18    | mV/dB |                                                                    |

| $I_{IN}$                        |                                   |      | 8      |       | mA    | Receiver current consumption at 900MHz                             |

| I <sub>SB</sub>                 | Full<br>Shutdown                  |      | 2      |       | uA    | Standby current (no clocks enabled)                                |

| -35                             | Crystal<br>Mode                   |      | 2      |       | mA    | System clock output enabled (6MHz)                                 |

| $T_{on}$                        |                                   |      | 100    |       | us    | Standby to receiver on time                                        |

| T <sub>RX_T</sub>               | <sub>X</sub> / T <sub>TX_RX</sub> |      | 100    |       | us    | Transition time from RX to TX or TX to RX                          |

| LAN                             |                                   |      |        |       |       |                                                                    |

| Input                           | Trim                              | 1.2  |        | 4     | pF    | Internal capacitor range for the receiver input                    |

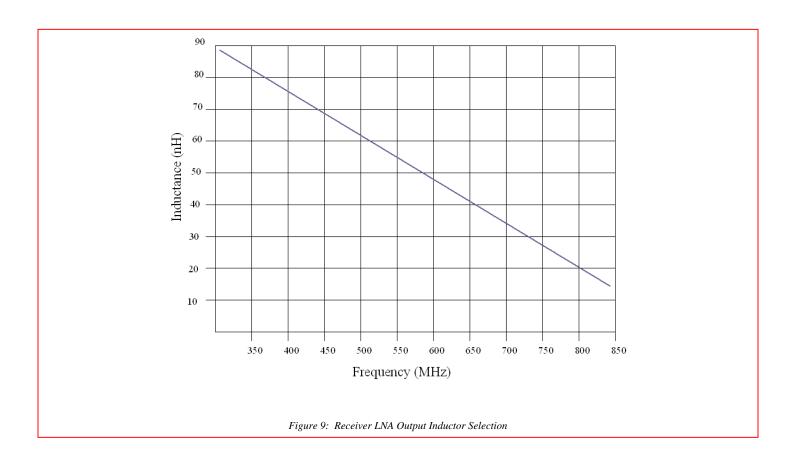

| Outp                            | ut Trim                           | 0.32 |        | 0.912 | pF    | Internal capacitor range for the output of the LNA in the receiver |

|                                 |                                   |      |        |       |       |                                                                    |

Table 6: Operational Specifications (Continued)

| Transmitter Frequency Range Ton TTX_RX OOK On/Off Ratio FSK Frequency Separation CW Output Power PHARMONICS TX PA Output Cap. Output Switch R On/Off Ratio Output Harmonics Operating Current High MAX Power Power Low Power High MAX Power Fower Low Power Crystal Oscillator Center Frequency Tolerance Startup Time Trim Cap Trim Resolution WMdd ataSheet4U.com Idd  10kHz Oscillator Output Frequency Operating Current  Duty Cycle                   | 0 -20 -25 5     | 100<br>100<br>60 | 928<br>200<br>15<br>0 | MHz us us dB kHz dBm dBm     | Standby to transmitter on time Transition time from TX to RX  Allowable transmit/receive peak deviation  Range of output power in the high power mode |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------|-----------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Frequency Range  Ton  TTX_RX  OOK On/Off Ratio  FSK Frequency Separation  CW Output Power  PHARMONICS  TX PA  Output Cap. Output Switch R  On/Off Ratio  Output Harmonics Operating Current  Operating Current  High MAX Power Power  Low Power  High MAX Power Power  Crystal Oscillator  Center Frequency Tolerance Startup Time Startup Time Trim Cap Trim Resolution  Widd ata Sheet 4 U.com Idd  10kHz Oscillator  Output Frequency Operating Current | 0<br>-20<br>-25 | 100              | 200                   | us<br>us<br>dB<br>kHz<br>dBm | Transition time from TX to RX  Allowable transmit/receive peak deviation                                                                              |

| Ton TTX_RX OOK On/Off Ratio FSK Frequency Separation CW Output Power  PHARMONICS TX PA Output Cap. Output Switch R On/Off Ratio Output Harmonics Operating Current Operating Current High Power Low Power High Power Low Power Crystal Oscillator Center Frequency Tolerance Startup Time Startup Time Trim Cap Trim Resolution Widd ata Sheet 4 U.com Idd  10kHz Oscillator Output Frequency Operating Current                                            | 0<br>-20<br>-25 | 100              | 200                   | us<br>us<br>dB<br>kHz<br>dBm | Transition time from TX to RX  Allowable transmit/receive peak deviation                                                                              |

| OOK On/Off Ratio FSK Frequency Separation  CW Output Power  PHARMONICS  TX PA  Output Cap. Output Switch R On/Off Ratio Output Harmonics Operating Current Operating Current  MAX Power Low Power High MAX Power Low Power Crystal Oscillator Center Frequency Tolerance Startup Time Trim Cap Trim Resolution  Widd ata Sheet 4 U.com Idd  10kHz Oscillator Output Frequency Operating Current                                                            | -20<br>-25      | 100              | 15                    | us<br>dB<br>kHz<br>dBm       | Transition time from TX to RX  Allowable transmit/receive peak deviation                                                                              |

| OOK On/Off Ratio FSK Frequency Separation  CW Output Power  PHARMONICS  TX PA  Output Cap. Output Switch R  On/Off Ratio Output Harmonics Operating Current Operating Current  High Power Low Power Low Power  Crystal Oscillator Center Frequency Tolerance Startup Time Startup Time Trim Cap Trim Resolution  Widd ata Sheet 4 U.com Idd  10kHz Oscillator Output Frequency Operating Current                                                           | -20<br>-25      | 60               | 15                    | dB<br>kHz<br>dBm             | Allowable transmit/receive peak deviation                                                                                                             |

| FSK Frequency Separation  CW Output Power  PHARMONICS  TX PA  Output Cap. Output Switch R  On/Off Ratio Output Harmonics Operating Current Operating Current  High MAX Power Low Power Low Power  Crystal Oscillator Center Frequency Tolerance Startup Time Startup Time Trim Cap Trim Resolution  Widd ata Sheet 4 U.com Idd  10kHz Oscillator Output Frequency Operating Current                                                                        | -20<br>-25      |                  | 15                    | kHz<br>dBm                   | ·                                                                                                                                                     |

| CW Output Power  Pharmonics  TX PA  Output Cap. Output Switch R  On/Off Ratio Output Harmonics Operating Current Operating Current  High Power Low Power Low Power  Crystal Oscillator Center Frequency Tolerance Startup Time Startup Time Trim Cap Trim Resolution  Widd ata Sheet 4 U.com Idd  10kHz Oscillator Output Frequency Operating Current                                                                                                      | -20<br>-25      | 35               | 15                    | dBm                          | ·                                                                                                                                                     |

| PHARMONICS  TX PA  Output Cap.  Output Switch R  On/Off Ratio  Output Harmonics  Operating Current  Operating Current  High Power Low Power High Power Low Power Crystal Oscillator  Center Frequency Tolerance Startup Time Startup Time Trim Cap Trim Resolution  Idd  10kHz Oscillator  Output Frequency Operating Current                                                                                                                              | -25             | 35               |                       |                              | Range of output power in the high power mode                                                                                                          |

| PHARMONICS  TX PA  Output Cap. Output Switch R On/Off Ratio Output Harmonics Operating Current Operating Current High Power Low Power High Power Low Power Crystal Oscillator Center Frequency Tolerance Startup Time Startup Time Trim Cap Trim Resolution Idd 10kHz Oscillator Output Frequency Operating Current                                                                                                                                        | 2               | 35               | 0                     | dBm                          |                                                                                                                                                       |

| Output Cap. Output Switch R On/Off Ratio Output Harmonics Operating Current High MAX Power Power High MAX Power Low Power Low Power Crystal Oscillator Center Frequency Tolerance Startup Time Startup Time Trim Cap Trim Resolution Widd ataSheet4U.com Idd I0kHz Oscillator Output Frequency Operating Current                                                                                                                                           |                 | 35               |                       |                              | Range of output power in the low power mode                                                                                                           |

| Output Cap. Output Switch R On/Off Ratio Output Harmonics Operating Current Operating Current High MAX Power Power Low Power High MAX Power Power Crystal Oscillator Center Frequency Tolerance Startup Time Startup Time Trim Cap Trim Resolution Vivid ata Sheet 4 U.com Idd  10kHz Oscillator Output Frequency Operating Current                                                                                                                        |                 |                  |                       | dBc                          | With complete matching network                                                                                                                        |

| Output Switch R On/Off Ratio Output Harmonics Operating Current Operating Current High Power Low Power High Power Low Power Crystal Oscillator Center Frequency Tolerance Startup Time Trim Cap Trim Resolution Vold ataSheet4U.com Idd 10kHz Oscillator Output Frequency Operating Current                                                                                                                                                                |                 |                  |                       |                              |                                                                                                                                                       |

| On/Off Ratio Output Harmonics Operating Current Operating Current High Power Low Power High Power Low Power Crystal Oscillator Center Frequency Tolerance Startup Time Startup Time Trim Cap Trim Resolution VoldataSheet4U.com Idd 10kHz Oscillator Output Frequency Operating Current                                                                                                                                                                    | 5               |                  | 7.5                   | pF                           | Internal capacitor range for the PA adjustable trim                                                                                                   |

| Output Harmonics Operating Current Operating Current High Power Low Power High MAX Power Power Crystal Oscillator Center Frequency Tolerance Startup Time Startup Time Trim Cap Trim Resolution Vold ataSheet4U.com Idd 10kHz Oscillator Output Frequency Operating Current                                                                                                                                                                                |                 |                  | 18                    | Ω                            |                                                                                                                                                       |

| Operating Current  Operating Current  High Power Low Power Low Power  Crystal Oscillator Center Frequency Tolerance Startup Time Startup Time Trim Cap Trim Resolution  Widd ataSheet4U.com Idd  10kHz Oscillator Output Frequency Operating Current                                                                                                                                                                                                       |                 | 60               |                       | dB                           |                                                                                                                                                       |

| Operating Current  High Power Power Low Power High Power Low Power Low Power Crystal Oscillator Center Frequency Tolerance Startup Time Startup Time Trim Cap Trim Resolution Idd 10kHz Oscillator Output Frequency Operating Current                                                                                                                                                                                                                      |                 | <b>5</b> 0       | -35                   | dBc                          | With typical 50Ω matching circuits                                                                                                                    |

| MAX Power Low Power High Power Low Power Low Power Low Power Crystal Oscillator Center Frequency Tolerance Startup Time Startup Time Trim Cap Trim Resolution Idd 10kHz Oscillator Output Frequency Operating Current                                                                                                                                                                                                                                      |                 | 50               | 68                    | mA                           | 15dBm CW                                                                                                                                              |

| MAX Power Low Power High MAX Power Low Power Low Power Crystal Oscillator Center Frequency Tolerance Startup Time Startup Time Trim Cap Trim Resolution Widd ata Sheet 4 U.com Idd 10kHz Oscillator Output Frequency Operating Current                                                                                                                                                                                                                     |                 | 12               | 24                    | mA                           | 0dBm CW                                                                                                                                               |

| Power High Power High Power Low Power Crystal Oscillator Center Frequency Tolerance Startup Time Startup Time Trim Cap Trim Resolution Widd ata Sheet 4 U.com Idd  10kHz Oscillator Output Frequency Operating Current                                                                                                                                                                                                                                     | 14              | 16.5             | 17                    | dBm                          |                                                                                                                                                       |

| MAX Power Low Power Crystal Oscillator Center Frequency Tolerance Startup Time Startup Time Trim Cap Trim Resolution Widd ataSheet4U.com Idd 10kHz Oscillator Output Frequency Operating Current                                                                                                                                                                                                                                                           | -1              | 4.5              | 5.7                   | dBm                          | Matching network for 50Ω 928MHz high                                                                                                                  |

| Power  Crystal Oscillator  Center Frequency Tolerance Startup Time Startup Time Trim Cap Trim Resolution Widd ataSheet4U.com Idd 10kHz Oscillator Output Frequency Operating Current                                                                                                                                                                                                                                                                       | 15.8            | 16.5             | 17                    | dBm                          | Matching network for 50Ω 433MHz high                                                                                                                  |

| Center Frequency Tolerance Startup Time Startup Time Trim Cap Trim Resolution wyddataSheet4U.com Idd 10kHz Oscillator Output Frequency Operating Current                                                                                                                                                                                                                                                                                                   | 3               | 4                | 5                     | dBm                          | Matching network for 3052 453/M 12 High                                                                                                               |

| Tolerance Startup Time Startup Time Trim Cap Trim Resolution Widd ata Sheet 4 U.com Idd  10kHz Oscillator Output Frequency Operating Current                                                                                                                                                                                                                                                                                                               |                 |                  |                       |                              |                                                                                                                                                       |

| Startup Time Startup Time Trim Cap Trim Resolution Widd ata Sheet 4 U.com Idd 10kHz Oscillator Output Frequency Operating Current                                                                                                                                                                                                                                                                                                                          |                 | 24               |                       | MHz                          | Trimmed                                                                                                                                               |

| Startup Time Trim Cap Trim Resolution Widd ataSheet4U.com Idd 10kHz Oscillator Output Frequency Operating Current                                                                                                                                                                                                                                                                                                                                          |                 |                  | 20                    | ppm                          | Required crystal tolerance                                                                                                                            |

| Trim Cap Trim Resolution wyadataSheet4U.com Idd 10kHz Oscillator Output Frequency Operating Current                                                                                                                                                                                                                                                                                                                                                        |                 | 50               | 100                   | us                           | Quick Start enabled                                                                                                                                   |

| Trim Resolution Wydd ata Sheet 4 U.com Idd 10kHz Oscillator Output Frequency Operating Current                                                                                                                                                                                                                                                                                                                                                             |                 | 2                | 5                     | ms                           | Quick Start disabled                                                                                                                                  |

| Idd  10kHz Oscillator  Output Frequency Operating Current                                                                                                                                                                                                                                                                                                                                                                                                  | 0               |                  | 45                    | pF                           | Internal trim capacitor (self calibration sets)                                                                                                       |

| 10kHz Oscillator Output Frequency Operating Current                                                                                                                                                                                                                                                                                                                                                                                                        | 145             | 160              | 175                   | fF                           |                                                                                                                                                       |

| 10kHz Oscillator Output Frequency Operating Current                                                                                                                                                                                                                                                                                                                                                                                                        |                 | 800              |                       | uA                           | Normal operation                                                                                                                                      |

| Output Frequency Operating Current                                                                                                                                                                                                                                                                                                                                                                                                                         |                 | 1.5              |                       | mA                           | During Quick Start                                                                                                                                    |

| Operating Current                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 |                  | l                     |                              |                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 9.8             | 10               | 10.2                  | kHz                          | After trimming                                                                                                                                        |

| Duty Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 300             | 375              | 450                   | nA                           | After trimming                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 | 50               |                       | %                            |                                                                                                                                                       |

| ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                 | 0                |                       | D:t-                         |                                                                                                                                                       |

| Resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                 | 8                | Vuet                  | Bits                         | Full coals input years                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1/00            | 4                | vrei                  |                              |                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Vss             |                  |                       |                              | •                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Vss             |                  |                       |                              | internal voltage reference                                                                                                                            |

| fclk                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Vss             | 1                | 2                     | MHz                          | Clock frequency                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 |                  |                       |                              | Clock rate = 2MHz                                                                                                                                     |

| Conversion Time                                                                                                                                                                                                                                                                                                                                                                                                                                            | Vss<br>0.01     |                  |                       | Tclk                         | OTOOK TOLO - ZIVII IZ                                                                                                                                 |

| FSR Ci Vref Reference Offset                                                                                                                                                                                                                                                                                                                                                                                                                               |                 | 1<br>2.0<br>1    | Vref                  | V<br>pF<br>V<br>%FSR         | Full scale input range Input capacitance Internal voltage reference                                                                                   |

# **AMIS-53000** Frequency Agile Transceiver

Table 6: Operational Specifications (Continued)

| rable 6. Operational s |      | <u> </u> |      |                    |                   |                                                           |

|------------------------|------|----------|------|--------------------|-------------------|-----------------------------------------------------------|

| Parameter              | Min. | Тур.     | Max. | Units              | Comment           |                                                           |

| Data Filter            |      |          |      |                    |                   |                                                           |

| 3dB Down Point         | 110  | 120      | 130  | %F <sub>DATA</sub> | AM data filter    | bandwidth (relative to associated defined data rates)     |

| Temperature Senso      | r    | •        | •    | *                  | ·<br>             |                                                           |

| Output Voltage         | 0.93 | 0.97     | 1.01 | V                  | At 27°C           |                                                           |

| Voltage Range          | 0.61 | 0.97     | 1.4  | V                  | Output            |                                                           |

| Slope                  |      | -5.24    |      | mv/°C              | dV/dT             |                                                           |

| RSSI Buffer            |      |          |      |                    |                   |                                                           |

| Input Range            | 0    |          | Vdd  | V                  |                   |                                                           |

| Operating Current      | 135  | 185      | 250  | uA                 |                   |                                                           |

| Unity Gain-BW          | 615  | 1000     | 1700 | kHz                | 100kΩ/100pF       | load                                                      |

| PLL                    | •    | •        | •    |                    | *                 |                                                           |

| Reference Input        |      | 12       |      | MHz                | Transmit mode     | e (24MHz external crystal)                                |

| Frequency              |      | 16       |      | MHz                | Receive mode      | (24MHz external crystal)                                  |

| Resolution             |      | 91.55    |      | Hz                 | Frequency ste     | p size                                                    |

| VCO Gain               | 9.62 | 12       | 14.4 | MHz/V              | @ 400MHz          | @ 900MHz, although layout PCB                             |

| Constant               | 25.6 | 32       | 38.4 | MHz/V              | @ 900MHz          | parasitics and component placement will change this value |

| Settling Time          |      | 100      |      | us                 | Internal loop fil | lter                                                      |

| Phase Noise            |      | -90      | -80  | dBc/Hz             | Internal loop fil | ter @ 10kHz offset                                        |

| Phase Noise            |      | -120     | -110 | dBc/Hz             | Internal loop fil | ter @ 3MHz offset                                         |

| Max Spurious<br>Level  |      | -70      | -50  | dBc                | Internal loop fil | lter                                                      |

| POR                    |      |          |      |                    |                   |                                                           |

| Delay Time             | 28   | 43       | 60   | ms                 |                   |                                                           |

| Brown-out Trip         | 1.2  | 1.6      | 1.8  | V                  |                   |                                                           |

www.DataSheet4U.com

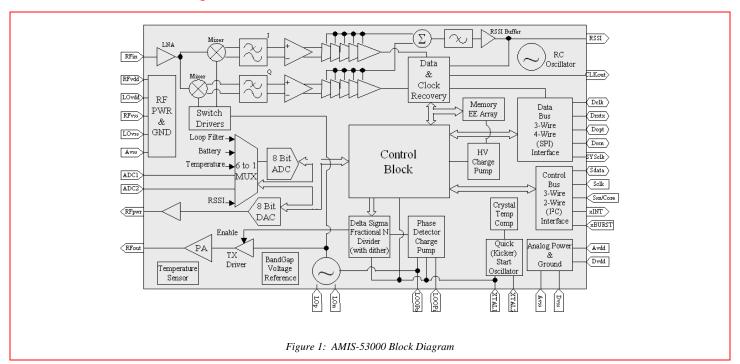

### 3.0 Block Diagrams

#### 3.1 AMIS-53000 Overall Block Diagram

#### 3.2 Package

## 3.2.1. Pin Definition www.DataSheet4U.com

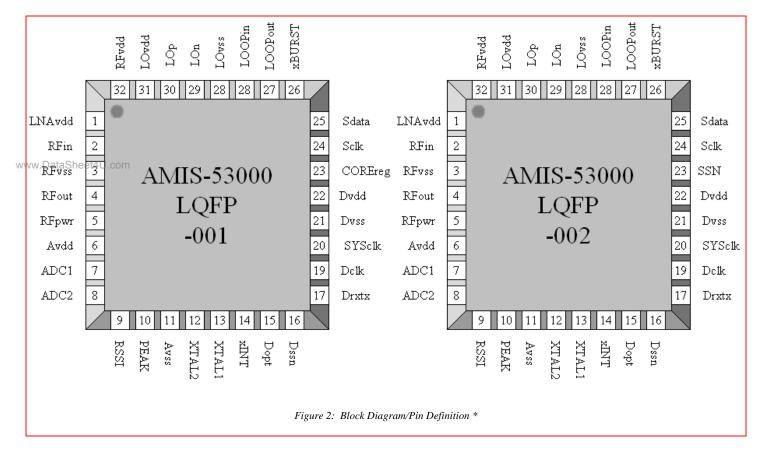

| Table 7: F | Pin Definitions |        |                |                                                                                                             |

|------------|-----------------|--------|----------------|-------------------------------------------------------------------------------------------------------------|

| Pin#       | -001            | -002   | Pin Type       | Description                                                                                                 |

| 1          | LNAvdd          | LNAvdd | Power          | A DC short (inductor) is connected to VDD from this pin                                                     |

| 2          | RFin            | RFin   | Analog Input   | The RF input to the receiver circuits                                                                       |

| 3          | RFvss           | RFvss  | Ground         | Ground for the RF circuits                                                                                  |

| 4          | RFout           | RFout  | Analog Output  | RF transmit output                                                                                          |

| 5          | RFpwr           | RFpwr  | Analog Output  | Variable DC voltage output to power the RF transmitter (requires a DC short {inductor} connection to Rfout) |

| 6          | Avdd            | Avdd   | Power          | Vdd power for the analog circuits                                                                           |

| 7          | ADC1            | ADC1   | Analog Input   | Input to the analog to digital conversion circuit                                                           |

| 8          | ADC2            | ADC2   | Analog Input   | Input to the analog to digital conversion circuit                                                           |

| 9          | RSSI            | RSSI   | Analog IO      | Analog voltage related to the strength of the received RF                                                   |

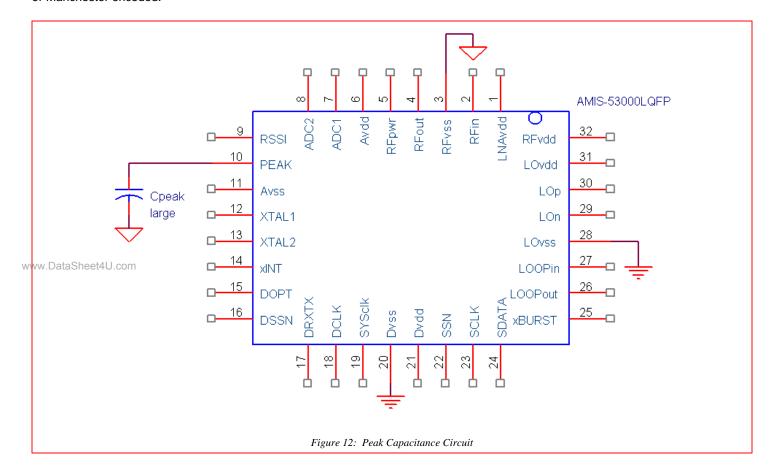

| 10         | PEAK            | PEAK   | Analog         | Analog voltage for external auto-slice capacitor                                                            |

| 11         | Avss            | Avss   | Ground         | Ground for the analog circuits                                                                              |

| 12         | XTAL2           | XTAL2  | Analog         | Connection to an external crystal                                                                           |

| 13         | XTAL1           | XTAL1  | Analog         | Connection to an external crystal                                                                           |

| 14         | INT             | INT    | Digital Output | Interrupt to external controller                                                                            |

| 15         | Dopt            | Dopt   | Digital Input  | Optional data pin for the 4-wire data interface mode                                                        |

| 16         | Dssn            | Dssn   | Digital IO     | Active low select line for the data interface                                                               |

Table 7: Pin Definitions (Continued)

| Pin# | -001    | -002    | Pin Type       | Description                                                                                                        |

|------|---------|---------|----------------|--------------------------------------------------------------------------------------------------------------------|

| 17   | Drxtx   | Drxtx   | Digital IO     | Serial data input (transmit) or output (received)                                                                  |

| 18   | Dclk    | Dclk    | Digital IO     | Recovered clock output (data interface clock)                                                                      |

| 19   | SYSclk  | SYSclk  | Digital Output | System clock output                                                                                                |

| 20   | Dvss    | Dvss    | Ground         | Ground for the digital circuits                                                                                    |

| 21   | Dvdd    | Dvdd    | Power          | Vdd power for the digital circuits                                                                                 |

| 22   | CoreReg | SSN     | Digital        | -001 (control and status for the serial data interface) -002 (decoupling capacitor pin for the internal regulator) |

| 23   | SCLK    | SCLK    | Digital        | Bi-directional clock for the 2-wire serial interface                                                               |

| 24   | SDATA   | SDATA   | Digital        | Bi-directional data for the 2-wire serial interface                                                                |

| 25   | xBURST  | xBURST  | Digital Input  | Active low input interrupt that will immediately cause a Burst transmission                                        |

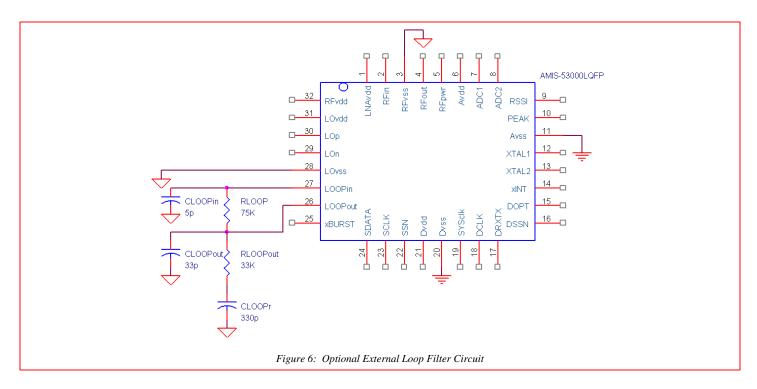

| 26   | LOOPout | LOOPout | Analog         | Output to the optional external loop filter                                                                        |

| 27   | LOOPin  | LOOPin  | Analog         | Input from the optional external loop filter                                                                       |

| 28   | LOvss   | LOvss   | Ground         | Ground for the local oscillator circuits                                                                           |

| 29   | LOn     | LOn     | Analog         | Negative side of the VCO tank                                                                                      |

| 30   | LOp     | LOp     | Analog         | Positive side of the VCO tank                                                                                      |

| 31   | LOvdd   | LOvdd   | Power          | Vdd for the local oscillator circuits                                                                              |

| 32   | RFvdd   | RFvdd   | Power          | Vdd power for the RF circuits                                                                                      |

#### 3.2.2. Block Diagram/Pin Definition

<sup>\*</sup> Not actual package markings. Please see marking format in 3.2.3.3.

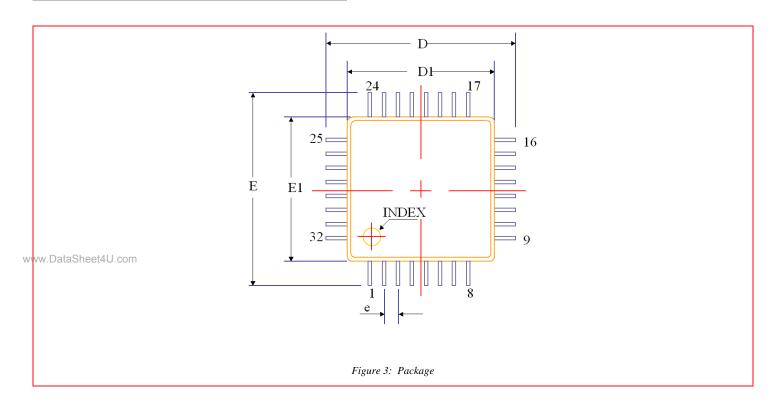

#### 3.2.3. Physical Characteristics

#### 3.2.3.1. Package Type

32 pin LQFP

#### 3.2.3.2. Package Dimensions

Table 8: AMIS-53000 LQFP Package Dimensions

| Symbol    | Min.     | Min. Nom. Max |      | Units |

|-----------|----------|---------------|------|-------|

| Thickness | -        | -             | 1.60 | mm    |

| D         | 9.00 E   | 3SC           |      | mm    |

| D1        | 7.00 E   | 3SC           |      | mm    |

| E         | 9.00 E   | 3SC           |      | mm    |

| E1        | 7.00 BSC |               |      | mm    |

| е         | 0.80 E   | 3SC           |      | mm    |

#### 3.2.3.3. Package Marking Format

(AMIS Logo) AMIS53000a 19608-bbb XXXXYZZ

Where:

a is the market application

bbb is the AMIS device version

XXXXYZZ is the date and tractability code\*\*\*\* is the country of origin (found on underside of chip).

The year in which the mask work was first fixed in a semiconductor chip product may also appear.

### 4.0 Acronyms

The following acronyms are used in this document.

| AM AMBIILIQUE MOQUIALEGISIGNA | AM | Amplitude Modulated signal |

|-------------------------------|----|----------------------------|

|-------------------------------|----|----------------------------|

ASIC Integrated circuit designed for a single customer requirement

ASK Amplitude Shift Key

ASSP A custom integrated circuit, that may be used in general designs

ASTRIC AMI Semiconductor's family of wireless products

CCA Clear Channel Assessment

CDR Clock and Data Recovery, data is recovered from the received signal using a synchronous clock

CRC Cyclic Redundancy Checking; data error checking

CW Continuous Wave, a single frequency or modulated signal carrier

DAC Digital to Analog Conversion