# Agilent AMMC-3040 18-36 GHz Double-Balanced Mixer with Integrated LO Amplifier/Multiplier

**Data Sheet**

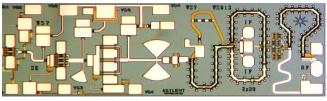

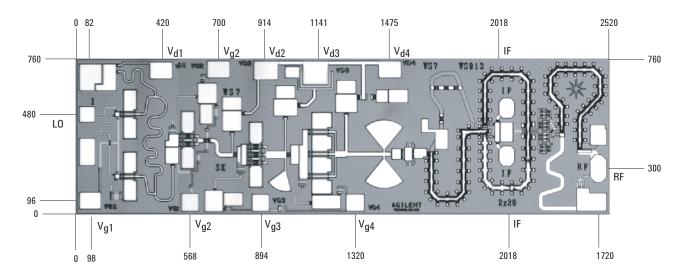

Chip Size: 2520 x 760 µm (99.2 x 29.9 mils)

Chip Size Tolerance:  $\pm$  10  $\mu$ m ( $\pm$  0.4 mils) Chip Thickness:  $100 \pm 10 \ \mu$ m ( $4 \pm 0.4 \ mils$ ) Pad Dimensions:  $75 \times 75 \ \mu$ m ( $3 \pm 0.4 \ mils$ )

#### **Description**

The AMMC-3040 is a broadband Double-Balanced Mixer (DBM) with an integrated high-gain LO amplifier. This MMIC can be used as either an up converter or down converter in microwave or millimeter wave applications. If desired, the LO amplifier can be biased to function as a frequency multiplier to enable second harmonic mixing of the LO input. The mixer section of the AMMC-3040 is fabricated using a suspended metal system to create a unique, broadsidecoupled balun structure (patent pending) to achieve exceptional bandwidth. The MMIC provides repeatable conversion loss without tuning, making it highly suitable for automated assembly processes.

DataSheet4LL com

#### **Features**

High IIP3: +23 dBm

· Wide Bandwidth

• RF: 18-36 GHz

· LO: 18-36 GHz

• IF: DC-3 GHz

Fundamental or Sub-Harmonic Mixing

· Up or Down Converter

· Conversion Loss: 9.5dB

• P1dB: +17 dBm

· Low LO Drive Power: + 2 dBm

Usable to 42 GHz

#### **Applications**

Point-to-Point Radio

LMDS

SATCOM

# AMMC-3040 Absolute Maximum Ratings<sup>[1]</sup>

| Symbol                   | Parameters/Conditions              | Units | Min. | Max. |

|--------------------------|------------------------------------|-------|------|------|

| V <sub>D1, 2, 3, 4</sub> | Positive Drain Voltage             | V     |      | 5    |

| V <sub>G1, 2, 3, 4</sub> | Gate Voltage                       | V     | -3.0 | 0.5  |

| I <sub>dd</sub>          | Total Drain Current                | mA    |      | 550  |

| T <sub>ch</sub>          | Operating Channel Temp.            | °C    |      | +160 |

| T <sub>b</sub>           | Operating Backside Temp.           | °C    | -55  |      |

| T <sub>stg</sub>         | Storage Case Temp.                 | °C    | -65  | +165 |

| T <sub>max</sub>         | Maximum Assembly Temp (60 sec max) | °C    |      | +300 |

Note

1. Operation in excess of any one of these conditions may result in permanent damage to this device.

Note: These devices are ESD sensitive. The following precautions are strongly recommended: Ensure that an ESD approved carrier is used when dice are transported from one destination to another. Personal grounding is to be worn at all times when handling these devices.

DataSh

# ${\bf AMMC\text{-}3040\ DC\ Specifications/Physical\ Properties}^{[1]}$

| Symbol                   | Parameters and Test Conditions                                                                            | Units | Min. | Тур. | Max. |

|--------------------------|-----------------------------------------------------------------------------------------------------------|-------|------|------|------|

| V <sub>D1, 2, 3, 4</sub> | Drain Supply Operating Voltage                                                                            | V     | 2    | 3.5  | 5    |

| I <sub>d1</sub>          | First Stage Drain Supply Current $V_{dd} = 3.5 \text{ V}, V_{g1} = -0.5 \text{ V}$                        | mA    |      | 50   |      |

| I <sub>D2, 3, 4</sub>    | Total Drain Supply Current for Stages 2, 3 and 4 ( $V_{dd} = 3.5 \text{ V}$ , $V_{gg} = -0.5 \text{ V}$ ) | mA    |      | 225  |      |

| V <sub>G1, 2, 3, 4</sub> | Gate Supply Operating Voltages (I <sub>dd</sub> = 250 mA)                                                 | V     |      | -0.5 |      |

| $\overline{V_p}$         | Pinch-off Voltage ( $V_{dd} = 3.5 \text{ V}$ , $I_{dd} < 10 \text{ mA}$                                   | V     |      | -1.5 |      |

| $\theta_{ch-b}$          | Thermal Resistance <sup>[2]</sup> (Backside Temp. T <sub>b</sub> = 25°C)                                  | °C/W  |      | 49   |      |

#### Notes:

et4U.com

- 1. Measured in wafer form with  $\rm T_{chuck}$  = 25°C. (Except  $\theta ch\text{-bs.})$

- 2. Channel-to-backside Thermal Resistance ( $\Theta$ ch-b)= $58^{\circ}$ C/ $\Omega$  at Tchannel (Tc)= $150^{\circ}$ C as measured using the liquid crystal method. Thermal Resistance at backside temperature ( $T_b$ )= $25^{\circ}$ C calculated from measured data.

# **AMMC-3040 RF Specifications**

Zo=50  $\Omega$ , Tb = 25°C, IF Output = 2 GHz, LO Input Power = +2 dBm, RF Input Power = -20 dBm, except as noted.

| Symbol              | Parameters and Test Conditions                                                                          |     | V dd =3.5 V,<br>I dd =250 mA |      | V dd =4.5 V,<br>I dd =150 mA |  |

|---------------------|---------------------------------------------------------------------------------------------------------|-----|------------------------------|------|------------------------------|--|

|                     | DataSheet4U.com                                                                                         |     | Тур.                         | Max. | Тур.                         |  |

| Lc                  | Conversion Loss, Down Conversion [1]                                                                    | dB  | 9.5                          | 12   | 10                           |  |

| Lc                  | Conversion Loss, Up Conversion [2]                                                                      | dB  | 10                           |      | 10.5                         |  |

| ISOL <sub>L-R</sub> | LO - RF Isolation at RF Frequency = 22 GHz <sup>[3]</sup>                                               | dB  | 31                           |      | 32                           |  |

| P <sub>-1 dB</sub>  | Input Power at 1 dB Conversion Loss<br>Compression, Down Conversion                                     | dBm | 17                           |      | 17                           |  |

| IIP3                | Input 3 <sup>rd</sup> Order Intercept Point,<br>Down Conversion at RF Frequency = 22 GHz <sup>[4]</sup> | dBm | 23                           |      | 22                           |  |

#### Notes:

- 1. 100% on-wafer RF testing is done at RF frequency = 18, 22, and 32 GHz.

- 2. IF Input = 2 GHz, IF Input Power = -20 dBm, RF freq = L0 + IF

- 3. Does not include LO amplifier gain of ~20 dB.

- 4.  $\Delta f = 2$  MHz, RF Input Power = -5 dBm.

DataSh

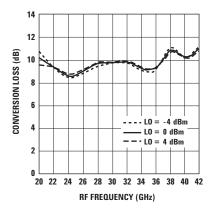

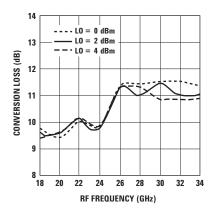

#### **AMMC-3040 Typical Performance**

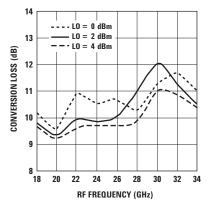

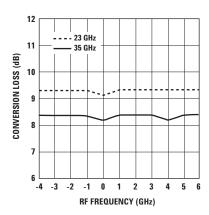

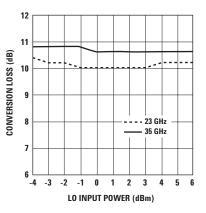

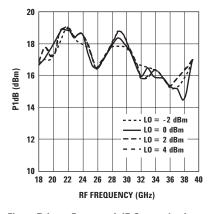

Zo=50  $\Omega$ , Tb = 25°C, IF = 2 GHz, LO Input Power = +2 dBm, RF Input Power = -20 dBm, except as noted.

L0 = -4 dBm 13 LO = 0 dBm CONVERSION LOSS (dB) --- L0 = 4 dBm 12 10 26 30 32 34 36 20 22 24 28 RF FREQUENCY (GHz)

Figure 1. Conversion Loss, UpConversion.  $V_d = 3.5 \text{ V}, I_d = 250 \text{ mA}, LO \text{ freq} = RF - IF.$

Figure 2. Conversion Loss, Down Conversion.  $V_d = 3.5 \text{ V}, I_d = 250 \text{ mA}, LO \text{ freq} = RF - IF.$

Figure 3. Conversion Loss, Up Conversion.  $V_d = 4.5 \text{ V}, I_d = 150 \text{ mA}, LO \text{ freq} = RF + IF.$

Figure 4. Conversion Loss, Down Conversion.  $V_d = 4.5 \text{ V}, I_d = 150 \text{ mA}, L0 \text{ freq} = RF + IF.$

Figure 5. Conversion Loss Vs. LO Input Power, Up Conversion.  $V_d = 3.5 \text{ V}$ ,  $I_d = 250 \text{ mA}$ , LO freq = RF

Figure 6. Conversion Loss Vs. LO Input Power, Down Conversion.  $V_d = 3.5 \text{ V, I}_d = 250 \text{ mA, LO}$ freq = RF - IF.

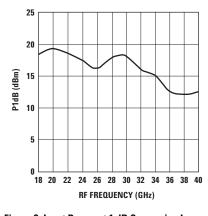

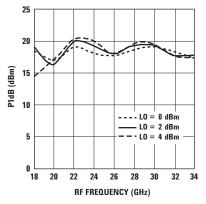

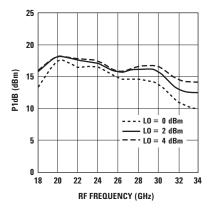

Figure 7. Input Power at 1 dB Conversion Loss Compression, Down Conversion.  $V_d = 3.5 \text{ V, I}_d = 250 \text{ mA, LO freq} = \text{RF} + \text{IF.}$

Figure 8. Input Power at 1 dB Conversion Loss Compression, Up Conversion.

$V_d = 3.5 \text{ V}, I_d = 250 \text{ mA}, LO \text{ freq} = RF + IF.$

Figure 9. Input Power at 1 dB Conversion Loss Compression, Down Conversion.

$V_d = 4.5 \text{ V}, I_d = 150 \text{ mA}, L0 \text{ freq} = RF + IF.$

DataSheet4U.com

et4U.com

## AMMC-3040 Typical Performance(cont.)

Figure 10. Input Power at 1 dB Conversion Loss Compression, Up Conversion.  $V_d=4.5\ V,\ I_d=150\ mA,\ L0\ freq=RF+IF.$

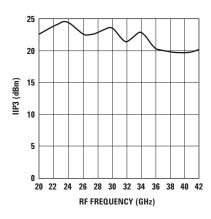

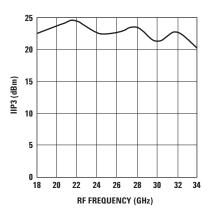

Figure 11. Input 3rd Order Intercept Point,, Down Conversion.  $V_d=3.5~\rm{V},~I_d=250~\rm{mA}, LO~\rm{freq}=RF$

Figure 12. Input 3rd Order Intercept Point, Down Conversion.  $V_d=4.5~\text{V},~l_d=150~\text{mA},~\text{LO freq}=$

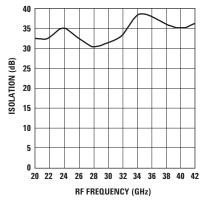

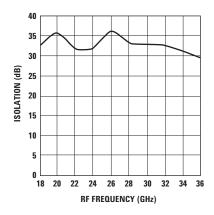

Figure 13. LO-RF Isolation, Down Conversion.  $V_d=3.5~V,~I_d=250~mA.$  Note: Does not include LO Buffer amplifier gain of ~20 dB, LO freq = RF

Figure 14. LO-RF Isolation, Down Conversion.  $V_d=4.5~V$ ,  $I_d=150~mA$ . Note: Does not include LO Buffer amplifier gain of  $\sim$ 18 dB, LO freq = RF - IF.

$\label{eq:Figure 15.4} \textbf{Figure 15. AMMC-3040 Bond Pad Locations, dimensions in microns.}$

DataSheet4U.com

et4U.com

DataSh

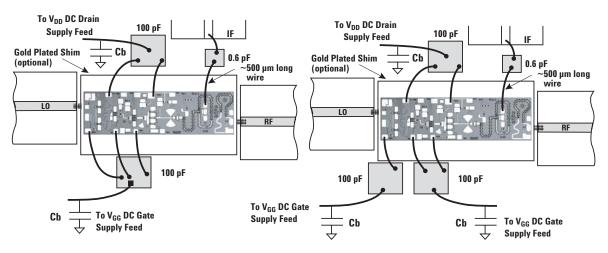

(a) Fundamental LO. Single drain and single gate supply assembly for using the LO amplifier in fundamental frequency mixer applications. (b) Sub-harmonic LO. Separate first-stage gate bias supply to use the LO amplifier as a multiplier for application as a sub-harmonic mixer.

(Note: To assure stable operation bias supply feeds should be bypassed to ground with a capacitor, Cb > 100 pF typical)

Figure 16. AMMC-3040 Assembly diagram.

#### **Biasing for Fundamental Mixing**

The recommended DC bias condition for the AMMC-3040 LO amplifier when used as a fundamental frequency mixer is with all four drains connected to a single 3.5 to 4.5V supply and all four gates connected to an adjustable negative supply voltage as shown in Figure 16 (a). The gate voltage is adjusted for a total drain supply current of typically 150 to 250 mA.

The second, third, and fourth stage DC drain bias lines are connected internally and therefore require only a single bond wire. A separate bond wire is needed for the first stage DC drain bias,  $V_{\rm d1}$

The third and fourth stage DC gate bias lines are connected internally. A total of three DC gate bond wires are required: one for  $V_{g1}$ , one for  $V_{g2}$ , and one for the  $V_{g3} \ / \ V_{g4}$  connection. The internal matching circuitry at the RF input creates a 50-ohm DC and RF path to ground. Any DC voltage applied to the RF input must be maintained below 1 volt, otherwise, a blocking capacitor should be used. The RF output is AC coupled.

No ground bond wires are needed since the ground connection is made by means of plated through via holes to the backside of the chip.

DataSheet4U.com

#### **Biasing for Sub-Harmonic Mixing**

The LO amplifier in the AMMC-3040 can also be used as a frequency doubler. Optimum conversion efficiency as a doubler is obtained with an input power level of 3 to 8 dBm.

Frequency multiplication is achieved by reducing the bias on the first stage FET to efficiently generate harmonics. The remaining three stages are then used to provide amplification.

While many bias methods could be used to generate and amplify the desired harmonics within the AMMC-3040's LO amplifier, the following information is suggested as a starting point for sub-harmonic mixing applications.

Frequency doubling is accomplished by biasing the first stage FET at pinch-off by setting  $V_{g1}$  =  $V_p \approx -1.1$  volts. The remaining three stages are biased for normal amplification, e.g.,  $V_{gg}$  is adjusted such that  $I_{d2} + I_{d3} + I_{d4} \approx 250$  mA. The drain voltage, Vdd, for all four stages should be 3.5 to 4.5 volts. The assembly diagram shown in Figure 16 (b) can be used as a guideline.

In all cases, Cb > 100 pF to assure stability.

### **IF Output Port**

The IF output port is located near the middle of the die, allowing this connection to be made from either side of the chip for maximum layout flexibility.

The LO and RF signals are reflectively terminating at the IF port by connecting a 20-mil (500 um) long bond wire from the IF output pad on the MMIC to a shunt 0.6 pF chip capacitor mounted off-chip as indicated in Figure 16.

JataSne

DataSheet

#### **Assembly Techniques**

The backside of the AMMC-3040 chip is RF ground. For microstripline applications, the chip should be attached directly to the ground plane (e.g., circuit carrier or heatsink) using electrically conductive epoxy<sup>[1]</sup>.

For best performance, the topside of the MMIC should be brought up to the same height as the circuit surrounding it. This can be accomplished by mounting a gold plated metal shim (same length and width as the MMIC) under the chip, which is of the correct thickness to make the chip and adjacent circuit coplanar.

The amount of epoxy used for chip and or shim attachment should be just enough to provide a thin fillet around the bottom perimeter of the chip or shim. The ground plane should be free of any residue that may jeopardize electrical or mechanical attachment.

For use on coplanar circuits, the chip can be mounted directly on the topside ground plane of the circuit as long as care is taken to ensure adequate heat sinking. Multiple vias underneath the chip will significantly improve heat conduction.

The location of the RF, LO, and IF bond pads is shown in Figure 15. Note that all RF input and output ports are in a Ground-Signal-Ground configuration. The IF port is located near the middle of the die, which allows for maximum layout flexibility since the IF connection can be made from either side of the chip.

RF connections should be kept as short as reasonable to minimize performance degradation due to series inductance. A single bond wire is sufficient for all signal connections. However, double-bonding with 0.7 mil gold wire or the use of gold mesh<sup>[2]</sup> is recommended for best performance, especially near the high end of the frequency range.

Thermosonic wedge bonding is the preferred method for wire attachment to the bond pads. Gold mesh can be attached using a 2 mil round tracking tool and a tool force of approximately 22 grams with an ultrasonic power of roughly 55 dB for a duration of 76 ± 8 mS. A guided wedge at an ultrasonic power level of 64 dB can be used for the 0.7 mil wire. The recommended wire bond stage temperature is 150 ± 2° C.

Caution should be taken to not exceed the Absolute Maximum Ratings for assembly temperature and time.

The chip is 100 µm thick and should be handled with care. This MMIC has exposed air bridges on the top surface and should be handled by the edges or with a custom collet (do not pick up die with vacuum on die center.)

This MMIC is also static sensitive and ESD handling precautions should be taken.

#### Notes:

- Ablebond 84-1 LM1 silver epoxy is recommended.

- 2. Buckbee-Mears Corporation, St. Paul, MN, 800-262-3824

#### **Ordering Information:**

AMMC-3040-W10 = waffle pack, 10 devices per tray

AMMC-3040-W50 = waffle pack, 50 devices per tray

# www.agilent.com/ semiconductors

For product information and a complete list of distributors, please go to our web site.

Data subject to change. Copyright © 2004 Agilent Technologies, Inc. February 12, 2004 5989-0528EN

DataSheet