# **Panasonic**

**AN32183A**

http://www.semicon.panasonic.co.jp/en/

### 9 x 9 Dots Matrix LED Driver IC

#### **FEATURES**

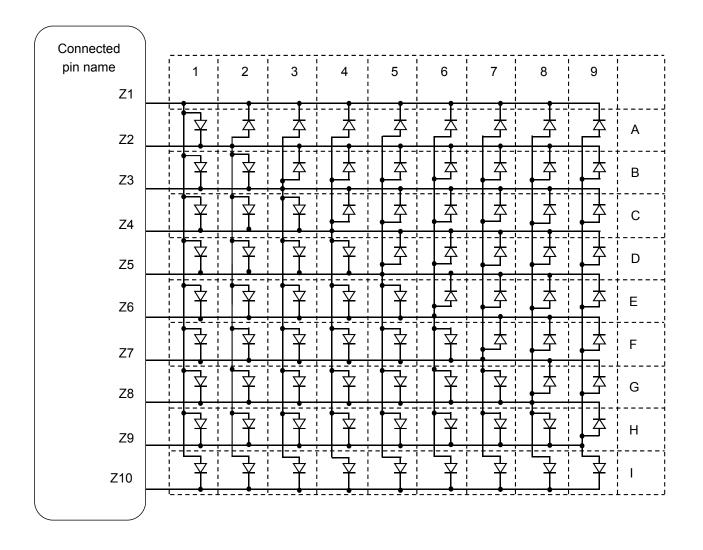

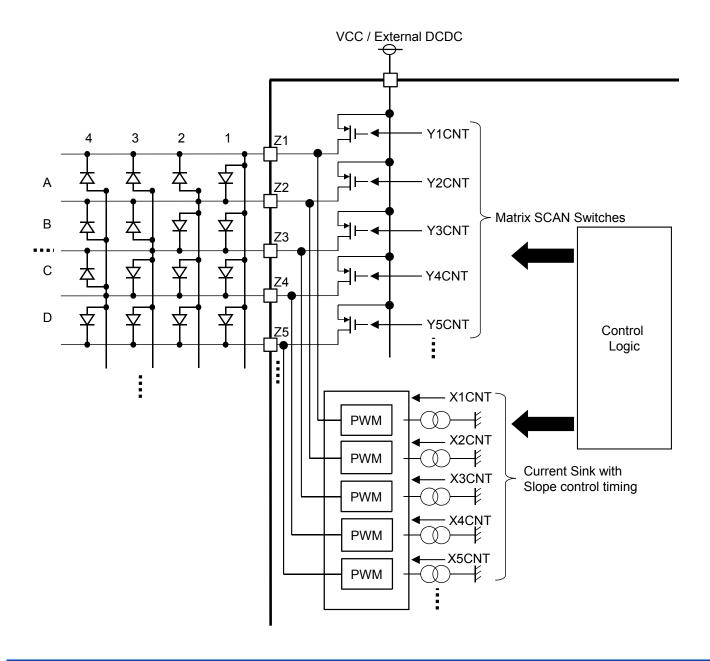

• 9 × 9 LED Matrix Driver

(Total LED that can be driven = 81)

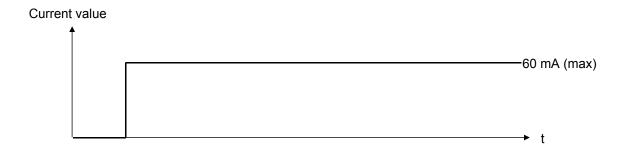

- LED Selectable Maximum Current

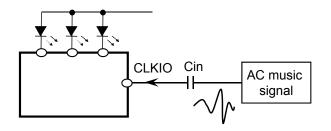

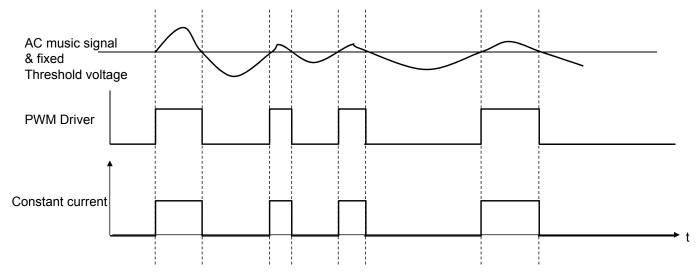

- LED Music Synchronizing Function

- I2C interface (Standard Mode, Fast Mode and

Fast Mode Plus)

(4 Slave address selectable)

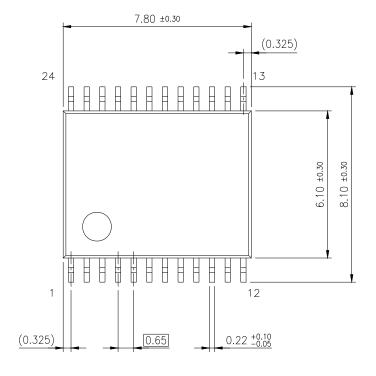

• 24 pin Shrink Small Outline Package (SSOP Type)

#### **DESCRIPTION**

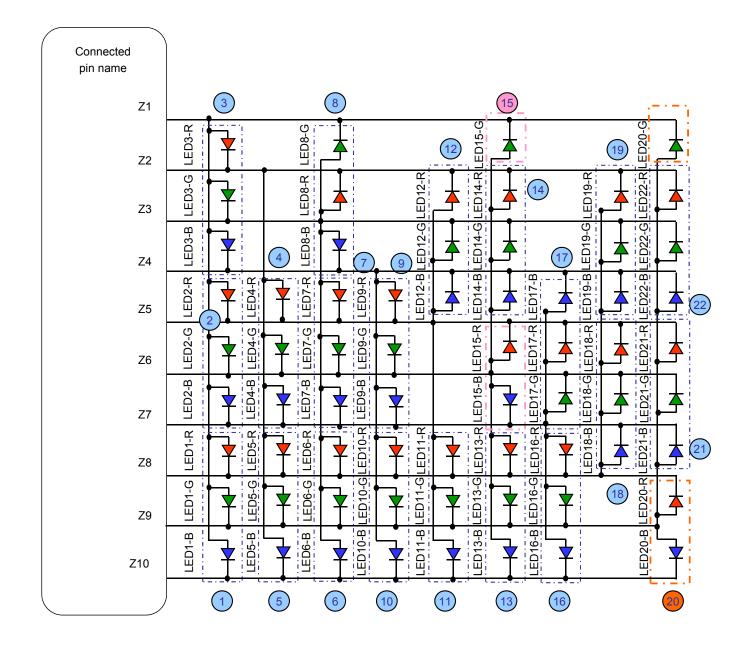

AN32183A is a 81 Dots Matrix LED Driver. It can drive up to 27 RGB LEDs.

#### **APPLICATIONS**

- Mobile Phone

- Smart Phone

- PCs

- Game Consoles

- · Home Appliances etc.

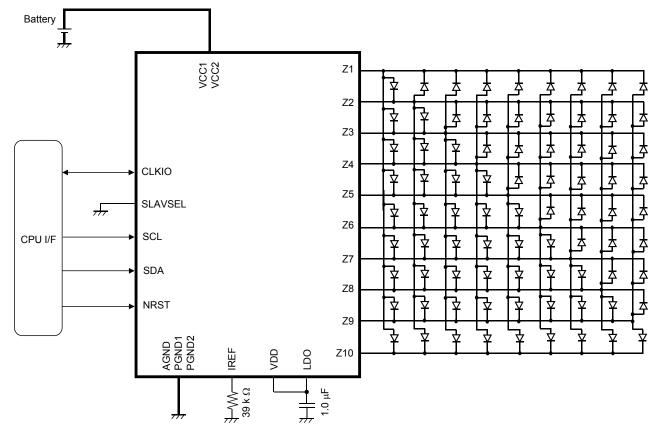

#### **TYPICAL APPLICATION**

Note:

The application circuit is an example. The operation of the mass production set is not guaranteed. Sufficient evaluation and verification is required in the design of the mass production set. The Customer is fully responsible for the incorporation of the above illustrated application circuit in the design of the equipment.

Page 1 of 56

## **AN32183A**

### **CONTENTS**

| ■ FEATURES         |                       |   | 1   |

|--------------------|-----------------------|---|-----|

| ■ DESCRIPTION      |                       |   | 1   |

| ■ APPLICATIONS     |                       |   | 1   |

| ■ TYPICAL APPLICAT | TON                   |   | 1   |

|                    |                       |   |     |

| ■ ORDERING INFORM  | ATION                 |   | 3   |

| ■ ABSOLUTE MAXIMU  | JM RATINGS            |   | 3   |

| ■ POWER DISSIPATIO | N RATING              |   | 3   |

| ■ RECOMMENDED OF   | PERATING CONDITIONS . |   | . 4 |

|                    |                       |   |     |

| ■ PIN CONFIGURATIO | N                     | 1 | 11  |

|                    |                       | 1 |     |

| ■ FUNCTIONAL BLOC  | K DIAGRAM             | 1 | 13  |

| ■ OPERATION        |                       | 1 | 15  |

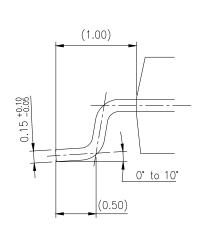

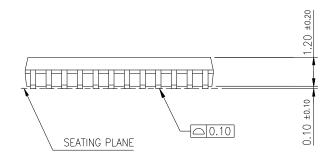

| ■ PACKAGE INFORM   | ATION                 |   | 55  |

| ■ IMPORTANT NOTICE | E                     |   | 56  |

**AN32183A**

#### ORDERING INFORMATION

| Order Number | Feature                     | Package     | Output Supply |

|--------------|-----------------------------|-------------|---------------|

| AN32183A-VF  | LED Driver for Illumination | 24 pin SSOP | Emboss Taping |

#### **ABSOLUTE MAXIMUM RATINGS**

| Parameter                      | Symbol                                                                                                    | Rating        | Unit | Note |

|--------------------------------|-----------------------------------------------------------------------------------------------------------|---------------|------|------|

| Cupply voltage                 | VCC <sub>MAX</sub>                                                                                        | 6.0           | V    | *1   |

| Supply voltage                 | VDD <sub>MAX</sub>                                                                                        | 6.0           | V    | *1   |

| Operating ambience temperature | T <sub>opr</sub>                                                                                          | - 30 to + 85  | °C   | *2   |

| Operating junction temperature | T <sub>j</sub>                                                                                            | – 30 to + 125 | °C   | *2   |

| Storage temperature            | T <sub>stg</sub>                                                                                          | – 55 to + 125 | °C   | *2   |

| Input Voltage Range            | $V_{SLAVSEL}, V_{SCL}, V_{SDA}, \ V_{CLKIO}, V_{NRST}$                                                    | - 0.3 to 6.0  | V    | _    |

| Output Voltage Range           | $V_{LDO}, V_{CLKIO}, \ V_{Z1}, V_{Z2}, V_{Z3}, V_{Z4}, V_{Z5}, \ V_{Z6}, V_{Z7}, V_{Z8}, V_{Z9}, V_{Z10}$ | - 0.3 to 6.0  | V    |      |

| ESD                            | НВМ                                                                                                       | 2.0           | kV   |      |

Note: This product may sustain permanent damage if subjected to conditions higher than the above stated absolute maximum rating. This rating is the maximum rating and device operating at this range is not guaranteed as it is higher than our stated recommended operating range. When subjected under the absolute maximum rating for a long time, the reliability of the product may be affected.

#### POWER DISSIPATION RATING

| PACKAGE                                         | $\theta_{JA}$ | P <sub>D</sub> (Ta=25 °C) | P <sub>D</sub> (Ta=85 °C) |

|-------------------------------------------------|---------------|---------------------------|---------------------------|

| 24 pin Shrink Small Outline Package (SSOP Type) | 135.1 °C /W   | 0.740 W                   | 0.296 W                   |

Note: For the actual usage, please refer to the P<sub>D</sub>-Ta characteristics diagram in the package specification, follow the power supply voltage, load and ambient temperature conditions to ensure that there is enough margin and the thermal design does not exceed the allowable value.

#### **CAUTION**

Although this IC has built-in ESD protection circuit, it may still sustain permanent damage if not handled properly. Therefore, proper ESD precautions are recommended to avoid electrostatic damage to the MOS gates.

Page 3 of 56

<sup>\*1:</sup>  $VCC_{MAX} = VCC$ ,  $VDD_{MAX} = VDD$ .

The values under the condition not exceeding the above absolute maximum ratings and the power dissipation.

<sup>\*2:</sup> Except for the power dissipation, operating ambient temperature, and storage temperature, all ratings are for Ta = 25°C.

**AN32183A**

#### RECOMMENDED OPERATING CONDITIONS

| Parameter            | Symbol                                                                                                                                                 | Min.  | Тур. | Max.                  | Unit | Note |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-----------------------|------|------|

| Supply voltage range | V <sub>CC</sub>                                                                                                                                        | 3.1   | 3.6  | 5.5                   | V    | *1   |

| Supply voltage range | V <sub>DD</sub>                                                                                                                                        | 1.7   | 1.85 | 5.5                   | V    | *1   |

| Input Voltage Range  | $V_{\text{SLAVSEL}}, V_{\text{SCL}}, V_{\text{SDA}}, \ V_{\text{CLKIO}}$                                                                               | - 0.3 | _    | V <sub>DD</sub> + 0.3 | V    | *2   |

|                      | V <sub>NRST</sub>                                                                                                                                      | - 0.3 | _    | V <sub>CC</sub> + 0.3 | V    | *2   |

| Output Voltage Range | $\begin{aligned} & V_{LDO}, V_{CLKIO}, \\ & V_{Z1},  V_{Z2},  V_{Z3},  V_{Z4},  V_{Z5} \\ & V_{Z6},  V_{Z7},  V_{Z8},  V_{Z9},  V_{Z10} \end{aligned}$ | - 0.3 | _    | V <sub>CC</sub> + 0.3 | V    | *2   |

Note: \*1: The values under the condition not exceeding the above absolute maximum ratings and the power dissipation.

Do not apply external currents and voltages to any pin not specifically mentioned.

Voltage values, unless otherwise specified, are with respect to GND. GND is voltage for AGND, PGND1 and GND2.

$\rm V_{\rm CC}$  is voltage for VCC1 and VCC2.  $\rm V_{\rm DD}$  is voltage for VDD.

\*2 : (V $_{\rm CC}$  + 0.3 ) V must not exceed 6 V. (V $_{\rm DD}$  + 0.3) V must not exceed 6 V.

**AN32183A**

#### **ELECTRICAL CHARACTERISTICS**

$V_{CC} = 3.6 \text{ V}, V_{DD} = 1.85 \text{ V}$  Notes:  $T_a = 25^{\circ}\text{C} \pm 2^{\circ}\text{C}$  unless otherwise noted.

|     | Danamatan                         | 0                | O a sa disti a sa                                            |                                                     | Limits |                                                     | 11!4 | Mada |

|-----|-----------------------------------|------------------|--------------------------------------------------------------|-----------------------------------------------------|--------|-----------------------------------------------------|------|------|

|     | Parameter                         | Symbol           | Condition                                                    | Min                                                 | Тур    | Max                                                 | Unit | Note |

| Cir | cuit Current                      |                  |                                                              |                                                     |        |                                                     |      |      |

|     | Circuit Current (1) OFF Mode      | I <sub>CC1</sub> | NRST = 0V                                                    | _                                                   | 0      | 1                                                   | μА   | _    |

|     | Circuit Current (2) OFF Mode      | I <sub>CC2</sub> | NRST = 3.6V                                                  |                                                     | 250    | 500                                                 | μА   |      |

| Int | ernal Oscillator                  |                  |                                                              |                                                     |        |                                                     |      |      |

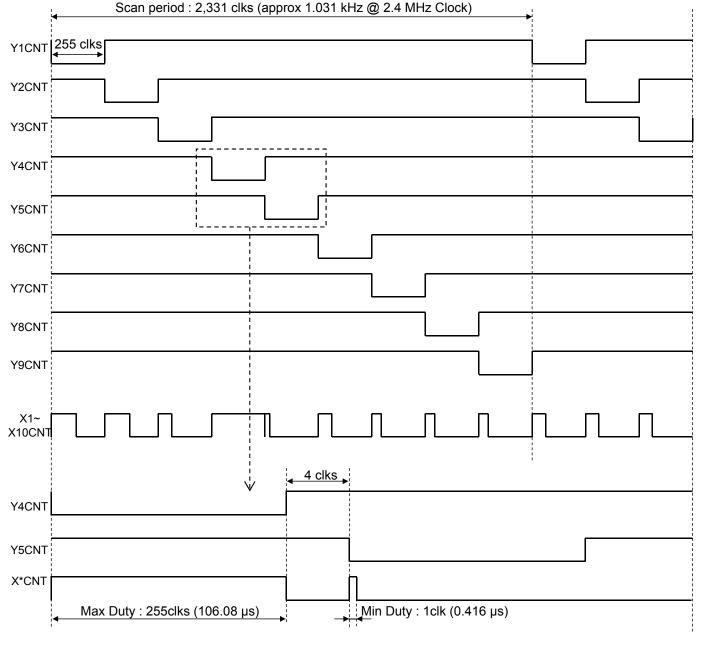

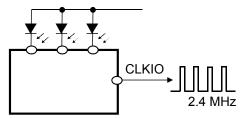

|     | Oscillation Frequency             | FDC1             | V <sub>CC</sub> = 3.6 V                                      | 1.92                                                | 2.40   | 2.88                                                | MHz  | _    |

| sc  | AN Switch                         |                  |                                                              |                                                     |        |                                                     |      |      |

|     | Switch On Resistance              | RSCAN            | $V_{CC} = 3.6 \text{ V}$<br>$I_{Z1\sim Z9} = -20 \text{ mA}$ | _                                                   | 1.5    | 3                                                   | Ω    | _    |

| Со  | nstant Voltage Source (LDC        | )                |                                                              | •                                                   |        | •                                                   | •    | •    |

|     | Output voltage (1)                | V <sub>L1</sub>  | I <sub>LDO</sub> = - 10 μA                                   | 2.75                                                | 2.85   | 2.95                                                | V    |      |

|     | Output voltage (2)                | V <sub>L2</sub>  | I <sub>LDO</sub> = - 15 mA                                   | 2.75                                                | 2.85   | 2.95                                                | V    |      |

| CL  | KIO                               |                  |                                                              |                                                     |        |                                                     |      |      |

|     | High Level Input<br>Voltage Range | V <sub>IH1</sub> | High Level Acknowledged Voltage (At External CLK Input Mode) | $\begin{array}{c} 0.7 \times \\ V_{DD} \end{array}$ | _      | V <sub>DD</sub> + 0.3                               | ٧    | _    |

|     | Low Level Input<br>Voltage Range  | V <sub>IL1</sub> | Low Level Acknowledged Voltage (At External CLK Input Mode)  | - 0.3                                               | _      | $\begin{array}{c} 0.3 \times \\ V_{DD} \end{array}$ | ٧    | _    |

|     | High Level Output Voltage         | V <sub>OH1</sub> | I <sub>CLKIO</sub> = -1 mA<br>(At Internal CLK Output Mode)  | $0.8 \times V_{DD}$                                 | _      | V <sub>DD</sub> + 0.3                               | ٧    | _    |

|     | Low Level Output Voltage          | V <sub>OL1</sub> | I <sub>CLKIO</sub> = 1 mA<br>(At Internal CLK Output Mode)   | - 0.3                                               | _      | 0.2 × V <sub>DD</sub>                               | ٧    | _    |

|     | High Level input Current          | I <sub>IH1</sub> | $V_{CC} = 5.5 \text{ V}$<br>$V_{CLKIO} = 5.5 \text{ V}$      | - 1                                                 | 0      | 1                                                   | μА   | _    |

|     | Low Level input Current           | I <sub>IL1</sub> | $V_{CC} = 5.5 \text{ V}$ $V_{CLKIO} = 0 \text{ V}$           | - 1                                                 | 0      | 1                                                   | μА   | _    |

**AN32183A**

### **ELECTRICAL CHARACTERISTICS (Continued)**

$V_{\rm CC}$  = 3.6 V,  $V_{\rm DD}$  = 1.85 V

Notes:  $T_a = 25^{\circ}C \pm 2^{\circ}C$  unless otherwise noted.

|     | Davamatav                    | Complete            | Condition                                                      |            | Limits |     | Unit   | Note |

|-----|------------------------------|---------------------|----------------------------------------------------------------|------------|--------|-----|--------|------|

|     | Parameter                    | Symbol              | Condition                                                      | Min        | Тур    | Max | Unit   | Note |

| Co  | nstant Current Source (Matr  | ix LED)             |                                                                |            |        |     |        |      |

|     |                              |                     | LED Current Setting = 20 mA                                    |            |        |     |        |      |

|     | Output Current (1)           | I <sub>MX1</sub>    | I <sub>MAX</sub> = [011], BRTXX = [1010]                       | 19         | 20     | 21  | mA     | *1   |

|     |                              |                     | $V_{Z1\sim Z10} = 1 \text{ V}$                                 |            |        |     |        |      |

|     |                              |                     | DAC Constant Current Mode                                      |            |        |     |        |      |

|     |                              |                     | LED Current Setting = 20 mA                                    |            |        |     |        |      |

|     |                              |                     | $I_{MAX} = [011], BRTXX = [1010]$                              |            | 2      |     |        |      |

|     | DAC Current Step             | DACSTEP             | $V_{Z1\sim Z10} = 1V$ , IDAC1 = $I_{Z1\sim Z10}$               | 0          |        | 4   | mA     | *2   |

|     | Drio odrieni otop            | DAGOTE              | LED Current Setting = 22 mA                                    |            |        |     | 1117 ( | _    |

|     |                              |                     | $I_{MAX} = [011], BRTXX = [1011]$                              |            |        |     |        |      |

|     |                              |                     | $V_{Z1\sim Z10} = 1 \text{ V, IDAC2} = I_{Z1\sim Z10}$         |            |        |     |        |      |

|     |                              |                     | DACSTEP = IDAC2 - IDAC1                                        |            |        |     |        |      |

|     |                              |                     | $V_{CC} = 5.5 \text{ V}, V_{DD} = 5.5 \text{ V}$               |            |        |     |        |      |

|     | OFF Mode Leak Current1       | I <sub>MXOFF1</sub> | $_{F1}$ MTXON = 0                                              |            | _      | 1   | μΑ     | *3   |

|     |                              |                     | $V_{Z1\sim Z10} = 5.5V$                                        |            |        |     |        |      |

|     |                              |                     | $V_{CC} = 5.5 \text{ V}, V_{DD} = 5.5 \text{ V}$               |            |        |     |        |      |

|     | OFF Mode Leak Current2       | I <sub>MXOFF2</sub> | MTXON = 0                                                      | <b>–</b> 1 | _      | 1   | μΑ     | *3   |

|     |                              |                     | $V_{Z1\sim Z10} = 0 \text{ V}$                                 |            |        |     |        |      |

|     |                              |                     | LED Current Setting = 20 mA                                    |            |        |     |        |      |

|     | Channel Difference           | I <sub>MXCH</sub>   | $I_{MAX} = [011], BRTXX = [1010]$                              | - 5        | _      | 5   | %      |      |

|     |                              | ·WXCH               | Difference of Z1 to 10 current from                            |            |        |     | , ,    |      |

|     |                              |                     | the average current value                                      |            |        |     |        |      |

| Vol | Itage at which LED driver ca | n keep con          | stant current value                                            |            |        |     |        |      |

| 1   |                              |                     | LED Current Setting = 20 mA                                    |            |        |     |        |      |

| 1   | LED Driver Veller            |                     | I <sub>MAX</sub> = [011], BRTXX = [1010]                       | 0.4        |        | _   | V      |      |

| 1   | LED Driver Voltage           | $V_{LD2}$           | Voltage at which LED Current change within ± 5 % compared with | 0.4        | _      |     |        | _    |

| 1   |                              |                     | LED Current of pin voltage = 0.5 V.                            |            |        |     |        |      |

Note: \* 1: This is allowable value when recommended parts (ERJ2RHD393X) are used for the terminal IREF.

<sup>\* 2:</sup> Current step for individual channels (Z1~Z10).

<sup>\* 3:</sup> Please refer to page 23 for more information on the setting.

**AN32183A**

#### **ELECTRICAL CHARACTERISTICS (Continued)**

$V_{CC} = 3.6 \text{ V}, V_{DD} = 1.85 \text{ V}$

Notes:  $T_a = 25^{\circ}C \pm 2^{\circ}C$  unless otherwise noted.

| Parameter                                     | Symbol                                      | Condition                                                                                                         |                     | Limits |                                | Unit  | Note |

|-----------------------------------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------|---------------------|--------|--------------------------------|-------|------|

| Parameter                                     | Syllibol                                    | Condition                                                                                                         | Min                 | Тур    | Max                            | Offic | Note |

| SLAVSEL                                       |                                             |                                                                                                                   |                     |        |                                |       |      |

| High Level Input Voltage<br>Range             | V <sub>IH2</sub>                            | High Level Acknowledged Voltage                                                                                   | $0.7 \times V_{DD}$ | _      | V <sub>DD</sub><br>+ 0.3       | V     | _    |

| Low Level Input Voltage<br>Range              | V <sub>IL2</sub>                            | Low Level Acknowledged Voltage                                                                                    | - 0.3               | _      | $0.3 \times V_{DD}$            | ٧     | _    |

| High Level Input Current                      | I <sub>IH2</sub>                            | $V_{CC} = 5.5 \text{ V}$ $V_{SLAVSEL} = 3.6 \text{ V}$                                                            | - 1                 | 0      | 1                              | μΑ    | _    |

| Low Level Input Current                       | I <sub>IL2</sub>                            | V <sub>CC</sub> = 5.5 V<br>V <sub>SLAVSEL</sub> = 0 V                                                             | - 1                 | 0      | 1                              | μΑ    | _    |

| NRST                                          | "                                           |                                                                                                                   | l                   |        |                                |       | l.   |

| High Level Input Voltage<br>Range             | V <sub>IH3</sub>                            | High Level Acknowledged Voltage                                                                                   | 1.5                 | _      | V <sub>CC</sub> + 0.3          | V     | _    |

| Low Level Input Voltage<br>Range              | V <sub>IL3</sub>                            | Low Level Acknowledged Voltage                                                                                    | - 0.3               | _      | 0.6                            | ٧     | _    |

| High Level Input Current                      | I <sub>IH3</sub>                            | V <sub>CC</sub> = 5.5 V<br>V <sub>NRST</sub> = 3.6 V                                                              | - 1                 | 0      | 1                              | μΑ    | _    |

| Low Level Input Current                       | I <sub>IL3</sub>                            | V <sub>CC</sub> = 5.5 V<br>V <sub>NRST</sub> = 0 V                                                                | - 1                 | 0      | 1                              | μΑ    | _    |

| I <sup>2</sup> C bus (Internal I/O stage char | acteristics)                                |                                                                                                                   |                     |        |                                |       |      |

| Low-level input voltage                       | V <sub>IL</sub>                             | Voltage which recognized that SDA and SCL are Low-level                                                           | -0.5                | _      | $0.3 \times V_{DD}$            | ٧     | *4   |

| High-level input voltage                      | V <sub>IH</sub>                             | Voltage which recognized that SDA and SCL are High-level                                                          | $0.7 \times V_{DD}$ | _      | VDD<br>MAX <sup>+</sup><br>0.5 | V     | *4   |

| Low-level output voltage 1                    | Low-level output voltage 1 V <sub>OL1</sub> |                                                                                                                   | 0                   | _      | 0.4                            | V     | _    |

| Low-level output voltage 2                    | V <sub>OL2</sub>                            | V <sub>DD</sub> < 2 V<br>I <sub>SDA</sub> = 3 mA                                                                  | 0                   | _      | $V_{DD}$                       | ٧     | _    |

| Low-level output current                      | I <sub>OL</sub>                             | V <sub>SDA</sub> = 0.4 V                                                                                          | 20                  | _      | _                              | mA    | _    |

| Input current each I/O pin                    | l <sub>i</sub>                              | $V_{CC}$ = 5.5 V, $V_{DD}$ = 5.5 V<br>$V_{SCL}$ , $V_{SDA}$ =<br>0.1 VDD <sub>MAX</sub> to 0.9 VDD <sub>MAX</sub> | - 10                | 0      | 10                             | μΑ    | _    |

| SCL clock frequency                           | f <sub>SCL</sub>                            | _                                                                                                                 | 0                   | _      | 1 000                          | kHz   | _    |

Note:  $\mathsf{VDD}_{\mathsf{MAX}}$  refers to the maximum operating supply voltage of  $\mathsf{V}_{\mathsf{DD}}$  .

Page 7 of 56

<sup>\*4 :</sup> The input threshold voltage of I²C bus (Vth) is linked to  $V_{DD}$  (I²C bus I/O stage supply voltage). In case the pull-up voltage is not  $V_{DD}$ , the threshold voltage (Vth) is fixed to (( $V_{DD}$  / 2)  $\pm$  (Schmitt width) / 2) and High-level, Low-level of input voltage are not specified. In this case, pay attention to Low-level (max.) value ( $V_{ILMAX}$ ). It is recommended that the pull-up voltage of I²C bus is set to the I²C bus I/O stage supply voltage ( $V_{DD}$ ).

**AN32183A**

### **ELECTRICAL CHARACTERISTICS (Continued)**

$V_{\rm CC}$  = 3.6 V,  $V_{\rm DD}$  = 1.85 V

Notes:  $T_a = 25^{\circ}C \pm 2^{\circ}C$  unless otherwise noted.

|                  | Parameter                                                                       | Symbol            | Condition                                                                                                                      |                           | Limits |      | Unit  | Note     |  |  |

|------------------|---------------------------------------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------|---------------------------|--------|------|-------|----------|--|--|

|                  | Parameter                                                                       | Syllibol          | Condition                                                                                                                      | Min                       | Тур    | Max  | Ullit | Note     |  |  |

| TS               | D (Thermal shutdown protec                                                      | tion circuit      | )                                                                                                                              |                           |        |      |       |          |  |  |

|                  | Detection temperature                                                           | Tdet              | Temperature which Constant current circuit, and Matrix SW turn off.                                                            | _                         | 150    | _    | °C    | *5<br>*6 |  |  |

| Со               | Constant Voltage Source (LDO)                                                   |                   |                                                                                                                                |                           |        |      |       |          |  |  |

|                  | Ripple rejection ratio (1)                                                      | PSL11             | $V_{CC} = 3.6 \text{ V} + 0.3 \text{ V[p-p]}$<br>f = 1  kHz<br>$I_{LDO} = -15 \text{ mA}$<br>$PSL11 = 20log(acV_{LDO} / 0.3)$  | _                         | - 50   | 40 — | dB    | *6       |  |  |

|                  | Ripple rejection ratio (2) PSL12                                                |                   | $V_{CC} = 3.6 \text{ V} + 0.3 \text{ V[p-p]}$<br>f = 10  kHz<br>$I_{LDO} = -15 \text{ mA}$<br>$PSL12 = 20log(acV_{LDO} / 0.3)$ | _                         | - 40   | _    | dB    | *6       |  |  |

|                  | Short-circuit protection current                                                | I <sub>PT1</sub>  | V <sub>LDO</sub> = 0 V                                                                                                         | _                         | 40     | _    | mA    | *6       |  |  |

| I <sup>2</sup> C | bus (Internal I/O stage chara                                                   | acteristics)      | (Continued)                                                                                                                    |                           |        |      |       |          |  |  |

|                  | Hysteresis of Schmitt trigger input 1                                           | $V_{hys1}$        | V <sub>DD</sub> > 2 V,<br>Hysteresis of SDA, SCL                                                                               | 0.05<br>× V <sub>DD</sub> | _      | _    | V     | *7<br>*8 |  |  |

|                  | Hysteresis of Schmitt trigger input 2                                           | V <sub>hys2</sub> | V <sub>DD</sub> < 2 V,<br>Hysteresis of SDA, SCL                                                                               | 0.1 × V <sub>DD</sub>     | _      | _    | ٧     | *7<br>*8 |  |  |

|                  | Output fall time from V <sub>IHMIN</sub> to V <sub>ILMAX</sub>                  | t <sub>of</sub>   | Bus capacitance : 10pF to 550pF $I_P \le 20$ mA ( $V_{OLMAX} = 0.4$ V) $I_P$ : Max. sink current                               | _                         |        | 120  | ns    | *7<br>*8 |  |  |

|                  | Pulse width of spikes which must be suppressed by the input filter $t_{\rm SP}$ |                   | _                                                                                                                              | 0                         | _      | 50   | ns    | *7<br>*8 |  |  |

|                  | Capacitance for each I/O pin                                                    | C <sub>i</sub>    | _                                                                                                                              | _                         | -      | 10   | pF    | *7<br>*8 |  |  |

Note: \*5 : Constant current circuit, and Matrix SW turn off and IC reset when TSD operates.

<sup>\*6 :</sup> Typical Design Value

$<sup>^{\</sup>star}7$ : The timing of Fast-mode Plus devices in I<sup>2</sup>C-bus is specified in Page.10. All values referred to  $V_{IHMIN}$  and  $V_{ILMAX}$  level.

<sup>\*8 :</sup> These are values checked by design but not production tested.

**AN32183A**

### **ELECTRICAL CHARACTERISTICS (Continued)**

$V_{\rm CC}$  = 3.6 V,  $V_{\rm DD}$  = 1.85 V

Notes:  $T_a = 25^{\circ}C\pm 2^{\circ}C$  unless otherwise noted.

| Parameter                                                       | Symbol              | Condition                                                      |                       | Limits |      | Unit | Note     |

|-----------------------------------------------------------------|---------------------|----------------------------------------------------------------|-----------------------|--------|------|------|----------|

| Parameter                                                       | Symbol              | Condition                                                      | Min                   | Тур    | Max  | Unit | note     |

| I <sup>2</sup> C bus (Bus line specifications                   | s) (Continue        | e)                                                             |                       |        |      |      |          |

| Hold time<br>(repeated) START<br>condition                      | t <sub>HD:STA</sub> | The first clock pulse is generated after t <sub>HD:STA</sub> . | 0.26                  | _      | _    | μS   | *7<br>*8 |

| Low period of the SCL clock                                     | t <sub>LOW</sub>    | _                                                              | 0.5                   | _      | _    | μS   | *7<br>*8 |

| High period of the SCL clock                                    | t <sub>HIGH</sub>   | _                                                              | 0.26                  | _      |      | μS   | *7<br>*8 |

| Set-up time for a repeat START condition                        | t <sub>su:sta</sub> | _                                                              | 0.26                  | _      | _    | μS   | *7<br>*8 |

| Data hold time                                                  | t <sub>HD:DAT</sub> | _                                                              | 0                     | _      | _    | μS   | *7<br>*8 |

| Data set-up time                                                | t <sub>SU:DAT</sub> | _                                                              | 50                    | _      | _    | ns   | *7<br>*8 |

| Rise time of both SDA and SCL signals                           | t <sub>r</sub>      | _                                                              | _                     | _      | 120  | ns   | *7<br>*8 |

| Fall time of both SDA and SCL signals                           | t <sub>f</sub>      | _                                                              |                       | _      | 120  | ns   | *7<br>*8 |

| Set-up time of STOP condition                                   | t <sub>su:sto</sub> | _                                                              | 0.26                  | _      | _    | μЅ   | *7<br>*8 |

| Bus free time between STOP and START condition                  | t <sub>BUF</sub>    | _                                                              | 0.5                   | _      | _    | μS   | *7<br>*8 |

| Capacitive load for each bus line                               | C <sub>b</sub>      | _                                                              | _                     | _      | 550  | pF   | *7<br>*8 |

| Data valid time                                                 | t <sub>VD:DAT</sub> | _                                                              | _                     | _      | 0.45 | μS   | *7<br>*8 |

| Data valid acknowledge                                          | t <sub>VD:ACK</sub> | _                                                              | _                     | _      | 0.45 | μS   | *7<br>*8 |

| Noise margin at the Low-<br>level for each connected<br>device  | V <sub>nL</sub>     | _                                                              | 0.1 × V <sub>DD</sub> | _      | _    | _ v  |          |

| Noise margin at the High-<br>level for each connected<br>device | $V_{nH}$            | _                                                              | 0.2 × V <sub>DD</sub> | _      |      | V    | *7<br>*8 |

Note: \*7 : The timing of Fast-mode Plus devices in I $^2$ C-bus is specified in Page 10. All values referred to  $V_{IHMIN}$  and  $V_{ILMAX}$  level.

<sup>\*8 :</sup> These are values checked by design but not production tested.

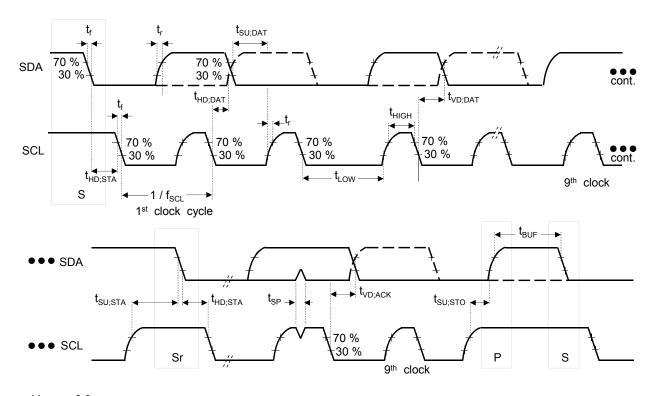

### **ELECTRICAL CHARACTERISTICS (Continued)**

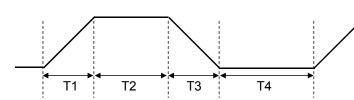

$V_{ILMAX} = 0.3_{VDD}$  $V_{IHMIN} = 0.7_{VDD}$

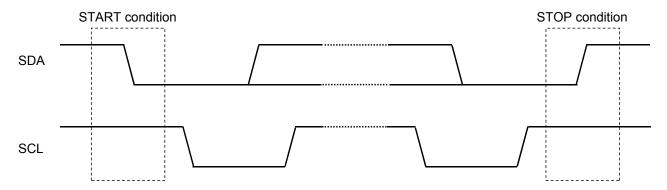

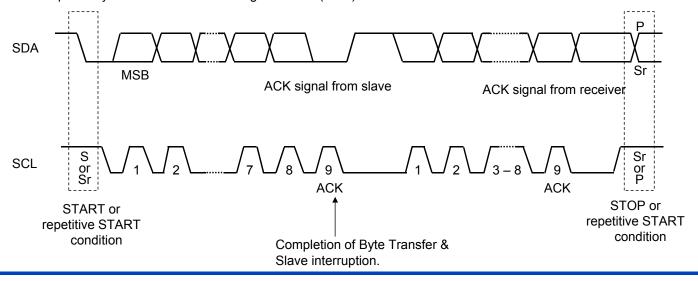

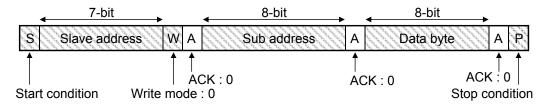

S: START condition

Sr: Repetitive START condition

P: STOP condition

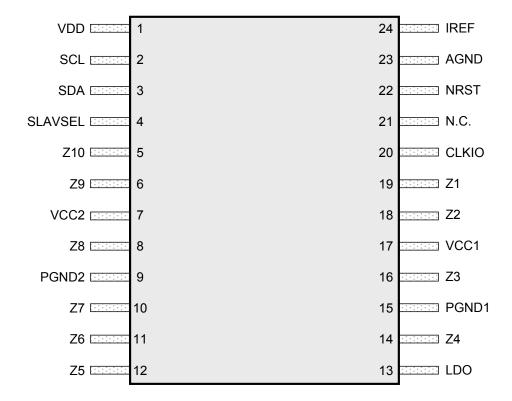

#### PIN CONFIGURATION

#### **TOP VIEW**

## **AN32183A**

#### **PIN FUNCTIONS**

| Pin No. | Pin name       | Туре         | Description                                                                            | Pin processing at unused         |

|---------|----------------|--------------|----------------------------------------------------------------------------------------|----------------------------------|

| 1       | VDD            | Power supply | Power supply for I <sup>2</sup> C interface                                            | (Required pin)                   |

| 2       | SCL            | Input        | Clock input pin for I <sup>2</sup> C interface                                         | (Required pin)                   |

| 3       | SDA            | Input/Output | Data input / output pin for I <sup>2</sup> C interface                                 | (Required pin)                   |

| 4       | SLAVSEL        | Input        | Slave address selection pin for I <sup>2</sup> C interface                             | GND or VCC or<br>SCL or SDA      |

| 5       | Z10            | Output       | Constant current circuit, PWM control output pin, Control switch pin for matrix driver | Open                             |

| 6       | <b>Z</b> 9     | Output       | Constant current circuit, PWM control output pin, Control switch pin for matrix driver | Open                             |

| 7<br>17 | VCC2<br>VCC1   | Power supply | Power supply for matrix driver, Internal reference circuit                             | Battery or External power supply |

| 8       | Z8             | Output       | Constant current circuit, PWM control output pin, Control switch pin for matrix driver | Open                             |

| 9<br>15 | PGND2<br>PGND1 | Ground       | Power Ground pin                                                                       | (Required pin)                   |

| 10      | Z7             | Output       | Constant current circuit, PWM control output pin, Control switch pin for matrix driver | Open                             |

| 11      | Z6             | Output       | Constant current circuit, PWM control output pin, Control switch pin for matrix driver | Open                             |

| 12      | Z5             | Output       | Constant current circuit, PWM control output pin, Control switch pin for matrix driver | Open                             |

| 13      | LDO            | Output       | LDO output pin                                                                         | (Required pin)                   |

| 14      | Z4             | Output       | Constant current circuit, PWM control output pin, Control switch pin for matrix driver | Open                             |

| 16      | Z3             | Output       | Constant current circuit, PWM control output pin, Control switch pin for matrix driver | Open                             |

| 18      | Z2             | Output       | Constant current circuit, PWM control output pin, Control switch pin for matrix driver | Open                             |

| 19      | Z1             | Output       | Constant current circuit, PWM control output pin, Control switch pin for matrix driver | Open                             |

| 20      | CLKIO          | Input/Output | Reference clock input output / Music Input pin                                         | Open                             |

| 21      | _              | _            | N.C                                                                                    | _                                |

| 22      | NRST           | Input        | Reset input pin                                                                        | (Required pin)                   |

| 23      | AGND           | Ground       | Ground pin                                                                             | (Required pin)                   |

| 24      | IREF           | Output       | Resistor connection pin for constant current setup                                     | (Required pin)                   |

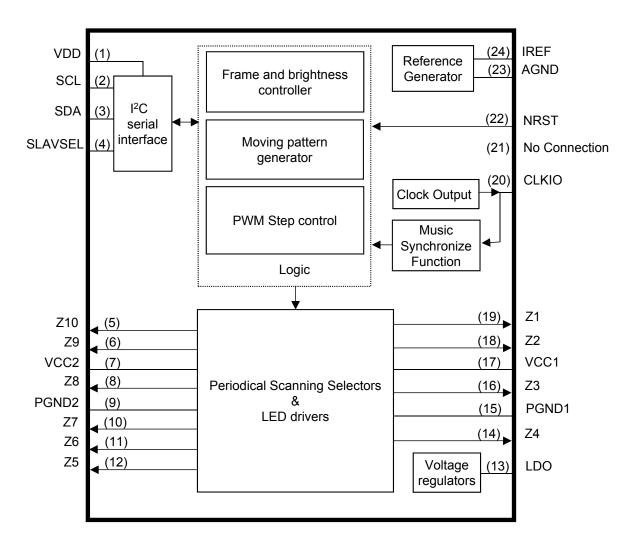

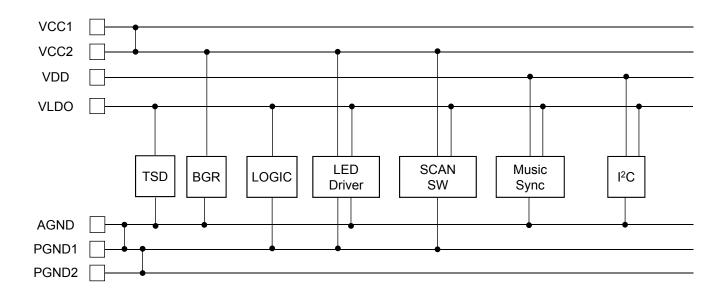

#### **FUNCTIONAL BLOCK DIAGRAM**

Notes: This block diagram is for explaining functions. Part of the block diagram may be omitted, or it may be simplified.

#### **OPERATION**

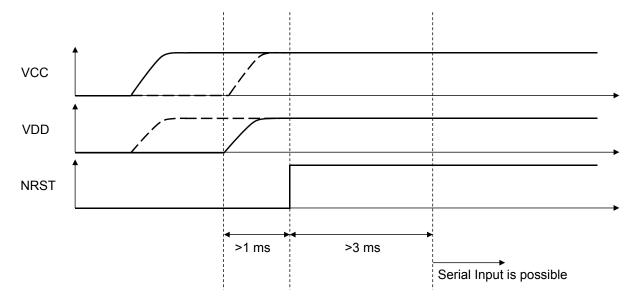

#### 1. Power Supply Sequence

#### 1.1 Power ON

Note: For the Startup Timing of VCC and VDD, it is possible to be changed.

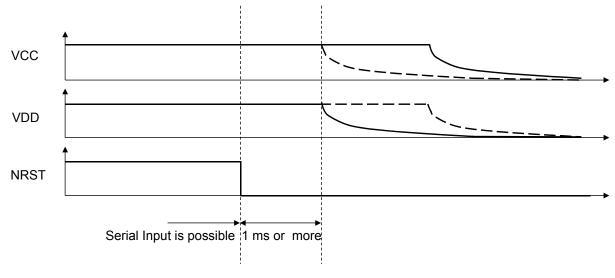

#### 1.2 Power OFF

Note: For the Shut down Timing of VCC and VDD, it is possible to be changed.

### **AN32183A**

### **OPERATION (Continued)**

#### 2. Register Map

| ADDD | Register | Default | DAM |       |       |       | DA               | TA      |           |        |        |

|------|----------|---------|-----|-------|-------|-------|------------------|---------|-----------|--------|--------|

| ADDR | Name     | Default | R/W | D7    | D6    | D5    | D4               | D3      | D2        | D1     | D0     |

| 01h  | RST      | 00h     | W   |       |       |       |                  |         |           | RAMRST | SRST   |

| 02h  | POWERCNT | 00h     | R/W |       |       |       |                  |         |           |        | OSCEN  |

| 03h  | reserved |         |     |       |       |       |                  |         |           |        |        |

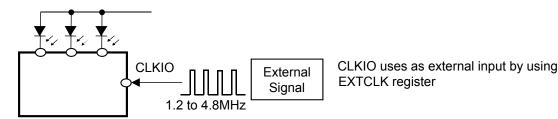

| 04h  | OPTION   | 00h     | R/W |       |       |       |                  | ZPDEN   | MLDACT    | CLKOUT | EXTCLK |

| 05h  | MTXON    | 1Eh     | R/W |       |       |       | IMAX<br>Reserved |         | IMAX[2:0] |        | MTXON  |

| 06h  | PWMEN1   | 00h     | R/W | PWMA8 | PWMA7 | PWMA6 | PWMA5            | PWMA4   | PWMA3     | PWMA2  | PWMA1  |

| 07h  | PWMEN2   | 00h     | R/W | PWMB7 | PWMB6 | PWMB5 | PWMB4            | PWMB3   | PWMB2     | PWMB1  | PWMA9  |

| 08h  | PWMEN3   | 00h     | R/W | PWMC6 | PWMC5 | PWMC4 | PWMC3            | PWMC2   | PWMC1     | PWMB9  | PWMB8  |

| 09h  | PWMEN4   | 00h     | R/W | PWMD5 | PWMD4 | PWMD3 | PWMD2            | PWMD1   | PWMC9     | PWMC8  | PWMC7  |

| 0Ah  | PWMEN5   | 00h     | R/W | PWME4 | PWME3 | PWME2 | PWME1            | PWMD9   | PWMD8     | PWMD7  | PWMD6  |

| 0Bh  | PWMEN6   | 00h     | R/W | PWMF3 | PWMF2 | PWMF1 | PWME9            | PWME8   | PWME7     | PWME6  | PWME5  |

| 0Ch  | PWMEN7   | 00h     | R/W | PWMG2 | PWMG1 | PWMF9 | PWMF8            | PWMF7   | PWMF6     | PWMF5  | PWMF4  |

| 0Dh  | PWMEN8   | 00h     | R/W | PWMH1 | PWMG9 | PWMG8 | PWMG7            | PWMG6   | PWMG5     | PWMG4  | PWMG3  |

| 0Eh  | PWMEN9   | 00h     | R/W | PWMH9 | PWMH8 | PWMH7 | PWMH6            | PWMH5   | PWMH4     | PWMH3  | PWMH2  |

| 0Fh  | PWMEN10  | 00h     | R/W | PWMI8 | PWMI7 | PWMI6 | PWMI5            | PWMI4   | PWMI3     | PWMI2  | PWMI1  |

| 10h  | PWMEN11  | 00h     | R/W |       |       |       |                  |         |           |        | PWMI9  |

| 11h  | MLDEN1   | 00h     | R/W | MLDA8 | MLDA7 | MLDA6 | MLDA5            | MLDA4   | MLDA3     | MLDA2  | MLDA1  |

| 12h  | MLDEN2   | 00h     | R/W | MLDB7 | MLDB6 | MLDB5 | MLDB4            | MLDB3   | MLDB2     | MLDB1  | MLDA9  |

| 13h  | MLDEN3   | 00h     | R/W | MLDC6 | MLDC5 | MLDC4 | MLDC3            | MLDC2   | MLDC1     | MLDB9  | MLDB8  |

| 14h  | MLDEN4   | 00h     | R/W | MLDD5 | MLDD4 | MLDD3 | MLDD2            | MLDD1   | MLDC9     | MLDC8  | MLDC7  |

| 15h  | MLDEN5   | 00h     | R/W | MLDE4 | MLDE3 | MLDE2 | MLDE1            | MLDD9   | MLDD8     | MLDD7  | MLDD6  |

| 16h  | MLDEN6   | 00h     | R/W | MLDF3 | MLDF2 | MLDF1 | MLDE9            | MLDE8   | MLDE7     | MLDE6  | MLDE5  |

| 17h  | MLDEN7   | 00h     | R/W | MLDG2 | MLDG1 | MLDF9 | MLDF8            | MLDF7   | MLDF6     | MLDF5  | MLDF4  |

| 18h  | MLDEN8   | 00h     | R/W | MLDH1 | MLDG9 | MLDG8 | MLDG7            | MLDG6   | MLDG5     | MLDG4  | MLDG3  |

| 19h  | MLDEN9   | 00h     | R/W | MLDH9 | MLDH8 | MLDH7 | MLDH6            | MLDH5   | MLDH4     | MLDH3  | MLDH2  |

| 1Ah  | MLDEN10  | 00h     | R/W | MLDI8 | MLDI7 | MLDI6 | MLDI5            | MLDI4   | MLDI3     | MLDI2  | MLDI1  |

| 1Bh  | MLDEN11  | 00h     | R/W |       |       |       |                  |         |           |        | MLDI9  |

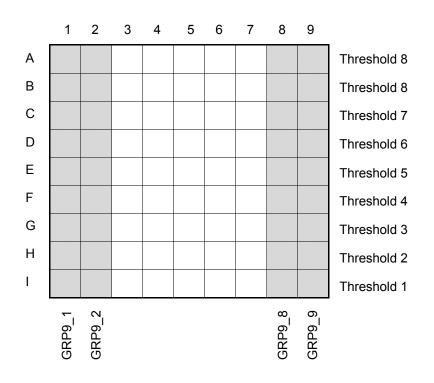

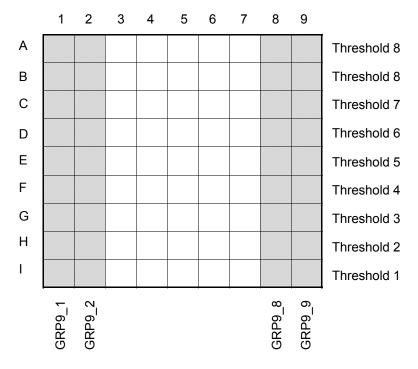

| 2Ah  | MLDMODE1 | 00h     | R/W |       |       |       |                  | GRP9_9  | GRP9_8    | GRP9_2 | GRP9_1 |

| 2Bh  | THOLD    | 00h     | R/W |       |       |       | THOL             | .D[7:0] |           |        |        |

Note: "Reserved" registers and data bits indicated by "--" cannot be accessed. "Reserved" registers are not used.

For data bits indicated by "--" in other registers except from "reversed" registers, will return "zero" value if these bits are read.

Writing to these bits will be ignored. IMAX Reserved will give default value [1].

### **AN32183A**

### **OPERATION (Continued)**

### 2. Register Map (Continued)

| ADDD | Register   | Default | DAM | DATA  D7 D6 D5 D4 D3 D2 D1 D0                                                                                                                         |  |       |                  |                |          |         |          |  |

|------|------------|---------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|-------|------------------|----------------|----------|---------|----------|--|

| ADDR | Name       | Default | R/W | D7         D6         D5         D4         D3         D2         D1         D0             X6         X5         X4         X3         X2         X1 |  |       |                  |                |          |         |          |  |

| 2Ch  | CONSTX6_1  | 00h     | R/W |                                                                                                                                                       |  | X6    | X5               | X4             | Х3       | X2      | X1       |  |

| 2Dh  | CONSTX10_7 | 00h     | R/W |                                                                                                                                                       |  |       |                  | X10            | X9       | X8      | X7       |  |

| 2Eh  | CONSTY6_1  | 00h     | R/W |                                                                                                                                                       |  | Y6    | Y5               | Y4             | Y3       | Y2      | Y1       |  |

| 2Fh  | CONSTY9_7  | 00h     | R/W |                                                                                                                                                       |  |       |                  |                | Y9       | Y8      | Y7       |  |

| 30h  | MASKY6_1   | 00h     | R/W |                                                                                                                                                       |  | Y6MSK | Y5MSK            | Y4MSK          | Y3MSK    | Y2MSK   | Y1MSK    |  |

| 31h  | MASKY9_7   | 00h     | R/W |                                                                                                                                                       |  |       |                  |                | Y9MSK    | Y8MSK   | Y7MSK    |  |

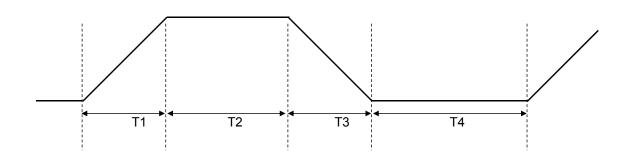

| 32h  | SLPTIME    | 00h     | R/W |                                                                                                                                                       |  |       | FADTIM           | SLOPEE         | XTL[1:0] | SLOPEE  | XTH[1:0] |  |

| 33h  | MLDCOM     | 03h     | R/W |                                                                                                                                                       |  |       |                  | 1              | М        | LDCOM[2 | :0]      |  |

| 34h  | reserved   |         |     |                                                                                                                                                       |  |       |                  |                |          |         |          |  |

| 35h  | reserved   |         |     |                                                                                                                                                       |  |       |                  | 1              |          |         |          |  |

| 36h  | SCANSET    | 08h     | R/W | SCANSET[3:0]                                                                                                                                          |  |       |                  |                |          |         |          |  |

| 40h  | DTA1       | 00h     | R/W | DTA1[7:0]                                                                                                                                             |  |       |                  |                |          |         |          |  |

| 41h  | DTA2       | 00h     | R/W | DTA2[7:0]                                                                                                                                             |  |       |                  |                |          |         |          |  |

| 42h  | DTA3       | 00h     | R/W |                                                                                                                                                       |  |       | DTA              | 3[7:0]         |          |         |          |  |

| 43h  | DTA4       | 00h     | R/W |                                                                                                                                                       |  |       | DTA              | <b>4</b> [7:0] |          |         |          |  |

| 44h  | DTA5       | 00h     | R/W |                                                                                                                                                       |  |       | DTA              | 5[7:0]         |          |         |          |  |

| 45h  | DTA6       | 00h     | R/W |                                                                                                                                                       |  |       | DTA              | 6[7:0]         |          |         |          |  |

| 46h  | DTA7       | 00h     | R/W |                                                                                                                                                       |  |       | DTA              | 7[7:0]         |          |         |          |  |

| 47h  | DTA8       | 00h     | R/W |                                                                                                                                                       |  |       | DTA              | 3[7:0]         |          |         |          |  |

| 48h  | DTA9       | 00h     | R/W |                                                                                                                                                       |  |       | DTA              | 9[7:0]         |          |         |          |  |

| 49h  | DTB1       | 00h     | R/W |                                                                                                                                                       |  |       | DTB <sup>2</sup> | 1[7:0]         |          |         |          |  |

| 4Ah  | DTB2       | 00h     | R/W |                                                                                                                                                       |  |       | DTB              | 2[7:0]         |          |         |          |  |

| 4Bh  | DTB3       | 00h     | R/W |                                                                                                                                                       |  |       | DTB:             | 3[7:0]         |          |         |          |  |

| 4Ch  | DTB4       | 00h     | R/W | DTB4[7:0]                                                                                                                                             |  |       |                  |                |          |         |          |  |

| 4Dh  | DTB5       | 00h     | R/W | V DTB5[7:0]                                                                                                                                           |  |       |                  |                |          |         |          |  |

| 4Eh  | DTB6       | 00h     | R/W |                                                                                                                                                       |  |       | DTB              | 6[7:0]         |          |         |          |  |

| 4Fh  | DTB7       | 00h     | R/W | W DTB7[7:0]                                                                                                                                           |  |       |                  |                |          |         |          |  |

| 50h  | DTB8       | 00h     | R/W | DTB8[7:0]                                                                                                                                             |  |       |                  |                |          |         |          |  |

| 51h  | DTB9       | 00h     | R/W | /W DTB9[7:0]                                                                                                                                          |  |       |                  |                |          |         |          |  |

Note: "Reserved" registers and data bits indicated by "--" cannot be accessed. "Reserved" registers are not used.

For data bits indicated by "--" in other registers except from "Reserved" registers, will return "zero" value if these bits are read.

Writing to these bits will be ignored.

## **AN32183A**

# **Panasonic**

### **OPERATION (Continued)**

### 2. Register Map (Continued)

| 4000 | Register | D-614   | DAM  | DATA  D7 D6 D5 D4 D3 D2 D1 D0 |    |    |      |        |    |    |    |  |

|------|----------|---------|------|-------------------------------|----|----|------|--------|----|----|----|--|

| ADDR | Name     | Default | R/VV | D7                            | D6 | D5 | D4   | D3     | D2 | D1 | D0 |  |

| 52h  | DTC1     | 00h     | R/W  |                               | •  |    | DTC  | 1[7:0] |    | •  |    |  |

| 53h  | DTC2     | 00h     | R/W  |                               |    |    | DTC  | 2[7:0] |    |    |    |  |

| 54h  | DTC3     | 00h     | R/W  |                               |    |    | DTC  | 3[7:0] |    |    |    |  |

| 55h  | DTC4     | 00h     | R/W  |                               |    |    | DTC  | 4[7:0] |    |    |    |  |

| 56h  | DTC5     | 00h     | R/W  |                               |    |    | DTC  | 5[7:0] |    |    |    |  |

| 57h  | DTC6     | 00h     | R/W  |                               |    |    | DTC  | 6[7:0] |    |    |    |  |

| 58h  | DTC7     | 00h     | R/W  |                               |    |    | DTC  | 7[7:0] |    |    |    |  |

| 59h  | DTC8     | 00h     | R/W  |                               |    |    | DTC  | 8[7:0] |    |    |    |  |

| 5Ah  | DTC9     | 00h     | R/W  |                               |    |    | DTC  | 9[7:0] |    |    |    |  |

| 5Bh  | DTD1     | 00h     | R/W  |                               |    |    | DTD  | 1[7:0] |    |    |    |  |

| 5Ch  | DTD2     | 00h     | R/W  |                               |    |    | DTD  | 2[7:0] |    |    |    |  |

| 5Dh  | DTD3     | 00h     | R/W  |                               |    |    | DTD: | 3[7:0] |    |    |    |  |

| 5Eh  | DTD4     | 00h     | R/W  |                               |    |    | DTD4 | 4[7:0] |    |    |    |  |

| 5Fh  | DTD5     | 00h     | R/W  |                               |    |    | DTD  | 5[7:0] |    |    |    |  |

| 60h  | DTD6     | 00h     | R/W  |                               |    |    | DTD  | 6[7:0] |    |    |    |  |

| 61h  | DTD7     | 00h     | R/W  |                               |    |    | DTD  | 7[7:0] |    |    |    |  |

| 62h  | DTD8     | 00h     | R/W  |                               |    |    | DTD  | 8[7:0] |    |    |    |  |

| 63h  | DTD9     | 00h     | R/W  |                               |    |    | DTD  | 9[7:0] |    |    |    |  |

| 64h  | DTE1     | 00h     | R/W  |                               |    |    | DTE  | 1[7:0] |    |    |    |  |

| 65h  | DTE2     | 00h     | R/W  |                               |    |    | DTE  | 2[7:0] |    |    |    |  |

| 66h  | DTE3     | 00h     | R/W  |                               |    |    | DTE: | 3[7:0] |    |    |    |  |

| 67h  | DTE4     | 00h     | R/W  |                               |    |    | DTE  | 4[7:0] |    |    |    |  |

| 68h  | DTE5     | 00h     | R/W  |                               |    |    | DTE  | 5[7:0] |    |    |    |  |

| 69h  | DTE6     | 00h     | R/W  |                               |    |    | DTE  | 6[7:0] |    |    |    |  |

| 6Ah  | DTE7     | 00h     | R/W  |                               |    |    | DTE  | 7[7:0] |    |    |    |  |

| 6Bh  | DTE8     | 00h     | R/W  |                               |    |    | DTE  | 3[7:0] |    |    |    |  |

| 6Ch  | DTE9     | 00h     | R/W  |                               |    |    | DTE  | 9[7:0] |    |    |    |  |

| 6Dh  | DTF1     | 00h     | R/W  |                               |    |    | DTF  | 1[7:0] |    |    |    |  |

| 6Eh  | DTF2     | 00h     | R/W  |                               |    |    | DTF2 | 2[7:0] |    |    |    |  |

## **AN32183A**

# **Panasonic**

### **OPERATION (Continued)**

### 2. Register Map (Continued)

| ADDD | Register | Defects | DAM | DATA D7 D6 D5 D4 D3 D2 D1 D0 |    |    |      |        |    |    |    |  |

|------|----------|---------|-----|------------------------------|----|----|------|--------|----|----|----|--|

| ADDR | Name     | Default | R/W | D7                           | D6 | D5 | D4   | D3     | D2 | D1 | D0 |  |

| 6Fh  | DTF3     | 00h     | R/W |                              | •  |    | DTF  | 3[7:0] | •  | •  |    |  |

| 70h  | DTF4     | 00h     | R/W |                              |    |    | DTF4 | 4[7:0] |    |    |    |  |

| 71h  | DTF5     | 00h     | R/W |                              |    |    | DTF  | 5[7:0] |    |    |    |  |

| 72h  | DTF6     | 00h     | R/W |                              |    |    | DTF  | 6[7:0] |    |    |    |  |

| 73h  | DTF7     | 00h     | R/W |                              |    |    | DTF  | 7[7:0] |    |    |    |  |

| 74h  | DTF8     | 00h     | R/W |                              |    |    | DTF8 | 3[7:0] |    |    |    |  |

| 75h  | DTF9     | 00h     | R/W |                              |    |    | DTF  | 9[7:0] |    |    |    |  |

| 76h  | DTG1     | 00h     | R/W |                              |    |    | DTG  | 1[7:0] |    |    |    |  |

| 77h  | DTG2     | 00h     | R/W |                              |    |    | DTG  | 2[7:0] |    |    |    |  |

| 78h  | DTG3     | 00h     | R/W |                              |    |    | DTG  | 3[7:0] |    |    |    |  |

| 79h  | DTG4     | 00h     | R/W |                              |    |    | DTG  | 4[7:0] |    |    |    |  |

| 7Ah  | DTG5     | 00h     | R/W |                              |    |    | DTG: | 5[7:0] |    |    |    |  |

| 7Bh  | DTG6     | 00h     | R/W |                              |    |    | DTG  | 6[7:0] |    |    |    |  |

| 7Ch  | DTG7     | 00h     | R/W |                              |    |    | DTG  | 7[7:0] |    |    |    |  |

| 7Dh  | DTG8     | 00h     | R/W |                              |    |    | DTG  | 8[7:0] |    |    |    |  |

| 7Eh  | DTG9     | 00h     | R/W |                              |    |    | DTG  | 9[7:0] |    |    |    |  |

| 7Fh  | DTH1     | 00h     | R/W |                              |    |    | DTH  | 1[7:0] |    |    |    |  |

| 80h  | DTH2     | 00h     | R/W |                              |    |    | DTH  | 2[7:0] |    |    |    |  |

| 81h  | DTH3     | 00h     | R/W |                              |    |    | DTH  | 3[7:0] |    |    |    |  |

| 82h  | DTH4     | 00h     | R/W |                              |    |    | DTH  | 4[7:0] |    |    |    |  |

| 83h  | DTH5     | 00h     | R/W |                              |    |    | DTH: | 5[7:0] |    |    |    |  |

| 84h  | DTH6     | 00h     | R/W |                              |    |    | DTH  | 6[7:0] |    |    |    |  |

| 85h  | DTH7     | 00h     | R/W |                              |    |    | DTH  | 7[7:0] |    |    |    |  |

| 86h  | DTH8     | 00h     | R/W |                              |    |    | DTH  | 8[7:0] |    |    |    |  |

| 87h  | DTH9     | 00h     | R/W |                              |    |    | DTH  | 9[7:0] |    |    |    |  |

| 88h  | DTI1     | 00h     | R/W |                              |    |    | DTI1 | [7:0]  |    |    |    |  |

| 89h  | DTI2     | 00h     | R/W |                              |    |    | DTI2 | 2[7:0] |    |    |    |  |

| 8Ah  | DTI3     | 00h     | R/W |                              |    |    | DTI3 | 3[7:0] |    |    |    |  |

| 8Bh  | DTI4     | 00h     | R/W |                              |    |    | DTI4 | [7:0]  |    |    |    |  |

### **AN32183A**

### **OPERATION (Continued)**

### 2. Register Map (Continued)

| 4000 | Register | D. C. 11 | Day |                                                                                                              |      |         | DA   | ΛTA    |                      |                      |        |  |  |    |

|------|----------|----------|-----|--------------------------------------------------------------------------------------------------------------|------|---------|------|--------|----------------------|----------------------|--------|--|--|----|

| ADDR | Name     | Default  | R/W | D7         D6         D5         D4         D3         D2         D1           DTI5[7:0]           DTI6[7:0] |      |         |      |        |                      | D1                   | D0     |  |  |    |

| 8Ch  | DTI5     | 00h      | R/W |                                                                                                              |      |         | DTI  | 5[7:0] |                      |                      |        |  |  |    |

| 8Dh  | DTI6     | 00h      | R/W |                                                                                                              |      |         | DTI  | 6[7:0] |                      |                      |        |  |  |    |

| 8Eh  | DTI7     | 00h      | R/W |                                                                                                              |      |         | DTI  | 7[7:0] |                      |                      |        |  |  |    |

| 8Fh  | DTI8     | 00h      | R/W |                                                                                                              |      |         | DTI8 | 3[7:0] |                      |                      |        |  |  |    |

| 90h  | DTI9     | 00h      | R/W |                                                                                                              |      |         | DTIS | 9[7:0] |                      |                      |        |  |  |    |

| 91h  | A1       | 00h      | R/W |                                                                                                              | BRTA | 1[3:0]  |      |        |                      | SDTA1[2:0            | )]     |  |  |    |

| 92h  | A2       | 00h      | R/W |                                                                                                              | BRTA | A2[3:0] |      |        |                      | SDTA2[2:0            | )]     |  |  |    |

| 93h  | A3       | 00h      | R/W |                                                                                                              | BRTA | \3[3:0] |      |        |                      | SDTA3[2:0            | )]     |  |  |    |

| 94h  | A4       | 00h      | R/W |                                                                                                              | BRTA | 4[3:0]  |      |        |                      | SDTA4[2:0            | )]     |  |  |    |

| 95h  | A5       | 00h      | R/W | BRTA5[3:0]                                                                                                   |      |         |      |        | SDTA5[2:0]           |                      |        |  |  |    |

| 96h  | A6       | 00h      | R/W | BRTA6[3:0]                                                                                                   |      |         |      |        |                      | SDTA6[2:0            | <br>)] |  |  |    |

| 97h  | A7       | 00h      | R/W | BRTA7[3:0]                                                                                                   |      |         |      |        |                      | - SDTA7[2:0]         |        |  |  |    |

| 98h  | A8       | 00h      | R/W | BRTA8[3:0]                                                                                                   |      |         |      |        |                      | SDTA8[2:0]           |        |  |  |    |

| 99h  | A9       | 00h      | R/W | BRTA9[3:0]                                                                                                   |      |         |      |        |                      | SDTA9[2:0            | )]     |  |  |    |

| 9Ah  | B1       | 00h      | R/W | BRTA9[3:0]<br>BRTB1[3:0]                                                                                     |      |         |      |        |                      | BRTB1[3:0] SDTB1[2:0 |        |  |  | )] |

| 9Bh  | B2       | 00h      | R/W | BRTB1[3:0]<br>BRTB2[3:0]                                                                                     |      |         |      |        | BRTB2[3:0] SDTB2[2:0 |                      |        |  |  |    |

| 9Ch  | В3       | 00h      | R/W |                                                                                                              | BRTE | 33[3:0] |      |        |                      | SDTB3[2:0            | )]     |  |  |    |

| 9Dh  | B4       | 00h      | R/W |                                                                                                              | BRTE | 34[3:0] |      |        |                      | SDTB4[2:0            | )]     |  |  |    |

| 9Eh  | B5       | 00h      | R/W |                                                                                                              | BRTE | 35[3:0] |      |        |                      | SDTB5[2:0            | )]     |  |  |    |

| 9Fh  | B6       | 00h      | R/W |                                                                                                              | BRTE | 36[3:0] |      |        |                      | SDTB6[2:0            | )]     |  |  |    |

| A0h  | B7       | 00h      | R/W |                                                                                                              | BRTE | 37[3:0] |      |        |                      | SDTB7[2:0            | )]     |  |  |    |

| A1h  | B8       | 00h      | R/W |                                                                                                              | BRTE | 38[3:0] |      |        |                      | SDTB8[2:0            | )]     |  |  |    |

| A2h  | B9       | 00h      | R/W |                                                                                                              | BRTE | 39[3:0] |      |        |                      | SDTB9[2:0            | )]     |  |  |    |

| A3h  | C1       | 00h      | R/W | BRTC1[3:0]                                                                                                   |      |         |      |        |                      | SDTC1[2:0            | )]     |  |  |    |

| A4h  | C2       | 00h      | R/W |                                                                                                              |      |         |      |        |                      | SDTC2[2:0            | )]     |  |  |    |

| A5h  | C3       | 00h      | R/W | V BRTC3[3:0] SDTC3[2:0]                                                                                      |      |         |      |        | )]                   |                      |        |  |  |    |

| A6h  | C4       | 00h      | R/W | W BRTC4[3:0] SDTC4[2:0]                                                                                      |      |         |      |        | )]                   |                      |        |  |  |    |

| A7h  | C5       | 00h      | R/W | W BRTC5[3:0] SDTC5[2:0]                                                                                      |      |         |      |        | )]                   |                      |        |  |  |    |

| A8h  | C6       | 00h      | R/W |                                                                                                              | BRTO | 26[3:0] |      |        |                      | SDTC6[2:0            | )]     |  |  |    |

Note: Data bits indicated by "--" cannot be accessed. It will return "zero" value if these bits are read. Writing to these bits will be ignored.

**AN32183A**

### **OPERATION (Continued)**

### 2. Register Map (Continued)

| 4000 | Register | Defects | DAM |                                                                             |            |         |   |    |            |           |    |

|------|----------|---------|-----|-----------------------------------------------------------------------------|------------|---------|---|----|------------|-----------|----|

| ADDR | Name     | Default | R/W | D7         D6         D5         D4           BRTC7[3:0]         BRTC8[3:0] |            |         |   | D3 | D2         | D1        | D0 |

| A9h  | C7       | 00h     | R/W | ,                                                                           | BRTC       | 7[3:0]  | • |    |            | SDTC7[2:0 | D] |

| AAh  | C8       | 00h     | R/W |                                                                             | BRTC       | 28[3:0] |   |    |            | SDTC8[2:0 | 0] |

| ABh  | C9       | 00h     | R/W |                                                                             | BRTC       | 09[3:0] |   |    |            | SDTC9[2:0 | 0] |

| ACh  | D1       | 00h     | R/W |                                                                             | BRTD       | 01[3:0] |   |    |            | SDTD1[2:0 | )] |

| ADh  | D2       | 00h     | R/W |                                                                             | BRTD       | 02[3:0] |   |    |            | SDTD2[2:0 | )] |

| AEh  | D3       | 00h     | R/W |                                                                             | BRTD       | 3[3:0]  |   |    |            | SDTD3[2:0 | 0] |

| AFh  | D4       | 00h     | R/W |                                                                             | BRTD       | 04[3:0] |   |    |            | SDTD4[2:0 | 0] |

| B0h  | D5       | 00h     | R/W |                                                                             | BRTD       | 5[3:0]  |   |    | SDTD5[2:0] |           |    |

| B1h  | D6       | 00h     | R/W | BRTD6[3:0]                                                                  |            |         |   |    |            | SDTD6[2:0 | 0] |

| B2h  | D7       | 00h     | R/W | BRTD7[3:0]                                                                  |            |         |   |    |            | SDTD7[2:0 | 0] |

| B3h  | D8       | 00h     | R/W | BRTD8[3:0]                                                                  |            |         |   |    |            | SDTD8[2:0 | 0] |

| B4h  | D9       | 00h     | R/W |                                                                             | BRTD9[3:0] |         |   |    |            | SDTD9[2:0 | 0] |

| B5h  | E1       | 00h     | R/W |                                                                             | BRTE       | [3:0]   |   |    | SDTE1[2:0] |           | )] |

| B6h  | E2       | 00h     | R/W | BRTE1[3:0]<br>BRTE2[3:0]                                                    |            |         |   |    | SDTE2[2:0] |           |    |

| B7h  | E3       | 00h     | R/W |                                                                             | BRTE       | [3:0]   |   |    | SDTE3[2:0] |           |    |

| B8h  | E4       | 00h     | R/W |                                                                             | BRTE       | 4[3:0]  |   |    | SDTE4[2:0] |           |    |

| B9h  | E5       | 00h     | R/W |                                                                             | BRTE       | 5[3:0]  |   |    |            | SDTE5[2:0 | )] |

| BAh  | E6       | 00h     | R/W |                                                                             | BRTE       | [0:0]   |   |    |            | SDTE6[2:0 | )] |

| BBh  | E7       | 00h     | R/W |                                                                             | BRTE       | 7[3:0]  |   |    |            | SDTE7[2:0 | )] |

| BCh  | E8       | 00h     | R/W |                                                                             | BRTE       | [0:8]8  |   |    |            | SDTE8[2:0 | )] |

| BDh  | E9       | 00h     | R/W |                                                                             | BRTE       | 9[3:0]  |   |    |            | SDTE9[2:0 | )] |

| BEh  | F1       | 00h     | R/W |                                                                             | BRTF       | 1[3:0]  |   |    |            | SDTF1[2:0 | )] |

| BFh  | F2       | 00h     | R/W |                                                                             | BRTF       | 2[3:0]  |   |    |            | SDTF2[2:0 | )] |

| C0h  | F3       | 00h     | R/W |                                                                             | BRTF       | 3[3:0]  |   |    |            | SDTF3[2:0 | )] |

| C1h  | F4       | 00h     | R/W | BRTF4[3:0]                                                                  |            |         |   |    |            | SDTF4[2:0 | )] |

| C2h  | F5       | 00h     | R/W | BRTF5[3:0]                                                                  |            |         |   |    | SDTF5[2:0] |           |    |

| C3h  | F6       | 00h     | R/W | BRTF6[3:0]                                                                  |            |         |   |    | SDTF6[2:0] |           |    |

| C4h  | F7       | 00h     | R/W | BRTF7[3:0]                                                                  |            |         |   |    | SDTF7[2:0] |           |    |

| C5h  | F8       | 00h     | R/W | BRTF8[3:0]                                                                  |            |         |   |    |            | SDTF8[2:0 | )] |

Note: Data bits indicated by "--" cannot be accessed. It will return "zero" value if these bits are read. Writing to these bits will be ignored.

### **AN32183A**

### **OPERATION (Continued)**

### 2. Register Map (Continued)

| 4000 | Register | Defect  | DAM |            |            |         | DA | TA |            |           |    |

|------|----------|---------|-----|------------|------------|---------|----|----|------------|-----------|----|

| ADDR | Name     | Default | R/W | D7         | D6         | D5      | D4 | D3 | D2         | D1        | D0 |

| C6h  | F9       | 00h     | R/W |            | BRTF       | 9[3:0]  | •  |    |            | SDTF9[2:0 | ]  |

| C7h  | G1       | 00h     | R/W |            | BRTG       | 31[3:0] |    |    |            | SDTG1[2:0 | )] |

| C8h  | G2       | 00h     | R/W |            | BRTG       | 62[3:0] |    |    |            | SDTG2[2:0 | )] |

| C9h  | G3       | 00h     | R/W |            | BRTG       | 3[3:0]  |    |    |            | SDTG3[2:0 | )] |

| CAh  | G4       | 00h     | R/W |            | BRTG       | 64[3:0] |    |    |            | SDTG4[2:0 | )] |

| CBh  | G5       | 00h     | R/W |            | BRTG       | 55[3:0] |    |    |            | SDTG5[2:0 | )] |

| CCh  | G6       | 00h     | R/W |            | BRTG       | 6[3:0]  |    |    |            | SDTG6[2:0 | )] |

| CDh  | G7       | 00h     | R/W |            | BRTG       | 37[3:0] |    |    | SDTG7[2:0] |           |    |

| CEh  | G8       | 00h     | R/W | BRTG8[3:0] |            |         |    |    | SDTG8[2:0] |           |    |

| CFh  | G9       | 00h     | R/W | BRTG9[3:0] |            |         |    |    |            | SDTG9[2:0 | )] |

| D0h  | H1       | 00h     | R/W |            | BRTH1[3:0] |         |    |    |            | SDTH1[2:0 | ]  |

| D1h  | H2       | 00h     | R/W |            | BRTH2[3:0] |         |    |    | SDTH2[2:0] |           |    |

| D2h  | Н3       | 00h     | R/W |            | BRTH       | 13[3:0] |    |    | SDTH3[2:0] |           |    |

| D3h  | H4       | 00h     | R/W |            | BRTH       | l4[3:0] |    |    | SDTH4[2:0] |           |    |

| D4h  | H5       | 00h     | R/W |            | BRTH       | l5[3:0] |    |    | SDTH5[2:0] |           |    |

| D5h  | H6       | 00h     | R/W |            | BRTH       | 16[3:0] |    |    | SDTH6[2:0] |           |    |

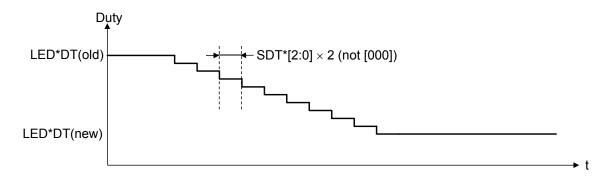

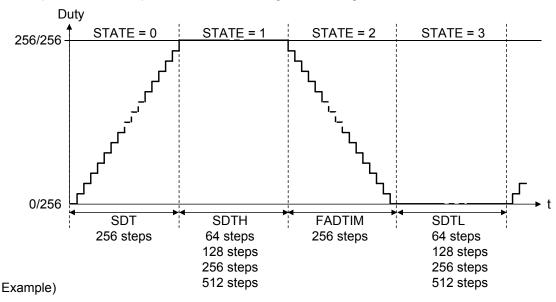

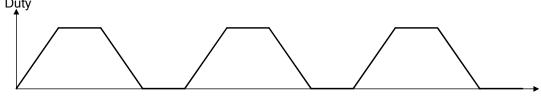

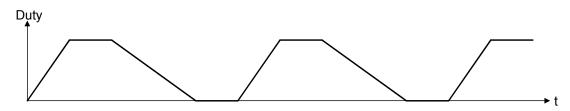

| D6h  | H7       | 00h     | R/W |            | BRTH       | 17[3:0] |    |    |            | SDTH7[2:0 | ]  |