## A SIMPLE ALTERNATIVE TO ANALOG ISOLATION AMPLIFIERS

#### 1. Introduction

Analog circuits sometimes require linear (analog) signal isolation for safety, signal level shifting, and/or ground loop elimination. Linear signal isolation is typically difficult to implement, costly, and often exhibits mediocre performance. While the design community thirsts for a flexible and inexpensive linear isolator solution, it is the analog isolation amplifier (ISOamp) that most often captures the socket.

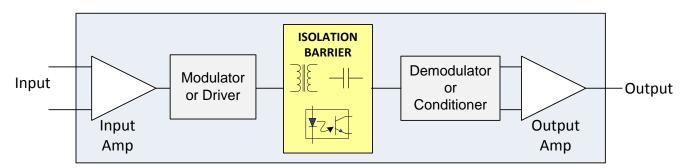

ISOamps are hybridized devices that contain linear input and output circuits separated by an internal isolation barrier. ISOamps typically modulate the linear input signal and transmit the resulting digital information across the isolation barrier to a demodulator where it is converted back to analog (Figure 1). ISOamps typically employ transformers and high-voltage capacitors or optocouplers in the isolation barrier design. While ISOamps are a convenient single-package linear isolation solution, the industry's limited device offerings often force the designer to make difficult trade-offs or add external circuitry for a complete solution. In addition, transformer-based ISOamps are susceptible to signal corruption from external field interference and errors due to poor common-mode transient immunity (CMTI). Optocoupler-based ISOamp versions also often suffer from poor linearity and even worse CMTI. This application note provides insight into a robust linear isolator reference design based on the Silicon Labs Si86xx family of CMOS digital isolators.

Figure 1. ISOamp Block Diagram

## 2. Silicon Labs' ISOlinear Reference Design Overview

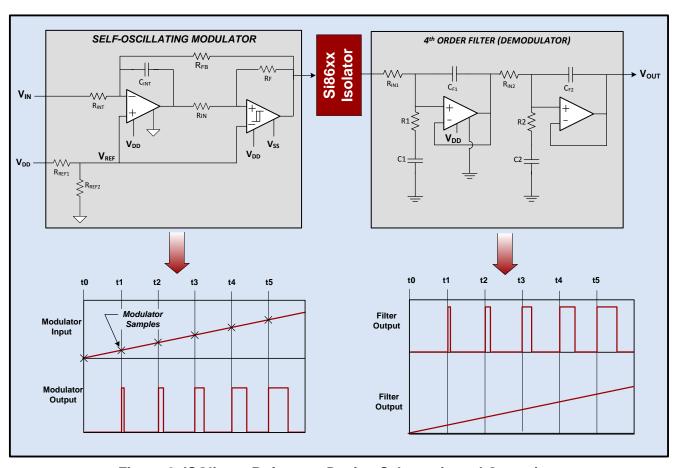

Silicon Labs offers the ISOlinear reference design (Si86IsoLin), a simple linear isolation circuit that is enabled by the Si86xx isolator family, offering industry-leading integration, operating performance, and reliability. The Si86xx isolators are available in UL/VDE/CSA certified isolation ratings of 2.5 or 5 kV. The ISOlinear reference design architecture is shown in Figure 2. A self-oscillating pulse width modulator (PWM) converts the linear input voltage into a series of fixed-frequency, variable duty, cycle pulses in which the width of each pulse is proportional to the sampled input signal amplitude as shown in the waveform diagrams at the bottom of Figure 2. This modulated (digital) signal is passed through the CMOS digital isolator and then restored to analog format by a fourth-order analog filter.

Unlike ISOamps, the ISOlinear reference design gives the designer flexibility to craft low-cost, linear isolators that meet the needs of the end application. For example, the user may elect to relax output ripple requirements to use a lower order (lower cost) output filter; or modulator performance can be enhanced if higher slew rate op-amps and/ or low-delay comparators are used, and so on.

Figure 2. ISOlinear Reference Design Schematic and Operation

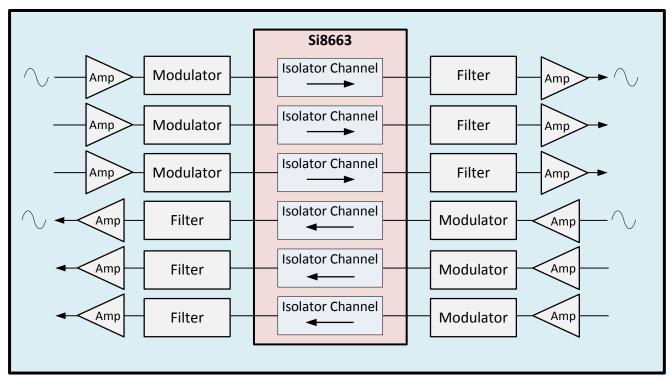

Figure 3. Six-Channel Linear Isolator Block Diagram

In addition, a single Si86xx isolator can host multiple linear isolators by adding additional modulator/filter circuits to a multi-channel Si86xx digital isolator, as shown in Figure 3. In this example, an Si8663 six-channel digital isolator provides three forward and three reverse linear isolator channels, amortizing the isolator across all six channels.

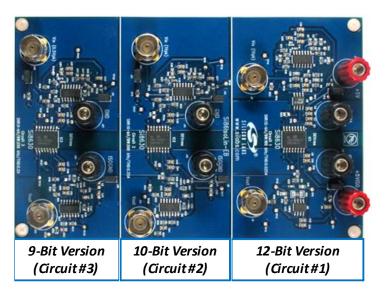

Figure 4. ISOlinear Reference Design Evaluation Board

Figure 4 shows the board included in the ISOlinear reference design kit. This board contains reference design configurations for 9-bit, 10-bit, and 12-bit linear isolator performance, enabling the user to optimize isolator cost/performance trade-offs. (For detailed circuit ISOlinear reference design schematics, see the "ISOlinear Reference Design Users Guide" available for download at <a href="https://www.silabs.com/isolation">www.silabs.com/isolation</a>.)

# **AN614**

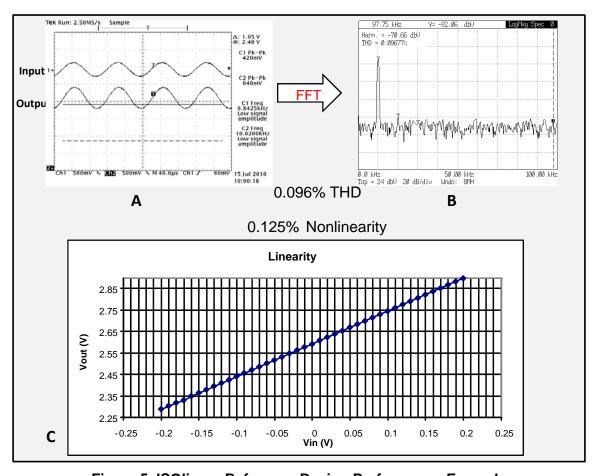

Figure 5 shows total harmonic distortion and nonlinearity measurements from the evaluation board of Figure 4. Waveform A shows the ISOlinear input and output oscilloscope waveforms. The FFT of waveform A reveals a total harmonic distortion (THD) of 0.096% (waveform B). The performance of this design rounds to 12-bit performance with 0.125% nonlinearity. (Note: for more information about the ISOlinear Reference Design, please see application note "AN559: Isolating Analog Signals Using the Si86xx CMOS Isolator Family". This application note provides detailed technical information for modifying the stock ISOlinear reference design, including modulator and filter design equations, design guidelines and more. The ISOlinear Reference Design Kit (Si86IsoLin)is available for purchase at www.silabs.com/isolation.)

Figure 5. ISOlinear Reference Design Performance Example

Table 1 compares the ISOlinear reference design performance against several commercially-available ISOamps. The ISOlinear reference designs offer higher signal-to-noise (sans the 9-bit version); higher CMTI, greater isolation rating flexibility and lower cost compared to competing ISOamps. (Note: a higher cost, faster comparator can be used to reduce nonlinearity to less than 0.1%.)

Table 1. ISOlinear vs. Analog Isolation Amplifiers

| Device                                              | SNR (dB)      | BW (kHz) | Linearity | Isolation<br>Rating (kV) | CMTI<br>(kV/µs)       | Price at 1 kU<br>(\$) |

|-----------------------------------------------------|---------------|----------|-----------|--------------------------|-----------------------|-----------------------|

| Silicon Labs ISOlinear<br>(12-Bit Reference Design) | 71.8          | 100      | 0.125     | 2.5 or 5.0               | 35 (min),<br>50 (typ) | 2.50 to 3.50          |

| Silicon Labs ISOlinear<br>(10-Bit Reference Design) | 62            | 250      | 0.125     | 2.5 or 5.0               | 35 (min),<br>50 (typ) | 2.00 to 2.50          |

| Silicon Labs ISOlinear<br>(9-Bit Reference Design)  | 50.8          | 500      | 0.125     | 2.5 or 5.0               | 35 (min),<br>50 (typ) | 1.75 to 2.25          |

| Avago HCPL-7840                                     | Not Specified | 100      | 0.1       | 2.5                      | 15                    | 3.05                  |

| Avago ACPL-790                                      | 60            | 200      | 0.05      | 5.0                      | 15                    | 6.63                  |

| Avago ACPL-780                                      | Not Specified | 100      | 0.004     | 5.0                      | 15                    | 7.30                  |

| Avago ACPL-C79A                                     | 60            | 200      | 0.05      | 5.0                      | 15                    | 10.00                 |

| Avago ACPL-C790 (Δ Σ)                               | 60            | 200      | 0.05      | 5.0                      | 15                    | 4.65                  |

| TI ISO-124                                          | Not Specified | 50       | 0.01      | 1.5                      | Not Specified         | 8.30                  |

| ADIAD202                                            | Not Specified | 5        | 0.05      | 1.0                      | Not Specified         | 29.82                 |

# 3. Application Examples

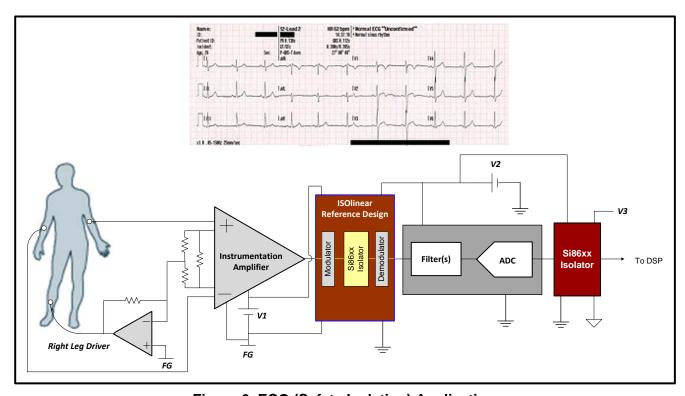

The electrocardiograph (ECG) application shown in Figure 6 requires safety isolation to protect the patient from dangerous leakage currents. Medical applications of this type typically use conductive gels at sensor sites, which lower human body impedance to the extent that a few milliamps of leakage current can cause injury or death. To mitigate this issue, ECGs typically have multiple stages of isolation to prevent downstream leakage current from flowing into the patient. The ECG of Figure 6 shows the patient connected to an instrumentation amplifier powered by a low-current floating supply, V1. The ISOlinear circuit (shown as a functional block in the center of the diagram) galvanically isolates the instrumentation amplifier input side from potential down-stream leakage currents generated by the voltage source, V2. The lower voltage, higher-current DSP circuit is also isolated from the ADC/ filter circuit by a separate Si86xx digital isolator, again to ensure no leakage current paths into the ECG inputs.

Figure 6. ECG (Safety Isolation) Application

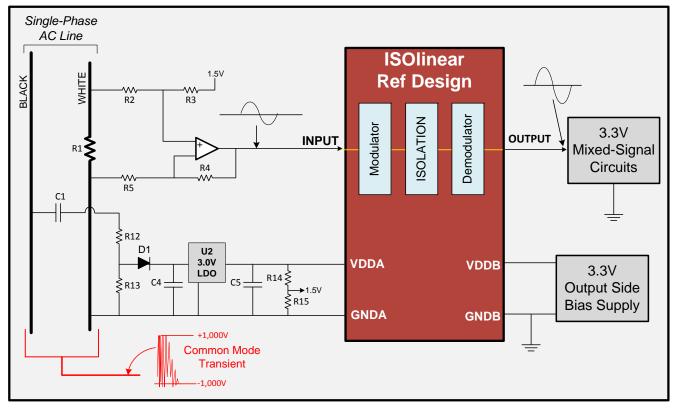

Figure 7. AC Line Current Monitor (Safety Isolation and Level Shift) Application

Figure 7 shows an ac line current monitor that demonstrates both safety isolation and level shifting. Safety isolation galvanically isolates the 110 VAC line from the low-voltage, ground-based circuits. This circuit uses resistive shunt R1 to sense ac current. The high-voltage interface circuit is referenced to the ac neutral (white) wire in a two-wire (non-earth grounded) single-phase ac service.

ISOlinear input-side bias voltage is line-derived and uses a 3 V linear regulator. The low-voltage output-side circuits are biased by a ground-referenced supply. Because there is no earth ground in this system, an ac line perturbation can potentially cause high voltage to appear on the neutral (white) wire. This elevated neutral line common-mode voltage is rejected by the Si86xx isolator's high CMTI of 35 kV/µs minimum, 50 kV/µs typical. For more isolated level shifting application examples, see Silicon Labs Application Note "AN598: High-Speed Level Shifting Using Si8xxx Isolators".

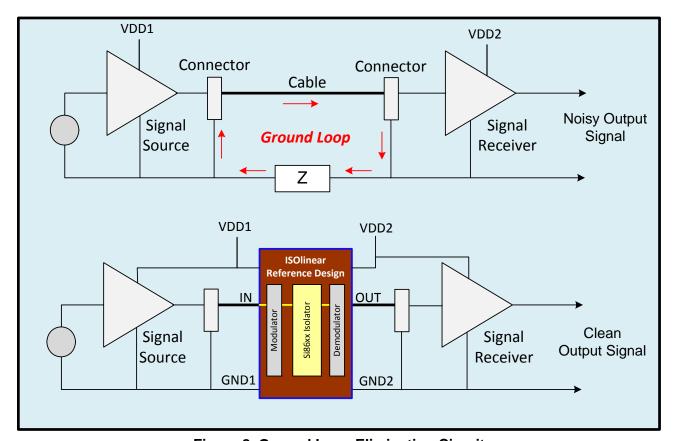

Figure 8 shows a common ground loop in the transmission path of two linear circuits (a common scenario in test and measurement, audio and other applications that use cable interconnects). The ground loop in the top diagram circulates between the connector grounds while parasitic inductance (Z) causes ringing that generates output noise. The bottom circuit of Figure 8 inserts the ISOlinear circuit between the signal source and receiver, breaking the ground loop and dramatically reducing the local ground path lengths and associated parasitic inductance.

Figure 8. Ground Loop Elimination Circuit

### 4. Summary

Many analog systems require isolation to provide safety, level shifting or to mitigate ground noise. ISOamps are a common but expensive solution that lack flexibility and force the designer to compromise and/or add supplemental circuitry to a design.

Silicon Labs' ISOlinear reference design (Si86IsoLin-EVB) offers a lower-cost, more flexible linear isolation solution. This design is enabled by the Silicon Labs Si86xx industry-leading digital isolator and requires only four operational amplifiers and some passive components in addition to the isolator. The ISOlinear reference design benefits the user with a robust, competitive solution and the opportunity to create an optimum solution for the application at hand at a fraction of the price of an ISOamp.

#### 4.1. Related Documents

- AN559: "Isolating Analog Signals Using the Si86xx CMOS Isolator Family", Silicon Labs, 2011

- ISOlinear Users Guide, Silicon Labs, 2011

- AN598: "High-Speed Level Shifting Using Si8xxx Isolators"

## **AN614**

### **CONTACT INFORMATION**

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701 Tel: 1+(512) 416-8500

Fax: 1+(512) 416-9669 Toll Free: 1+(877) 444-3032

Please visit the Silicon Labs Technical Support web page: https://www.silabs.com/support/pages/contacttechnicalsupport.aspx

and register to submit a technical support request.

### **Patent Notice**

Silicon Labs invests in research and development to help our customers differentiate in the market with innovative low-power, small size, analog-intensive mixed-signal solutions. Silicon Labs' extensive patent portfolio is a testament to our unique approach and world-class engineering team.

The information in this document is believed to be accurate in all respects at the time of publication but is subject to change without notice. Silicon Laboratories assumes no responsibility for errors and omissions, and disclaims responsibility for any consequences resulting from the use of information included herein. Additionally, Silicon Laboratories assumes no responsibility for the functioning of undescribed features or parameters. Silicon Laboratories reserves the right to make changes without further notice. Silicon Laboratories makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Silicon Laboratories assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. Silicon Laboratories products are not designed, intended, or authorized for use in applications intended to support or sustain life, or for any other application in which the failure of the Silicon Laboratories product could create a situation where personal injury or death may occur. Should Buyer purchase or use Silicon Laboratories products for any such unintended or unauthorized application, Buyer shall indemnify and hold Silicon Laboratories harmless against all claims and damages.

Silicon Laboratories and Silicon Labs are trademarks of Silicon Laboratories Inc.

Other products or brandnames mentioned herein are trademarks or registered trademarks of their respective holders.