## **General Description**

The AOZ7100 is a USB Type-C controller that supports to Power Delivery 2.0/3.0. It has a built-in 32-bit MCU, GPIOs, I2C interface and 10bits ADC unit for fulfilling power control and protection on charger and adapter applications. It is available in 28-pin WQFN package.

## **Features**

- Support USB PD 2.0/3.0 via CC1 & CC2 pins

- Support BC 1.2 via DP & DM pins

- Discharge MOS control and cold-socket detection

- CC1/CC2 with high noise immunity

- Support over voltage detection for CC1/CC2

- Support external NTC over temperature Detection

- Support under voltage protection (UVP)

- One high accuracy 10bit-SAR ADC for Voltage and low-side Current monitors

- Built-in 32-bit MCU

- Built-in 16 KB SRAM

- Built-in 32 KB EEPROM

## Applications

- USB Type-C PD Charger

- Smart Charger

- Expose PAD

#### Drain DFT VO CSN C Source Drain GND CSSECN DIS\_S Source CSSECF CPG AOZ7100 AOZ76x5 CC. CS CPS CC2 DP DM A0776x8 VDD FE RXN RXP TXN SDA PRO TR Ī Ī lγr

## **Typical Application**

## **Ordering Information**

| Part Number | Ambient Temperature Range | Package      | Environmental |  |  |

|-------------|---------------------------|--------------|---------------|--|--|

| AOZ7100QI   | -40°C to +85°C            | WQFN 4X4-28L | Green Product |  |  |

AOS Green Products use reduced levels of Halogens, and are also RoHS compliant.

Green

## **Pin Configuration**

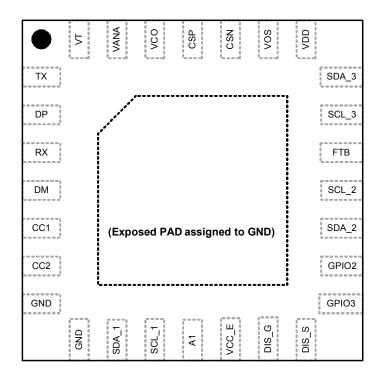

QFN 4mm x 4mm 28-pin (Top View)

## **Pin Description**

| Pin Number | Pin Name | Pin Function                                                         |

|------------|----------|----------------------------------------------------------------------|

| 1          | ТХ       | GPIO/ UART_TX                                                        |

| 2          | DP       | USB D+ Channel                                                       |

| 3          | RX       | GPIO/ UART_RX                                                        |

| 4          | DM       | USB D- Channel                                                       |

| 5          | CC1      | Configuration Channel 1 of Type C                                    |

| 6          | CC2      | Configuration Channel 1 of Type C                                    |

| 7          | GND      | Ground                                                               |

| 8          | GND      | Ground                                                               |

| 9          | SDA_1    | I2C slave SDA of built-in EEPROM:                                    |

| 10         | SCL_1    | I2C slave SCL of built-in EEPROM:                                    |

| 11         | A1       | Slave I2C: device address pin of built-in EEPROM:                    |

| 12         | VCC_E    | EEPROM power input                                                   |

| 13         | DIS_G    | VBUS Discharge Function: to NMOS gate terminal                       |

| 14         | DIS_S    | VBUS Discharge Function: to NMOS source terminal / VBUS monitor      |

| 15         | GPIO3    | General Purpose I/O                                                  |

| 16         | GPIO2    | General Purpose I/O                                                  |

| 17         | SDA_2    | General Purpose I/O: Specific master SDA to AOZ-76x8                 |

| 18         | SCL_2    | General Purpose I/O: Specific master SCL to AOZ-76x8                 |

| 19         | FTB      | Fault Interrupt Channel                                              |

| 20         | SCL_3    | I2C Master SCL to external slave device or built-in EEPROM           |

| 21         | SDA_3    | I2C Master SDA to external slave device or built-in EEPROM           |

| 22         | VDD      | Power Input                                                          |

| 23         | VOS      | Output Voltage detection                                             |

| 24         | CSN      | Low-side current sense Input-negative                                |

| 25         | CSP      | Low-side Current Sense Input-positive                                |

| 26         | VCO      | LDO output 1.2V for MCU Core                                         |

| 27         | VANA     | LDO output 3.3V for built-in analog device                           |

| 28         | VT       | Temperature sense pin (Need External NTC Resistor )& RESET PIN input |

| Expose PAD |          | Ground                                                               |

## **Absolute Maximum Ratings**

Exceeding the Absolute Maximum Ratings may damage the device.

| Parameter                                             | Rating          |

|-------------------------------------------------------|-----------------|

| VDD                                                   | 0V to 6.0V      |

| V <sub>SDA</sub> , V <sub>SCL</sub> ,V <sub>FTB</sub> | 0V to 6.0V      |

|                                                       | -0.3V to +6.0V  |

| VANA                                                  | -0.3V to +3.6V  |

| VCO                                                   | -0.3V to +1.3V  |

| GND                                                   | -0.3V to +0.3V  |

| Package Power Dissipation                             | 2.9W            |

| Junction Temperature (T <sub>J</sub> )                | +150°C          |

| Storage Temperature (T <sub>S</sub> )                 | -65°C to +150°C |

| ESD HBM <sup>(1)</sup>                                | 4kV             |

| ESD CDM <sup>(1)</sup>                                | 250V            |

#### Notes:

1. Devices are inherently ESD sensitive, handling precautions are required. Human body model rating:  $1.5k\Omega$  in series with 100pF.

## **Electrical Characteristics**

$V_O$ =5V,  $T_A$  = -25°C to 85°C, unless otherwise specified.

| Symbol                 | Parameter                       | Parameter Conditions                   |     | Тур | Max | Units |  |  |  |

|------------------------|---------------------------------|----------------------------------------|-----|-----|-----|-------|--|--|--|

| VDD Supply Input       |                                 |                                        |     |     |     |       |  |  |  |

| V <sub>DD_ON</sub>     | Power On Threshold              |                                        | 2.9 | 3   | 3.1 | V     |  |  |  |

| I <sub>VDD</sub>       | Operating Average Current       | V <sub>VDD</sub> =5V                   |     | 2.5 |     | mA    |  |  |  |

| V <sub>VDD_th</sub>    | Threshold Voltage of UVLO       |                                        | 2.7 | 2.8 | 2.9 | V     |  |  |  |

| P <sub>AVDD_PSC</sub>  | Power Saving Current            | V <sub>VDD</sub> =5V, Enter sleep mode | 500 | 600 |     | μA    |  |  |  |

| VANA LDO               |                                 |                                        |     |     |     |       |  |  |  |

| V <sub>VANA</sub>      | LDO Voltage to Peripheral Units | C_VANA =1uF                            | 2.9 | 3.1 | 3.6 | V     |  |  |  |

| VCO LDO                |                                 |                                        |     |     |     |       |  |  |  |

| V <sub>CO</sub>        | LDO Voltage to MCU Core         | C_VCO =1uF                             | 1.1 | 1.2 | 1.3 | V     |  |  |  |

| V <sub>reset_vco</sub> | Power-On Reset Voltage          | Vary by Firmware design                |     | 0.4 |     | V     |  |  |  |

| GPIOs                  |                                 |                                        |     |     |     |       |  |  |  |

| V <sub>GPIO</sub>      | VGPIO_ABS                       | Maximum Voltage per GPIO               | 2.9 | 3.1 | 3.5 | V     |  |  |  |

| I <sub>GPIO</sub>      | IGPIO_ABS                       | Maximum Current per GPIO               | 2.0 | 2.5 | 3.0 | mA    |  |  |  |

| GPIO_INH               | "H" Level                       | Threshold to Logical "1"               | 2.0 | 2.2 |     | V     |  |  |  |

| GPIO_INL               | "H" Level                       | Threshold to Logical "0"               |     | 0.4 | 0.6 | V     |  |  |  |

## **Recommended Operating Conditions**

The device is not guaranteed to operate beyond the Maximum Recommended Operating Conditions.

| Parameter                                                     | Rating           |

|---------------------------------------------------------------|------------------|

| Supply Voltage (VDD)                                          | 3.3V to 5.5V     |

| Ambient Temperature (T <sub>A</sub> )                         | -40°C to +105°C  |

| Package Thermal Resistance $(\theta_{JA})$<br>$(\theta_{JC})$ | 42°C/W<br>9 °C/W |

## Electrical Characteristics (Continued)

$V_O$ =5V,  $T_A$  = -25°C to 85°C, unless otherwise specified.

| Symbol                                 | Parameter                                        | Conditions                                                                           | Min | Тур                  | Max | Units    |

|----------------------------------------|--------------------------------------------------|--------------------------------------------------------------------------------------|-----|----------------------|-----|----------|

| Fault Bar (F                           | TB Pin)                                          |                                                                                      |     |                      | 1   | 1        |

| V <sub>FTBL</sub>                      | Low Level Threshold Voltage                      |                                                                                      |     |                      | 0.6 | V        |

| V <sub>FTBH</sub>                      | High Level Threshold Voltage                     |                                                                                      | 1.8 |                      |     | V        |

| V <sub>FTBHYS</sub>                    | Hysteresis of Schmitt Trigger Inputs             |                                                                                      | 0.1 |                      |     | V        |

| V <sub>FTBOL</sub>                     | Low Level Output Voltage                         | Open drain, 3mA sink                                                                 |     |                      | 0.4 | V        |

| V <sub>FPO</sub>                       | Output Level                                     |                                                                                      |     | V <sub>ANA-0.1</sub> |     | V        |

| EXTERNAL                               | OTP (VT)                                         | ·                                                                                    |     |                      |     |          |

| I <sub>OTP</sub>                       | OTP Detect Source Current                        | Vary by Firmware design                                                              | 18  | 20                   | 22  | μA       |

| V <sub>OTP</sub>                       | OTP Enable Level                                 | VT pin connect with (100k NTC+ $8k\Omega$ resistor) to GND (Vary by Firmware design) |     | 0.8                  |     | v        |

| V <sub>OTPHYS</sub>                    | Hysteresis Voltage                               | 100kΩ NTC+ 8kΩ resistor<br>(Vary by Firmware design)                                 |     | 100                  |     | mV       |

| t <sub>OTP</sub>                       | Debounce Time                                    | 100k $\Omega$ NTC+ 8k $\Omega$ resistor<br>(Vary by Firmware design)                 |     | 60                   |     | mSec     |

| V <sub>reset_VT</sub>                  | Power on Reset Voltage                           | (Vary by Firmware design)                                                            |     | 0.4                  |     | V        |

| VBUS Moni                              | itor (DIS_S Pin)                                 |                                                                                      |     |                      |     |          |

| V <sub>BUSM_L</sub>                    | Input Low Threshold                              | VBUS=5V, R <sub>DIS_1</sub> =10kΩ,<br>R <sub>DIS_2</sub> =1.2kΩ                      |     | 0.15                 |     | V        |

| V <sub>BUSM_H</sub>                    | Input High Threshold                             | VBUS=5V, $R_{DIS_1}$ =10k $\Omega$ , $R_{DIS_2}$ =1.2k $\Omega$                      |     | 0.3                  |     | V        |

| t <sub>BUSM_de</sub>                   | Denounce Timer                                   | Programmable parameter                                                               | 0.1 |                      | 1   | mSec     |

| DP and DM                              | Pins                                             |                                                                                      |     |                      |     |          |

| V <sub>O_DP</sub><br>V <sub>O_DM</sub> | Line Output Voltage                              | V <sub>VANA</sub> =2.9~3.6V                                                          |     | 2.7                  |     | V        |

|                                        | very PHY Interface                               |                                                                                      |     | <u> </u>             | 1   | <u>.</u> |

| I <sub>CC_Default</sub>                | Default Current                                  | VDD =5V, Detach                                                                      | 64  | 80                   | 96  | μA       |

| R <sub>d_1.5A</sub>                    | Pull-Down Resister                               |                                                                                      | 4.6 | 5.1                  | 5.6 | kΩ       |

| CC <sub>CLP</sub>                      | Clamp Voltage to CC1/2                           |                                                                                      | 3.0 | 3.3                  | 3.5 | V        |

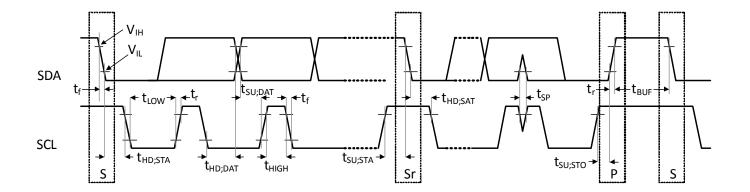

| I2C PHY Int                            | terface                                          | ·                                                                                    |     |                      |     |          |

| V <sub>IL</sub>                        | Low Level Threshold Voltage                      |                                                                                      |     |                      | 0.6 | V        |

| V <sub>IH</sub>                        | High Level Threshold Voltage                     |                                                                                      | 1.8 |                      |     | V        |

| V <sub>HYS</sub>                       | Hysteresis of Schmitt Trigger Inputs             |                                                                                      | 0.1 |                      |     | V        |

| V <sub>OL</sub>                        | Low Level Output Voltage                         | Open Drain, 3mA Sink Current                                                         |     |                      | 0.4 | V        |

| t <sub>SP</sub>                        | Pulse Width of Spikes Suppressed by Input Filter |                                                                                      | 32  |                      |     | ns       |

| f <sub>SCL</sub>                       | SCL Clock Frequency                              |                                                                                      | 100 |                      | 400 | kHz      |

| t <sub>HD:STA</sub>                    | Hold Time (repeated) START<br>Condition          |                                                                                      | 0.6 |                      |     | μS       |

## Electrical Characteristics (Continued)

$V_O$ =5V,  $T_A$  = -25°C to 85°C, unless otherwise specified.

| Symbol              | Parameter                                     | Conditions | Min           | Тур | Мах | Units |

|---------------------|-----------------------------------------------|------------|---------------|-----|-----|-------|

| t <sub>LOW</sub>    | Low Period of SCL Clock                       |            | 1.3           |     |     | μS    |

| t <sub>HIGH</sub>   | High Period of SCL Clock                      |            | 0.6           |     |     | μS    |

| t <sub>SU:STA</sub> | Set-up Time for a Repeated START<br>Condition |            | 0.6           |     |     | μS    |

| t <sub>HD:DAT</sub> | Data Hold Time                                |            | 50            |     | 900 | nS    |

| t <sub>SU:DAT</sub> | Data Set-up Time                              |            | 100           |     |     | nS    |

| t <sub>R2</sub>     | Rising Time (SDA or SCL)                      |            | 20+0.1<br>Cb* |     | 300 | nS    |

| t <sub>F2</sub>     | Falling Time (SDA or SCL)                     |            | 20+0.1<br>Cb* |     | 300 | nS    |

| t <sub>SU:STO</sub> | Set-up Time for STOP Condition                |            | 0.6           |     |     | μS    |

| t <sub>BUF</sub>    | Bus Free Time between STOP & START Condition  |            | 1.3           |     |     | μS    |

| Cb                  | Capacitive Load of Each Bus Line              |            |               |     | 400 | pF    |

Notes:

2. Guaranteed by design.

3. Refer to Figure 1 for I2C Timing Definitions.

4. Cb= capacitance for bus line in pF.

Figure 1. I<sup>2</sup>C Timing Definitions (reproduced from Phillips I<sup>2</sup>C specification version 1.1)

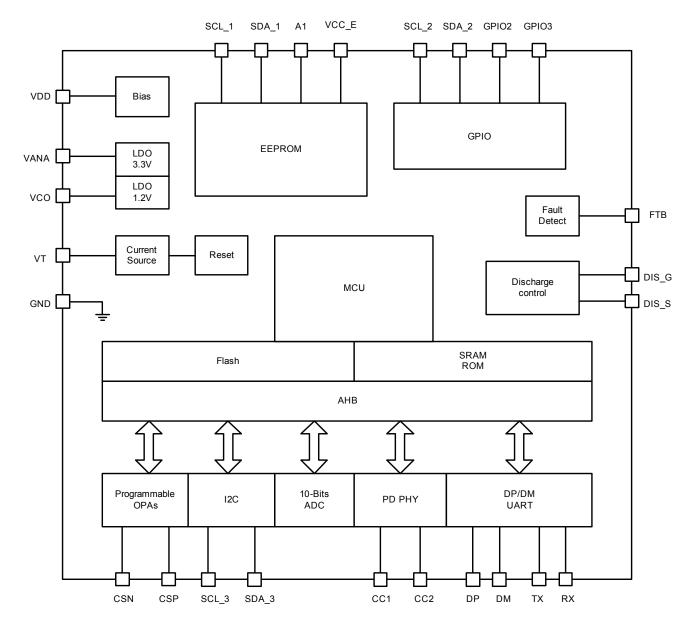

## **Functional Block Diagram**

## **Detailed Description**

USB Implementers Forum (USB-IF) released USB Power Delivery (PD) 2.0/3.0 Specifications for intelligent and flexible system level management of power. Both power provider and power consumer would need Power Delivery interface to negotiate and share the message such as VBUS and protection method. Existing PD interface of AOZ7100 could fulfill Dual Role Port application for power provider and consumer. An I2C master interface is adapted for power management and expanding peripheral control mechanism.

#### Start Up Via Pin VDD

Using external device's LDO or possible source, AO7100 can be powered to start up. AOZ7100 is designed to operate with low supply voltages down to 2.9V. Two internal LDOs of AOZ7100 operate to provide individual power to MCU core, comparators and built-in ADCs. It is recommended to add over 1uF ceramic capacitor to VANA and VCO output pin respectively.

#### **I2C Master Interface**

AOZ7100 has two I2C master Interface to fulfill design flexibility and expand digital control mechanism. Two pull-up resistors are built into AOZ7100 for minimizing external component.

#### **Configuration Channel CC1/CC2**

CC channels are used for connection detect, PD interface configuration and message sending/receiving.

#### **GPIOs Device**

GPIOs can be utilized to control other switch component or sense specific digital signal. Additionally, firmware hardware of MASK ROM can be selectable by status of the GPIOs.

#### Mask-ROM (Option)

High reliability built-in Mask-ROM can be merged into AOZ7100 to store the boot-loader or customized firmware. Additional, Multi Mask-ROM providing different firmware version is adapted in advance to ensure design selection. For the product development or validation period, it is recommended to use built-in I2C-EEPROM to store the boot-loader or firmware.

#### 32kB EEPROM

An EEPROM device is integrated into AOZ7100 for customized development period or final product. Microcontroller of AOZ7100 could be programmed by downloading firmware of EEPROM. Pin SDA(S) and SCL(S) could be used to implement update or download firmware. Pin A1 is device address input that would be internally pulled down to GND. Therefore, EEPROM provides design flexibility to fulfill system function.

#### **VBUS Voltage Monitor Pin VOS**

VOS could monitor VBUS level via divided resistors. Firmware can set individual OVP level to corresponding Power Data Object (PDO). Once built-in OVP is triggered, AOZ7100 could turn off load switch and set VBUS back to default 5V.

#### **VBUS Current Monitor Pin CSP & CSN**

Pin CSP and CSN are used to sense load current. Firmware can set individual OCP level to corresponding Power Data Object (PDO). Under overload conditions, AOZ7100 could take Current Fold-Back mechanism to reduce the power dissipation within safe operating area.

# External Discharge Switch Control and Cold-Socket Detect

AOZ7100 provide gate driver pin DIS\_G to control external discharge switch. Once receiving PD hard reset message or taking protection, external discharge switch would be used to discharge. In addition, AOZ7100 can check cold socket of receptacle via DIS\_S with appropriate divided pull down resistor.

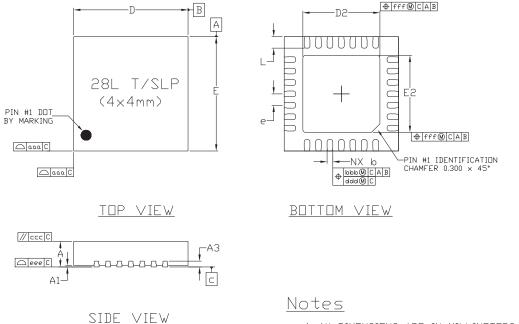

## Packaging Dimensions WQFN4x4-28L

|      | Dimensional Ref. |         |        |  |  |  |  |  |  |  |

|------|------------------|---------|--------|--|--|--|--|--|--|--|

| REF. | Min.             | Nom.    | Max.   |  |  |  |  |  |  |  |

| Α    | 0.700            | 0.750   | 0.800  |  |  |  |  |  |  |  |

| A1   | 0.000            |         | 0.050  |  |  |  |  |  |  |  |

| A 3  | 0                | .203 Re | f.     |  |  |  |  |  |  |  |

| D    | 3.950            | 4.000   | 4.050  |  |  |  |  |  |  |  |

| E    | 3.950            | 4.000   | 4.050  |  |  |  |  |  |  |  |

| D2   | 2.650            | 2.700   | 2.750  |  |  |  |  |  |  |  |

| E2   | 2.650            | 2.700   | 2.750  |  |  |  |  |  |  |  |

| Ь    | 0.150            | 0.200   | 0.250  |  |  |  |  |  |  |  |

| L    | 0.350            | 0.400   | 0.450  |  |  |  |  |  |  |  |

| e    | 0                | .400 BS | )0 BSC |  |  |  |  |  |  |  |

| Τc   | <u>pl. of Fc</u> | rm&Po:  | sition |  |  |  |  |  |  |  |

| ааа  |                  | 0.10    |        |  |  |  |  |  |  |  |

| ЬЬЬ  | 0.10             |         |        |  |  |  |  |  |  |  |

| ccc  | 0.10             |         |        |  |  |  |  |  |  |  |

| ddd  | 0.05             |         |        |  |  |  |  |  |  |  |

| eee  |                  | 0.08    |        |  |  |  |  |  |  |  |

| fff  |                  | 0.10    |        |  |  |  |  |  |  |  |

1. AU DIMENSIONS ARE IN MILLIMETERS.

2. DIMENSIONING AND TOLERANCING PER JEDEC MO-220.

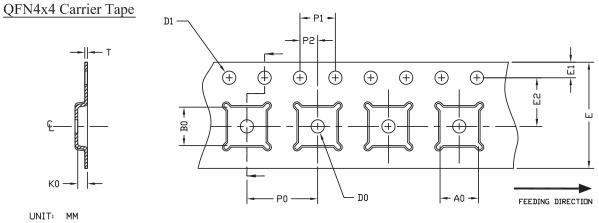

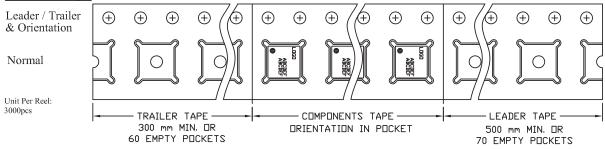

## Tape and Reel, WQFN4x4-28L

| PACKAGE           | A0            | BO            | К0            | DO           | D1                   | E            | E1            | E2            | P0            | P1            | P2            | Т             |

|-------------------|---------------|---------------|---------------|--------------|----------------------|--------------|---------------|---------------|---------------|---------------|---------------|---------------|

| QFN4x4<br>(12 mm) | 4.35<br>±0.10 | 4.35<br>±0.10 | 1.10<br>±0.10 | 1.50<br>MIN. | 1.50<br>+0.1<br>-0.0 | 12.0<br>±0.3 | 1.75<br>±0.10 | 5.50<br>±0.05 | 8.00<br>±0.10 | 4.00<br>±0.10 | 2.00<br>±0.05 | 0.30<br>±0.05 |

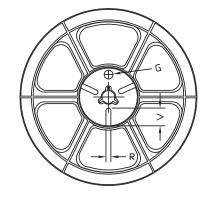

### QFN4x4 Reel

ŀ

UNIT: MM

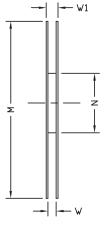

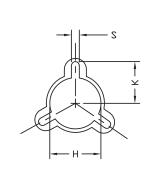

| TAPE SIZE | REEL SIZE | м              | N             | W                    | W1                   | Н             | к            | S           | G | R | V |

|-----------|-----------|----------------|---------------|----------------------|----------------------|---------------|--------------|-------------|---|---|---|

| 12 mm     | ø330      | Ø330.0<br>±2.0 | ø79.0<br>±1.0 | 12.4<br>+2.0<br>-0.0 | 17.0<br>+2.6<br>-1.2 | ø13.0<br>±0.5 | 10.5<br>±0.2 | 2.0<br>±0.5 |   |   |   |

#### QFN4x4 Tape

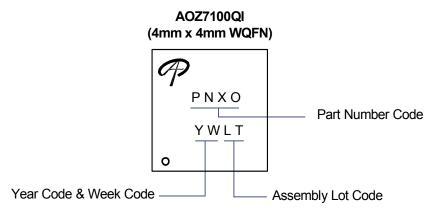

## Part Marking

| Part No.  | Description   | Code |

|-----------|---------------|------|

| AOZ7100QI | Green Product | BU00 |

#### LEGAL DISCLAIMER

Applications or uses as critical components in life support devices or systems are not authorized. AOS does not assume any liability arising out of such applications or uses of its products. AOS reserves the right to make changes to product specifications without notice. It is the responsibility of the customer to evaluate suitability of the product for their intended application. Customer shall comply with applicable legal requirements, including all applicable export control rules, regulations and limitations.

AOS' products are provided subject to AOS' terms and conditions of sale which are set forth at: <a href="http://www.aosmd.com/terms">http://www.aosmd.com/terms</a> and conditions of sale

#### LIFE SUPPORT POLICY

ALPHA AND OMEGA SEMICONDUCTOR PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS.

As used herein:

1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user. 2. A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.