## Chipown

## 1.2 MHz, Micropower Synchronous Step-Up Converter

**General Description**

The AP2000 is synchronous, fixed frequency, step-up DC/DC converters delivering high efficiency in a 6-lead SOT package. Capable of supplying 3.3V at 100mA from a single AA cell input, the device contain an internal NMOS switch and PMOS synchronous rectifier. A switching frequency of 1.2MHz minimizes solution footprint by allowing the use of tiny, low profile inductors and ceramic capacitors. The current mode PWM design is internally compensated, reducing external parts count. The AP2000 features continuous switching at light loads. Antiringing control circuitry reduces EMI concerns by damping the inductor in discontinuous mode, and the device features low shutdown current of under 1A. The device is available in the small profile (1.1mm) SOT-23 package.

### **Applications**

- Cellular and Smart Phones

- Microprocessors and DSP Core Supplies

- Wireless and DSL Modems

- MP3 Player

- Digital Still and Video Cameras

- Portable Instruments

#### **Features**

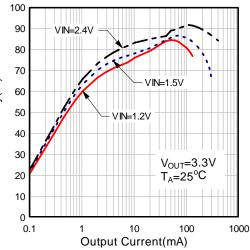

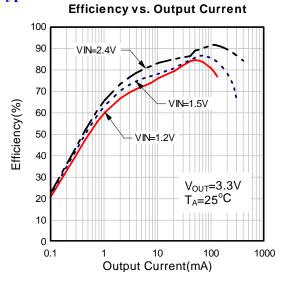

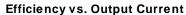

- High Efficiency: Up to 92%

- 1.2MHz Constant Switching Frequency

- 3.3V Output Voltage at I<sub>OUT</sub>=100mA from a Single AA Cell; 3.3V Output Voltage at I<sub>OUT</sub>=400mA from two AA cells

- Low Start-up Voltage: 0.85V

- Integrated main switch and synchronous rectifier.

No Schottky Diode Required

- 2.5V to 5V Output Voltage Range

- Automatic Pulse Skipping Mode Operation

- Tiny External Components

- <1µA Shutdown Current

- Antiringing Control Reduces EMI

- Space Saving 6-Pin SOT23 Package

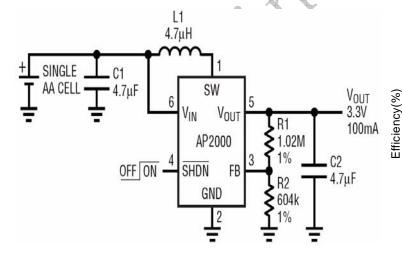

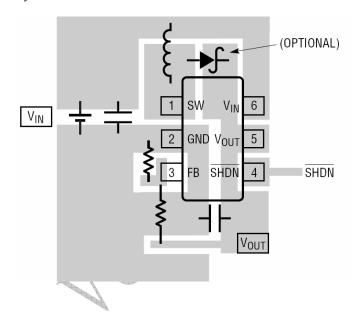

### **Typical Application Circuit**

Figure 1. Basic Application Circuit with AP2000 Adjustable Version

### Efficiency vs. Output Current

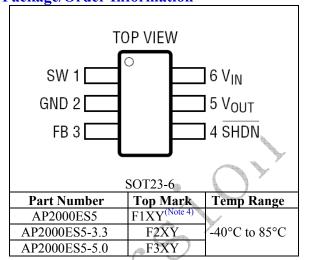

# **Chipown**Package/Order Information

## Absolute Maximum Rating(Note 1)

| Input Supply Voltage                            | 0.3V to +6V    |

|-------------------------------------------------|----------------|

| SW Voltage                                      | 0.3V to +6V    |

| FB, SHDN Voltages                               | 0.3V to +6V    |

| V <sub>OUT</sub> Voltage                        | 0.3V to +6V    |

| Operating Temperature Range <sup>(Note 2)</sup> | 40°C to +85°C  |

| Storage Temperature Range                       | 65°C to +150°C |

| Lead Temperature (Soldering, 10s)               | +300°C         |

## Thermal Resistance (Note 3):

| Package  | $\Theta_{ m JA}$ | $\Theta_{ m JC}$ |

|----------|------------------|------------------|

| TSOT23-6 | 250°C /W         | 110°C /W         |

### **Electrical Characteristics** (Note 5)

$(V_{IN} = 1.2V, V_{OUT} = 3.3V, T_A = 25$ °C, Test Circuit of Figure 1, unless otherwise noted.)

| Parameter                     | Conditions                                                           | MIN   | TYP   | MAX   | unit |

|-------------------------------|----------------------------------------------------------------------|-------|-------|-------|------|

| Minimum Start-Up Voltage      | $I_{OUT} = 1 \text{mA}$                                              |       | 0.85  | 1     | V    |

| Minimum Operating Voltage     | $V_{SHDN} = V_{IN}$                                                  |       | 0.5   | 0.65  | V    |

| Output Voltage Range          |                                                                      | 2.5   |       | 5     | V    |

| Feedback Voltage              | $-40^{\circ}\text{C} \le T_{A} \le 85^{\circ}\text{C}$               | 1.192 | 1.230 | 1.268 | V    |

| Quiescent Current(Shutdown)   | $V_{SHDN} = 0V$                                                      |       | 0.01  | 1     | μA   |

| Quiescent Current(Active)     | Measured on V <sub>OUT</sub>                                         |       | 300   | 500   | μA   |

| NMOS Switch Leakage           | $V_{SW} = 5V$                                                        |       | 0.1   | 5     | μΑ   |

| PMOS Switch Leakage           | $V_{SW} = 0V$                                                        |       | 0.1   | 5     | μA   |

| NMOS Switch ON Resistance     | $V_{OUT} = 3.3V$                                                     |       | 0.40  |       | Ω    |

| INMOS SWITCH ON RESIstance    | $V_{OUT} = 5V$                                                       |       | 0.35  |       | Ω    |

| PMOS Switch ON Resistance     | $V_{OUT} = 3.3V$                                                     |       | 0.70  |       | Ω    |

| PWOS SWIICH ON RESIstance     | $V_{OUT} = 5V$                                                       |       | 0.60  |       | Ω    |

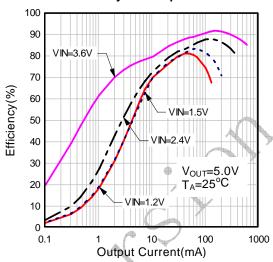

| Output Voltage                | $V_{OUT} = 3.3V$ , $I_{OUT} = 1$ mA                                  | 3.201 | 3.300 | 3.399 | V    |

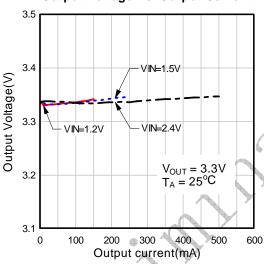

| Output voltage                | $V_{OUT} = 5V$ , $I_{OUT} = 1mA$ , $V_{IN} = 2.4V$                   | 4.850 | 5.000 | 5.150 | V    |

| Line Regulation               | $V_{IN} = 0.8V$ to 3.0V, $I_{OUT} = 10$ mA                           |       | 1     |       | %/V  |

| Load Regulation               | $I_{OUT} = 1 \text{mA to } 100 \text{mA}$                            |       | 0.02  |       | %/mA |

| NMOS Current Limit            |                                                                      | 600   | 850   |       | mA   |

| Current Limit Delay to Output | Note 6                                                               |       | 40    |       | ns   |

| Max Duty Cycle                | $V_{FB} = 1.15V, -40^{\circ}C \le T_A \le 85^{\circ}C$               | 80    | 85    |       | %    |

| Switching Fraguency           |                                                                      | 0.95  | 1.2   | 1.5   | MHz  |

| Switching Frequency           | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le 85^{\circ}\text{C}$ | 0.85  | 1.2   | 1.5   | MHz  |

| SHDN Input Threshold          |                                                                      | 0.35  | 0.60  | 1.50  | V    |

| SHDN Input Current            | $V_{SHDN} = 5.5V$                                                    |       | 0.01  | 1     | μΑ   |

Note 1: Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

**Note 2:** T<sub>J</sub> is calculated from the ambient temperature T<sub>A</sub> and power dissipation P<sub>D</sub> according to the following formula:

$T_J = TA + (PD) \times (250^{\circ}C/W).$

**Note 3:** Thermal Resistance is specified with approximately 1 square of 1 oz copper.

## Chipown

**Note 4:** XY= Manufacturing Date Code.

**Note 5:** 100% production test at +25°C. Specifications over the temperature range are guaranteed by design and characterization.

Note 6: Guaranteed by design.

## Chipown

**Typical Performance Characteristics**

### **Output Voltage vs. Output Current**

**Output Voltage vs. Output Current**

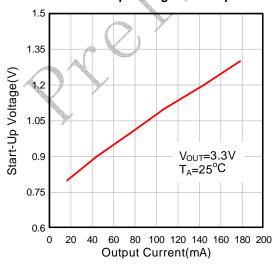

### Minimum Start-Up Voltage vs. Output Current

Maximum Output Current vs. Input Voltage

## Chipown

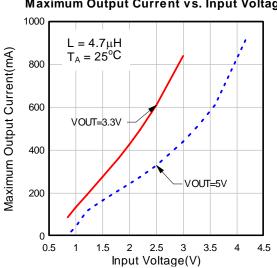

**Typical Performance Characteristics** (Continued)

## Chipown

## **Pin Description**

| PIN | NAME | FUNCTION                                                                                                                                                                |  |  |

|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1   | SW   | Power Switch Pin. It is the switch node connection to Inductor.                                                                                                         |  |  |

| 2   | GND  | Ground Pin                                                                                                                                                              |  |  |

| 3   | FB   | Feedback Input Pin. Connect FB to the center point of the external resistor divider. The feedback threshold voltage is 1.23V.                                           |  |  |

| 4   | SHDN | Chip Shutdown Signal Input. Logic high is normal operation mode, Logic Low is Shutdown. Typically, this pin is connected to $V_{\rm IN}$ through a $1M\Omega$ resistor. |  |  |

| 5   | VOUT | Power Output Pin. $V_{OUT}$ is held 0.6V below than $V_{IN}$ in shutdown.                                                                                               |  |  |

| 6   | VIN  | Power Supply Input. Must be closely decoupled to GND, Pin 2, with a 4.7μF or greater ceramic capacitor.                                                                 |  |  |

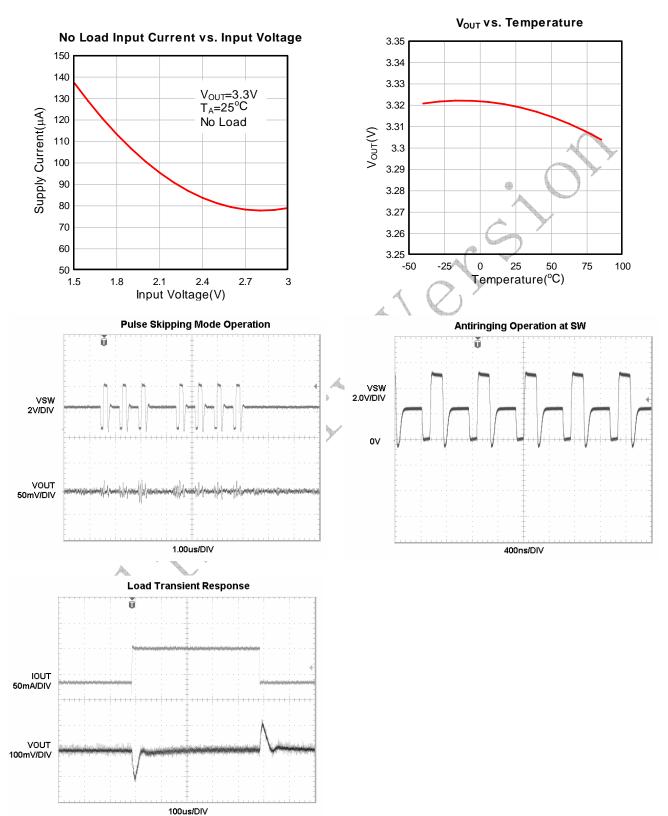

## Functional Block Diagram

Figure 2. AP2000 Block Diagram

## Chipown

### **Operation**

The AP2000 is 1.2MHz, synchronous boost converter housed in a 6-lead SOT package. Able to operate from an input voltage below 1V, the device features fixed frequency, current mode PWM control for exceptional line and load regulation. With its low RDS (ON) and gate charge internal MOSFET switches, the device maintains high efficiency over a wide range of load current. Detailed descriptions of the operating modes follow. Operation can be best understood by referring to the Block Diagram.

#### **Synchronous Rectification**

The AP2000 integrates a synchronous rectifier to improve efficiency as well as to eliminate the external Schottky diode. The synchronous rectifier is used to reduce the conduction loss contributed by the forward voltage of Schottky diode. The synchronous rectifier is realized by a P-ch MOSFET with gate control circuitry that incorporates relatively complicated timing concerns.

#### Low Voltage Start-Up

The AP2000 will start up at a typical VIN volt-age of 0.85V or higher. The low voltage start-up circuitry controls the internal NMOS switch up to a maximum peak inductor current of 850mA (typical), with an approximate 1.5 us off-time during start-up, allowing the devices to start up into an output load. Once Vour exceeds 2.3V, the start-up circuitry is disabled and normal fixed frequency PWM operation is initiated. In this mode, the AP2000 operate independent of VIN, allowing extended operating time as the battery can droop to several tenths of a volt without affecting output voltage regulation. The limiting factor for the application becomes the ability of the battery to supply sufficient energy to the output.

#### **Low Noise Fixed Frequency Operation**

Oscillator: The frequency of operation is internally set to 1.2MHz.

Error Amp: The error amplifier is an internally compensated trans-conductance type (current output) with a trans-conductance (gm) = 33 micro-siemens. The internal 1.23V reference voltage is compared to the voltage at the FB pin to generate an error signal at the output of the error amplifier. A volt-age divider from Vout to ground programs the output voltage via FB from 2.5V to 5V using the equation:

$$V_{OUT} = 1.23V \cdot [1 + (R1/R2)]$$

Current Sensing: A signal representing NMOS switch current is summed with the slope compensator. The summed signal is compared to the error amplifier output to provide a peak current control command for the PWM. Peak switch current is limited to approximately 850mAindependent of input or output voltage. The current signal is blanked for 40ns to enhance noise rejection.

Zero Current Comparator: The zero current comparator monitors the inductor current to the output and shuts off the synchronous rectifier once this current reduces to approximately 20mA. This prevents the inductor current from reversing in polarity improving efficiency at light loads.

Antiringing Control: The antiringing control circuitry pre-vents high frequency ringing of the SW pin as the inductor current goes to zero by damping the resonant circuit formed by L and CSW (capacitance on SW pin).

### **Pulse Skipping Mode**

At very light load, the AP2000 automatically switches into Pulse Skipping Mode to improve efficiency. During this mode, the PWM control will skip some pulses to maintain regulation. If the load increases and the output voltage drops, the device will automatically switch back to normal PWM mode and maintain regulation.

#### **Device Shutdown**

When SHDN is set logic high, the AP2000 is put into operation. If SHDN is set logic low, the device is put into shutdown mode and consumes lower than  $1\mu A$  current. After start-up timing, the internal circuitry is supplied by  $V_{OUT}$ , however, if shutdown mode is enabled, the internal circuitry will be supplied by battery again.

Setting the Output Voltage

An external resistor divider is used to set the output voltage. The output voltage of the switching regulator  $(V_{OUT})$  is determined by the following equation:

$$V_{OUT} = 1.23V \times \left(1 + \frac{R1}{R2}\right)$$

Table 1 list the resistor selection for output voltage setting.

Table 1. Resistor selection for output voltage setting

| $V_{OUT}$ | R1(Ω) | $R2(\Omega)$ |

|-----------|-------|--------------|

| 3.3V      | 1.02M | 604k         |

| 5.0V      | 1.02M | 332k         |

#### Inductor Selection

The high switching frequency of 1.2MHz allows for small surface mount inductors. For most designs, the AP2000 operates with inductors of  $4.7\mu H$  to  $10\mu H. The equation below can help to select the inductor, the$

maximum output current can be get by this equation; where  $\eta$  is the efficiency,  $I_{PEAK}$  is the peak current limit, f is the switching frequency, L is the inductance value and D is the duty cycle.

$$I_{OUT} = \eta \times \left(Ipeak - \frac{VIN \times D}{2 \times f \times L}\right) \times (1 - D)$$

Larger inductors mean less inductor current ripple and usually less output voltage ripple. Larger inductors also mean more load power can be delivered. But large inductors are also with large profile and costly. The inductor ripple current is typically set for 20% to 40% of the maximum inductor current. When selecting an inductor, the DC current rating must be high enough to avoid saturation at peak current. For optimum load transient and efficiency, the low DCR should be selected. Table 2 lists some typical surface mount inductors that meet target applications for the AP2000:

Table2. Typical Surface Mount Inductors

| Part Number        | L<br>(µH)               | Max<br>DCR<br>(mΩ)      | Rated<br>D.C.<br>Current<br>(A) | Size<br>WxLxH<br>(mm) |

|--------------------|-------------------------|-------------------------|---------------------------------|-----------------------|

| Sumida<br>CR43     | 4.7<br>10               | 108.7<br>182            | 1.15<br>1.04                    | 4.3x4.8x3.5           |

| Sumida<br>CDRH4D28 | 4.7<br>5.6<br>6.8<br>10 | 72<br>101<br>109<br>128 | 1.32<br>1.17<br>1.12<br>1.00    | 5.0x5.0x3.0           |

| Toko<br>D53LC      | 4.7<br>6.8<br>10        | 45<br>68<br>90          | 1.87<br>1.51<br>1.33            | 5.0x5.0x3.0           |

## Chipown

**Output Capacitor Selection**

The output capacitor is required to keep the output voltage ripple small and to ensure regulation loop stability. A  $2.2\mu F$  to  $10\mu F$  output capacitor is sufficient for most applications. If output capacitor is larger than  $10\mu F$ , a phase lead capacitor must be included to maintain enough phase margin. The output capacitor must have low impedance at the switching frequency. Ceramic capacitors with X5R or X7R dielectrics are recommended due to their low ESR and high ripple current ratings.

Input Capacitor Selection

The input capacitor reduces the surge current drawn from the input and switching noise from the device. A minimum  $4.7\mu F$  input capacitor is needed for most applications. The input capacitor impedance at the switching frequency should be less than input source impedance to prevent high frequency switching current passing to the input. A low ESR input capacitor sized for maximum RMS current must be used. Ceramic capacitors with X5R or X7R dielectrics are highly recommended because of their low ESR and small temperature coefficients.

### **Output Diode Selection**

An Shottky diode should be included when the output voltage is above 4.5V. The Schottky diode is optional for the output voltage not more than 4.5V, but can improve efficiency by about 2% to 3%.

## Chipown

### **PCB** Layout Guidance

The AP2000 operates at 1.2MHz typically. This is a considerably high frequency for dc-dc converters. In such case PCB layout is important to guarantee satisfactory performance. It is recommended to make traces of the power loop, especially where switching node is involved as short and wide as possible. First of all, the inductor, input and output capacitor should be close to the device. Feedback and shut down circuit should avoid the proximity of large AC signals, e.g. the power inductor and switching nodes. The optional rectifier diode (D1) can improve efficiency and alleviate the stress on the integrated MOSFET. The diode should also be close to the inductor and the chip to form the shortest possible switching loop. While 2 layer PCB shown in Fig.4 is enough for most applications. Large and integral multi layer ground planes are ideal for high power applications. Large area of copper has lower resistance and helps to dissipate heat on the device. The converter's ground should join the system ground to which it supplies power at one point only. Figure 3 is the schematic for a typical

application for AP2000. Figure 4 is an example PCB layout for AP2000.

## Chipown

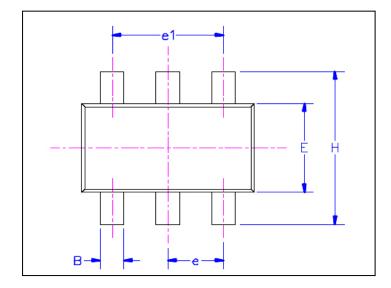

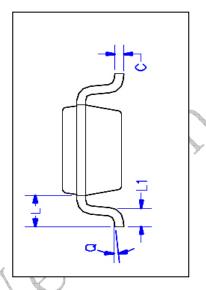

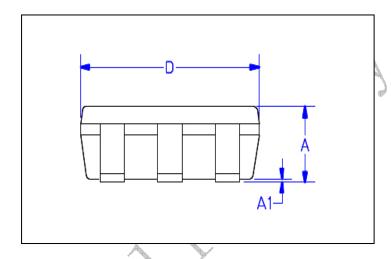

### **Package Information**

| Dimension | Min.      | Max. |  |

|-----------|-----------|------|--|

| A         | 1.10      | 1.30 |  |

| A1        | 0.01      | 0.13 |  |

| В         | 0.30      | 0.50 |  |

| С         | 0.09      | 0.20 |  |

| D         | 2.80      | 3.10 |  |

| Н         | 2.50      | 3.10 |  |

| Е         | 1.50      | 1.70 |  |

| e         | 0.95 REF. |      |  |

| e1        | 1.90 REF. |      |  |

| L1        | 0.20      | 0.55 |  |

| L         | 0.35      | 0.80 |  |

| Q         | 0°        | 10°  |  |

Note: All dimensions in mm

6 Lead SOT-23 Package Outline Dimensions

#### **IMPORTANT NOTICE**

Chipown Microelectronics Co. Ltd. reserves the right to make changes without further notice to any products or specifications herein. Chipown Microelectronics Co. Ltd. does not assume any responsibility for use of any its products for any particular purpose, nor does Chipown Microelectronics Co. Ltd assume any liability arising out of the application or use of any its products or circuits. Chipown Microelectronics Co. Ltd does not convey any license under its patent rights or other rights of others.