### 1MHz, 2A Step Up Regulator

#### **General Description**

AP2008 is an asynchronous PWM boost converter using a constant frequency peak current mode. An external Schottky diode is needed. At light load, AP2008 works in the light load mode. The supply current during the light mode is 100 uA, together with the  $200 m\Omega$  internal NMOS power transistor guarantees high efficiency in the whole output load current range. Up to 2A peak current, Let AP2008 can provide 1A output load current, which is suitable to use as MID and mobile power supply. The input voltage  $3V{\sim}25V.$  The operating frequency is internally set at 1MHz.

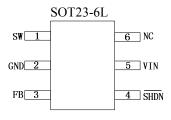

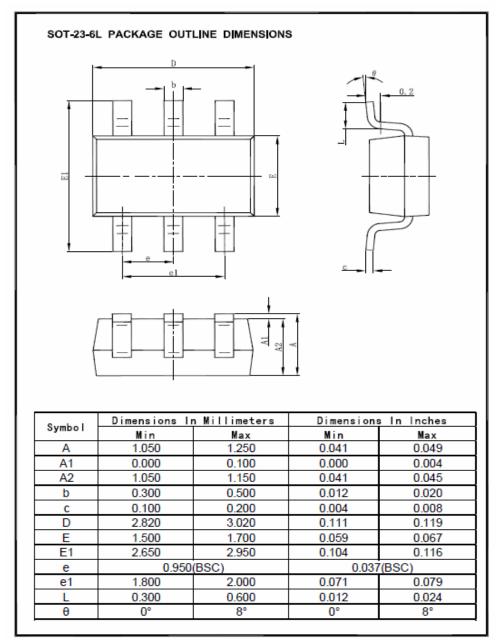

The device is available in the small profile SOT23-6L package.

#### **Applications**

- WLED Drivers

- Networking cards powered from PCI or PCIexpress slots

#### • MID and Mobile Power

#### **Features**

- High Efficiency: Up to 92%

- 1.0MHz Constant Switching Frequency

- Switch current up to 2A

- Low Rdson:  $0.2\Omega$

- Accurate Reference:0.6V

- Tiny External Components

- Space Saving 6-Pin SOT23 Package

#### **Package**

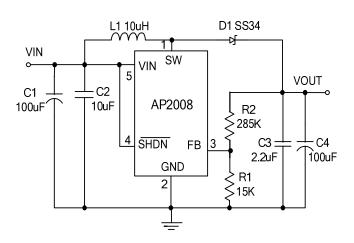

### **Typical Application Circuit**

Figure 1. Basic Application Circuit with AP2008

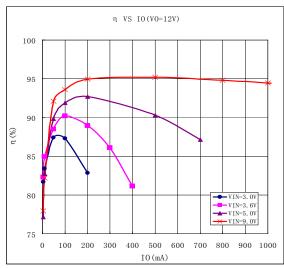

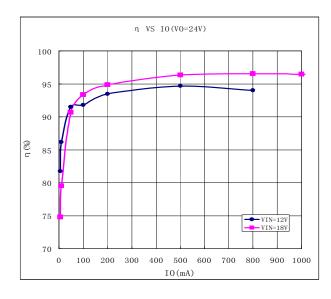

Figure 2. Typical Efficiency Curve

#### **Pin Description**

| Pin | Pin  | Pin Function                                                                                                                 |  |  |

|-----|------|------------------------------------------------------------------------------------------------------------------------------|--|--|

| No. | Name |                                                                                                                              |  |  |

| 1   | SW   | Power Switch Pin. It is the switch node connection to Inductor.                                                              |  |  |

| 2   | GND  | Ground Pin.                                                                                                                  |  |  |

| 3   | FB   | Feedback Input Pin. Connect FB to the center point of the external resistor divider. The feedback threshold voltage is 0.6V. |  |  |

| 4   | SHDN | Chip Shutdown Signal Input. Logic high is normal operation mode, Logic Low is Shutdown. Don't leave it floated.              |  |  |

| 5   | VIN  | VIN Power Supply Input. Must be closely decoupled to GND, Pin 2, with a 10µF or greater ceramic capacitor.                   |  |  |

| 6   | NC   | No Internal Connection.                                                                                                      |  |  |

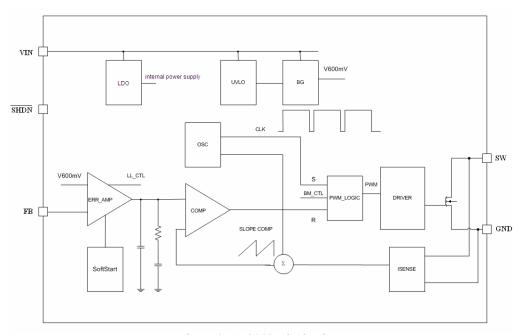

### **Functional Block Diagram**

Figure 3. AP2008 Block Diagram

## Absolute Maximum Rating (Note 1)

| Input Supply VoltageSW, SHDN Voltage |                |

|--------------------------------------|----------------|

| FB Voltages                          | 0.3V to +6V    |

| (Note 2)                             |                |

| Package Thermal Resistance           |                |

| θ                                    | 220°C/W        |

| JA                                   |                |

| $\theta_{_{IO}}$                     | 110°C/W        |

| JC                                   |                |

| Operating Temperature Range          | 40°C to +85°C  |

| Storage Temperature Range.           | 65°C to +150°C |

| Lead Temperature (Soldering, 10s)    | +260°C         |

# Chipown

#### **Electrical Characteristics** (Note 3)

$(V_{OUT}=12V, T_A=25^{\circ}C, Test Circuit of Figure 1, unless otherwise noted.)$

| Parameter                     | Symbol         | Test Conditions     | Min   | Typ | Max   | Unit |

|-------------------------------|----------------|---------------------|-------|-----|-------|------|

| Input Voltage Range           | VIN            |                     | 3     |     | 25    | V    |

| Quiescent Current             | IQ             | FB=0.66V, No switch |       | 100 |       | μA   |

| Shutdown Current              | $I_{SHDN}$     | SHDN=0              |       | 3   |       | μΑ   |

| Low Side Main FET RON         | RDS(ON)        |                     |       | 200 |       | mΩ   |

| Main FET Current<br>Limit     | $I_{LIM1}$     |                     | 2     |     | 2.6   | A    |

| Switching Frequency           | Fsw            | VIN=3V,IO=300mA     | 0.8   | 1   | 1.2   | MHz  |

| Feedback Reference<br>Voltage | VREF           | VIN=3V,IO=10mA      | 0.588 | 0.6 | 0.612 | V    |

| IN UVLO rising threshold      | $V_{\rm UVLO}$ | VIN Rising          |       |     | 2.7   | V    |

| UVLO hysteresis               | $UVLO_{,HYS}$  |                     |       | 0.1 |       | V    |

| Thermal Shutdown Temperature  | TSD            |                     |       | 150 |       | °C   |

**Note 1:** Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

**Note 2:** Thermal Resistance is specified with approximately 1 square of 1oz copper.

**Note 3:**100% production test at +25°C. Specifications over the temperature range are guaranteed by design and characterization.

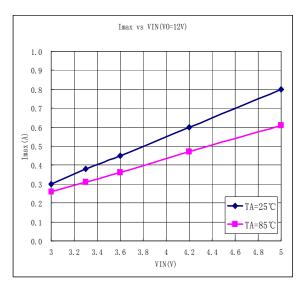

#### **Typical Performance Characteristics**

#### **Ordering Information**

| Part number    | Mark               | Package   |  |  |

|----------------|--------------------|-----------|--|--|

| AP2008TCER-ADJ | U1XYP <sup>1</sup> | SOT-23-6L |  |  |

1.XY=date code

P= Package factory

# **AP2008**

# Chipown

#### **Operation**

The AP2008 uses a fixed frequency, peak current mode boost regulator architecture to regulate voltage at the feedback pin. The operation of the AP2008 can be understood by referring to the block diagram of Figure 3. At the start of each oscillator cycle the MOSFET is turned on through the control circuitry. To prevent subharmonic oscillations at duty cycles greater than 50 percent, a stabilizing ramp is added to the output of the current sense amplifier and the result is fed into the negative input of the PWM comparator. When this voltage equals the output voltage of the error amplifier the power MOSFET is turned off. The voltage at the output of the error amplifier is an amplified version of the difference between the 0.6V bandgap reference voltage and the feedback voltage. In this way the peak current level keeps the output in regulation. If the feedback voltage starts to drop, the output of the error amplifier increases. These results in more current to flow through the power MOSFET, thus increasing the power delivered to the output. The AP2008 has internal soft start to limit the amount of input current at startup and to also limit the amount of overshoot on the output.

# **Application Information Setting the Output Voltage**

The internal reference VREF is 0.6V (Typical). The output voltage is divided by a resistor divider, R1 and R2 to the FB pin. The output voltage is given by

$$V_{OUT} = 0.6V \times \left(1 + \frac{R2}{R1}\right)$$

#### **Inductor Selection**

The recommended values of inductor are 3.3 to  $10\mu H$ . Small size and better efficiency are the major concerns for portable device, such as AP2008 used for mobile phone. The inductor should have low core

loss at 1.0MHz and low DCR for better efficiency. To avoid inductor saturation current rating should be considered

#### **Capacitor Selection**

Input ceramic capacitor of  $10\mu F$  is recommended for AP2008 applications. For better voltage filtering, ceramic capacitors with low ESR are recommended. X5R and X7R types are suitable because of their wider voltage and temperature ranges.

#### **Diode Selection**

Schottky diode is a good choice for AP2008 because of its low forward voltage drop and fast reverses recovery. Using Schottky diode can get better efficiency. The high speed rectification is also a good characteristic of Schottky diode for high switching frequency. Current rating of the diode must meet the root mean square of the peak current and output average current multiplication as following:

$$I_{D(RMS)} \approx \sqrt{I_{OUT} \times I_{PEAK}}$$

The diode's reverse breakdown voltage should be larger than the output voltage.

#### **Layout Consideration**

For best performance of the AP2008, the following guidelines must be strictly followed.

- Input and Output capacitors should be placed close to the IC and connected to ground plane to reduce noise coupling.

- The GND should be connected to a strong ground plane for heat sinking and noise protection.

- Keep the main current traces as possible as short and wide.

- SW node of DC-DC converter is with high frequency voltage swing. It should be kept at a small area

- Place the feedback components as close as possible to the IC and keep away from the noisy device

# Chipown

#### **Package Information**

#### **Important Notice**

Chipown Microelectronics Co. Ltd. reserves the right to make changes without further notice to any products or specifications herein. Chipown Microelectronics Co. Ltd. does not assume any responsibility for use of any its products for any particular purpose, nor does Chipown Microelectronics Co. Ltd assume any liability arising out of the application or use of any its products or circuits. Chipown Microelectronics Co. Ltd does not convey any license under its patent rights or other rights of others.