#### **Description**

The AP30N65MP is silicon N-channel Enhanced VDMOSFETs, is obtained by the self-aligned planar Technology which reduce the conduction loss, improve switching performance and enhance the avalanche energy. The transistor can be used in various power switching circuit for system miniaturization and higher efficiency.

#### **General Features**

$V_{DS} = 650V I_{D} = 30A$

$R_{DS(ON)} < 270 \text{m}\Omega$  @  $V_{GS}=10V$  (Type: 230m $\Omega$ )

#### **Application**

Uninterruptible Power Supply(UPS)

Power Factor Correction (PFC)

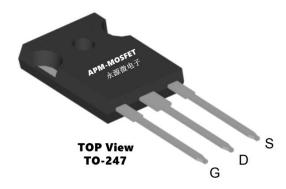

**Package Marking and Ordering Information**

|            | <u> </u>  |                    |          |

|------------|-----------|--------------------|----------|

| Product ID | Pack      | Marking            | Qty(PCS) |

| AP30N65MP  | TO-247-3L | AP30N65MP XXX YYYY | 360      |

### Absolute Maximum Ratings (T<sub>c</sub>=25<sup>°</sup>Cunless otherwise noted)

| Symbol         | Parameter                                        | Value    | Unit |

|----------------|--------------------------------------------------|----------|------|

| VDSS           | Drain-Source Voltage (V <sub>GS</sub> = 0V)      | 650      | V    |

| ID@TC=25°C     | Continuous Drain Current                         | 30       | Α    |

| ID@TC=100°C    | Continuous Drain Current                         | 16       | Α    |

| IDM            | Pulsed Drain Current (note1)                     | 100      | Α    |

| VGS            | Gate-Source Voltage                              | ±30      | V    |

| Eas            | Single Pulse Avalanche Energy (note2)            | 1500     | mJ   |

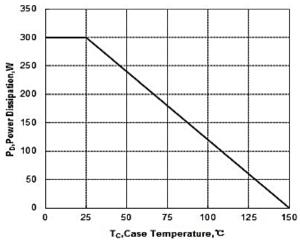

| P <sub>D</sub> | Power Dissipation (T <sub>C</sub> = 25°C)        | 300      | W    |

| TJ, Tstg       | Operating Junction and Storage Temperature Range | -55~+150 | °C   |

| RthJC          | Thermal Resistance, Junction-to-Case             | 0.42     | °C/W |

| RthJA          | Thermal Resistance, Junction-to-Ambient          | 62.5     | °C/W |

#### Electrical Characteristics (T<sub>J</sub>=25°C, unless otherwise noted)

| Symbol          | Parameter                          | Test Conditions                                                             | Min | Тур  | Max  | Unit |

|-----------------|------------------------------------|-----------------------------------------------------------------------------|-----|------|------|------|

| V(BR)DSS        | Drain-Source Breakdown Voltage     | V <sub>GS</sub> = 0V, I <sub>D</sub> = 250μA                                | 650 | 690  |      | V    |

| IDSS            | Zero Gate Voltage Drain Current    | V <sub>DS</sub> = 500V, V <sub>GS</sub> = 0V, T <sub>J</sub> = 25°C         |     |      | 1    | μA   |

| IGSS            | Gate-Source Leakage                | V <sub>GS</sub> = ±30V                                                      |     |      | ±100 | nA   |

| VGS(th)         | Gate-Source Threshold Voltage      | $V_{DS} = V_{GS}, I_D = 250 \mu A$                                          | 2.0 | 3.0  | 4.0  | V    |

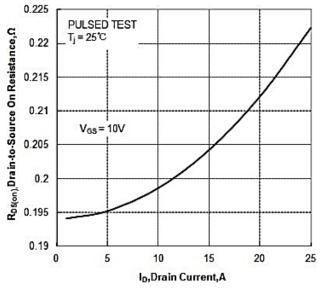

| RDS(on)         | Drain-Source On-Resistance (Note3) | V <sub>GS</sub> = 10V, I <sub>D</sub> = 9A                                  |     | 230  | 270  | mΩ   |

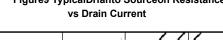

| Ciss            | Input Capacitance                  | ., .,                                                                       |     | 3450 |      |      |

| Coss            | Output Capacitance                 | $V_{GS} = 0V$ ,<br>$V_{DS} = 25V$ , f= 1.0MHz                               |     | 214  |      | pF   |

| Crss            | Reverse Transfer Capacitance       | ·                                                                           |     | 10   |      |      |

| Qg              | Total Gate Charge                  | VDD =400V,ID=30A,<br>VGS =10V                                               |     | 64   |      |      |

| Q <sub>gs</sub> | Gate-Source Charge                 |                                                                             |     | 17   |      | nC   |

| Q <sub>gd</sub> | Gate-Drain Charge                  |                                                                             |     | 23   |      |      |

| td(on)          | Turn-on Delay Time                 |                                                                             |     | 37   |      |      |

| t <sub>r</sub>  | Turn-on Rise Time                  | VDS=250V, ID=30A,                                                           |     | 64   |      | ]    |

| td(off)         | Turn-off Delay Time                | VGS =10V                                                                    |     | 87   |      | ns   |

| tf              | Turn-off Fall Time                 |                                                                             |     | 46   |      | -    |

| Is              | Continuous Body Diode Current      | T <sub>C</sub> = 25 °C                                                      |     |      | 30   | Α    |

| ISM             | Pulsed Diode Forward Current       | 10-20 0                                                                     |     |      | 100  |      |

| V <sub>SD</sub> | Body Diode Voltage                 | $T_J = 25^{\circ}C$ , $I_{SD} = 30A$ , $V_{GS} = 0V$                        |     |      | 1.5  | V    |

| trr             | Reverse Recovery Time              | V <sub>GS</sub> = 0V,I <sub>S</sub> = 30A, di <sub>F</sub> /dt =100A<br>/µs |     | 490  |      | ns   |

| Q <sub>rr</sub> | Reverse Recovery Charge            |                                                                             |     | 6246 |      | μC   |

#### Note:

- 1. The data tested by surface mounted on a 1 inch2 FR-4 board with 2OZ copper.

- 2. The EAS data shows Max. rating . L=4.1Mh  $\,$  IAS=30A, VDD=50V, RG=25  $\!\Omega$ , Starting TJ = 25  $^{\circ}C$

- 3、The test condition is Pulse Test: Pulse width ≤  $300\mu$ s, Duty Cycle ≤ 1%

- 5、The data is theoretically the same as ID and IDM, in real applications, should be limited by total power dissipation.

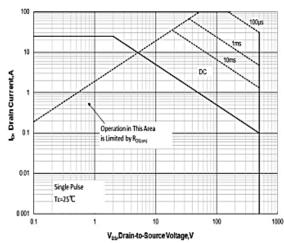

## **Typical Characteristics**

Figure 1 Maximum Forward Bias Safe Operating Area

Figure 2 Maximum Power dissipation vs Case Temperature

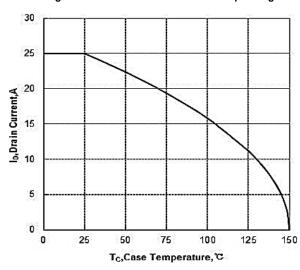

Figure 3 Maximum Continuous Drain Current vs Case Temperature

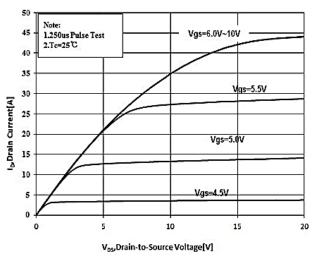

**Figure 4 Typical Output Characteristics**

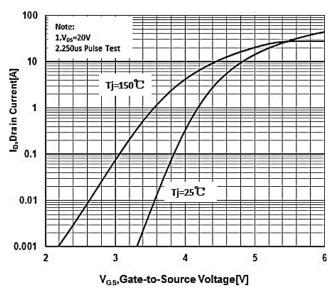

Figure 6 TypicalTransferCharacteristics

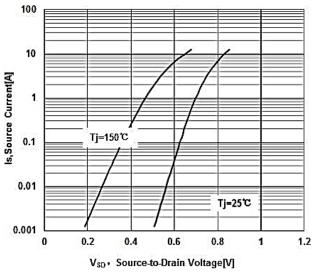

Figure7 TypicalBody DiodeTransfer Characteristics

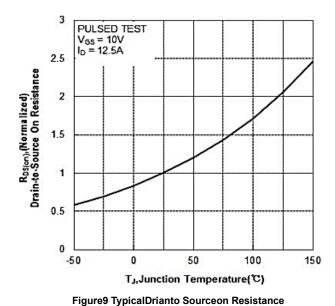

Figure 8 Typical Drain to Source ON Resistance vs JunctionTemperature

Figure11 TypicalCapacitancevs Drainto SourceVoltage

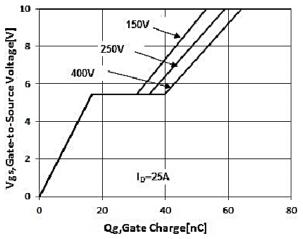

Figure 12 Typical Gate Chargevs Gate to Source Voltage

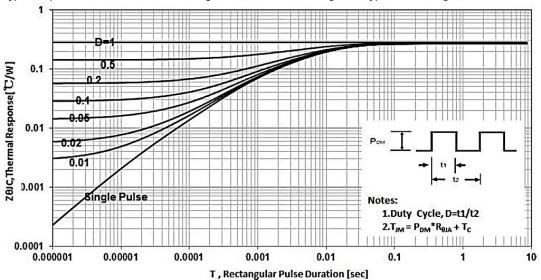

Figure 5 Maximum Effective Thermal Impedance, Junction to Case

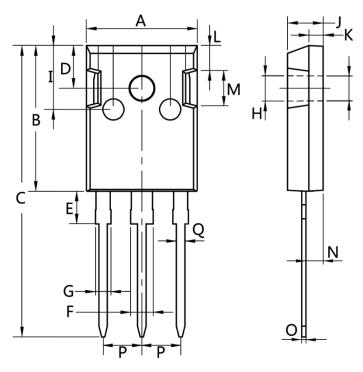

# Package Mechanical Data-TO-247-3L

| Dim. | Min.     | Max.  |

|------|----------|-------|

| A    | 15.0     | 16. 0 |

| В    | 20.0     | 21.0  |

| С    | 41.0     | 42.0  |

| D    | 5.0      | 6.0   |

| Е    | 4.0      | 5.0   |

| F    | 2.5      | 3.5   |

| G    | 1.75     | 2.5   |

| Н    | 3.0      | 3.5   |

| 1    | 8.0      | 10.0  |

| J    | 4.9      | 5.1   |

| К    | 1.9      | 2.1   |

| L    | 3.5      | 4.0   |

| M    | 4.75     | 5.25  |

| N    | 2.0      | 3.0   |

| 0    | 0.55     | 0.75  |

| Р    | Тур 5.08 |       |

| Q    | 1.2      | 1.3   |

## AP30N65MP

#### 650V N-Channel Enhancement Mode MOSFET

#### **Attention**

- 1,Any and all APM Microelectronics products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your APM Microelectronics representative nearest you before using any APM Microelectronics products described or contained herein in such applications.

- 2,APM Microelectronics assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all APM Microelectronics products described or contained herein.

- 3, Specifications of any and all APM Microelectronics products described or contained here instipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

- 4, APM Microelectronics Semiconductor CO., LTD. strives to supply high quality high reliability products. However, any and all semiconductor products fail with some probability. It is possible that these probabilistic failures could give rise to accidents or events that could endanger human lives that could give rise to smoke or fire, or that could cause damage to other property. Whendesigning equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- 5,In the event that any or all APM Microelectronics products (including technical data, services) described or contained herein are controlled under any of applicable local export control laws and regulations, such products must not be exported without obtaining the export license from the authorities concerned in accordance with the above law.

- 6, No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written permission of APM Microelectronics Semiconductor CO., LTD.

- 7, Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. APM Microelectronics believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

- 8, Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "DeliverySpecification" for the APM Microelectronics product that you Intend to use.

# AP30N65MP

## **650V N-Channel Enhancement Mode MOSFET**

| Edition | Date      | Change          |

|---------|-----------|-----------------|

| REV1.0  | 2024/1/31 | Initial release |

Copyright Attribution"APM-Microelectronice"