**AP3720**

### **General Description**

The AP3720 is a low startup current, current mode PWM controller with green-mode operation. The PWM switching frequency at normal operation is 65k, but when the output power drops below the specifically level, the device enters the frequency-drop mode and the typical operating frequency is 20kHz (no audible noise). Additionally, when the load drops to a very low level or zero, the IC operates in so called 'burst mode' to minimize switching loss.

The IC integrated a lot of functions such as the Lead-Edge Blanking (LEB) of the current sensing, internal slope compensation, line compensation, and several protection features. The protection functions include cycle-by-cycle current limit (OCP), VCC over voltage protection (OVP), OTP and OLP.

The AP3720 is available in DIP-8 and SOIC-8 packages.

#### **Features**

- Low Startup Current (2.5μA) and Low Operating Current (1.2mA)

- Off-line Converter Applied in Sub 25W Range

- Skip Cycle Mode Achieves Low Standby Power (<200mW)</li>

- Cycle-by-Cycle Power Limited

- Frequency-drop Mode

- Soft Start with 2ms

- Programmable Drive Current for BJT

- Leading Edge Blanking

- Pre-shutdown Decreases Turn-off Losses

- Reliable Protection:

Accurate OCP with Line Compensation

Short Circuit Protection

Over Voltage Protection for VCC

Hysteretic Thermal Shutdown Protection

### **Applications**

- STB

- Cable Modem

- ADSL Modem

- DVD Recorder

Figure 1. Package Types of AP3720

**AP3720**

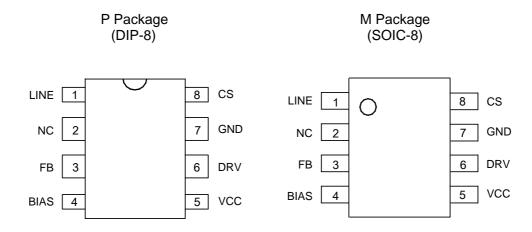

## **Pin Configuration**

Figure 2. Pin Configuration of AP3720 (Top View)

## **Pin Description**

| Pin Number | Pin Name | Function                                                                                                                                                                                                                                                    |

|------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | LINE     | Line compensation for OLP                                                                                                                                                                                                                                   |

| 2          | NC       | No connection                                                                                                                                                                                                                                               |

| 3          | FB       | Connect opto-coupler to this pin. The voltage of FB controls the mode of operation in one of the three modes: burst mode, frequency-drop mode (20kHz) and normal mode (65kHz). When the voltage of FB reaches a limit-point, the system enters the OLP mode |

| 4          | BIAS     | This pin sets the driver current inside AP3720 with an external resistor to GND                                                                                                                                                                             |

| 5          | VCC      | This pin is the positive supply voltage input. During start up, the power is supplied from line voltage. When $V_{CC}$ reaches 20V, the system begins running and the power is supplied from the auxiliary transformer winding                              |

| 6          | DRV      | This pin supplies the drive current for the external power NPN switch                                                                                                                                                                                       |

| 7          | GND      | This pin is the control ground                                                                                                                                                                                                                              |

| 8          | CS       | This pin senses the primary current and routes it to internal comparator. By changing the value of the sense resistor, the primary peak current set point is adjusted according to the output power demand                                                  |

**AP3720**

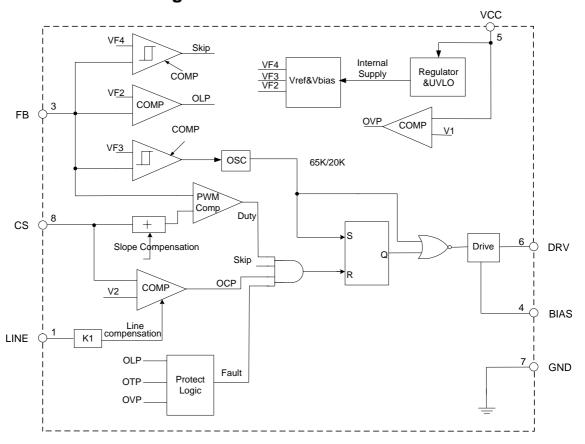

### **Functional Block Diagram**

Figure 3. Functional Block Diagram of AP3720

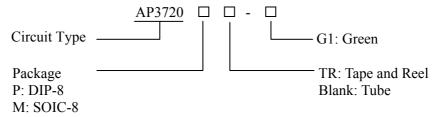

## **Ordering Information**

| Package | Temperature<br>Range | Part Number  | Number Marking ID Packing |             |  |

|---------|----------------------|--------------|---------------------------|-------------|--|

| DIP-8   | -40 to 85°C          | AP3720P-G1   | AP3720P-G1                | Tube        |  |

| SOIC-8  | -40 to 85°C          | AP3720MTR-G1 | 3720M-G1                  | Tape & Reel |  |

BCD Semiconductor's Pb-free products, as designated with "G1" suffix in the part number, are RoHS compliant and green.

**AP3720**

### **Absolute Maximum Ratings (Note 1)**

| Parameter                                 | Symbol                 | Value              |      | Unit |

|-------------------------------------------|------------------------|--------------------|------|------|

| Supply Voltage                            | $V_{CC}$               | -0.3 to 28         |      | V    |

| Voltage at DRV, FB, CS, BIAS, LINE        |                        | -0.3 to 7          |      | V    |

| Output Current at DRV                     | $I_{DRV}$              | Internally limited |      | A    |

| Payvan Dissination at T =25%C             | D                      | DIP-8              | 1.35 | W    |

| Power Dissipation at T <sub>A</sub> =25°C | $P_{D}$                | SOIC-8             | 0.55 | W    |

| Operating Junction Temperature            | $T_{J}$                | 160                |      | °C   |

| Storage Temperature                       | $T_{STG}$              | -65 to 150         |      | °C   |

| Lead Temperature (Soldering, 10 sec)      | $T_{LEAD}$             | 300                |      | °C   |

| Thermal Resistance                        | $\theta_{\mathrm{JA}}$ | DIP-8              | 83   | 0C/W |

| (Junction-to-Ambient)                     |                        | SOIC-8             | 186  | °C/W |

| ESD (Machine Model)                       |                        | 400                |      | V    |

Note 1: Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "Recommended Operating Conditions" is not implied. Exposure to "Absolute Maximum Ratings" for extended periods may affect device reliability.

## **Recommended Operating Conditions**

| Parameter           | Symbol   | Min | Max | Unit |

|---------------------|----------|-----|-----|------|

| Supply Voltage      | $V_{CC}$ | 12  | 18  | V    |

| Ambient Temperature | $T_A$    | -40 | 85  | °C   |

**AP3720**

## **Electrical Characteristics**

$V_{CC}$ =15V,  $T_A$ =25°C, unless otherwise specified.

| Parameter                            | Conditions                 | Min   | Тур   | Max   | Unit |

|--------------------------------------|----------------------------|-------|-------|-------|------|

| Supply Voltage ( VCC Pin )           |                            | •     |       | •     | •    |

| Startup Current                      | V <sub>CC</sub> =15V       |       | 2.5   | 8     | μΑ   |

| Operating Current                    | $V_{FB}=V_{CS}=0V$         |       | 1.2   | 2.5   | mA   |

| UVLO (on)                            |                            | 18.5  | 20    | 21.5  | V    |

| UVLO (off)                           |                            | 7.1   | 8     | 8.9   | V    |

| VCC OVP                              |                            |       | 26.5  | 28.5  | V    |

| PWM Section / Oscillator Section     | on                         |       |       |       |      |

| Maximum Duty Cycle                   |                            | 67    | 75    | 83    | %    |

| Normal Frequency                     | V <sub>FB</sub> =3V        | 60    | 65    | 70    | kHz  |

| Green Frequency                      | V <sub>FB</sub> =2V        |       | 20    |       | kHz  |

| Francisco Carital Dalas Tima         | From 65k to 20k            |       | 64    |       | ms   |

| Frequency Switch Delay Time          | From 20k to 65k            |       | 0     |       | ms   |

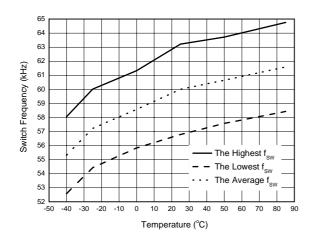

| Frequency Temperature Stability      | -40°C to 85°C              |       | ±5    | ±8    | %    |

| Frequency Voltage Stability          | V <sub>CC</sub> =8V to 18V |       | 1.5   | 3     | %    |

| <b>Current Sense Section (CS Pin</b> | )                          |       |       |       |      |

| Maximum CS Voltage                   | V <sub>LINE</sub> =0.95V   | 0.983 | 1.032 | 1.081 | V    |

| Line Compensation Coefficient        |                            |       | 4.6   | 9.5   | %    |

| LEB Time                             |                            | 250   | 350   | 400   | ns   |

| Soft Start Time                      |                            |       | 2     |       | ms   |

| Feedback Input Section (FB Pin       | n )                        |       |       |       |      |

| The Ratio of FB to CS                | $G_{FB}$                   | 2.5   | 3     | 3.5   | V/V  |

| Input Impedance                      | $R_{FB}$                   | 7     | 10    | 13    | kΩ   |

| Source Current                       | $I_{FB}$                   | -1    | -0.5  |       | mA   |

| Output Section ( Gate Pin )          |                            |       |       |       |      |

| Output Maximum Current               | R <sub>BIAS</sub> =1M      |       | 32    |       | mA   |

| Output Sink Current                  | $V_{FB}=V_{CS}=0V$         |       |       | 0.5   | mA   |

| <b>Protection Section</b>            |                            | •     | •     | •     | •    |

| OLP Delay Time                       | V <sub>FB</sub> =5.1V      |       | 64    |       | ms   |

| Shutdown Temperature                 |                            |       | 160   |       | °C   |

**AP3720**

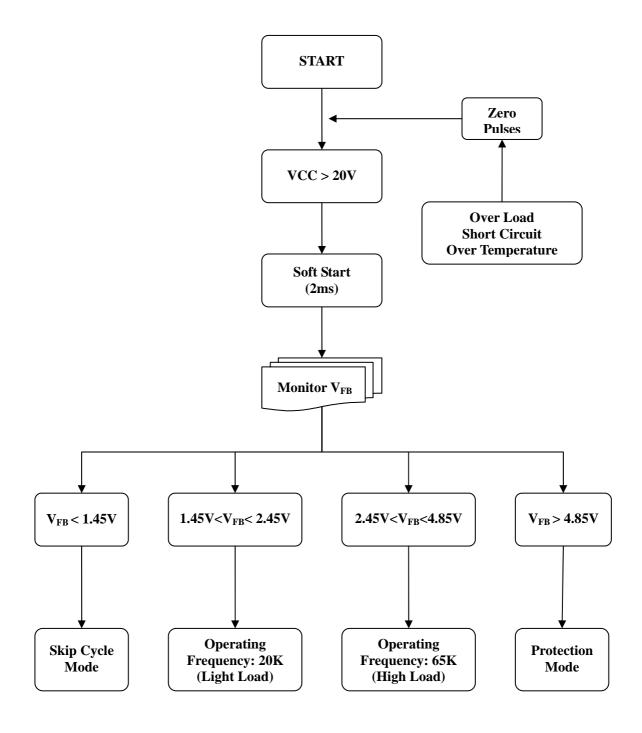

### **Control Flow Chart**

**AP3720**

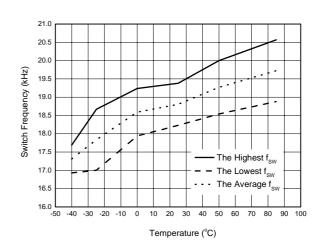

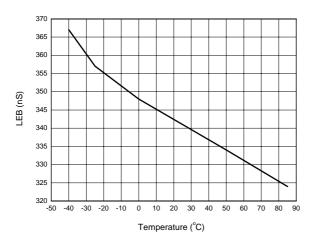

## **Typical Performance Characteristics**

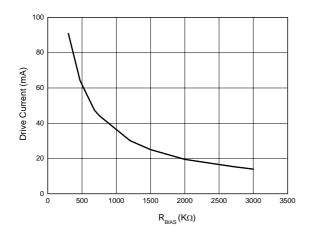

Figure 4. Drive Current vs. RBIAS

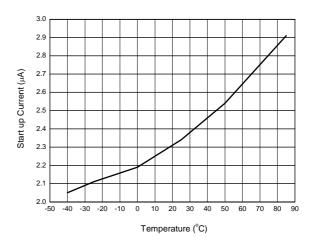

Figure 5. Start-up Current vs. Temperature

Figure 6. Switch Frequency (65k) vs. Temperature

Figure 7. Switch Frequency (20k) vs. Temperature

**AP3720**

# **Typical Performance Characteristics (Continued)**

Figure 8. LEB vs. Temperature

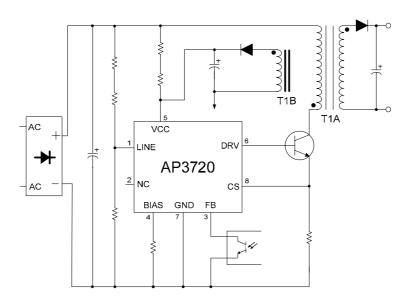

## **Operation Description**

Figure 9. Operation Diagram of AP3720

AP3720

### **Operation Description (Continued)**

#### **Start Sequence**

When the VCC capacitor reaches the  $UVLO_{(on)}$  level (typically 20V), the controller runs. At this time, VCC capacitor supplies the controller and the auxiliary supply takes over before VCC collapses below  $UVLO_{(off)}$ .

#### **Soft Start**

The internal soft start function is activated at start-up with a duration of 2ms (typical). The current sense compensation starts from 1.0V and slowly decreases to zero at the end of the 2ms duration. This function is activated at each auto-restart attempt due to OLP or TSD condition. The feature also helps minimize output overshoot and prevents saturation of transformer during start-up.

#### **FB Pin Operation**

The AP3720 can automatically adjust the operating mode according to the loading condition. The voltage of FB controls the mode of operation in one of the three modes: burst mode, frequency-drop mode (20kHz) and normal mode (65kHz). To prevent saturation of transformer and achieve good transient load performance, the switch from frequency-drop mode to normal mode occurs with no delay time and that from normal mode to frequency-drop mode occurs with 64ms delay time when the load condition changes.

#### **Burst Mode Operation**

At zero load or light load condition, majority of the power dissipation is in proportion to the number of switch events within a fixed period of time. To reduce the loss in this situation, the device enters burst mode control which makes some switching cycle skip when  $V_{\rm FB}$  drops below the burst mode threshold level.

#### Frequency-drop Mode (20kHz)

When the output power drops below a specific level, the device enters the frequency-drop mode and the typical operating frequency is 20kHz. In this mode, the system efficiency at specific load will improve obviously.

#### Normal Mode (65kHz)

At the higher load, the device operates in normal mode and the frequency is 65kHz (typical).

#### **Cycle-by-Cycle Current Limit**

The cycle terminates when the CS voltage exceeds 1.074V.

The AP3720 operates as a current mode controller, whereby output switch conduction is initiated by the oscillator and terminated when the peak inductor current reaches the threshold level established by  $V_{\rm FB}$ . The inductor current is converted to a voltage by inserting the ground referenced sense resistor  $R_{\rm S}$  in series with the emitter of the power transistor.

When the power supply output is overload or the control loop is open, the current sense comparator threshold will be internally clamped to about 1.074V. Therefore the maximum peak inductor current is:

$$I_{PK(\text{max})} = \frac{1.074 - k * V_{LINE}}{R_{s}}$$

(k=0.0444)

#### Leading Edge Blanking (LEB)

At the instant the power transistor is turned on, there usually exists a high current spike through the BJT, caused by primary-side capacitance and secondary-side rectifier reverse recovery. Excessive voltage across the  $R_{\rm S}$  can lead to incorrect feedback operation in the current mode PWM control. To counter this effect, the AP3720 employs a leading edge blanking (LEB) circuit. This circuit inhibits the PWM comparator for a short time ( $t_{\rm LEB}$ ) after the BJT is turn on.

#### **Line Compensation**

The AP3720 has an adjustable line compensation so that achieves constant output power limit over the universal input voltage range.

#### **Drive Current Control**

The AP3720 drive current is programmable through an external resistor to GND (see Figure 4).

**AP3720**

### **Operation Description (Continued)**

#### **Protection Circuit**

The AP3720 has several self-protective functions such as over load protection (OLP), open loop protection, over voltage protection for VCC, thermal shutdown (TSD). Because these protection circuits are fully integrated into the IC without external components, the reliability can be improved without increasing cost. Once the fault condition occurs, switching is terminated and the power transistor remains off. This causes  $V_{\text{CC}}$  to fall. When  $V_{\text{CC}}$ reaches the UVLO stop voltage of 8V, the current consumed by the AP3720 decreases to the start-up current (typically 2.5µA) and the current supplied from the DC link charges the VCC capacitor. When V<sub>CC</sub> reaches the start voltage of 20V, the AP3720 resumes its normal operation. In this manner, the auto-restart can alternately enable and disable the switching of the power transistor until the fault condition is eliminated.

Over Load Protection: In this situation, the protection circuit should be activated to protect the SMPS. However, even when the SMPS is in the normal operation, the over load protection circuit can be activated during the load transition. To avoid this undesired operation, the over load protection circuit is designed to be activated after a specified time (typically 64ms) to determine whether it is a transient situation or an overload situation. Because of the cycle-by-cycle current limit, the maximum peak current through the BJT is limited, and therefore the maximum input power is restricted. If the output consumes exceeds this maximum power, the voltage decreases below the rated voltage. This reduces the

current through the opto-coupler LED, which also reduces the opto-coupler transistor current, thus increasing  $V_{FB}$ . If  $V_{FB}$  exceeds 4.85V and holds the situation beyond 64ms, the over load protection circuit is activated.

**Open Loop Protection:** In this abnormal situation, OLP or OVP will be activated.

Over Voltage Protection: If the control loop is open, the current through the opto-coupler transistor becomes almost zero. Then  $V_{FB}$  climbs up to the over load situation and the over load protection is activated. But maybe the output voltage exceed the rated voltage before the over load protection is activated, resulting in the breakdown of the devices in the secondary side and the primary side. To prevent this situation, an over voltage protection circuit is employed. In general,  $V_{CC}$  is proportional to the output voltage. If  $V_{CC}$  exceeds 26.5V, an OVP circuit is activated resulting in the termination of the switching operation. To avoid undesired activation of OVP during normal operation,  $V_{CC}$  should be designed to be below 20V.

#### Thermal Shutdown

Thermal shutdown is provided by a precision analog circuit that turns the power transistor off when the junction temperature exceeds the thermal shutdown temperature (typically 160°C). When the junction temperature drops about the hysteretic temperature, normal operation resumes.

AP3720

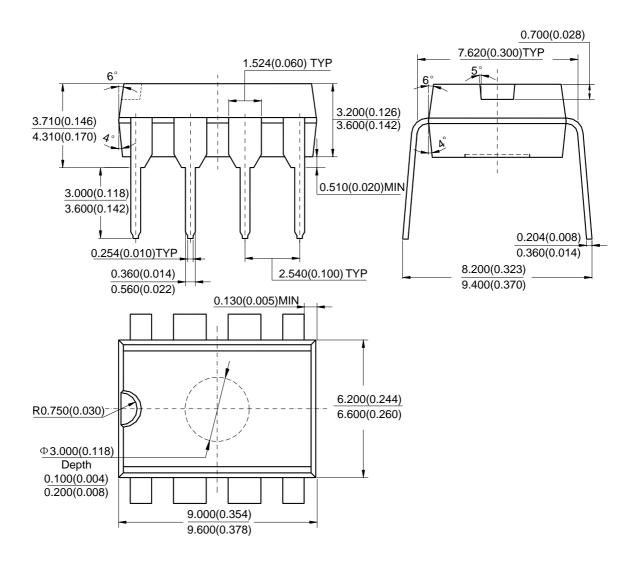

### **Mechanical Dimensions**

DIP-8 Unit: mm(inch)

Note: Eject hole, oriented hole and mold mark is optional.

**AP3720**

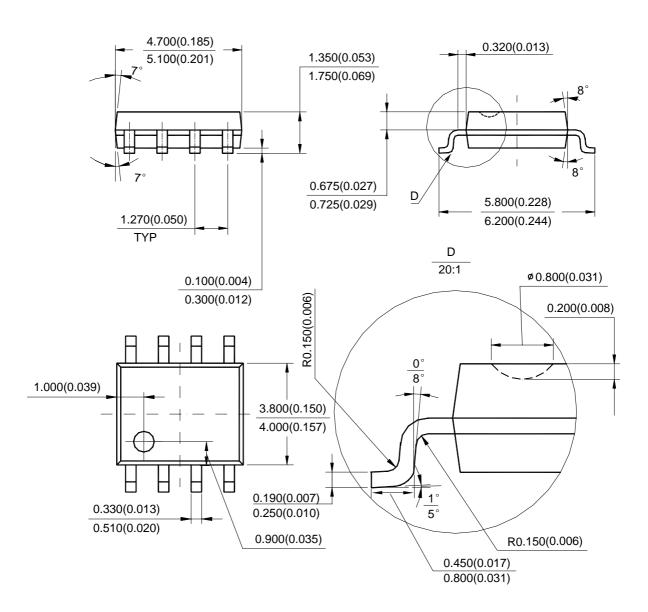

## **Mechanical Dimensions (Continued)**

SOIC-8 Unit: mm(inch)

Note: Eject hole, oriented hole and mold mark is optional.

#### **BCD Semiconductor Manufacturing Limited**

http://www.bcdsemi.com

#### IMPORTANT NOTICE

BCD Semiconductor Manufacturing Limited reserves the right to make changes without further notice to any products or specifications herein. BCD Semiconductor Manufacturing Limited does not assume any responsibility for use of any its products for any particular purpose, nor does BCD Semiconductor Manufacturing Limited assume any liability arising out of the application or use of any its products or circuits. BCD Semiconductor Manufacturing Limited does not convey any license under its patent rights or other rights nor the rights of others.

#### MAIN SITE

- Headquarters

BCD Semiconductor Manufacturing Limited

No. 1600, Zi Xing Road, Shanghai ZiZhu Science-based Industrial Park, 200241, China Tel: +86-21-24162266, Fax: +86-21-24162277

#### REGIONAL SALES OFFICE

Shenzhen Office

Shanghai SIM-BCD Semiconductor Manufacturing Co., Ltd., Shenzhen Office Unit A Room 1203, Skyworth Bldg., Gaoxin Ave.1.S., Nanshan District, Shenzhen,

China Tel: +86-755-8826 7951 Fax: +86-755-8826 7865

#### - Wafer Fab

Shanghai SIM-BCD Semiconductor Manufacturing Co., Ltd. 800 Yi Shan Road, Shanghai 200233, China Tel: +86-21-6485 1491, Fax: +86-21-5450 0008

#### **Taiwan Office**

BCD Semiconductor (Taiwan) Company Limited 4F, 298-1, Rui Guang Road, Nei-Hu District, Taipei,

Taiwan Tel: +886-2-2656 2808 Fax: +886-2-2656 2806

USA Office BCD Semiconductor Corp. 30920 Huntwood Ave. Hayward, CA 94544, USA Tel: +1-510-324-2988 Fax: +1-510-324-2788