# APS12200, APS12210, and APS12230

## **High-Temperature Precision Hall-Effect Latches**

#### **FEATURES AND BENEFITS**

- Symmetrical latch switch points

- · ASIL A functional safety compliance

- Automotive-grade ruggedness and fault tolerance

- ☐ Extended AEC-Q100 qualification

- □ Reverse-battery and 40 V load dump protection

- □ Operation from –40°C to 175°C junction temperature

- □ High EMC immunity, ±12 kV HBM ESD

- □ Output short-circuit and overvoltage protection

- □ Superior temperature stability

- ☐ Resistant to physical stress

- Operation from unregulated supplies, 2.8 to 24 V

- Chopper stabilization

- · Solid-state reliability

- · Industry-standard packages and pinouts

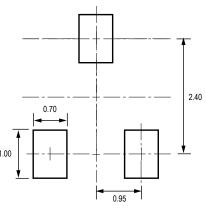

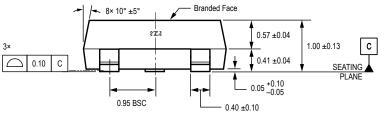

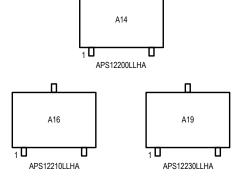

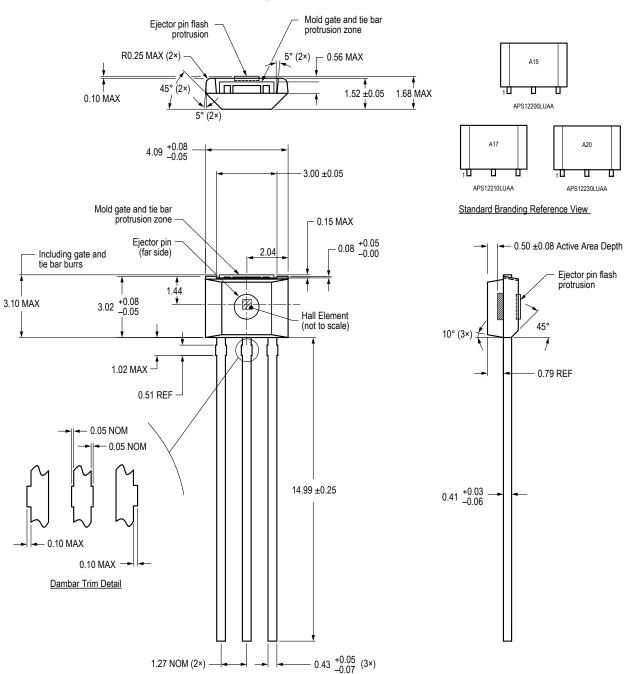

# PACKAGES: Not to scale 3-pin SIP (suffix UA) 3-pin SOT23W (suffix LH)

#### **DESCRIPTION**

The APS12200, APS12210, and APS12230 are three-wire, planar Hall-effect sensor integrated circuits (ICs). These devices were developed in accordance with ISO 26262:2011 and support a functional safety level of ASIL A.

This family of precision Hall-effect latch ICs feature extended AEC-Q100 qualification and are ideal for high-temperature operation up to 175°C junction temperatures. In addition, the APS12200/10/30 include a number of features designed specifically to maximize system robustness, such as reversebattery protection, output current limiter, overvoltage, and EMC protection.

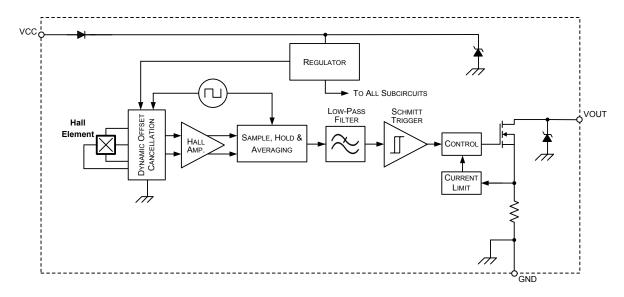

The single silicon chip includes: a voltage regulator, a Hall plate, small signal amplifier, chopper stabilization, Schmitt trigger, and a short-circuit-protected open-drain output. A south pole of sufficient strength turns the output on; a north pole of sufficient strength is necessary to turn the output off. The devices include on-board transient protection for all pins, permitting operation directly from a vehicle battery or regulator with supply voltages from 2.8 to 24 V.

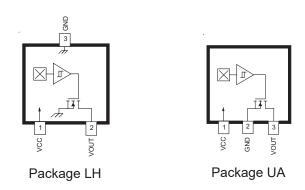

Two package styles provide a choice of through-hole or surface mounting. Package type LH is a modified 3-pin SOT23W surface-mount package, while UA is a three-pin ultramini SIP for through-hole mounting. Both packages are lead (Pb) free and RoHS compliant, with 100% matte-tin-plated leadframes.

## **Functional Block Diagram**

#### **SELECTION GUIDE**

| Part Number                   | Packing <sup>[1]</sup>         | Mounting                   | Branding | B <sub>RP</sub> (Min) | B <sub>OP</sub> (Max) |

|-------------------------------|--------------------------------|----------------------------|----------|-----------------------|-----------------------|

| APS12200LLHALX                | 13-in. reel, 10000 pieces/reel | 3-pin SOT23W surface mount | A14      |                       |                       |

| APS12200LLHALT <sup>[2]</sup> | 7-in. reel, 3000 pieces/reel   | 3-pin SOT23W surface mount | A14      | –35 G                 | 35 G                  |

| APS12200LUAA                  | Bulk, 500 pieces/bag           | 3-pin SIP through hole     | A15      |                       |                       |

| APS12210LLHALX                | 13-in. reel, 10000 pieces/reel | 3-pin SOT23W surface mount | A16      |                       |                       |

| APS12210LLHALT <sup>[2]</sup> | 7-in. reel, 3000 pieces/reel   | 3-pin SOT23W surface mount | A16      | –80 G                 | 80 G                  |

| APS12210LUAA                  | Bulk, 500 pieces/bag           | 3-pin SIP through hole     | A17      |                       |                       |

| APS12230LLHALX                | 13-in. reel, 10000 pieces/reel | 3-pin SOT23W surface mount | A19      |                       |                       |

| APS12230LLHALT <sup>[2]</sup> | 7-in. reel, 3000 pieces/reel   | 3-pin SOT23W surface mount | A19      | –180 G                | 180 G                 |

| APS12230LUAA                  | Bulk, 500 pieces/bag           | 3-pin SIP through hole     | A20      |                       |                       |

#### **ABSOLUTE MAXIMUM RATINGS**

| Characteristic               | Symbol                | Notes                                          | Rating      | Units |

|------------------------------|-----------------------|------------------------------------------------|-------------|-------|

| Forward Supply Voltage [1]   | V <sub>cc</sub>       |                                                | 30          | V     |

| Reverse Supply Voltage [1]   | V <sub>RCC</sub>      |                                                | -18         | V     |

| Output Off Voltage [1]       | V <sub>OUT</sub>      |                                                | 30          | V     |

| Output Current [2]           | I <sub>OUT</sub>      |                                                | 60          | mA    |

| Reverse Output Current       | I <sub>ROUT</sub>     |                                                | <b>–</b> 50 | mA    |

| Magnetic Flux Density [3]    | В                     |                                                | Unlimited   | _     |

| Mariana India Tanana         | T (may)               |                                                | 165         | °C    |

| Maximum Junction Temperature | T <sub>J</sub> (max)  | For 500 hours                                  | 175         | °C    |

| Storage Temperature          | T <sub>stg</sub>      |                                                | -65 to 170  | °C    |

|                              | V <sub>ESD(HBM)</sub> | Human Body Model according to AEC-Q100-002     | ±12         | kV    |

| ESD Voltage [4]              | V <sub>ESD(CDM)</sub> | Charged Device Model according to AEC-Q100-011 | ±1          | kV    |

|                              | V <sub>ESD(SYS)</sub> | ISO 10605, System Level                        | ±15         | kV    |

<sup>[1]</sup> This rating does not apply to extremely short voltage transients such as load dump and/or ESD. Those events have individual ratings, specific to the respective transient voltage event.

<sup>[1]</sup> Contact Allegro for additional packing options.

<sup>[2]</sup> Available through authorized Allegro distributors only.

<sup>[2]</sup> Through short-circuit current limiting device.

<sup>[3]</sup> Guaranteed by design.

$<sup>^{[4]}</sup>$  System level ESD rating based on characterization performed under ISO 10605:2008 (2 k $\Omega$  / 330 pF) with the application circuit shown in Figure 4.

#### PINOUT DIAGRAMS AND TERMINAL LIST TABLE

#### **Terminal List**

| Name | Description                   | Number     |            |  |

|------|-------------------------------|------------|------------|--|

| Name | Description                   | Package LH | Package UA |  |

| VCC  | Connects power supply to chip | 1          | 1          |  |

| VOUT | Output from circuit           | 2          | 3          |  |

| GND  | Ground                        | 3          | 2          |  |

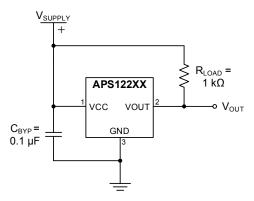

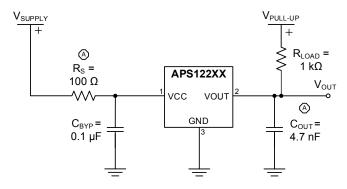

**Figure 1: Typical Application Diagram**

**ELECTRICAL CHARACTERISTICS:** Valid over full operating voltage, ambient temperature range  $T_A = -40$ °C to 150°C, and with  $C_{BYP} = 0.1 \mu F$  (unless otherwise specified)

| Characteristics                       | Symbol                | Test Conditions                                                                       | Min.   | Typ. [1] | Max.       | Unit [2] |

|---------------------------------------|-----------------------|---------------------------------------------------------------------------------------|--------|----------|------------|----------|

| ELECTRICAL CHARACTERISTICS            | 3                     |                                                                                       |        |          |            |          |

| Forward Supply Voltage                | V <sub>CC</sub>       | Operating, T <sub>J</sub> < 175°C                                                     | 2.8    | _        | 24         | V        |

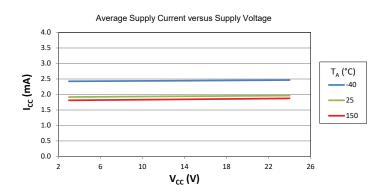

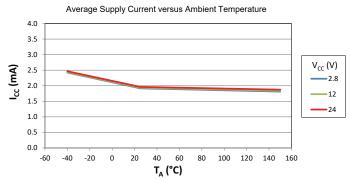

| Supply Current                        | I <sub>cc</sub>       |                                                                                       | 1      | 2        | 3          | mA       |

| Output Leakage Current                | I <sub>OUTOFF</sub>   | V <sub>OUTOFF</sub> = 24 V, B < B <sub>RP</sub>                                       | _      | _        | 10         | μΑ       |

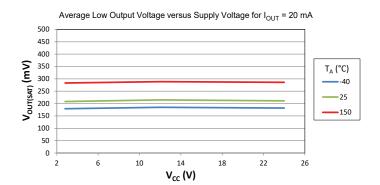

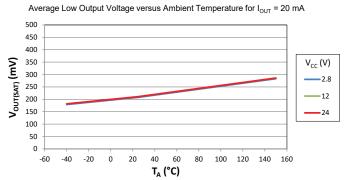

| Output Saturation Voltage             | V <sub>OUT(SAT)</sub> | I <sub>OUT</sub> = 20 mA, B > B <sub>OP</sub>                                         | _      | 200      | 500        | mV       |

| Output Off Voltage                    | V <sub>OUTOFF</sub>   | B < B <sub>RP</sub>                                                                   | _      | _        | 24         | V        |

| Power-On Time                         | t <sub>ON</sub>       | $V_{CC} \ge V_{CC}(min), B < B_{RP}(min) - 10 G,$<br>B > B <sub>OP</sub> (max) + 10 G | _      | _        | 25         | μs       |

| Power-On State, Output <sup>[3]</sup> | POS                   | $V_{CC} \ge V_{CC}(min), t < t_{ON}$                                                  |        | Low      |            | _        |

| Chopping Frequency                    | f <sub>C</sub>        |                                                                                       | _      | 800      | _          | kHz      |

| Output Rise Time <sup>[4]</sup>       | t <sub>r</sub>        | $R_{LOAD} = 1 \text{ k}\Omega, C_L = 20 \text{ pF}$                                   | _      | 0.2      | 2          | μs       |

| Output Fall Time <sup>[4]</sup>       | t <sub>f</sub>        | $R_{LOAD} = 1 \text{ k}\Omega, C_L = 20 \text{ pF}$                                   | _      | 0.1      | 2          | μs       |

| TRANSIENT PROTECTION CHARA            | ACTERISTICS           |                                                                                       |        |          |            |          |

| Output Short-Circuit Current Limit    | I <sub>OM</sub>       |                                                                                       | 30     | _        | 60         | mA       |

| Output Zener Clamp Voltage            | V <sub>Zoutput</sub>  | I <sub>OUT</sub> = 3 mA, T <sub>A</sub> = 25°C, Output Off                            | 30     | _        | _          | V        |

| Reverse Battery Current               | I <sub>RCC</sub>      | V <sub>RCC</sub> = -18 V, T <sub>A</sub> = 25°C                                       | _      | _        | <b>–</b> 5 | mA       |

| Supply Zener Clamp Voltage            | V <sub>Z</sub>        | $I_{CC} = I_{CC}(max) + 3 \text{ mA}, T_A = 25^{\circ}\text{C}$                       | 30     | _        | _          | V        |

| MAGNETIC CHARACTERISTICS              |                       |                                                                                       |        |          |            |          |

|                                       |                       | APS12200                                                                              | 5      | 20       | 35         | G        |

| Operate Point                         | B <sub>OP</sub>       | APS12210                                                                              | 25     | 50       | 80         | G        |

|                                       |                       | APS12230                                                                              | 100    | 150      | 180        | G        |

|                                       |                       | APS12200                                                                              | -35    | -20      | <b>-</b> 5 | G        |

| Release Point                         | B <sub>RP</sub>       | APS12210                                                                              | -80    | -50      | -25        | G        |

|                                       |                       | APS12230                                                                              | -180   | -150     | -100       | G        |

| Hysteresis                            |                       | APS12200                                                                              | 10     | 40       | 70         | G        |

|                                       | B <sub>HYS</sub>      | APS12210                                                                              | 50     | 100      | 160        | G        |

|                                       |                       | APS12230                                                                              | 200    | 300      | 360        | G        |

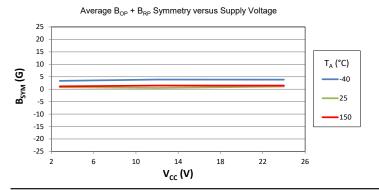

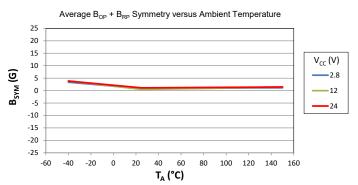

| Symmetry                              | B <sub>SYM</sub>      | B <sub>OP</sub> + B <sub>RP</sub>                                                     | -27.5  | _        | 27.5       | G        |

| Magnetic Offset                       | B <sub>OFF</sub>      | (B <sub>OP</sub> + B <sub>RP</sub> ) / 2                                              | -13.75 | _        | 13.75      | G        |

$<sup>^{[1]}</sup>$  Typical data are at  $T_A$  = 25°C and  $V_{CC}$  = 12 V.  $^{[2]}$  1 G (gauss) = 0.1 mT (millitesla).  $^{[3]}$  Guaranteed by device design and characterization.

$<sup>^{[4]}</sup>C_L$  = oscilloscope probe capacitance.

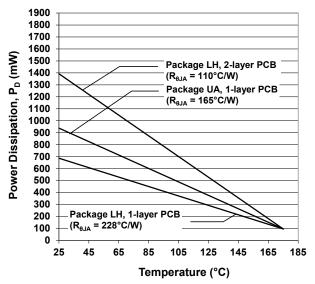

THERMAL CHARACTERISTICS: May require derating at maximum conditions; see application information

| Characteristic             | Symbol         | Test Conditions                                                                            |     | Units |

|----------------------------|----------------|--------------------------------------------------------------------------------------------|-----|-------|

| Package Thermal Resistance |                | Package LH, 1-layer PCB with copper limited to solder pads                                 |     | °C/W  |

|                            | $R_{	heta JA}$ | Package LH, 2-layer PCB with 0.463 in 2 of copper area each side connected by thermal vias | 110 | °C/W  |

|                            |                | Package UA, 1-layer PCB with copper limited to solder pads                                 | 165 | °C/W  |

## **Power Derating Curve** $T_{J(max)} = 175$ °C; $I_{CC} = I_{CC(max)}$ , $I_{OUT} = 0$ mA (Output Off) 2542322120918716543211098765432 $\mathbf{V}_{\mathrm{CC}(\mathrm{max})}$ Maximum Allowable V<sub>cc</sub> (V) Package LH, 2-layer PCB (R<sub>BJA</sub> = 110 °C/W) Package UA, 1-layer (R<sub>BJA</sub> = 165 °C/W) Package LH, 1-layer PCB (R<sub>BJA</sub> = 228 °C/W) $\mathbf{V}_{\text{CC(min)}}$ 25 45 65 85 105 125 145 165 | 185 Temperature (°C) T<sub>J</sub>(max)

#### **Power Dissipation versus Ambient Temperature**

## CHARACTERISTIC PERFORMANCE DATA Electrical Characteristics

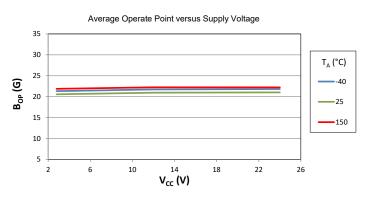

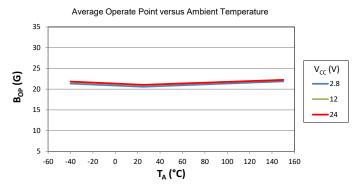

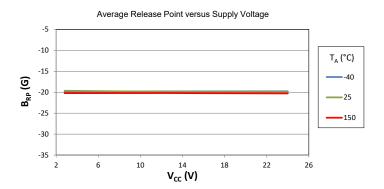

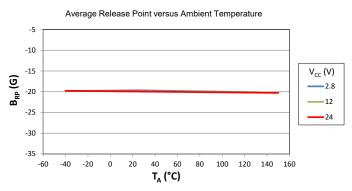

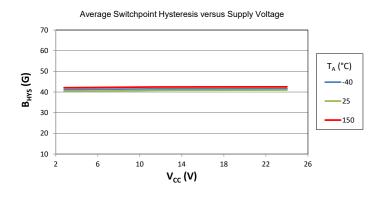

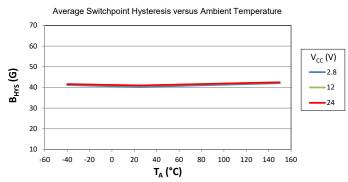

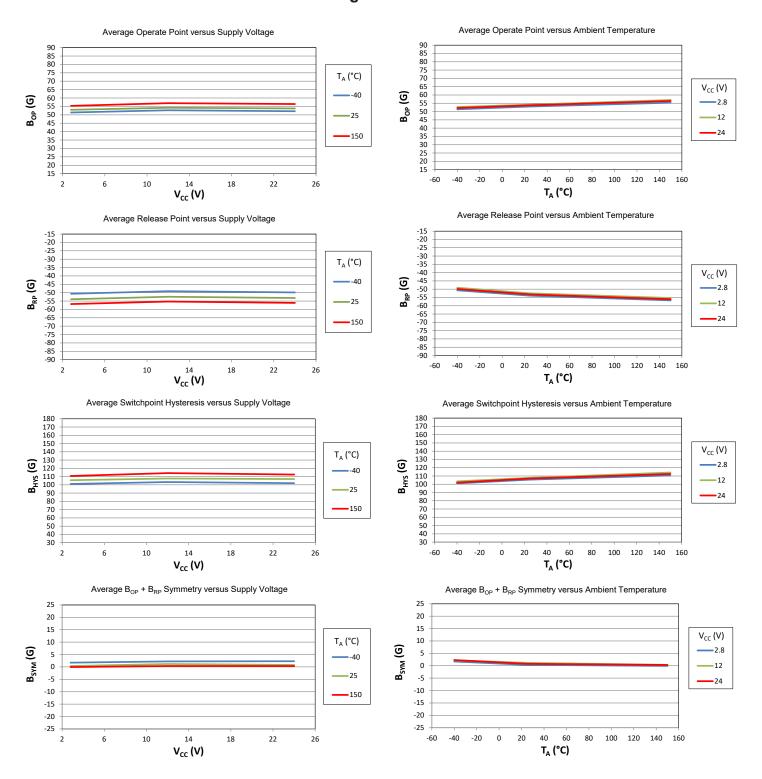

# CHARACTERISTIC PERFORMANCE DATA (continued) APS12200 Magnetic Characteristics

## CHARACTERISTIC PERFORMANCE DATA (continued) APS12210 Magnetic Characteristics

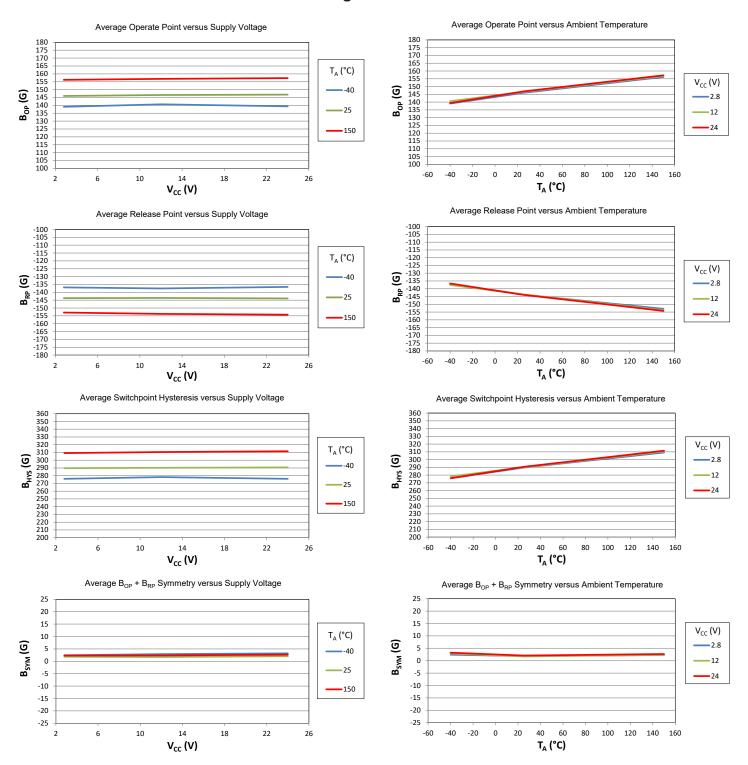

# CHARACTERISTIC PERFORMANCE DATA (continued) APS12230 Magnetic Characteristics

#### **FUNCTIONAL DESCRIPTION**

#### **OPERATION**

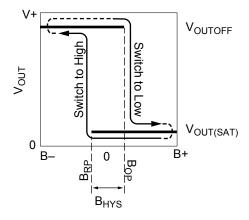

The output of these devices switches low (turns on) when a magnetic field perpendicular to the Hall element exceeds the operate point threshold,  $B_{OP}$  (see Figure 2). After turn-on, the output voltage is  $V_{OUT(SAT)}$ . The output transistor is capable of continuously sinking up to 30 mA. When the magnetic field is reduced below the release point,  $B_{RP}$ , the device output goes high (turns off) to  $V_{OUTOFF}$ . The difference in the magnetic operate and release points is the hysteresis,  $B_{HYS}$ , of the device. This built-in hysteresis allows clean switching of the output even in the presence of external mechanical vibration and electrical noise.

Removal of the magnetic field will leave the device output latched on if the last crossed switch point is  $B_{\text{OP}}$ , or latched off if the last crossed switch point is  $B_{\text{RP}}$ .

Figure 2: Switching Behavior of Latches

On the horizontal axis, the B+ direction indicates increasing south polarity magnetic field strength, and the B- direction indicates increasing north polarity field strength.

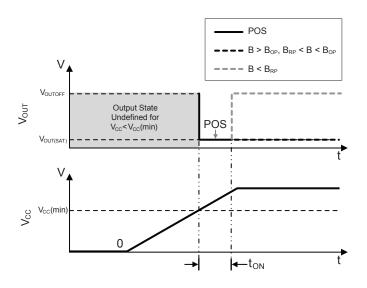

#### **POWER-ON BEHAVIOR**

Device power-on occurs once  $t_{ON}$  has elapsed. During the time prior to  $t_{ON}$ , and after  $V_{CC} \geq V_{CC}(min)$ , the output state is  $V_{OUT(SAT)}$  (Low). After  $t_{ON}$  has elapsed, the output will correspond with the applied magnetic field for  $B > B_{OP}$  or  $B < B_{RP}$ . See Figure 3 for an example.

Powering-on the device in the hysteresis range (less than  $B_{OP}$  and higher than  $B_{RP}$ ) will give an output state of  $V_{OUT(SAT)}$ . The correct state is attained after the first excursion beyond  $B_{OP}$  or  $B_{RP}$ .

Figure 3: Power-On Timing Diagram

#### **FUNCTIONAL SAFETY**

The APS12200, APS12210, and APS12230 were developed in accordance with ISO 26262:2011 as a hardware Safety Ele-

ment out of Context (SEooC) with ASIL A capability for use in automotive safety-related systems when integrated and used in the manner prescribed in the applicable safety manual and datasheet. The APS12200, APS12210, and APS12230 can be easily integrated into safety-critical systems requiring higher ASIL ratings that incorporate external diagnostics or use measures such as redundancy. Safety documentation will be provided to support and guide the integration process. For further information, contact your local Allegro field applications engineer or sales representative.

A R<sub>S</sub> and C<sub>OUT</sub> are recommended for maximum robustness in an automotive environment.

**Figure 4: Enhanced Protection Circuit**

#### **APPLICATIONS**

It is strongly recommended that an external bypass capacitor be connected (in close proximity to the Hall element) between the supply and ground of the device to guarantee correct performance under harsh environmental conditions and to reduce noise from internal circuitry. As is shown in Figure 1: Typical Application Circuit, a 0.1  $\mu F$  capacitor is required. In applications where maximum robustness is required, such as in an automobile, additional measures may be taken. In Figure 4: Enhanced Protection Circuit, a resistor in series with the VCC pin and a capacitor on the VOUT pin enhance the EMC immunity of the device. It is up to the user to fully qualify the Allegro sensor IC in their end system to ensure they achieve their system requirements.

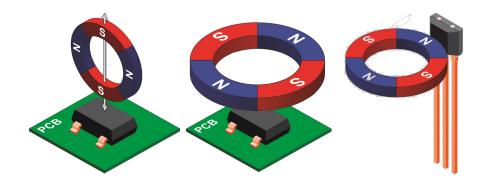

These devices are sensitive in the direction perpendicular to the branded face, as depicted in Figure 5. For further information, extensive applications information on magnets and Hall-effect sensors is available in:

- Hall-Effect IC Applications Guide, AN27701,

- Hall-Effect Devices: Guidelines for Designing Subassemblies Using Hall-Effect Devices AN27703.1

- Soldering Methods for Allegro's Products SMD and Through-Hole, AN26009

All are provided on the Allegro website:

www.allegromicro.com

Figure 5: Sensing Configurations

#### **CHOPPER STABILIZATION**

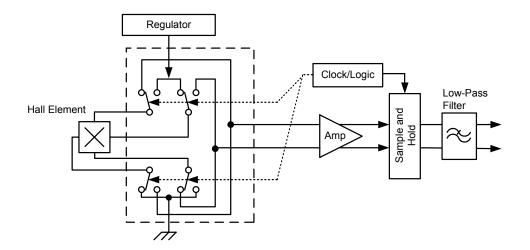

A limiting factor for switch point accuracy when using Hall-effect technology is the small signal voltage developed across the Hall plate. This voltage is proportionally small relative to the offset that can be produced at the output of the Hall sensor. This makes it difficult to process the signal and maintain an accurate, reliable output over the specified temperature and voltage range. Chopper stabilization is a proven approach used to minimize Hall offset.

The Allegro technique, dynamic quadrature offset cancellation, removes key sources of the output drift induced by temperature and package stress. This offset reduction technique is based on a signal modulation-demodulation process. Figure 6 illustrates how it is implemented.

The undesired offset signal is separated from the magnetically induced signal in the frequency domain through modulation. The

subsequent demodulation acts as a modulation process for the offset, causing the magnetically induced signal to recover its original spectrum at baseband while the DC offset becomes a highfrequency signal. Then, using a low-pass filter, the signal passes while the modulated DC offset is suppressed. Allegro's innovative chopper stabilization technique uses a high-frequency clock. The high-frequency operation allows a greater sampling rate that produces higher accuracy, reduced jitter, and faster signal processing. Additionally, filtering is more effective and results in a lower noise analog signal at the sensor output. Devices such as the APS12200, APS12210, and APS12230 that use this approach have an extremely stable quiescent Hall output voltage, are immune to thermal stress, and have precise recoverability after temperature cycling. This technique is made possible through the use of a BiCMOS process which allows the use of low offset and low noise amplifiers in combination with high-density logic and sample-and-hold circuits.

Figure 6: Model of Chopper Stabilization (Dynamic Offset Cancellation)

#### **POWER DERATING**

The device must be operated below the maximum junction temperature of the device,  $T_J(max)$ . Under certain combinations of peak conditions, reliable operation may require derating supplied power or improving the heat dissipation properties of the application. This section presents a procedure for correlating factors affecting operating  $T_J$ . (Thermal data is also available on the Allegro MicroSystems website.)

The Package Thermal Resistance,  $R_{\theta JA}$ , is a figure of merit summarizing the ability of the application and the device to dissipate heat from the junction (die), through all paths to the ambient air. Its primary component is the Effective Thermal Conductivity, K, of the printed circuit board, including adjacent devices and traces. Radiation from the die through the device case,  $R_{\theta JC}$ , is a relatively small component of  $R_{\theta JA}$ . Ambient air temperature,  $T_A$ , and air motion are significant external factors, damped by overmolding.

The resulting power dissipation capability directly reflects upon the ability of the device to withstand extreme operating conditions. The junction temperature mission profile specified in the Absolute Maximum Ratings table designates a total operating life capability based on qualification for the most extreme conditions, where  $T_J$  may reach  $175^{\circ}$ C.

The silicon IC is heated internally when current is flowing into the VCC terminal. When the output is on, current sinking into the VOUT terminal generates additional heat. This may increase the junction temperature,  $T_J$ , above the surrounding ambient temperature. The APS12200, APS12210, and APS12230 are permitted to operate up to  $T_J = 175^{\circ}\text{C}$ . As mentioned above, an operating device will increase  $T_J$  according to equations 1, 2, and 3 below. This allows an estimation of the maximum ambient operating temperature.

$$P_D = V_{IN} \times I_{IN} \tag{1}$$

$$\Delta T = P_D \times R_{\Theta IA} \tag{2}$$

$$T_I = T_A + \Delta T \tag{}$$

For example, given common conditions such as:  $T_A$ = 25°C,  $V_{CC}$  = 12 V,  $I_{CC}$  = 2 mA,  $V_{OUT}$  = 185 mV,  $I_{OUT}$  = 20 mA (output on), and  $R_{\theta JA}$  = 165°C/W, then:

$$P_D = (V_{CC} \times I_{CC}) + (V_{OUT} \times I_{OUT}) = (12 \ V \times 2 \ mA) + (185 \ mV \times 20 \ mA) = 24 \ mW + 3.7 \ mW = 27.7 \ mW$$

$$\Delta T = P_D \times R_{\theta JA} = 27.7 \text{ mW} \times 165 \text{°C/W} = 4.6 \text{°C}$$

$$T_J = T_A + \Delta T = 25^{\circ}C + 4.6^{\circ}C = 29.6^{\circ}C$$

A worst-case estimate,  $P_D(max)$ , represents the maximum allowable power level ( $V_{CC}(max)$ ,  $I_{CC}(max)$ ), without exceeding  $T_J(max)$ , at a selected  $R_{\theta JA}$ .

For example, given the conditions  $R_{\theta JA} = 228^{\circ}\text{C/W}$ ,  $T_{J}(\text{max}) = 175^{\circ}\text{C}$ ,  $V_{CC}(\text{max}) = 24$  V,  $I_{CC}(\text{max}) = 3$  mA,  $V_{OUT} = 500$  mV, and  $I_{OUT} = 25$  mA (output on), the maximum allowable operating ambient temperature can be determined.

The power dissipation required for the output is shown below:

$$P_D(V_{OUT}) = V_{OUT} \times I_{OUT} = 500 \text{ mV} \times 25 \text{ mA} = 12.5 \text{ mW}$$

The power dissipation required for the IC supply is shown below:

$$P_D(V_{CC}) = V_{CC} \times I_{CC} = 24 \ V \times 3 \ mA = 72 \ mW$$

Next, by inverting using equation 2:

$$\Delta T = P_D \times R_{\theta JA} = [P_D(V_{OUT}) + P_D(V_{CC})] \times 228^{\circ}C/W =$$

$$(12.5 \text{ mW} + 72 \text{ mW}) \times 228^{\circ}C/W =$$

$$84.5 \text{ mW} \times 228^{\circ}C/W = 19.3^{\circ}C$$

Finally, by inverting equation 3 with respect to voltage:

$$T_A(est) = T_J(max) - \Delta T = 175^{\circ}C - 19.3^{\circ}C = 155.7^{\circ}C$$

In the above case, there is sufficient power dissipation capability to operate up to  $T_A(est)$ . The example indicates that  $T_A(max)$  can be as high as 155.7°C without exceeding  $T_J(max)$ . Howe-

- ver, the  $T_A(max)$  rating of the devices is 150°C; the APS12200,

- APS12210, and APS12230 performance is not guaranteed above  $T_A = 150$  °C.

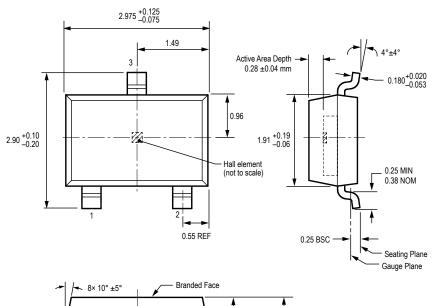

## Package LH, 3-Pin (SOT-23W)

## For Reference Only – Not for Tooling Use (Reference Allegro DWG-0000628, Rev. 1)

(Reference Allegro DWG-0000628, Rev. 1) NOT TO SCALE Dimensions in millimeters

Dimensions in millimeters

Dimensions exclusive of mold flash, gate burrs, and dambar protrusions

Exact case and lead configuration at supplier discretion within limits shown

#### PCB Layout Reference View

All pads a minimum of 0.20 mm from all adjacent pads; adjust as necessary to meet application process requirements and PCB layout tolerances

Standard Branding Reference View

### Package UA, 3-Pin SIP

#### For Reference Only - Not For Tooling Use

(Reference DWG-000404, Rev. 1)

NOT TO SCALE

Dimensions in millimeters

Exact case and lead configuration at supplier discretion within limits shown

APS12200, APS12210, and APS12230

## **High-Temperature Precision Hall-Effect Latches**

#### **Revision History**

| Number | Date              | Description                                                                                                              |

|--------|-------------------|--------------------------------------------------------------------------------------------------------------------------|

| _      | March 6, 2018     | Initial release                                                                                                          |

| 1      | February 11, 2019 | Minor editorial updates                                                                                                  |

| 2      | May 28, 2019      | Updated Typical Application Diagram (page 3), Functional Safety section (page 11), and Power Derating section (page 13). |

| 3      | July 21, 2021     | Updated ASIL Status to pending assessment                                                                                |

| 4      | July 18, 2022     | Updated package drawings (pages 14-15)                                                                                   |

| 5      | November 27, 2024 | Updated ASIL status (page 1, page 11)                                                                                    |

Copyright 2024, Allegro MicroSystems.

Allegro MicroSystems reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in any devices or systems, including but not limited to life support devices or systems, in which a failure of Allegro's product can reasonably be expected to cause bodily harm.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

Copies of this document are considered uncontrolled documents.

For the latest version of this document, visit our website: www.allegromicro.com